## PCI-EXPRESS GEN 1, GEN 2, GEN 3, AND GEN 4 **FANOUT BUFFER**

#### **Features**

- PCI-Express Gen 1, Gen 2, Gen 3, Six PCI-Express buffered clock and Gen 4 common clock compliant

- Supports Serial ATA (SATA) at 100 MHz

- 100-210 MHz operation

- Low power, push pull, differential output buffers

- Internal termination for maximum integration

- Dedicated output enable pin for each

- outputs

- Clock input spread tolerable

- Supports LVDS outputs

- I<sup>2</sup>C support with readback capabilities

- Extended temperature:

- –40 to 85 °C

- 3.3 V power supply

- 32-pin QFN package

### **Applications**

- Network attached storage

- Multi-function printers

- Wireless access point

- Routers

### **Description**

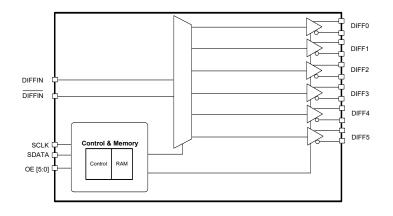

The Si53156 is a spread spectrum tolerant PCle clock buffer that can source six PCIe clocks simultaneously. The device has six hardware output enable control inputs for enabling the respective differential outputs on the fly. The device also features output enable control through I<sup>2</sup>C communication. I<sup>2</sup>C programmability is also available to dynamically control skew, edge rate and amplitude on the true, compliment, or both differential signals on the clock outputs. This control feature enables optimal signal integrity as well as optimal EMI signature on the clock outputs. Measuring PCle clock jitter is quick and easy with the Skyworks Solutions PCIe Clock Jitter Tool. Download it for free at https://www.skyworksinc.com/en/application-pages/pci-express-learning-center.

### **Functional Block Diagram**

Patents pending

3

# TABLE OF CONTENTS

| Section                         | Page |

|---------------------------------|------|

| I. Electrical Specifications    | 4    |

| 2. Functional Description       |      |

| 2.1. OE Pin Definition          | 7    |

| 2.2. OE Assertion               | 7    |

| 2.3. OE Deassertion             | 7    |

| B. Test and Measurement Setup   |      |

| l. Control Registers            | 10   |

| 4.1. I2C Interface              | 10   |

| 4.2. Data Protocol              |      |

| 5. Pin Descriptions: 32-Pin QFN |      |

| 6. Ordering Guide               |      |

| 7. Package Outline              | 18   |

| 3. Land Pattern                 | 19   |

| Document Change List            | 21   |

## 1. Electrical Specifications

**Table 1. DC Electrical Specifications**

| Parameter                                           | Symbol               | Test Condition                                                                 | Min                   | Тур | Max                   | Unit |

|-----------------------------------------------------|----------------------|--------------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| 3.3 V Operating Voltage                             | VDD core             | 3.3 ± 5%                                                                       | 3.135                 | _   | 3.465                 | V    |

| 3.3 V Input High Voltage                            | V <sub>IH</sub>      | Control input pins                                                             | 2.0                   | _   | V <sub>DD</sub> + 0.3 | V    |

| 3.3 V Input Low Voltage                             | V <sub>IL</sub>      | Control input pins                                                             | V <sub>SS</sub> - 0.3 | _   | 0.8                   | V    |

| Input High Voltage                                  | V <sub>IHI2C</sub>   | SDATA, SCLK                                                                    | 2.2                   | _   | _                     | V    |

| Input Low Voltage                                   | V <sub>ILI2C</sub>   | SDATA, SCLK                                                                    | _                     | _   | 1.0                   | V    |

| Input High Leakage Current                          | I <sub>IH</sub>      | Except internal pull-down resistors, 0 < V <sub>IN</sub> < V <sub>DD</sub>     | _                     |     | 5                     | μА   |

| Input Low Leakage Current                           | I <sub>IL</sub>      | Except internal pull-up resistors, 0 < V <sub>IN</sub> < V <sub>DD</sub>       | <b>-</b> 5            | _   | _                     | μА   |

| 3.3 V Output High Voltage<br>(Single-Ended Outputs) | V <sub>OH</sub>      | I <sub>OH</sub> = -1 mA                                                        | 2.4                   | _   | _                     | V    |

| 3.3 V Output Low Voltage (Single-Ended Outputs)     | V <sub>OL</sub>      | I <sub>OL</sub> = 1 mA                                                         | _                     |     | 0.4                   | V    |

| High-impedance Output<br>Current                    | I <sub>OZ</sub>      |                                                                                | -10                   |     | 10                    | μА   |

| Input Pin Capacitance                               | C <sub>IN</sub>      |                                                                                | 1.5                   |     | 5                     | pF   |

| Output Pin Capacitance                              | C <sub>OUT</sub>     |                                                                                | _                     | _   | 6                     | pF   |

| Pin Inductance                                      | L <sub>IN</sub>      |                                                                                | _                     | _   | 7                     | nΗ   |

| Power Down Current                                  | I <sub>DD</sub> PD   |                                                                                | _                     | _   | 1                     | mA   |

| Dynamic Supply Current in Fanout Mode               | I <sub>DD_3.3V</sub> | Differential clocks with 5"<br>traces and 2 pF load, fre-<br>quency at 100 MHz | _                     | _   | 45                    | mA   |

**Table 2. AC Electrical Specifications**

| Parameter                                                                                     | Symbol                         | Condition                                                                                       | Min  | Тур | Max  | Unit |

|-----------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------|------|-----|------|------|

| DIFFIN at 0.7 V                                                                               | •                              |                                                                                                 |      |     |      |      |

| Input Frequency Range                                                                         | f <sub>in</sub>                |                                                                                                 | 100  | _   | 210  | MHz  |

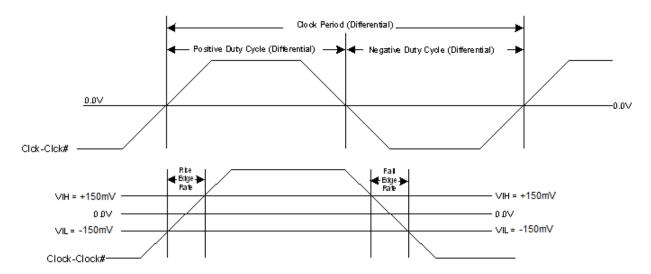

| Rising and Falling Slew Rates for<br>Each Clock Output Signal in a<br>Given Differential Pair | T <sub>R</sub> /T <sub>F</sub> | Single ended measurement:<br>V <sub>OL</sub> = 0.175 to V <sub>OH</sub> = 0.525 V<br>(Averaged) | 0.6  | _   | 4    | V/ns |

| Differential Input High Voltage                                                               | V <sub>IH</sub>                |                                                                                                 | 150  | _   | _    | mV   |

| Differential Input Low Voltage                                                                | V <sub>IL</sub>                |                                                                                                 | _    | _   | -150 | mV   |

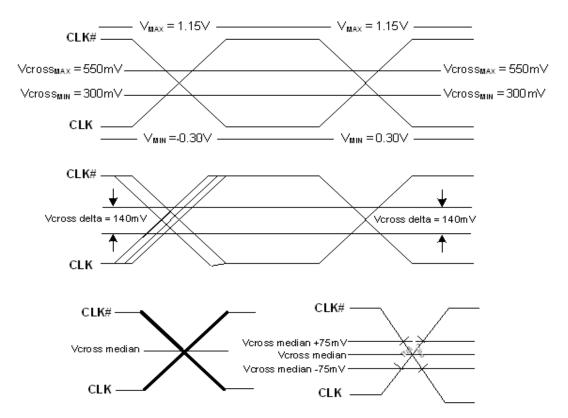

| Crossing Point Voltage at 0.7 V<br>Swing                                                      | V <sub>OX</sub>                | Single-ended measurement                                                                        | 250  | _   | 550  | mV   |

| Vcross Variation over all edges                                                               | $\Delta V_{OX}$                | Single-ended measurement                                                                        | _    | _   | 140  | mV   |

| Differential Ringback Voltage                                                                 | V <sub>RB</sub>                |                                                                                                 | -100 | _   | 100  | mV   |

| Time before ringback allowed                                                                  | T <sub>STABLE</sub>            |                                                                                                 | 500  | _   | _    | ps   |

| Absolute maximum input voltage                                                                | V <sub>MAX</sub>               |                                                                                                 | _    | _   | 1.15 | V    |

| Absolute minimum input voltage                                                                | V <sub>MIN</sub>               |                                                                                                 | -0.3 | _   | _    | V    |

| Duty Cycle for Each Clock Output<br>Signal in a Given<br>Differential Pair                    | T <sub>DC</sub>                | Measured at crossing point V <sub>OX</sub>                                                      | 45   | _   | 55   | %    |

| Rise/Fall Matching                                                                            | T <sub>RFM</sub>               | Determined as a fraction of $2 \times (T_R - T_F)/(T_R + T_F)$                                  | _    | _   | 20   | %    |

| DIFF at 0.7 V                                                                                 | •                              |                                                                                                 |      | •   |      | •    |

| Duty Cycle                                                                                    | T <sub>DC</sub>                | Measured at 0 V differential                                                                    | 45   | _   | 55   | %    |

| Clock Skew                                                                                    | T <sub>SKEW</sub>              | Measured at 0 V differential                                                                    | _    | _   | 50   | ps   |

| Additive Peak Jitter                                                                          | Pk-Pk                          |                                                                                                 | 0    | _   | 10   | ps   |

| Additive PCIe Gen 2 Phase Jitter                                                              | RMS <sub>GEN2</sub>            | 10 kHz < F < 1.5 MHz                                                                            | 0    | _   | 0.5  | ps   |

|                                                                                               |                                | 1.5 MHz< F < Nyquist Rate                                                                       | 0    | _   | 0.5  | ps   |

| Additive PCIe Gen 3 Phase Jitter                                                              | RMS <sub>GEN3</sub>            | Includes PLL BW 2-4 MHz<br>(CDR = 10 MHz)                                                       | 0    | _   | 0.10 | ps   |

| Additive PCIe Gen 4 Phase Jitter                                                              | RMS <sub>GEN4</sub>            | PCIe Gen 4                                                                                      |      | _   | 0.10 | ps   |

| Additive Cycle to Cycle Jitter                                                                | T <sub>CCJ</sub>               | Measured at 0 V differential                                                                    | _    | _   | 50   | ps   |

| Long-term Accuracy                                                                            | L <sub>ACC</sub>               | Measured at 0 V differential                                                                    | _    | _   | 100  | ppm  |

| Rising/Falling Slew rate                                                                      | T <sub>R</sub> /T <sub>F</sub> | Measured differentially from ±150 mV                                                            | 2.5  | _   | 8    | V/ns |

| Crossing Point Voltage at 0.7 V<br>Swing                                                      | V <sub>OX</sub>                |                                                                                                 | 300  | _   | 550  | mV   |

### Notes:

- 1. Gen 4 specifications based on the PCI-Express Base Specification 4.0 rev. 0.5.

- 2. Download the Skyworks Solutions PCIe Clock Jitter Tool at https://www.skyworksinc.com/en/application-pages/pci-express-learning-center.

**Table 2. AC Electrical Specifications (Continued)**

| Parameter                         | Symbol              | Condition                                                                   | Min  | Тур | Max | Unit |

|-----------------------------------|---------------------|-----------------------------------------------------------------------------|------|-----|-----|------|

| Enable/Disable and Setup          |                     |                                                                             |      |     |     |      |

| Clock Stabilization from Power-Up | T <sub>STABLE</sub> | Measured from the point when both V <sub>DD</sub> and clock input are valid | _    | _   | 5   | ms   |

| Stopclock Set-up Time             | T <sub>SS</sub>     |                                                                             | 10.0 |     | _   | ns   |

### Notes:

- 1. Gen 4 specifications based on the PCI-Express Base Specification 4.0 rev. 0.5.

- 2. Download the Skyworks Solutions PCIe Clock Jitter Tool at https://www.skyworksinc.com/en/application-pages/pciexpress-learning-center.

**Table 3. Absolute Maximum Conditions**

| Parameter                                    | Symbol               | Condition                   | Min  | Тур | Max | Unit     |

|----------------------------------------------|----------------------|-----------------------------|------|-----|-----|----------|

| Main Supply Voltage                          | V <sub>DD_3.3V</sub> | Functional                  |      |     | 4.6 | V        |

| Input Voltage                                | V <sub>IN</sub>      | Relative to V <sub>SS</sub> | -0.5 |     | 4.6 | $V_{DC}$ |

| Temperature, Storage                         | T <sub>S</sub>       | Non-functional              | -65  |     | 150 | ů        |

| Industrial Temperature, Operating<br>Ambient | T <sub>A</sub>       | Functional                  | -40  | _   | 85  | °C       |

| Commercial Temperature, Operating<br>Ambient | T <sub>A</sub>       | Functional                  | 0    | _   | 85  | ů        |

| Temperature, Junction                        | $T_J$                | Functional                  |      |     | 150 | °C       |

| Dissipation, Junction to Case                | Ø <sub>JC</sub>      | JEDEC (JESD 51)             | _    | _   | 17  | °C/W     |

| Dissipation, Junction to Ambient             | Ø <sub>JA</sub>      | JEDEC (JESD 51)             | _    | _   | 35  | °C/W     |

| ESD Protection (Human Body Model)            | ESD <sub>HBM</sub>   | JEDEC (JESD 22 - A114)      | 2000 | _   |     | V        |

| Flammability Rating                          | UL-94                | UL (Class)                  |      | V-0 |     |          |

**Note:** Multiple Supplies: The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is not required.

### 2. Functional Description

### 2.1. OE Pin Definition

The OE pins are active high inputs used to enable and disable the output clocks. To enable the output clock, the OE pin needs to be logic high and the  $I^2C$  output enable bit needs to be logic high. There are two methods to disable the output clocks: the OE is pulled to a logic low, or the  $I^2C$  enable bit is set to a logic low. The OE pins are required to be driven at all times even though they have an internal 100 k $\Omega$  resistor.

### 2.2. OE Assertion

The OE signals are active high inputs used for synchronous stopping and starting the DIFF output clocks respectively while the rest of the clock generator continues to function. The assertion of the OE signal by making it logic high causes stopped respective DIFF outputs to resume normal operation. No short or stretched clock pulses are produced when the clock resumes. The maximum latency from the assertion to active outputs is no more than two to six output clock cycles.

#### 2.3. OE Deassertion

When the OE pin is deasserted by making it logic low, the corresponding DIFF output is stopped, and the final output state is driven low.

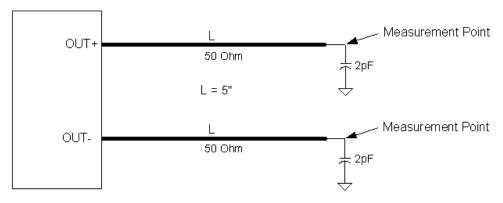

### 3. Test and Measurement Setup

This diagram shows the test load configuration for differential clock signals.

Figure 1. 0.7 V Differential Load Configuration

Figure 2. Differential Measurement for Differential Output Signals (for AC Parameters Measurement)

Figure 3. Single-Ended Measurement for Differential Output Signals (for AC Parameters Measurement)

### 4. Control Registers

### 4.1. I<sup>2</sup>C Interface

To enhance the flexibility and function of the clock buffer, an  $I^2C$  interface is provided. Through the  $I^2C$  Interface, various device functions are available, such as individual clock output enable. The registers associated with the  $I^2C$  Interface initialize to their default setting at power-up. The use of this interface is optional. Clock device register changes are normally made at system initialization, if any are required. Power management functions can only be programed in program mode and not in normal operation modes.

### 4.2. Data Protocol

The I<sup>2</sup>C protocol accepts byte write, byte read, block write, and block read operations from the controller. For block write/read operation, access the bytes in sequential order from lowest to highest (most significant bit first) with the ability to stop after any complete byte is transferred. For byte write and byte read operations, the system controller can access individually indexed bytes.

The block write and block read protocol is outlined in Table 4 on page 10 while Table 5 on page 11 outlines byte write and byte read protocol. The slave receiver address is 11010110 (D6h).

Table 4. Block Read and Block Write Protocol

|       | Block Write Protocol         |       | Block Read Protocol               |

|-------|------------------------------|-------|-----------------------------------|

| Bit   | Description                  | Bit   | Description                       |

| 1     | Start                        | 1     | Start                             |

| 8:2   | Slave address—7 bits         | 8:2   | Slave address—7 bits              |

| 9     | Write                        | 9     | Write                             |

| 10    | Acknowledge from slave       | 10    | Acknowledge from slave            |

| 18:11 | Command Code—8 bits          | 18:11 | Command Code–8 bits               |

| 19    | Acknowledge from slave       | 19    | Acknowledge from slave            |

| 27:20 | Byte Count—8 bits            | 20    | Repeat start                      |

| 28    | Acknowledge from slave       | 27:21 | Slave address—7 bits              |

| 36:29 | Data byte 1–8 bits           | 28    | Read = 1                          |

| 37    | Acknowledge from slave       | 29    | Acknowledge from slave            |

| 45:38 | Data byte 2–8 bits           | 37:30 | Byte Count from slave—8 bits      |

| 46    | Acknowledge from slave       | 38    | Acknowledge                       |

|       | Data Byte/Slave Acknowledges | 46:39 | Data byte 1 from slave—8 bits     |

|       | Data Byte N–8 bits           | 47    | Acknowledge                       |

|       | Acknowledge from slave       | 55:48 | Data byte 2 from slave—8 bits     |

|       | Stop                         | 56    | Acknowledge                       |

|       |                              |       | Data bytes from slave/Acknowledge |

|       |                              |       | Data Byte N from slave—8 bits     |

|       |                              |       | NOT Acknowledge                   |

|       |                              |       | Stop                              |

**Table 5. Byte Read and Byte Write Protocol**

|       | Byte Write Protocol    | Byte Read Protocol |                        |  |

|-------|------------------------|--------------------|------------------------|--|

| Bit   | Description            | Bit                | Description            |  |

| 1     | Start                  | 1                  | Start                  |  |

| 8:2   | Slave address–7 bits   | 8:2                | Slave address–7 bits   |  |

| 9     | Write                  | 9                  | Write                  |  |

| 10    | Acknowledge from slave | 10                 | Acknowledge from slave |  |

| 18:11 | Command Code–8 bits    | 18:11              | Command Code–8 bits    |  |

| 19    | Acknowledge from slave | 19                 | Acknowledge from slave |  |

| 27:20 | Data byte–8 bits       | 20                 | Repeated start         |  |

| 28    | Acknowledge from slave | 27:21              | Slave address–7 bits   |  |

| 29    | Stop                   | 28                 | Read                   |  |

|       |                        | 29                 | Acknowledge from slave |  |

|       |                        | 37:30              | Data from slave–8 bits |  |

|       |                        | 38                 | NOT Acknowledge        |  |

|       |                        | 39                 | Stop                   |  |

### Control Register 0. Byte 0

| Bit  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name |     |     |     |     |     |     |     |     |

| Туре | R/W |

Reset settings = 00000000

| Bit | Name     | Function |

|-----|----------|----------|

| 7:0 | Reserved |          |

### Control Register 1. Byte 1

| Bit  | D7  | D6  | D5  | D4       | D3  | D2       | D1  | D0       |

|------|-----|-----|-----|----------|-----|----------|-----|----------|

| Name |     |     |     | DIFF0_OE |     | DIFF1_OE |     | DIFF2_OE |

| Type | R/W | R/W | R/W | R/W      | R/W | R/W      | R/W | R/W      |

Reset settings = 00010101

| Bit | Name     | Function                 |

|-----|----------|--------------------------|

| 7:5 | Reserved |                          |

| 4   | DIFF0_OE | Output Enable for DIFF0. |

|     |          | 0: Output disabled.      |

|     |          | 1: Output Enabled.       |

| 3   | Reserved |                          |

| 2   | DIFF1_OE | Output Enable for DIFF1. |

|     |          | 0: Output disabled.      |

|     |          | 1: Output enabled.       |

| 1   | Reserved |                          |

| 0   | DIFF2_OE | Output Enable for DIFF2. |

|     |          | 0: Output disabled.      |

|     |          | 1: Output enabled.       |

### Control Register 2. Byte 2

| Bit  | D7       | D6       | D5       | D4  | D3  | D2  | D1  | D0  |

|------|----------|----------|----------|-----|-----|-----|-----|-----|

| Name | DIFF3_OE | DIFF4_OE | DIFF5_OE |     |     |     |     |     |

| Type | R/W      | R/W      | R/W      | R/W | R/W | R/W | R/W | R/W |

Reset settings = 11100000

| Bit | Name     | Function                                                          |

|-----|----------|-------------------------------------------------------------------|

| 7   | DIFF3_OE | Output Enable for DIFF3.  0: Output disabled.  1: Output enabled. |

| 6   | DIFF4_OE | Output Enable for DIFF4.  0: Output disabled.  1: Output enabled. |

| 5   | DIFF5_OE | Output Enable for DIFF5.  0: Output disabled.  1: Output enabled. |

| 4:0 | Reserved |                                                                   |

### Control Register 3. Byte 3

| Bit  | D7            | D6  | D5  | D4             | D3  | D2  | D1  | D0  |

|------|---------------|-----|-----|----------------|-----|-----|-----|-----|

| Name | Rev Code[3:0] |     |     | Vendor ID[3:0] |     |     |     |     |

| Туре | R/W           | R/W | R/W | R/W            | R/W | R/W | R/W | R/W |

Reset settings = 00001000

| Bit | Name           | Function                    |  |

|-----|----------------|-----------------------------|--|

| 7:4 | Rev Code[3:0]  | Program Revision Code.      |  |

| 3:0 | Vendor ID[3:0] | Vendor Identification Code. |  |

### Control Register 4. Byte 4

| Bit  | D7  | D6      | D5  | D4  | D3  | D2  | D1  | D0  |

|------|-----|---------|-----|-----|-----|-----|-----|-----|

| Name |     | BC[7:0] |     |     |     |     |     |     |

| Туре | R/W | R/W     | R/W | R/W | R/W | R/W | R/W | R/W |

Reset settings = 00000110

| Bit | Name    | Function             |

|-----|---------|----------------------|

| 7:0 | BC[7:0] | Byte Count Register. |

### Control Register 5. Byte 5

| Bit  | D7           | D6               | D5               | D4               | D3  | D2  | D1  | D0  |

|------|--------------|------------------|------------------|------------------|-----|-----|-----|-----|

| Name | DIFF_Amp_Sel | DIFF_Amp_Cntl[2] | DIFF_Amp_Cntl[1] | DIFF_Amp_Cntl[0] |     |     |     |     |

| Туре | R/W          | R/W              | R/W              | R/W              | R/W | R/W | R/W | R/W |

Reset settings = 11011000

| Bit | Name             | Function                                                                                                                                                    |

|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DIFF_Amp_Sel     | Amplitude Control for DIFF Differential Outputs.  0: Differential outputs with Default amplitude.  1: Differential outputs amplitude is set by Byte 5[6:4]. |

| 6   | DIFF_Amp_Cntl[2] | DIFF Differential Outputs Amplitude Adjustment.                                                                                                             |

| 5   | DIFF_Amp_Cntl[1] | 000: 300 mV 001: 400 mV 010: 500 mV 011: 600 mV                                                                                                             |

| 4   | DIFF_Amp_Cntl[0] | 100: 700 mV 101: 800 mV 110: 900 mV 111: 1000 mV                                                                                                            |

| 3:0 | Reserved         |                                                                                                                                                             |

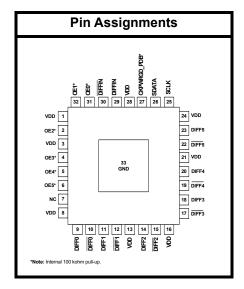

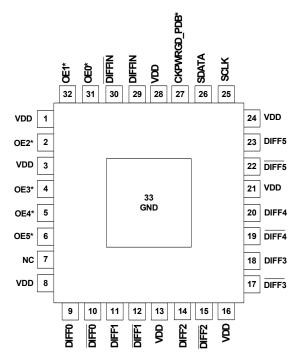

## 5. Pin Descriptions: 32-Pin QFN

\*Note: Internal 100 kohm pull-up.

Figure 4. 32-Pin QFN

Table 6. Si53156 32-Pin QFN Descriptions

| Pin# | Name  | Туре   | Description                                                                                                              |

|------|-------|--------|--------------------------------------------------------------------------------------------------------------------------|

| 1    | VDD   | PWR    | 3.3 V power supply.                                                                                                      |

| 2    | OE2   | I,PU   | Active high input pin enables DIFF2 (internal 100 k $\Omega$ pull-up). Refer to Table 1 on page 4 for OE specifications. |

| 3    | VDD   | PWR    | 3.3 V Power Supply                                                                                                       |

| 4    | OE3   | I,PU   | Active high input pin enables DIFF3 (internal 100 k $\Omega$ pull-up). Refer to Table 1 on page 4 for OE specifications. |

| 5    | OE4   | I,PU   | Active high input pin enables DIFF4 (internal 100 k $\Omega$ pull-up). Refer to Table 1 on page 4 for OE specifications. |

| 6    | OE5   | I,PU   | Active high input pin enables DIFF5 (internal 100 k $\Omega$ pull-up). Refer to Table 1 on page 4 for OE specifications. |

| 7    | NC    | NC     | No connect.                                                                                                              |

| 8    | VDD   | PWR    | 3.3 V power supply.                                                                                                      |

| 9    | DIFF0 | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                       |

| 10   | DIFF0 | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                       |

| 11   | DIFF1 | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                       |

Table 6. Si53156 32-Pin QFN Descriptions

| Pin# | Name        | Туре   | Description                                                                                                                                                                                                                                                   |

|------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12   | DIFF1       | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                                                                                                                                                            |

| 13   | VDD         | PWR    | 3.3 V power supply.                                                                                                                                                                                                                                           |

| 14   | DIFF2       | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                                                                                                                                                            |

| 15   | DIFF2       | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                                                                                                                                                            |

| 16   | VDD         | PWR    | 3.3 V power supply.                                                                                                                                                                                                                                           |

| 17   | DIFF3       | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                                                                                                                                                            |

| 18   | DIFF3       | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                                                                                                                                                            |

| 19   | DIFF4       | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                                                                                                                                                            |

| 20   | DIFF4       | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                                                                                                                                                            |

| 21   | VDD         | PWR    | 3.3 V power supply.                                                                                                                                                                                                                                           |

| 22   | DIFF5       | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                                                                                                                                                            |

| 23   | DIFF5       | O, DIF | 0.7 V, 100 MHz differential clock.                                                                                                                                                                                                                            |

| 24   | VDD         | PWR    | 3.3 V power supply.                                                                                                                                                                                                                                           |

| 25   | SCLK        | 1      | SMBus compatible SCLOCK.                                                                                                                                                                                                                                      |

| 26   | SDATA       | I/O    | SMBus compatible SDATA.                                                                                                                                                                                                                                       |

| 27   | CKPWRGD_PDB | I, PU  | $3.3~V~LVTTL$ input. This pin is a level sensitive strobe used to determine when latch inputs are valid and are ready to be sampled. A real-time active low input for asserting power down (PDB) and disabling all outputs (internal 100 k $\Omega$ pull-up). |

| 28   | VDD         | PWR    | 3.3 V power supply.                                                                                                                                                                                                                                           |

| 29   | DIFFIN      | I      | 0.7 V Differential True Input, typically 100 MHz. Input frequency range 100 to 210 MHz.                                                                                                                                                                       |

| 30   | DIFFIN      | 0      | 0.7 V Differential Complement Input, typically 100 MHz. Input frequency range 100 to 210 MHz.                                                                                                                                                                 |

| 31   | OE0         | I,PU   | Active high input pin enables DIFF0 (internal 100 k $\Omega$ pull-up). Refer to Table 1 on page 4 for OE specifications.                                                                                                                                      |

| 32   | OE1         | I,PU   | Active high input pin enables DIFF1 (internal 100 k $\Omega$ pull-up). Refer to Table 1 on page 4 for OE specifications.                                                                                                                                      |

| 33   | GND         | GND    | Ground for bottom pad of the IC.                                                                                                                                                                                                                              |

## 6. Ordering Guide

| Part Number     | Package Type             | Temperature            |

|-----------------|--------------------------|------------------------|

| Lead-free       |                          |                        |

| Si53156-A01AGM  | 32-pin QFN               | Extended, –40 to 85 °C |

| Si53156-A01AGMR | 32-pin QFN—Tape and Reel | Extended, –40 to 85 °C |

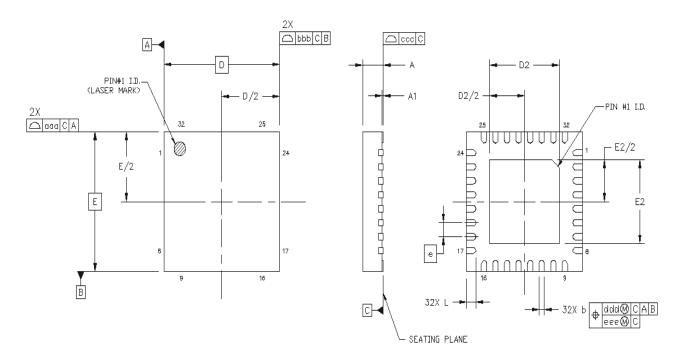

### 7. Package Outline

Figure 5 illustrates the package details for the Si53156. Table 7 lists the values for the dimensions shown in the illustration.

Figure 5. 32-Pin Quad Flat No Lead (QFN) Package

Table 7. Package Diagram Dimensions

| Dimension | Min      | Nom      | Max  |  |

|-----------|----------|----------|------|--|

| A         | 0.70     | 0.75     | 0.80 |  |

| A1        | 0.00     | 0.02     | 0.05 |  |

| b         | 0.18     | 0.25     | 0.30 |  |

| D         |          | 5.00 BSC |      |  |

| D2        | 3.15     | 3.20     | 3.25 |  |

| е         | 0.50 BSC |          |      |  |

| E         |          | 5.00 BSC |      |  |

| E2        | 3.15     | 3.20     | 3.25 |  |

| L         | 0.30     | 0.40     | 0.50 |  |

| aaa       | 0.10     |          |      |  |

| bbb       | 0.10     |          |      |  |

| ccc       | 0.08     |          |      |  |

| ddd       |          | 0.10     |      |  |

### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- **2.** Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

- 4. Coplanarity less than 0.08 mm.

- 5. Terminal #1 identifier and terminal numbering convention conform to JESD 95-1 SPP-012.

### 8. Land Pattern

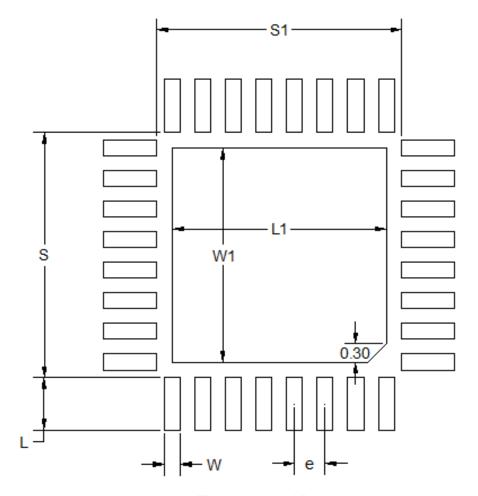

Figure 6 illustrates the recommended land pattern details for the Si53156 in a 32-pin QFN package. Table 8 lists the values for the dimensions shown in the illustration.

Figure 6. Land Pattern

**Table 8. PCB Land Pattern Dimensions**

| Dimension | mm   |

|-----------|------|

| S1        | 4.01 |

| S         | 4.01 |

| L1        | 3.20 |

| W1        | 3.20 |

| е         | 0.50 |

| W         | 0.26 |

| L         | 0.86 |

### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm).

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 m minimum, all the way around the pad.

#### Stencil Desian

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125mm (5 mils).

- 3. The ratio of stencil aperture to land pad size can be 1:1 for all perimeter pads.

- **4.** A 3x3 array of 0.85mm square openings on a 1.00mm pitch can be used for the center ground pad..

### **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### **DOCUMENT CHANGE LIST**

### Revision 0.1 to Revision 1.0

- Updated Features and Description.

- Updated Table 2.

- Updated Table 3.

- Updated Section 4.1.

### Revision 1.0 to Revision 1.1

- Updated Features on page 1.

- Updated Description on page 1.

- Updated specs in Table 2, "AC Electrical Specifications," on page 5.

- Added Land Pattern

### Revision 1.1 to Revision 1.2

Added condition for Clock Stabilization from Powerup, T<sub>STABLE</sub>, in Table 2.

### Revision 1.2 to Revision 1.3

■ Updated Package Outline on page 18.