# Si5341/40 Rev D Data Sheet

# Low-Jitter, 10 or 4-Output, Any-Frequency, Any-Output Clock Generator

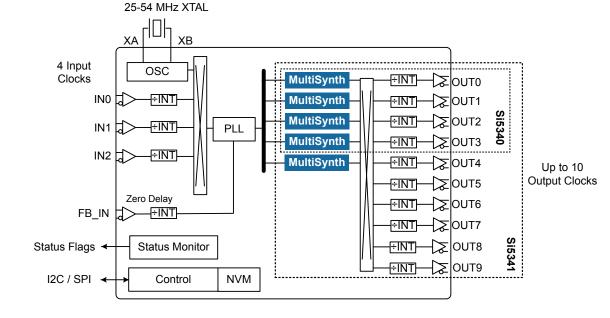

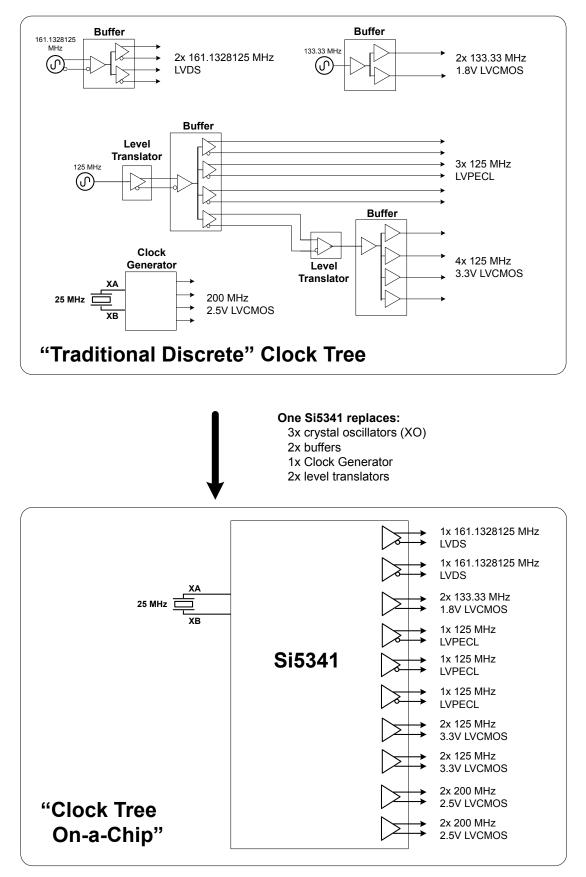

The any-frequency, any-output Si5341/40 clock generators combine a wide-band PLL with proprietary MultiSynth<sup>™</sup> fractional synthesizer technology to offer a versatile and high performance clock generator platform. This highly flexible architecture is capable of synthesizing a wide range of integer and non-integer related frequencies up to 1 GHz on 10 differential clock outputs while delivering sub-100 fs rms phase jitter performance with 0 ppm error. Each of the clock outputs can be assigned its own format and output voltage enabling the Si5341/40 to replace multiple clock ICs and oscillators with a single device making it a true "clock tree on a chip."

The Si5341/40 can be quickly and easily configured using ClockBuilderPro software. Custom part numbers are automatically assigned using a ClockBuilder Pro<sup>™</sup> for fast, free, and easy factory pre-programming or the Si5341/40 can be programmed via I<sup>2</sup>C and SPI serial interfaces.

#### Applications:

- · Clock tree generation replacing XOs, buffers, signal format translators

- · Any-frequency clock translation

- · Clocking for FPGAs, processors, memory

- · Ethernet switches/routers

- · OTN framers/mappers/processors

- · Test equipment and instrumentation

- · Broadcast video

#### KEY FEATURES

- Generates any combination of output frequencies from any input frequency

- · Ultra-low jitter of 90 fs rms

- · Input frequency range:

- External crystal: 25 to 54 MHz

- Differential clock: 10 to 750 MHz

- · LVCMOS clock: 10 to 250 MHz

- Output frequency range:

- Differential: 100 Hz to 1028 MHz

- LVCMOS: 100 Hz to 250 MHz

- Highly configurable outputs compatible with LVDS, LVPECL, LVCMOS, CML, and HCSL with programmable signal amplitude

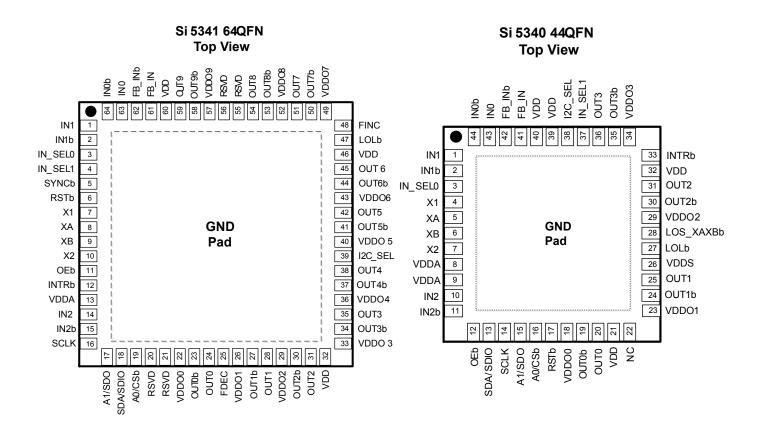

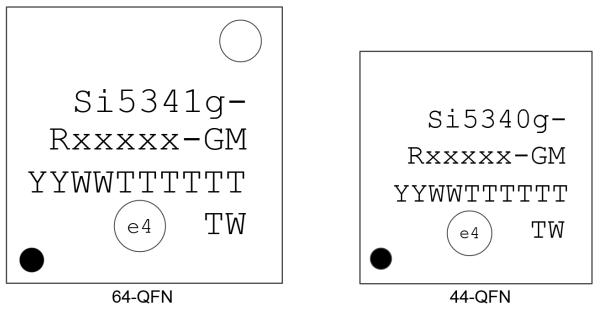

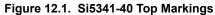

- Si5341: 4 input, 10 output, 64-QFN 9x9 mm

1

• Si5340: 4 input, 4 output, 44-QFN 7x7 mm

Si5341/40 Rev D Data Sheet • Features List

## 1. Features List

The Si5341/40 Rev D features are listed below:

- Generates any combination of output frequencies from any input frequency

- · Ultra-low jitter of 90 fs rms

- Input frequency range:

- · External crystal: 25 to 54 MHz

- Differential clock: 10 to 750 MHz

- LVCMOS clock: 10 to 250 MHz

- Output frequency range:

- · Differential: 100 Hz to 1028 MHz

- LVCMOS: 100 Hz to 250 MHz

- Highly configurable outputs compatible with LVDS, LVPECL, LVCMOS, CML, and HCSL with programmable signal amplitude

- · Locks to gapped clock inputs

- · Optional zero delay mode

- · Glitchless on the fly output frequency changes

- DCO mode: as low as 0.001 ppb steps

- · Core voltage

- VDD: 1.8 V ±5%

- VDDA: 3.3 V ±5%

- · Independent output clock supply pins

- 3.3 V, 2.5 V, or 1.8 V

- Serial interface: I<sup>2</sup>C or SPI

- · In-circuit programmable with non-volatile OTP memory

- ClockBuilder Pro software simplifies device configuration

- Si5341: 4 input, 10 output, 64-QFN 9x9 mm

- Si5340: 4 input, 4 output, 44-QFN 7x7 mm

- Temperature range: -40 to +85 °C

- · Pb-free, RoHS-6 compliant

## 2. Ordering Guide

| Ordering Part Number<br>(OPN) | Number of In-<br>put/Output<br>Clocks | Output Clock Frequency<br>Range (MHz) | Frequency Syn-<br>thesis Mode    | Package    | Temperature<br>Range |

|-------------------------------|---------------------------------------|---------------------------------------|----------------------------------|------------|----------------------|

| Si5341                        |                                       |                                       |                                  |            |                      |

| Si5341A-D-GM <sup>1, 2</sup>  |                                       | 0.0001 to 1028 MHz                    | Integer and                      |            |                      |

| Si5341B-D-GM <sup>1, 2</sup>  | 4/40                                  | 0.0001 to 350 MHz                     | Fractional                       | 64-QFN     | 40 to 95 °C          |

| Si5341C-D-GM <sup>1, 2</sup>  | - 4/10                                | 0.0001 to 1028 MHz                    | late was Oak                     | 9x9 mm     | –40 to 85 °C         |

| Si5341D-D-GM <sup>1, 2</sup>  |                                       | 0.0001 to 350 MHz                     | <ul> <li>Integer Only</li> </ul> |            |                      |

| Si5340                        |                                       |                                       |                                  |            |                      |

| Si5340A-D-GM <sup>1, 2</sup>  |                                       | 0.0001 to 1028 MHz                    | Integer and                      |            |                      |

| Si5340B-D-GM <sup>1, 2</sup>  |                                       | 0.0001 to 350 MHz                     | Fractional                       | 44-QFN     | 40.4- 05.80          |

| Si5340C-D-GM <sup>1, 2</sup>  | - 4/4                                 | 0.0001 to 1028 MHz                    |                                  | 7x7 mm     | –40 to 85 °C         |

| Si5340D-D-GM <sup>1, 2</sup>  | _                                     | 0.0001 to 350 MHz                     | <ul> <li>Integer Only</li> </ul> |            |                      |

| Si5341/40-D-EVB               | 1                                     |                                       |                                  | 1          | 1                    |

| Si5341-D-EVB                  |                                       |                                       |                                  | Evaluation |                      |

| Si5340-D-EVB                  |                                       | —                                     |                                  | Board      | _                    |

| Note:                         |                                       |                                       | -                                |            |                      |

## Table 2.1. Si5341/40 Ordering Guide

1. Add an R at the end of the OPN to denote tape and reel ordering options.

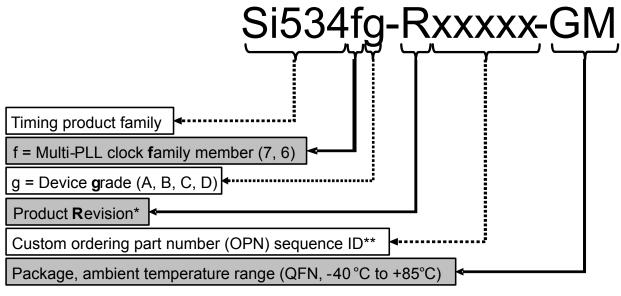

2. Custom, factory pre-programmed devices are available. Ordering part numbers are assigned by Skyworks and the ClockBuilder Pro software utility. Custom part number format is: e.g., Si5341A-Dxxxxx-GM, where "xxxxx" is a unique numerical sequence representing the preprogrammed configuration.

3. See 3.9 Custom Factory Preprogrammed Devices and 3.10 Enabling Features and/or Configuration Settings Not Available in ClockBuilder Pro for Factory Pre-Programmed Devices for important notes about specifying a preprogrammed device to use features or device register settings not yet available in CBPro.

\*See Ordering Guide table for current product revision \*\* 5 digits; assigned by ClockBuilder Pro

# **Table of Contents**

| 1. | Features List                                                                                                                                                                     | • | . 2 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

| 2. | Ordering Guide                                                                                                                                                                    |   | . 3 |

| 3. | Functional Description.                                                                                                                                                           |   | . 7 |

|    | 3.1 Power-up and Initialization                                                                                                                                                   |   | . 7 |

|    | 3.2 Frequency Configuration                                                                                                                                                       |   | . 7 |

|    | 3.3 Inputs                                                                                                                                                                        |   | . 7 |

|    | 3.3.1 XA/XB Clock and Crystal Input                                                                                                                                               |   |     |

|    | 3.3.2 Input Clocks (IN0, IN1, IN2)                                                                                                                                                |   |     |

|    |                                                                                                                                                                                   |   |     |

|    | 3.4 Fault Monitoring                                                                                                                                                              |   |     |

|    | 3.4.2 Interrupt Pin (INTRb)                                                                                                                                                       |   |     |

|    | 3.5 Outputs                                                                                                                                                                       |   |     |

|    | 3.5.1 Output Signal Format                                                                                                                                                        |   |     |

|    | 3.5.2 Differential Output Terminations                                                                                                                                            |   |     |

|    | 3.5.3 Programmable Common Mode Voltage for Differential Outputs                                                                                                                   |   |     |

|    | 3.5.4 LVCMOS Output Terminations                                                                                                                                                  |   |     |

|    | 3.5.5 LVCMOS Output Impedance and Drive Strength Selection       3.5.6 LVCMOS Output Signal Swing         3.5.6 LVCMOS Output Signal Swing       3.5.6 LVCMOS Output Signal Swing |   |     |

|    | 3.5.7 LVCMOS Output Polarity                                                                                                                                                      |   |     |

|    | 3.5.8 Output Enable/Disable                                                                                                                                                       |   |     |

|    | 3.5.9 Output Driver State When Disabled                                                                                                                                           |   |     |

|    | 3.5.10       Synchronous/Asynchronous Output Disable Feature                                                                                                                      |   |     |

|    | 3.5.12 Output Crosspoint                                                                                                                                                          |   |     |

|    | 3.5.13 Digitally Controlled Oscillator (DCO) Modes                                                                                                                                |   |     |

|    | 3.6 Power Management                                                                                                                                                              |   | .13 |

|    | 3.7 In-Circuit Programming                                                                                                                                                        |   | .13 |

|    | 3.8 Serial Interface                                                                                                                                                              |   |     |

|    | 3.9 Custom Factory Preprogrammed Devices                                                                                                                                          |   | .13 |

|    | 3.10 Enabling Features and/or Configuration Settings Not Available in ClockBuilder Pro for Factory                                                                                |   |     |

|    | Pre-Programmed Devices                                                                                                                                                            |   | .14 |

| 4. | Register Map                                                                                                                                                                      |   | 16  |

| 5. | Electrical Specifications                                                                                                                                                         |   | 17  |

| 6. | Typical Application Schematic                                                                                                                                                     |   | 32  |

| 7. | Detailed Block Diagrams                                                                                                                                                           |   | 33  |

| 8. | Typical Operating Characteristics                                                                                                                                                 |   | 35  |

| 9. | Pin Descriptions                                                                                                                                                                  |   | 37  |

| 10. | . Pac | ckage C  | outline | es  | •   | •  | •  | •  | •   | •  | •   | •   | •  | •  | • | • | • | • | • | • | • | • | • | • |  | • | • | • | • | • | 42  |

|-----|-------|----------|---------|-----|-----|----|----|----|-----|----|-----|-----|----|----|---|---|---|---|---|---|---|---|---|---|--|---|---|---|---|---|-----|

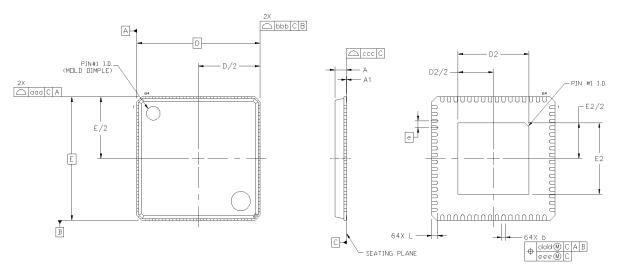

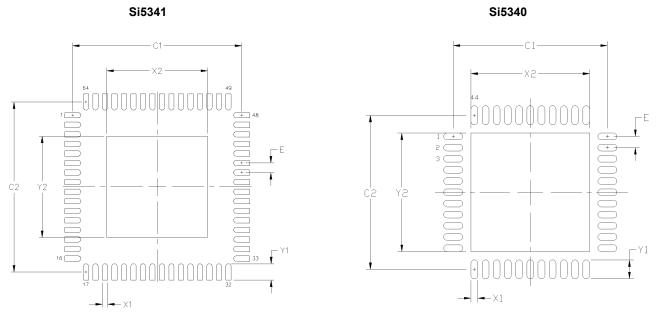

|     | 10.1  | Si5341   | 9x9 m   | m ( | 64- | QF | NI | Pa | cka | ge | Dia | agr | am | ۱. |   |   |   |   |   |   |   |   |   |   |  |   |   |   |   |   | .42 |

|     | 10.2  | Si5340   | 7x7 m   | m 4 | 44- | QF | N  | Pa | cka | ge | Dia | agr | am | ۱. |   |   |   |   |   |   |   |   |   |   |  |   | • |   | • |   | .43 |

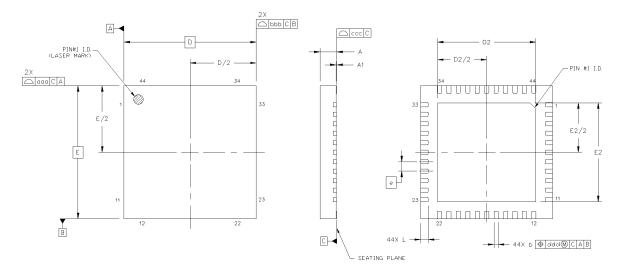

| 11. | PC    | B Land   | Patte   | rn  |     | •  |    | •  | •   |    |     |     | •  |    |   |   |   |   |   | • |   |   |   |   |  |   | • |   |   |   | 44  |

| 12. | . Top | o Markir | ng.     |     |     | •  |    | •  | •   |    |     |     | •  |    |   |   |   |   |   | • |   |   |   |   |  |   | • |   |   |   | 46  |

| 13. | . Dev | vice Err | ata .   |     | •   | •  |    |    | •   |    |     |     | •  | •  |   |   |   |   |   | • |   |   |   |   |  |   | • |   |   |   | 47  |

| 14. | . Rev | vision F | listory | y.  |     |    |    |    |     |    |     |     |    |    |   |   |   |   |   |   |   |   |   |   |  |   |   |   |   |   | 48  |

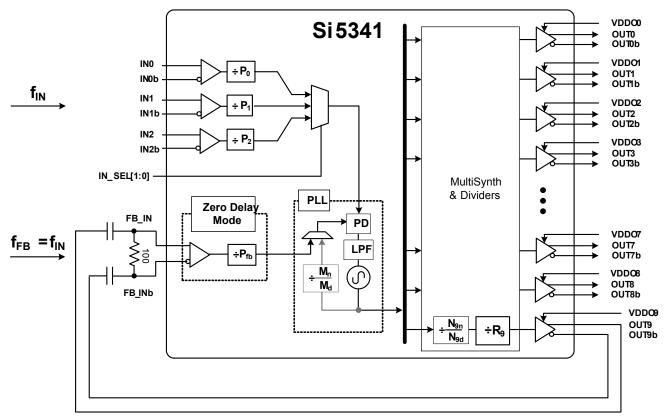

## 3. Functional Description

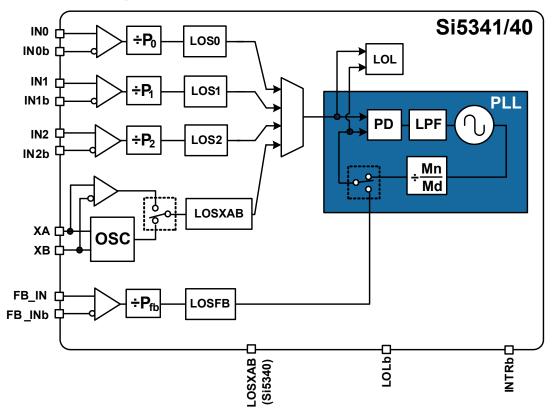

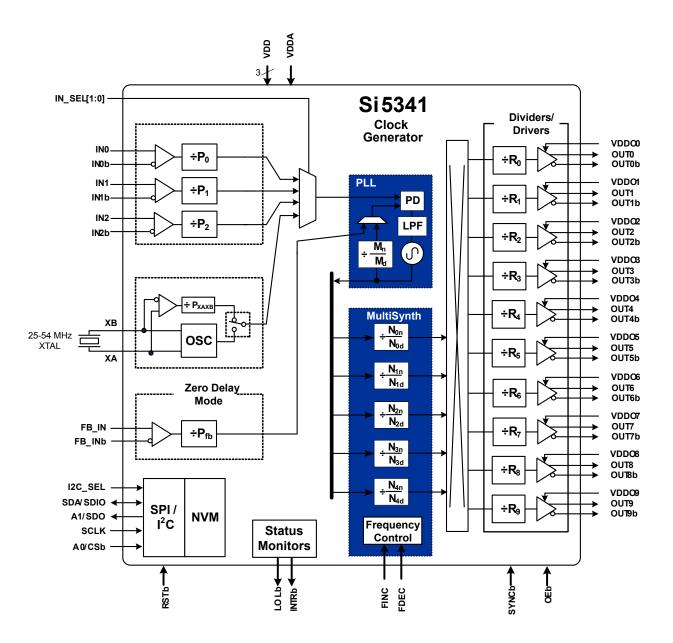

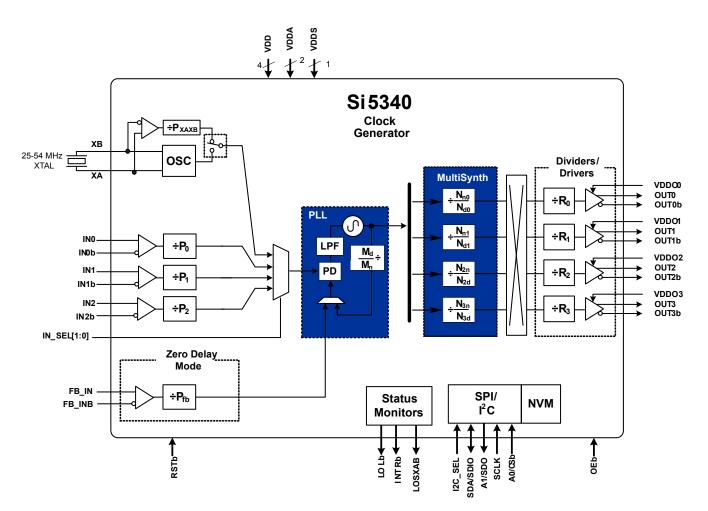

The Si5340/41-D combines a wide band PLL with next generation MultiSynth technology to offer the industry's most versatile and high performance clock generator. The PLL locks to either an external **crystal** between XA/XB or to an external **clock** connected to XA/XB or IN0, 1, 2. A fractional or integer multiplier takes the selected input clock or cystal frequency up to a very high frequency that is then divided by the MultiSynth output stage to any frequency in the range of 100 Hz to 1 GHz on each output. The MultiSynth stage can divide by both integer and fractional values. The high-resolution fractional MultiSynth dividers enable true any-frequency input to any-frequency on any of the outputs. The output drivers offer flexible output formats which are independently configurable on each of the outputs. This clock generator is fully configurable via its serial interface (I<sup>2</sup>C/SPI) and includes in-circuit programmable non-volatile memory.

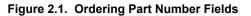

#### 3.1 Power-up and Initialization

Once power is applied, the device begins an initialization period where it downloads default register values and configuration data from NVM and performs other initialization tasks. Communicating with the device through the serial interface is possible once this initialization period is complete. No clocks will be generated until the initialization is done. There are two types of resets available. A hard reset is functionally similar to a device power-up. All registers will be restored to the values stored in NVM, and all circuits will be restored to their initial state including the serial interface. A hard reset is initiated using the RSTb pin or by asserting the hard reset bit. A soft reset bypasses the NVM download. It is simply used to initiate register configuration changes.

Figure 3.1. Si5341 Power-Up and Initialization

#### 3.2 Frequency Configuration

The phase-locked loop is fully contained and does not require external loop filter components to operate. Its function is to phase lock to the selected input and provide a common reference to the MultiSynth high-performance fractional dividers.

A crosspoint mux connects any of the MultiSynth divided frequencies to any of the outputs drivers. Additional output integer dividers provide further frequency division by an even integer from 2 to  $(2^{25})$ -2. The frequency configuration of the device is programmed by setting the input dividers (P), the PLL feedback fractional divider (Mn/Md), the MultiSynth fractional dividers (Nn/Nd), and the output integer dividers (R). Skyworks's ClockBuilder Pro configuration utility determines the optimum divider values for any desired input and output frequency plan.

#### 3.3 Inputs

The Si5340/41-D requires either an external crystal at its XA/XB pins or an external clock at XA/XB or IN0, 1, 2.

#### 3.3.1 XA/XB Clock and Crystal Input

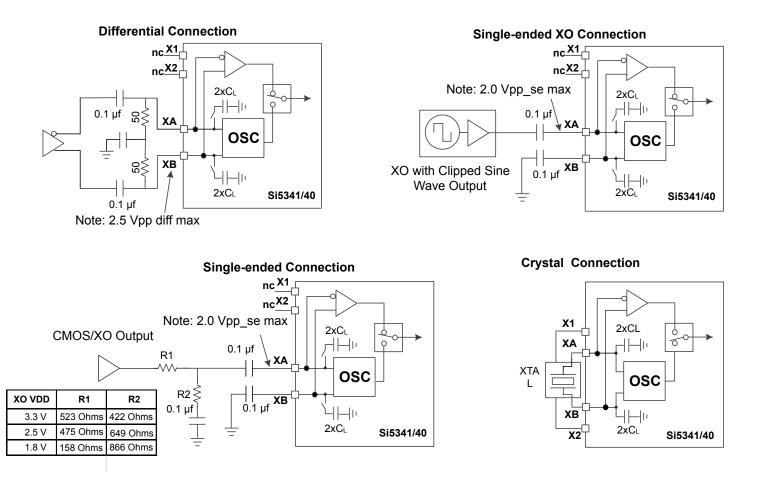

An internal crystal oscillator exists between pin XA and XB. When this oscillator is enabled, an external crystal connected across these pins will oscillate and provide a clock input to the PLL. A crystal frequency of 25 MHz can be used although crystals in the frequency range of 48 MHz to 54 MHz are recommended for best jitter performance. Frequency offsets due to  $C_L$  mismatch can be adjusted using the frequency adjustment feature which allows frequency adjustments of  $\pm$  1000 ppm. The Si5340/41 Family Reference Manual provides additional information on PCB layout recommendations for the crystal to ensure optimum jitter performance. Refer to Table 5.12 Crystal Specifications on page 30 for crystal specifications.

To achieve optimal jitter performance and minimize BOM cost, a crystal is recommended on the XA/XB reference input. A clock (e.g., XO) may be used in lieu of the crystal, but it will result in higher output jitter. See the Si5340/41 Reference Manual for more information.

Selection between the external XTAL or input clock is controlled by register configuration. The internal crystal load capacitors ( $C_L$ ) are disabled in the input clock mode. Refer to Table 5.3 Input Clock Specifications on page 19 for the input clock requirements at XAXB. Both a single-ended or a differential input clock can be connected to the XA/XB pins as shown in the figure below. A  $P_{XAXB}$  divider is available to accommodate external clock frequencies higher than 54 MHz.

Figure 3.2. XAXB External Crystal and Clock Connections

Note: See Table 5.3 Input Clock Specifications on page 19 for more information.

#### 3.3.2 Input Clocks (IN0, IN1, IN2)

A differential or single-ended clock can be applied at IN2, IN1, or IN0.

The recommended input termination schemes are can be found in Si5341/40 Rev D Family Reference Manual.

#### 3.3.3 Input Selection (IN0, IN1, IN2, XA/XB)

The active clock input is selected using the IN\_SEL[1:0] pins or by register control. A register bit determines input selection as pin or register selectable. There are internal pull ups on the IN\_SEL pins.

#### Table 3.1. Manual Input Selection Using IN\_SEL[1:0] Pins

| IN_SE | :L[1:0] | Selected Input |

|-------|---------|----------------|

| 0     | 0       | INO            |

| 0     | 1       | IN1            |

| 1     | 0       | IN2            |

| 1     | 1       | XA/XB          |

#### 3.4 Fault Monitoring

The Si5340/41-D provides fault indicators which monitor loss of signal (LOS) of the inputs (IN0, IN1, IN2, XA/XB, FB\_IN) and loss of lock (LOL) for the PLL as shown in the figure below.

Figure 3.3. LOS and LOL Fault Monitors

#### 3.4.1 Status Indicators

The state of the status monitors are accessible by reading registers through the serial interface or with dedicated pin (LOLb). Each of the status indicator register bits has a corresponding sticky bit in a separate register location. Once a status bit is asserted its corresponding sticky bit (\_FLG) will remain asserted until cleared. Writing a logic zero to a sticky register bit clears its state.

#### 3.4.2 Interrupt Pin (INTRb)

An interrupt pin (INTRb) indicates a change in state with any of the status registers. All status registers are maskable to prevent assertion of the interrupt pin. The state of the INTRb pin is reset by clearing the status registers.

#### 3.5 Outputs

The Si5341 supports 10 differential output drivers which can be independently configured as differential or LVCMOS. The Si5340 supports 4 output drivers independently configurable as differential or LVCMOS.

#### 3.5.1 Output Signal Format

The differential output amplitude and common mode voltage are both fully programmable and compatible with a wide variety of signal formats including LVDS and LVPECL. In addition to supporting differential signals, any of the outputs can be configured as LVCMOS (3.3 V, 2.5 V, or 1.8 V) drivers providing up to 20 single-ended outputs, or any combination of differential and single-ended outputs.

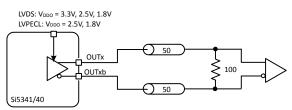

#### 3.5.2 Differential Output Terminations

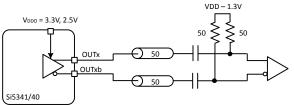

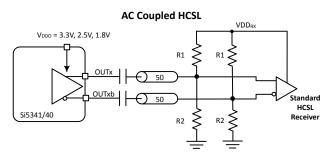

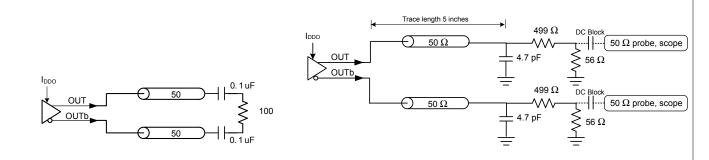

The differential output drivers support both ac-coupled and dc-coupled terminations as shown in the figure below.

#### DC Coupled LVDS/LVPECL

AC Coupled LVDS/LVPECL

#### AC Coupled LVPECL/CML

Figure 3.4. Supported Differential Output Terminations

**Note:** See the Si5341/40 Rev D Family Reference Manual for resistor values.

#### 3.5.3 Programmable Common Mode Voltage for Differential Outputs

The common mode voltage (VCM) for the differential modes are programmable so that LVDS specifications can be met and for the best signal integrity with different supply voltages. When dc coupling the output driver it is essential that the receiver should have a relatively high common mode impedance so that the common mode current from the output driver is very small.

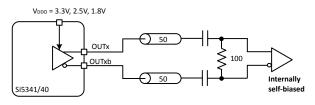

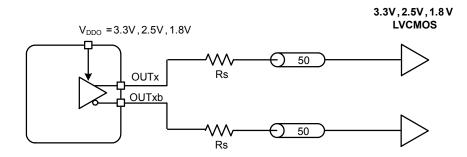

#### 3.5.4 LVCMOS Output Terminations

LVCMOS outputs are typically dc-coupled, as shown in the figure below.

## **DC Coupled LVCMOS**

Figure 3.5. LVCMOS Output Terminations

#### 3.5.5 LVCMOS Output Impedance and Drive Strength Selection

Each LVCMOS driver has a configurable output impedance. It is highly recommended that the minimum output impedance (strongest drive setting) is selected and a suitable series resistor (Rs) is chosen to match the trace impedance.

| VDDO  |                 | CMOS_DRIVE_Selection |                 |

|-------|-----------------|----------------------|-----------------|

|       | OUTx_CMOS_DRV=1 | OUTx_CMOS_DRV=2      | OUTx_CMOS_DRV=3 |

| 3.3 V | 38 Ω            | 30 Ω                 | 22 Ω            |

| 2.5 V | 43 Ω            | 35 Ω                 | 24 Ω            |

| 1 8 V | _               | 46.0                 | 31.0            |

#### Table 3.2. Nominal Output Impedance vs. OUTx\_CMOS\_DRV (register)

Note: Refer to the Si5340/41 Family Reference Manual for more information on register settings.

#### 3.5.6 LVCMOS Output Signal Swing

The signal swing (V<sub>OL</sub>/V<sub>OH</sub>) of the LVCMOS output drivers is set by the voltage on the VDDO pins. Each output driver has its own VDDO pin allowing a unique output voltage swing for each of the LVCMOS drivers.

## 3.5.7 LVCMOS Output Polarity

When a driver is configured as an LVCMOS output it generates a clock signal on both pins (OUTx and OUTxb). By default the clock on the OUTxb pin is generated with complementary polarity with the clock on the OUTx pin. The LVCMOS OUTx and OUTxb outputs can also be generated in phase.

#### 3.5.8 Output Enable/Disable

The OEb pin provides a convenient method of disabling or enabling the output drivers. When the OEb pin is held high all outputs will be disabled. When held low, the outputs will be enabled. Outputs in the enabled state can be individually disabled through register control.

## 3.5.9 Output Driver State When Disabled

The disabled state of an output driver is configurable as: disable low or disable high.

## 3.5.10 Synchronous/Asynchronous Output Disable Feature

Outputs can be configured to disable synchronously or asynchronously. The default state is synchronous output disable. In synchronous disable mode the output will wait until a clock period has completed before the driver is disabled. This prevents unwanted runt pulses from occurring when disabling an output. In asynchronous disable mode the output clock will disable immediately without waiting for the period to complete.

#### 3.5.11 Zero Delay Mode

A zero delay mode is available for applications that require fixed and consistent minimum delay between the selected input and outputs. The zero delay mode is configured by opening the internal feedback loop through software configuration and closing the loop externally as shown in the figure below. This helps to cancel out the internal delay introduced by the dividers, the crosspoint, the input, and the output drivers. Any one of the outputs can be fed back to the FB\_IN pins, although using the output driver that achieves the shortest trace length will help to minimize the input-to-output delay. It is recommended to connect OUT9 (Si5341) or OUT3 (Si5340) to FB\_IN for external feedback. The FB\_IN input pins must be terminated and ac-coupled when zero delay mode is used. A differential external feedback path connection is necessary for best performance.

**External Feedback Path**

Figure 3.6. Si5341 Zero Delay Mode Setup

#### 3.5.12 Output Crosspoint

The output crosspoint allows any of the N dividers to connect to any of the clock outputs.

#### 3.5.13 Digitally Controlled Oscillator (DCO) Modes

Each MultiSynth can be digitally controlled so that all outputs connected to the MultiSynth change frequency in real time without any transition glitches. There are two ways to control the MultiSynth to accomplish this task:

- Use the Frequency Increment/Decrement Pins or register bits.

- Write directly to the numerator of the MultiSynth divider.

An output that is controlled as a DCO is useful for simple tasks such as frequency margining or CPU speed control. The output can also be used for more sophisticated tasks such as FIFO management by adjusting the frequency of the read or write clock to the FIFO or using the output as a variable Local Oscillator in a radio application.

#### 3.5.13.1 DCO with Frequency Increment/Decrement Pins/Bits

Each of the MultiSynth fractional dividers can be independently stepped up or down in predefined steps with a resolution as low as 0.001 ppb. Setting of the step size and control of the frequency increment or decrement is accomplished by setting the step size with the 44 bit Frequency Step Word (FSTEPW). When the FINC or FDEC pin or register bit is asserted the output frequency will increment or decrement respectively by the amount specified in the FSTEPW.

#### 3.5.13.2 DCO with Direct Register Writes

When a MultiSynth numerator and its corresponding update bit is written, the new numerator value will take effect and the output frequency will change without any glitches. The MultiSynth numerator and denominator terms can be left and right shifted so that the least significant bit of the numerator word represents the exact step resolution that is needed for your application.

#### 3.6 Power Management

Several unused functions can be powered down to minimize power consumption. Consult the Si5340/41 Family Reference Manual and ClockBuilder Pro configuration utility for details.

#### 3.7 In-Circuit Programming

The Si5341/40 is fully configurable using the serial interface (I<sup>2</sup>C or SPI). At power-up the device downloads its default register values from internal non-volatile memory (NVM). Application specific default configurations can be written into NVM allowing the device to generate specific clock frequencies at power-up. Writing default values to NVM is in-circuit programmable with normal operating power supply voltages applied to its V<sub>DD</sub> and V<sub>DDA</sub> pins. The NVM is two time writable. Once a new configuration has been written to NVM, the old configuration is no longer accessible. Refer to the Si5340/41 Family Reference Manual for a detailed procedure for writing registers to NVM.

#### 3.8 Serial Interface

Configuration and operation of the Si5341/40 is controlled by reading and writing registers using the I<sup>2</sup>C or SPI interface. The I2C\_SEL pin selects I<sup>2</sup>C or SPI operation. Communication with both 3.3 V and 1.8 V host is supported. The SPI mode operates in either 4-wire or 3-wire. See the Si5340/41 Family Reference Manual for details.

#### 3.9 Custom Factory Preprogrammed Devices

For applications where a serial interface is not available for programming the device, custom pre-programmed parts can be ordered with a specific configuration written into NVM. A factory pre-programmed device will generate clocks at power-up. Custom, factory-pre-programmed devices are available. Use the ClockBuilder Pro custom part number wizard (https://www.skyworksinc.com/en/application-pages/clockbuilder-pro-software) to quickly and easily request and generate a custom part number for your configuration. In less than three minutes, you will be able to generate a custom part number with a detailed data sheet addendum matching your design's configuration. Once you receive the confirmation email with the data sheet addendum, simply place an order with your local Skyworks sales representative. Samples of your pre-programmed device will ship to you typically within two weeks.

#### 3.10 Enabling Features and/or Configuration Settings Not Available in ClockBuilder Pro for Factory Pre-Programmed Devices

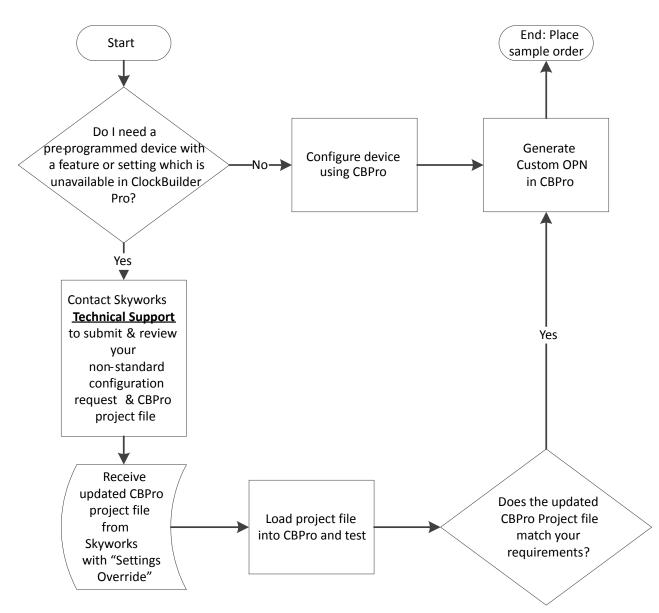

As with essentially all software utilities, ClockBuilder Pro is continuously updated and enhanced. By registering at https://www.skyworksinc.com/ and opting in for updates to software, you will be notified whenever changes are made and what the impact of those changes are. This update process will ultimately enable ClockBuilder Pro users to access all features and register setting values documented in this data sheet and the Si5341/40 Family Reference Manual. However, if you must enable or access a feature or register setting value so that the device starts up with this feature or a register setting, but the feature or register setting is NOT yet available in CBPro, you must contact a Skyworks applications engineer for assistance. An example of this type of feature or custom setting is the customizable amplitudes for the clock outputs. After careful review of your project file and custom requirements, a Skyworks applications engineer will email back your CBPro project file with your specific features and register settings enabled, using what is referred to as the manual "settings override" feature of CBPro. "Override" settings to match your request(s) will be listed in your design report file. Examples of setting "overrides" in a CBPro design report are shown below:

#### Table 3.3. Setting Overrides

| Location  | Name      | Туре | Target    | Dec Value | Hex Value |

|-----------|-----------|------|-----------|-----------|-----------|

| 0128[6:4] | OUT6_AMPL | User | OPN & EVB | 5         | 5         |

Once you receive the updated design file, simply open it in CBPro. After you create a custom OPN, the device will begin operation after startup with the values in the NVM file, including the Skyworks-supplied override settings.

Si5341/40 Rev D Data Sheet • Functional Description

Figure 3.7. Flowchart to Order Custom Parts with Features not Available in CBPro

Note: Contact Skyworks Technical Support at https://www.skyworksinc.com/en/Support.

Si5341/40 Rev D Data Sheet • Register Map

## 4. Register Map

Refer to the Si5340/41 Family Reference Manual for a complete list of register descriptions and settings.

## 5. Electrical Specifications

## Table 5.1. Recommended Operating Conditions<sup>1</sup>

$(V_{DD}=1.8 V \pm 5\%, V_{DDA}=3.3 V \pm 5\%, T_{A}=-40 \text{ to } 85^{\circ}\text{C})$

| Parameter                    | Symbol            | Min  | Тур  | Мах  | Units |

|------------------------------|-------------------|------|------|------|-------|

| Ambient Temperature          | T <sub>A</sub>    | -40  | 25   | 85   | °C    |

| Junction Temperature         | TJ <sub>MAX</sub> | _    | _    | 125  | °C    |

| Core Supply Voltage          | V <sub>DD</sub>   | 1.71 | 1.80 | 1.89 | V     |

|                              | V <sub>DDA</sub>  | 3.14 | 3.30 | 3.47 | V     |

| Output Driver Supply Voltage | V <sub>DDO</sub>  | 3.14 | 3.30 | 3.47 | V     |

|                              |                   | 2.37 | 2.50 | 2.62 | V     |

|                              |                   | 1.71 | 1.80 | 1.89 | V     |

Note:

1. All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise noted.

#### Table 5.2. DC Characteristics

$(V_{DD}=1.8V \pm 5\%, V_{DDA}=3.3V \pm 5\%, V_{DDO}=1.8V \pm 5\%, 2.5V \pm 5\%, or 3.3V \pm 5\%, T_{A}= -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                               | Symbol            | Test Condition                   | Min | Тур | Max  | Units |

|-----------------------------------------|-------------------|----------------------------------|-----|-----|------|-------|

| Core Supply Current <sup>1, 2</sup>     | I <sub>DD</sub>   | Si5340/41                        | —   | 115 | 230  | mA    |

|                                         | I <sub>DDA</sub>  | Si5340/41                        |     | 120 | 130  | mA    |

| Output Buffer Supply Current            | I <sub>DDOx</sub> | LVPECL Output <sup>3</sup>       | —   | 22  | 26   | mA    |

|                                         |                   | @ 156.25 MHz                     |     |     |      |       |

|                                         |                   | LVDS Output <sup>3</sup>         |     | 15  | 18   | mA    |

|                                         |                   | @ 156.25 MHz                     |     |     |      |       |

|                                         |                   | 3.3 V LVCMOS <sup>4</sup> output | _   | 22  | 30   | mA    |

|                                         |                   | @ 156.25 MHz                     |     |     |      |       |

|                                         |                   | 2.5 V LVCMOS <sup>4</sup> output | —   | 18  | 23   | mA    |

|                                         |                   | @ 156.25 MHz                     |     |     |      |       |

|                                         |                   | 1.8 V LVCMOS <sup>4</sup> output | —   | 12  | 16   | mA    |

|                                         |                   | @ 156.25 MHz                     |     |     |      |       |

| Total Power Dissipation <sup>1, 5</sup> | Pd                | Si5341                           |     | 880 | 1150 | mW    |

|                                         |                   | Si5340                           | _   | 680 | 875  | mW    |

## Note:

1. Si5341 test configuration: 7 x 2.5 V LVDS outputs enabled @ 156.25 MHz. Excludes power in termination resistors.

2. Si5340 test configuration: 4 x 2.5 V LVDS outputs enabled @ 156.25 MHz. Excludes power in termination resistors.

3. Differential outputs terminated into an ac-coupled 100  $\Omega$  load.

4. LVCMOS outputs measured into a 6-inch 50 W PCB trace with 5 pF load. The LVCMOS outputs were set to OUTx\_CMOS\_DRV=3, which is the strongest driver setting. Refer to the Si5341/40 Family Reference Manual for more details on register settings.

## **Differential Output Test Configuration**

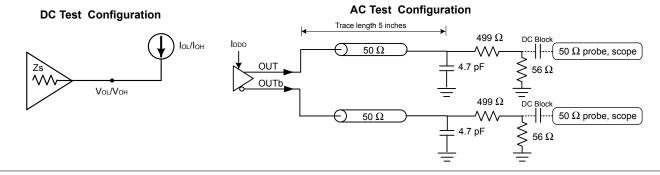

## LVCMOS Output Test Configuration

5. Detailed power consumption for any configuration can be estimated using ClockBuilderPro when an evaluation board (EVB) is not available. All EVBs support detailed current measurements for any configuration.

## Table 5.3. Input Clock Specifications

## (V<sub>DD</sub> =1.8 V ± 5%, V<sub>DDA</sub> = 3.3 V ± 5%, T<sub>A</sub>= -40 to 85 °C)

| Parameter                           | Symbol               | Test Condition                                                   | Min                        | Тур           | Max         | Units     |

|-------------------------------------|----------------------|------------------------------------------------------------------|----------------------------|---------------|-------------|-----------|

| Standard Input Buffer with Diff     | erential or Sing     | le-Ended - AC-Coupled (IN0                                       | /IN0b, IN1/IN <sup>,</sup> | 1b, IN2/IN2b, | FB_IN/FB_IN | <b>)</b>  |

| Input Frequency Range               | f <sub>IN</sub>      | Differential                                                     | 10                         |               | 750         | MHz       |

|                                     |                      | All Single-ended Signals                                         | 10                         | _             | 250         | MHz       |

|                                     |                      | (including LVCMOS)                                               |                            |               |             |           |

| Input Voltage Swing <sup>1</sup>    | V <sub>IN</sub>      | Differential AC-coupled                                          | 100                        | _             | 1800        | mVpp_se   |

|                                     |                      | f <sub>IN</sub> < 250 MHz                                        |                            |               |             |           |

|                                     |                      | Differential AC-coupled                                          | 225                        | _             | 1800        | mVpp_se   |

|                                     |                      | 250 MHz < f <sub>IN</sub> < 750 MHz                              |                            |               |             |           |

|                                     |                      | Single-ended AC-coupled                                          | 100                        | _             | 3600        | mVpp_se   |

|                                     |                      | f <sub>IN</sub> < 250 MHz                                        |                            |               |             |           |

| Slew Rate <sup>2, 3</sup>           | SR                   |                                                                  | 400                        | _             | -           | V/µs      |

| Input Capacitance                   | C <sub>IN</sub>      |                                                                  | _                          | 2.4           | _           | pF        |

| Input Resistance Differential       | R <sub>IN_DIFF</sub> |                                                                  | _                          | 16            | _           | kΩ        |

| Input Resistance Single-Ended       | R <sub>IN_SE</sub>   |                                                                  | _                          | 8             | _           | kΩ        |

| Pulsed CMOS Input Buffer - DC       | Coupled (IN0,        | IN1, IN2)                                                        |                            |               | 1           | 1         |

| Input Frequency                     | f <sub>IN</sub>      |                                                                  | 10                         |               | 250         | MHz       |

| Input Voltage                       | V <sub>IL</sub>      |                                                                  | -0.2                       | _             | 0.4         | V         |

|                                     | VIH                  |                                                                  | 0.8                        |               | _           | V         |

| Slew Rate <sup>2, 3</sup>           | SR                   |                                                                  | 400                        |               | _           | V/µs      |

| Minimum Pulse Width                 | PW                   | Pulse Input                                                      | 1.6                        |               | _           | ns        |

| Input Resistance                    | R <sub>IN</sub>      |                                                                  | _                          | 8             | _           | kΩ        |

| REFCLK (Applied to XA/XB)           | 1                    |                                                                  |                            | 1             | 1           |           |

| Input Frequency Range               | f <sub>IN</sub>      | Full operating range. Jit-<br>ter performance may be<br>reduced. | 10                         | _             | 200         | MHz       |

|                                     |                      | Range for best jitter.                                           | 48                         |               | 54          | MHz       |

| Input Single-ended Voltage<br>Swing | V <sub>IN_SE</sub>   |                                                                  | 365                        | _             | 2000        | mVpp_se   |

| Input Differential Voltage Swing    | V <sub>IN_DIFF</sub> |                                                                  | 365                        | _             | 2500        | mVpp_diff |

| Slew Rate <sup>2, 3</sup>           | SR                   | Imposed for best jitter per-<br>formance                         | 400                        | _             | _           | V/µs      |

| Input Duty Cycle                    | DC                   |                                                                  | 40                         | _             | 60          | %         |

Si5341/40 Rev D Data Sheet • Electrical Specifications

| Parameter                                                   | Symbol         | Test Condition                            | Min             | Тур           | Мах                   | Units        |

|-------------------------------------------------------------|----------------|-------------------------------------------|-----------------|---------------|-----------------------|--------------|

| Note:                                                       |                |                                           |                 |               |                       |              |

| 1. Voltage swing is specified as                            | single-ended m | Vcm + + + + + + + + + + + + + + + + + + + |                 |               | <br>Vpp_diff = 2*<br> | ℃Vpp_se      |

| 2. Recommended for specified<br>(see the Family Reference M |                | e. Jitter performance can de              | grade if the mi | nimum slew ra | te specification      | n is not met |

3. Pulsed CMOS mode is intended primarily for single-ended LVCMOS input clocks < 1 MHz, which must be dc-coupled because they have a duty cycle significantly less than 50%. A typical application example is a low frequency video frame sync pulse. Since the input thresholds (V<sub>IL</sub>, V<sub>IH</sub>) of this buffer are non-standard (0.4 and 0.8 V, respectively), refer to the input attenuator circuit for DC-coupled Pulsed LVCMOS in the Family Reference Manual. Otherwise, for standard LVCMOS input clocks, use the Standard AC-Coupled, Single-ended input mode.

## Table 5.4. Control Input Pin Specifications

$(V_{DD} = 1.8 \text{ V} \pm 5\%, V_{DDA} = 3.3 \text{ V} \pm 5\%, V_{DDIO} = 3.3 \text{ V} \pm 5\%, 1.8 \text{ V} \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                      | Symbol          | Test Condition              | Min                                | Тур          | Мах                                | Units |

|--------------------------------|-----------------|-----------------------------|------------------------------------|--------------|------------------------------------|-------|

| Si5341 Control Input Pins (I2C | SEL, IN_SEL[1   | :0], RSTb, OEb, SYNCb, A1   | , SCLK, A0/CS                      | 6b, FINC, FD | EC, SDA/SDIO)                      |       |

| Input Voltage                  | V <sub>IL</sub> |                             | —                                  | —            | 0.3xV <sub>DDIO</sub> <sup>1</sup> | V     |

|                                | V <sub>IH</sub> |                             | 0.7xV <sub>DDIO</sub> <sup>1</sup> | _            | _                                  | V     |

| Input Capacitance              | C <sub>IN</sub> |                             | _                                  | 2            | -                                  | pF    |

| Input Resistance               | R <sub>IN</sub> |                             | —                                  | 20           | _                                  | kΩ    |

| Minimum Pulse Width            | T <sub>PW</sub> | RSTb, SYNCb, FINC, and FDEC | 100                                | _            | _                                  | ns    |

| Frequency Update Rate          | F <sub>UR</sub> | FINC and FDEC               | —                                  | _            | 1                                  | MHz   |

| Si5340 Control Input Pins (I2C | SEL, IN_SEL[1   | :0], RSTb, OEb, A1, SCLK, A | A0/CSb, SDA/                       | SDIO)        | 1 1                                |       |

| Input Voltage                  | V <sub>IL</sub> |                             | _                                  | _            | 0.3xV <sub>DDIO</sub> <sup>1</sup> | V     |

|                                | V <sub>IH</sub> |                             | 0.7xV <sub>DDIO</sub> 1            | _            | _                                  | V     |

| Input Capacitance              | C <sub>IN</sub> |                             | —                                  | 2            | _                                  | pF    |

| Input Resistance               | R <sub>IN</sub> |                             | —                                  | 20           | _                                  | kΩ    |

| Minimum Pulse Width            | T <sub>PW</sub> | RSTb only                   | 100                                |              |                                    | ns    |

#### Note:

1. V<sub>DDIO</sub> is determined by the IO\_VDD\_SEL bit. It is selectable as V<sub>DDA</sub> or V<sub>DD</sub>. Refer to the Family Reference Manual for more details on register settings.

## Table 5.5. Differential Clock Output Specifications

$(V_{DD}=1.8 V \pm 5\%, V_{DDA}=3.3 V \pm 5\%, V_{DDO}=1.8 V \pm 5\%, 2.5 V \pm 5\%, or 3.3 V \pm 5\%, T_{A}=-40 \text{ to } 85 \text{ °C})$

| Parameter                                   | Symbol                         | Test Con                       | dition       | Min    | Тур  | Max    | Units   |

|---------------------------------------------|--------------------------------|--------------------------------|--------------|--------|------|--------|---------|

| Output Frequency                            | f <sub>OUT</sub>               | MultiSynth                     | not used     | 0.0001 | _    | 720    | MHz     |

|                                             |                                |                                | -            | 733.33 |      | 800.00 | -       |

|                                             |                                |                                | -            | 825    |      | 1028   | -       |

|                                             |                                | MultiSynt                      | h used       | 0.0001 |      | 720    | MHz     |

| Duty Cycle                                  | DC                             | f <sub>OUT</sub> < 40          | 0 MHz        | 48     | _    | 52     | %       |

|                                             |                                | 400 MHz < f <sub>OUT</sub>     | - < 1028 MHz | 45     |      | 55     | %       |

| Output-Output Skew<br>Using Same MultiSynth | T <sub>SKS</sub>               | Outputs on sam<br>(Measured at |              | _      | 0    | 75     | ps      |

| OUT-OUTb Skew                               | T <sub>SK_OUT</sub>            | Measured from<br>to negative o |              | _      | 0    | 50     | ps      |

| Output Voltage Swing <sup>1</sup>           | V <sub>OUT</sub>               | LVD                            | S            | 350    | 430  | 510    | mVpp_se |

|                                             |                                | LVPE                           | CL           | 640    | 750  | 900    | _       |

| Common Mode Voltage <sup>1, 2</sup>         | V <sub>CM</sub>                | V <sub>DDO</sub> = 3.3 V       | LVDS         | 1.1    | 1.2  | 1.3    | V       |

|                                             |                                |                                | LVPECL       | 1.9    | 2.0  | 2.1    |         |

|                                             |                                | V <sub>DDO</sub> = 2.5 V       | LVPECL       | 1.1    | 1.2  | 1.3    | -       |

|                                             |                                |                                | LVDS         |        |      |        |         |

|                                             |                                | V <sub>DDO</sub> = 1.8 V       | Sub-LVDS     | 0.8    | 0.9  | 1.0    |         |

| Rise and Fall Times<br>(20% to 80%)         | t <sub>R</sub> /t <sub>F</sub> |                                |              | _      | 100  | 150    | ps      |

| Differential Output Impedance               | ZO                             |                                |              | _      | 100  | _      | Ω       |

| Power Supply Noise Rejection <sup>2</sup>   | PSRR                           | 10 kHz sinus                   | oidal noise  |        | -101 | _      | dBc     |

|                                             |                                | 100 kHz sinus                  | oidal noise  | _      | -96  | _      | -       |

|                                             |                                | 500 kHz sinus                  | oidal noise  | _      | -99  | _      | -       |

|                                             |                                | 1 MHz sinuso                   | oidal noise  | _      | -97  | _      | 1       |

| Output-Output Crosstalk <sup>3</sup>        | XTALK                          | Si534                          | 41           | _      | -72  | -      | dBc     |

|                                             |                                | Si534                          | 40           | _      | -88  | _      | dBc     |

Si5341/40 Rev D Data Sheet • Electrical Specifications

guidance on crosstalk minimization.

| Parameter                                        | Symbol                                | Test Condition                                                                                                                 | Min                           | Тур                              | Мах                   | Units  |

|--------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------|-----------------------|--------|

| Notes:                                           |                                       |                                                                                                                                |                               |                                  |                       |        |

| NVM. Each output driver up to 110 mV higher than | can be programme<br>the TIA/EIA-644 m | is are programmable through re<br>d independently. The maximun<br>aximum. Refer to the Family R<br>oltage amplitude and common | n LVDS single<br>eference Man | -ended ampliti<br>ual for more s | ude can be<br>sugges- |        |

| OUTx Vcm<br>OUTxb Vcm                            | Vpp_se                                | Vpp_diff=2*                                                                                                                    | Vpp_se                        |                                  |                       |        |

| 2. Measured for 156.25 MH measured.              | z carrier frequency.                  | 100 mVpp sinewave noise add                                                                                                    | ded to VDDO                   | = 3.3 V and no                   | oise spur ampl        | litude |

| -                                                | •                                     | in LVDS mode, with the victim mizing Si534x Jitter Performan                                                                   | •                             |                                  |                       |        |

## Table 5.6. LVCMOS Clock Output Specifications

(V\_{DD} =1.8 V ± 5%, V\_{DDA}= 3.3 V ± 5%, V\_{DDO}= 1.8 V ± 5%, 2.5 V ± 5%, or 3.3 V ± 5%, T\_A = -40 to 85 °C)

| Parameter                              | Symbol          | Test Conditi                 | ion                      | Min                     | Тур | Max | Units |

|----------------------------------------|-----------------|------------------------------|--------------------------|-------------------------|-----|-----|-------|

| Output Frequency                       |                 |                              |                          | 0.0001                  | _   | 250 | MHz   |

| Duty Cycle                             | DC              | f <sub>OUT</sub> < 100 N     | lHz                      | 48                      | _   | 52  | %     |

|                                        |                 | 100 MHz < f <sub>OUT</sub> < | 250 MHz                  | 45                      | _   | 55  |       |

| Output Voltage High <sup>1, 2, 3</sup> | V <sub>OH</sub> | V <sub>DDO</sub> = 3.3 V     |                          | 1                       |     |     |       |

|                                        |                 | OUTx_CMOS_DRV=1              | I <sub>OH =</sub> -10 mA | V <sub>DDO</sub> x 0.85 | _   | _   | V     |

|                                        |                 | OUTx_CMOS_DRV=2              | I <sub>OH =</sub> -12 mA |                         | _   | _   |       |

|                                        |                 | OUTx_CMOS_DRV=3              | I <sub>OH =</sub> -17 mA |                         | _   | _   |       |

|                                        |                 | V <sub>DDO</sub> = 2.5 V     |                          |                         |     |     |       |

|                                        |                 | OUTx_CMOS_DRV=1              | I <sub>OH =</sub> -6 mA  | V <sub>DDO</sub> x 0.85 | _   | _   | V     |

|                                        |                 | OUTx_CMOS_DRV=2              | I <sub>OH =</sub> -8 mA  |                         | _   | _   |       |

|                                        |                 | OUTx_CMOS_DRV=3              | I <sub>OH =</sub> -11 mA |                         |     | _   |       |

|                                        |                 | V <sub>DDO</sub> = 1.8 V     |                          |                         |     |     | -     |

|                                        |                 | OUTx_CMOS_DRV=2              | I <sub>OH =</sub> -4 mA  | V <sub>DDO</sub> x 0.85 | _   | _   | V     |

|                                        |                 | OUTx_CMOS_DRV=3              | I <sub>OH =</sub> -5 mA  |                         | _   | _   |       |

| Parameter                             | Symbol          | Test Conditi             | on                      | Min | Тур | Max                     | Units |

|---------------------------------------|-----------------|--------------------------|-------------------------|-----|-----|-------------------------|-------|

| Output Voltage Low <sup>1, 2, 3</sup> | V <sub>OL</sub> | V <sub>DDO</sub> = 3.3 V |                         |     |     |                         |       |

|                                       |                 | OUTx_CMOS_DRV=1          | I <sub>OL</sub> = 10 mA |     | _   | V <sub>DDO</sub> x 0.15 | V     |

|                                       |                 | OUTx_CMOS_DRV=2          | I <sub>OL</sub> = 12 mA |     | _   | -                       |       |

|                                       |                 | OUTx_CMOS_DRV=3          | I <sub>OL</sub> = 17 mA |     | _   |                         |       |

|                                       |                 | V <sub>DDO</sub> = 2.5 V |                         | 1   |     |                         | I     |

|                                       |                 | OUTx_CMOS_DRV=1          | I <sub>OL</sub> = 6 mA  |     | _   | V <sub>DDO</sub> x 0.15 | V     |

|                                       |                 | OUTx_CMOS_DRV=2          | I <sub>OL</sub> = 8 mA  |     | _   | -                       |       |

|                                       |                 | OUTx_CMOS_DRV=3          | I <sub>OL</sub> = 11 mA |     | _   |                         |       |

|                                       |                 | V <sub>DDO</sub> = 1.8 V |                         | I   |     |                         | 1     |

|                                       |                 | OUTx_CMOS_DRV=2          | I <sub>OL</sub> = 4 mA  |     | _   | V <sub>DDO</sub> x 0.15 | V     |

|                                       |                 | OUTx_CMOS_DRV=3          | I <sub>OL</sub> = 5 mA  |     | _   |                         |       |

| LVCMOS Rise and Fall                  | tr/tf           | VDDO = 3.3               | 3V                      |     | 400 | 600                     | ps    |

| Times <sup>3</sup>                    |                 | VDDO = 2.5               | V                       | —   | 450 | 600                     | ps    |

| (20% to 80%)                          |                 | VDDO = 1.8               | V                       | _   | 550 | 750                     | ps    |

#### Notes:

1. Driver strength is a register programmable setting and stored in NVM. Options are OUTx\_CMOS\_DRV = 1, 2, 3. Refer to the Family Reference Manual for more details on register settings.

2.  $I_{OL}/I_{OH}$  is measured at  $V_{OL}/V_{OH}$  as shown in the dc test configuration.

3. A series termination resistor (Rs) is recommended to help match the source impedance to a 50 W PCB trace. A 5 pF capacitive load is assumed. The LVCMOS outputs were set to OUTx\_CMOS\_DRV = 3.

#### Table 5.7. Output Status Pin Specifications

## $(V_{DD} = 1.8 \text{ V} \pm 5\%, V_{DDA} = 3.3 \text{ V} \pm 5\%, V_{DDIO}/V_{DDS} = 3.3 \text{ V} + -5\%, 1.8 \text{ V} \pm 5\%, T_A = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                 | Symbol               | Test Condition          | Min                                      | Тур | Max                                      | Units |

|---------------------------|----------------------|-------------------------|------------------------------------------|-----|------------------------------------------|-------|

| Si5341/40 Status Output P | ins (INTRb, SDA/SDIC | ) <sup>1</sup>          |                                          |     |                                          |       |

| Output Voltage            | V <sub>OH</sub>      | I <sub>OH</sub> = -2 mA | V <sub>DDIO</sub> <sup>2</sup> x<br>0.85 | —   | -                                        | V     |

|                           | V <sub>OL</sub>      | I <sub>OL</sub> = 2 mA  | -                                        | _   | V <sub>DDIO</sub> <sup>2</sup> x<br>0.15 | V     |

| Si5341 Status Output Pins | (LOLb)               |                         |                                          |     |                                          |       |

| Output Voltage            | V <sub>OH</sub>      | I <sub>OH</sub> = -2 mA | V <sub>DDIO</sub> <sup>2</sup> x<br>0.85 | —   | —                                        | V     |

|                           | V <sub>OL</sub>      | I <sub>OL</sub> = 2 mA  | -                                        | —   | V <sub>DDIO</sub> <sup>2</sup> x<br>0.15 | V     |

| Si5340 Status Output Pins | (LOLb, LOS_XAXBb)    | 1                       |                                          |     |                                          |       |

| Output Voltage            | V <sub>OH</sub>      | I <sub>OH</sub> = -2 mA | V <sub>DDS</sub> x 0.85                  | _   | _                                        | V     |

|                           | V <sub>OL</sub>      | I <sub>OL</sub> = 2 mA  | _                                        |     | V <sub>DDS</sub> x 0.15                  | V     |

with I2C\_SEL pulled high. V<sub>OL</sub> remains valid in all cases.

2. V<sub>DDIO</sub> is determined by the IO\_VDD\_SEL bit. It is selectable as V<sub>DDA</sub> or V<sub>DD</sub>. Refer to the Family Reference Manual for more details on register settings.

#### Table 5.8. Performance Characteristics

## (V<sub>DD</sub>= 1.8 V ± 5%, V<sub>DDA</sub>= 3.3 V ± 5%, T<sub>A</sub>= –40 to 85 °C)

| Parameter                                  | Symbol             | Test Condition                                                                                | Min | Тур | Max | Units |

|--------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| PLL Loop Bandwidth                         | f <sub>BW</sub>    |                                                                                               | _   | 1.0 | _   | MHz   |

| Initial Start-Up Time                      | t <sub>START</sub> | Time from power-up to<br>when the device gener-<br>ates clocks (Input Fre-<br>quency >48 MHz) | _   | 30  | 45  | ms    |

| PLL Lock Time <sup>1</sup>                 | t <sub>ACQ</sub>   | f <sub>IN</sub> = 19.44 MHz                                                                   | 15  |     | 150 | ms    |

| POR <sup>2</sup> to Serial Interface Ready | t <sub>RDY</sub>   |                                                                                               | _   | _   | 15  | ms    |

| Parameter                       | Symbol           | Test Condition                                                                                                                                   | Min | Тур  | Мах | Units    |  |  |

|---------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|----------|--|--|

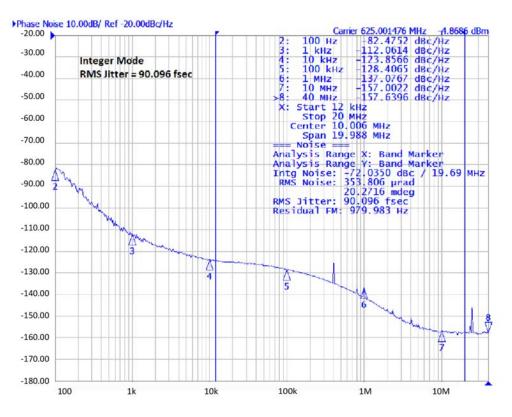

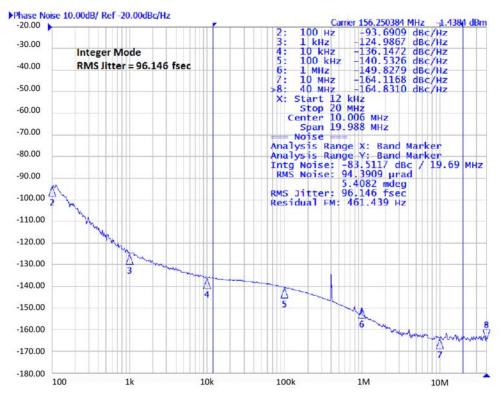

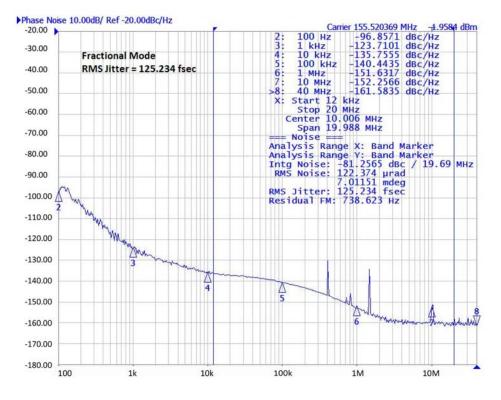

| Jitter Generation Locked to Ex- | J <sub>GEN</sub> | Integer Mode <sup>4</sup>                                                                                                                        | _   | 140  | 180 | fs rms   |  |  |

| ternal Clock <sup>3</sup>       |                  | 12 kHz to 20 MHz                                                                                                                                 |     |      |     |          |  |  |

|                                 |                  | Fractional/DCO Mode <sup>5</sup>                                                                                                                 | _   | 160  | 210 | fs rms   |  |  |

|                                 |                  | 12 kHz to 20 MHz                                                                                                                                 |     |      |     |          |  |  |

|                                 | J <sub>PER</sub> | Derived from integrated                                                                                                                          | _   | 110  | _   | fs rms   |  |  |

|                                 | J <sub>CC</sub>  | - phase noise -                                                                                                                                  | _   | 180  | _   | fs rms   |  |  |

|                                 | J <sub>PER</sub> | N = 10,000 cycles Integer                                                                                                                        | _   | 4710 |     | fs pk-pk |  |  |

|                                 | J <sub>CC</sub>  | or Fractional Mode <sup>4, 5</sup> .<br>Measured in the time do-<br>main. Performance is limi-<br>ted by the noise floor of<br>the equipment.    | _   | 4000 | _   | fs pk    |  |  |

| Jitter Generation Locked to Ex- | XTAL Frequen     | FAL Frequency = 48 MHz                                                                                                                           |     |      |     |          |  |  |

| ernal XTAL                      | J <sub>GEN</sub> | Integer Mode <sup>4</sup>                                                                                                                        | _   | 90   | 140 | fs rms   |  |  |

|                                 | -                | 12 kHz to 20 MHz                                                                                                                                 |     |      |     |          |  |  |

|                                 |                  | Fractional/DCO Mode <sup>5</sup>                                                                                                                 | _   | 115  | 170 | fs rms   |  |  |

|                                 |                  | 12 kHz to 20 MHz                                                                                                                                 |     |      |     |          |  |  |

|                                 | J <sub>PER</sub> | Derived from integrated                                                                                                                          | _   | 110  | —   | fs rms   |  |  |

|                                 | J <sub>CC</sub>  | - phase noise -                                                                                                                                  | _   | 180  | _   | fs rms   |  |  |

|                                 | J <sub>PER</sub> | N = 10, 000 cycles Inte-                                                                                                                         | _   | 5080 |     | fs pk-pk |  |  |

|                                 | J <sub>CC</sub>  | ger or Fractional Mode. <sup>4, 5</sup><br>Measured in the time do-<br>main. Performance is limi-<br>ted by the noise floor of<br>the equipment. | _   | 4340 | _   | fs pk    |  |  |

|                                 | XTAL Frequen     | cy = 25 MHz                                                                                                                                      |     |      |     |          |  |  |

|                                 | J <sub>GEN</sub> | Integer Mode <sup>4</sup>                                                                                                                        |     | 115  | 140 | fs rms   |  |  |

|                                 |                  | 12 kHz to 20 MHz                                                                                                                                 |     |      |     |          |  |  |

|                                 |                  | Fractional Mode <sup>5</sup>                                                                                                                     |     | 140  | 190 | fs rms   |  |  |

|                                 |                  | 12 kHz to 20 MHz                                                                                                                                 |     |      |     |          |  |  |

## Notes:

1. PLL lock time is measured by first letting the PLL lock, then turning off the input clock, and then turning on the input clock. The time from the first edge of the input clock being re-applied until LOL de-asserts is the PLL lock time.

2. Measured as time from valid V<sub>DD</sub> and V<sub>DD33</sub> rails (90% of their value) to when the serial interface is ready to respond to commands. Measured in SPI 4-wire mode, with SCLK @ 10 MHz.

3. Jitter generation test conditions  $f_{IN}$  = 100 MHz,  $f_{OUT}$  = 156.25 MHz LVPECL.

4. Integer mode assumes that the output dividers (Nn/Nd) are configured with an integer value.

5. Fractional and DCO modes assume that the output dividers (Nn/Nd) are configured with a fractional value and the feedback divider is integer.

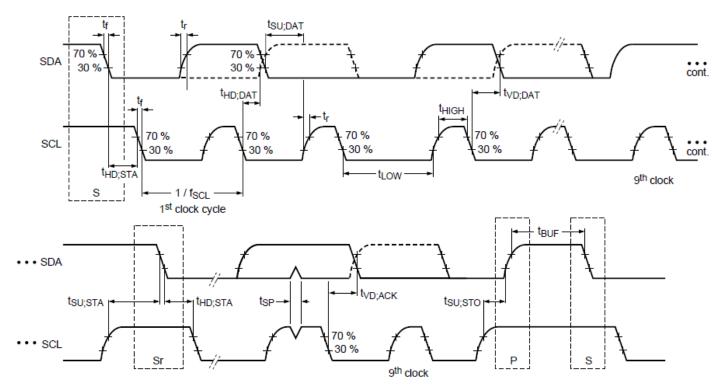

| Parameter                                        | Symbol              | Test Condition | Standard Mode<br>100 kbps |      | Fast Mode<br>400 kbps |     | Units |

|--------------------------------------------------|---------------------|----------------|---------------------------|------|-----------------------|-----|-------|

|                                                  |                     |                | Min                       | Мах  | Min                   | Мах | -     |

| SCL Clock Frequency                              | f <sub>SCL</sub>    |                | —                         | 100  | —                     | 400 | kHz   |

| Hold Time (Repeated)<br>START Condition          | t <sub>HD:STA</sub> |                | 4.0                       | -    | 0.6                   | -   | μs    |

| Low Period of the SCL Clock                      | t <sub>LOW</sub>    |                | 4.7                       | _    | 1.3                   | —   | μs    |

| HIGH Period of the SCL<br>Clock                  | <sup>t</sup> ніgн   |                | 4.0                       | -    | 0.6                   | -   | μs    |

| Set-up Time for a Repeated START Condition       | t <sub>SU:STA</sub> |                | 4.7                       | -    | 0.6                   | -   | μs    |

| Data Hold Time                                   | t <sub>HD:DAT</sub> |                | 100                       | _    | 100                   | —   | ns    |

| Data Set-up Time                                 | t <sub>SU:DAT</sub> |                | 250                       | _    | 100                   | —   | ns    |

| Rise Time of Both SDA and SCL Signals            | t <sub>r</sub>      |                | _                         | 1000 | 20                    | 300 | ns    |

| Fall Time of Both SDA and SCL Signals            | t <sub>f</sub>      |                | _                         | 300  | _                     | 300 | ns    |

| Set-up Time for STOP Con-<br>dition              | t <sub>SU:STO</sub> |                | 4.0                       | _    | 0.6                   | _   | μs    |

| Bus Free Time between a STOP and START Condition | t <sub>BUF</sub>    |                | 4.7                       | -    | 1.3                   | -   | μs    |

| Data Valid Time                                  | t <sub>VD:DAT</sub> |                | _                         | 3.45 | _                     | 0.9 | μs    |

| Data Valid Acknowledge<br>Time                   | t <sub>VD:ACK</sub> |                | —                         | 3.45 | —                     | 0.9 | μs    |

## Table 5.9. I<sup>2</sup>C Timing Specifications (SCL,SDA)

Figure 5.1. I<sup>2</sup>C Serial Port Timing Standard and Fast Modes

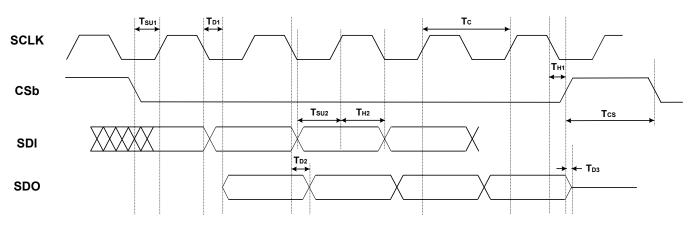

#### Table 5.10. SPI Timing Specifications (4-Wire)

## (V<sub>DD</sub>=1.8 V ± 5%, V<sub>DDA</sub>=3.3 V ± 5%, T<sub>A</sub>= -40 to 85 °C)

| Parameter                                          | Symbol           | Min | Тур  | Мах | Units          |

|----------------------------------------------------|------------------|-----|------|-----|----------------|

| SCLK Frequency                                     | f <sub>SPI</sub> | _   | _    | 20  | MHz            |

| SCLK Duty Cycle                                    | T <sub>DC</sub>  | 40  | _    | 60  | %              |

| SCLK Period                                        | T <sub>C</sub>   | 50  | _    | _   | ns             |

| Delay Time, SCLK Fall to SDO Active                | T <sub>D1</sub>  | _   | 12.5 | 18  | ns             |

| Delay Time, SCLK Fall to SDO                       | T <sub>D2</sub>  | _   | 10   | 15  | ns             |

| Delay Time, CSb Rise to SDO Tri-State              | T <sub>D3</sub>  | _   | 10   | 15  | ns             |

| Setup Time, CSb to SCLK                            | T <sub>SU1</sub> | 5   | _    | _   | ns             |

| Hold Time, SCLK Fall to CSb                        | T <sub>H1</sub>  | 5   | _    | _   | ns             |

| Setup Time, SDI to SCLK Rise                       | T <sub>SU2</sub> | 5   | _    | _   | ns             |

| Hold Time, SDI to SCLK Rise                        | T <sub>H2</sub>  | 5   | _    | _   | ns             |

| Delay Time Between Chip Selects (CSb) <sup>1</sup> | T <sub>CS</sub>  | 2   | _    | _   | T <sub>C</sub> |

### Note:

1. The minimum time is based on 20 MHz SPI clock (50 ns). So the minimum wait time between two frames should be 2\*50 ns = 100 ns.

Figure 5.2. 4-Wire SPI Serial Interface Timing

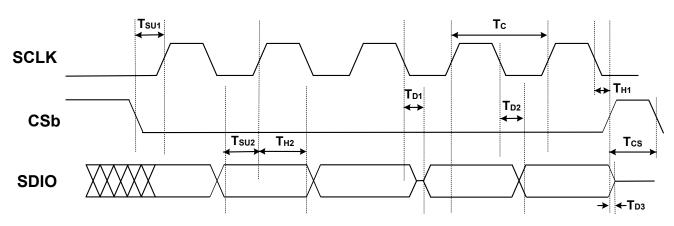

#### Table 5.11. SPI Timing Specifications (3-Wire)

(V<sub>DD</sub>=1.8 V ± 5%, V<sub>DDA</sub>= 3.3 V ± 5%, T<sub>A</sub>= -40 to 85 °C)

| Parameter                                          | Symbol           | Min | Тур  | Мах | Units          |

|----------------------------------------------------|------------------|-----|------|-----|----------------|

| SCLK Frequency                                     | f <sub>SPI</sub> | _   | _    | 20  | MHz            |

| SCLK Duty Cycle                                    | T <sub>DC</sub>  | 40  | _    | 60  | %              |

| SCLK Period                                        | T <sub>C</sub>   | 50  | _    | _   | ns             |

| Delay Time, SCLK Fall to SDO Turn-on               | T <sub>D1</sub>  | _   | 12.5 | 20  | ns             |

| Delay Time, SCLK Fall to SDO Next-bit              | T <sub>D2</sub>  | _   | 10   | 15  | ns             |

| Delay Time, CSb Rise to SDO Tri-State              | T <sub>D3</sub>  | _   | 10   | 15  | ns             |

| Setup Time, CSb to SCLK                            | T <sub>SU1</sub> | 5   |      | _   | ns             |

| Hold Time, SCLK Fall to CSb                        | T <sub>H1</sub>  | 5   | _    | _   | ns             |

| Setup Time, SDI to SCLK Rise                       | T <sub>SU2</sub> | 5   | _    | _   | ns             |

| Hold Time, SDI to SCLK Rise                        | T <sub>H2</sub>  | 5   | _    | _   | ns             |

| Delay Time Between Chip Selects (CSb) <sup>1</sup> | T <sub>CS</sub>  | 2   | _    | _   | T <sub>C</sub> |

#### Note:

1. The minimum time is based on 20 MHz SPI clock (50 ns). So the minimum wait time between two frames should be 2\*50 ns = 100 ns.

Figure 5.3. 3-Wire SPI Serial Interface Timing

## Table 5.12. Crystal Specifications