### BT.656 Encoder with Colour-Space Converter Rev. 1.1

## Key Design Features

- Synthesizable, technology independent VHDL IP Core

- Converts 24-bit RGB digital video to an industry standard 8-bit ITU-R BT.656 stream

- Integrated RGB888 to 4:2:2 YCbCr colour-space converter

- Both PAL and NTSC (576i and 480i) formats supported

- All signals synchronous with the pixel clock

- Small implementation size ideal for all types of FPGA

- Compatible with a wide range of SD video encoder ICs

## Applications

- BT.656 output video generation

- PAL & NTSC SDTV video format conversion

- Connectivity with a wide range of commercially available video encoder ICs

- Simple and cost-effective method for generating digital video outputs from your FPGA or ASIC

# **Generic Parameters**

| Generic name | Description       | Туре    | Valid range                     |

|--------------|-------------------|---------|---------------------------------|

| mode         | Output video mode | integer | 0: PAL (576i)<br>1: NTSC (480i) |

# **Pin-out Description**

| Pin name        | <i>I/O</i> | Description                                    | Active state                  |

|-----------------|------------|------------------------------------------------|-------------------------------|

| clk             | in         | Pixel clock                                    | rising edge                   |

| reset           | in         | Asynchronous reset                             | low                           |

| underflow       | out        | Pixel underflow error                          | high                          |

| video_out [7:0] | out        | BT.656 output video (8-bit)                    | data                          |

| video_val       | out        | BT.656 output video valid                      | high                          |

| pixin [23:0]    | in         | 24-bit RGB888 pixel                            | data                          |

| pixin_field     | in         | Field flag                                     | 0: odd field<br>1: even field |

| pixin_vsync     | in         | Vertical sync in                               | high                          |

| pixin_hsync     | in         | Horizontal sync in                             | high                          |

| pixin_val       | in         | Input pixel valid                              | high                          |

| pixin_rdy       | out        | Ready to accept input pixel (handshake signal) | high                          |

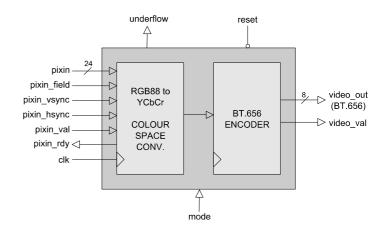

# Block Diagram

### **General Description**

BT\_656\_ENCODER (Figure 1) is a digital video encoder with integrated colour-space converter. The encoder accepts 24-bit RGB pixels from sequential odd and even fields. These pixels are then mapped to the YCbCr colour-space and formatted correctly into a BT.656 output stream.

The encoder begins operation after *reset* is de-asserted and on detection of input field '0'. Input pixels are sampled on the rising-edge of *clk* when the *pixin\_val* and *pixin\_rdy* signals are both asserted high. The *pixin\_vsync* and the *pixin\_hsync* flags are coincident with the first pixel of a field and line. The *pixin\_field* flag indicates whether the field is odd or even.

The valid-ready flow-control interface shares a common format with all other Zipcores video IP and allows easy connectivity between IP cores. The valid-ready interface also allows simple connectivity with an input FIFO or external frame buffer.

The output of the encoder generates an industry standard ITU-R BT.656 format video stream together with a *video\_val* signal that is asserted with the first valid byte of the output stream.

If the encoder is starved of pixels during the generation of an active line then the *underflow* flag will be asserted. In the event of an underflow condition, then design must be reset by asserting the reset signal low for at least one clock cycle. Operation will then resume as normal when the next input field is detected.

#### BT.656 Encoder

The encoder samples the incoming RGB pixels and looks for the first active line in field '0' (odd field). Once this is detected the generation of the BT.656 stream begins. Only active input pixels are processed by the encoder.

After all the lines in the odd field have been encoded, operation continues with the encoding of all active lines in field '1' (even field). The encoder then reverts back to field '0' once again.

After a system reset, the encoder will revert to it's initial state and stop generating the output stream. Encoding will then resume again with the first active line of field '0'.

When the generic parameter mode is set to '0', the encoder expects an 576i interlaced video input with a resolution of 720 x 288 pixels per field. Conversely, when mode is set to '1' then the expected input is (480i) or 720 x 240 pixels per field.

Note that only active pixels should be sent to the encoder. The encoder input is not concerned with input pixels during periods of vertical or All video timing information is automatically horizontal blanking. embedded in the BT.656 output stream.

#### Colour-space converter

The encoder features an integrated colour-space converter that converts the RGB inputs to YCbCr 4:2:2 format. Chroma values are decimated every second pixel to generate the 4:2:2 video. The colour-space conversion is done according to the following formula:

> Y = 16 + 0.257R + 0.504G + 0.098BCb = 128 - 0.148R - 0.291G + 0.439BCr = 128 + 0.439R - 0.368G - 0.071B

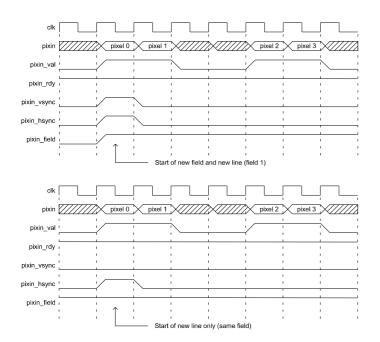

### **Functional Timing**

Example input waveforms are shown in Figure 2. Input pixels and syncs are sampled on a rising clock-edge when pixin val and pixin rdy are both high. When pixin\_val is low then the inputs are ignored by the encoder.

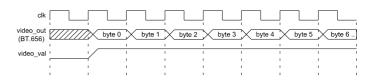

Figure 3 shows the output BT.656 video stream from the encoder. Bytes are transferred on a rising clock-edge when video\_val is active high.

# Source File Description

All source files are provided as text files coded in VHDL. The following table gives a brief explanation of each file.

| Source file              | Description                  |  |

|--------------------------|------------------------------|--|

| video_in.txt             | Source input video text file |  |

| pipeline_reg.vhd         | Pipeline register element    |  |

| fifo_sync.vhd            | Synchronous FIFO             |  |

| video_file_reader.vhd    | Input video text file reader |  |

| bt_656_enc_sof.vhd       | Field sync component         |  |

| bt_656_enc_csc.vhd       | Colour-space converter       |  |

| bt_656_enc_422.vhd       | Chroma re-sampler            |  |

| bt_656_enc_pack.vhd      | Pixel packer component       |  |

| bt_656_enc_unpack.vhd    | Pixel unpacker component     |  |

| bt_656_enc_enc.vhd       | Main BT.656 formatter        |  |

| bt_656_encoder.vhd       | Top-level component          |  |

| bt_656_encoder_bench.vhd | Top-level testbench          |  |

# Functional Testing

An example VHDL testbench is provided for use in a suitable VHDL simulator. The compilation order of the source code is as follows:

- pipeline\_reg.vhd 1

- 2 fifo\_sync.vhd

- 3. bt\_656\_enc\_sof.vhd

- 4. bt 656 enc csc.vhd 5

- bt\_656\_enc\_422.vhd

- 6. bt\_656\_enc\_pack.vhd 7.

- bt\_656\_enc\_unpack.vhd 8. bt 656 enc.vhd

- 9.

- bt\_656\_encoder.vhd bt\_656\_encoder\_bench.vhd 10.

- video\_file\_reader.vhd 11.

The VHDL testbench instantiates the BT\_656\_ENCODER component with the video format set to 'PAL' or 576i. The source video for the simulation is generated by the file-reader component. This component reads a text-based file which contains the RGB pixels and flags on consecutive lines. The text file is called video\_in.txt and should be placed in the top-level simulation directory.