## DATA SHEET

# SKY13380-350LF: 20 MHz-3.0 GHz High Power SP4T Switch With Decoder

## **Applications**

- GSM/WCDMA/EDGE datacards and handsets

- Mobile high power switching systems

## **Features**

- Broadband frequency range: 20 MHz to 3.0 GHz

- $\bullet$  Low insertion loss: 0.40 dB @ 1 GHz, 0.45 dB @ 2 GHz with high isolation (28 dB @ 1 GHz)

- VDD: 2.5 to 3.0 V for high power applications; can be used down to 1.6 V for low power applications

- High linearity IMD < -100 dBm over phase

- Good harmonic performance < -80 dBc @ 0.9 GHz

- Low voltage logic compatible (minimum VHIGH = 1.8 V)

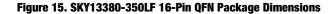

- Small, QFN (16-pin, 3 x 3 mm) package (MSL1, 260 °C per JEDEC J-STD-020)

Skyworks Green<sup>™</sup> products are RoHS (Restriction of Hazardous Substances)-compliant, conform to the EIA/EICTA/JEITA Joint Industry Guide (JIG) Level A guidelines, are halogen free according to IEC-61249-2-21, and contain <1,000 ppm antimony trioxide in polymeric materials.

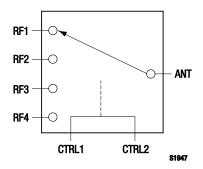

Figure 1. SKY13380-350LF Block Diagram

# Description

The SKY13380-350LF is a symmetrical, single-pole, four-throw (SP4T) switch. The device is designed for broadband, high power switching applications that demand high linearity and low insertion loss. This is a general purpose switch optimized for a variety of multimode applications such as GSM/WCDMA/EDGE.

The switch is manufactured using Skyworks state-of-the-art pHEMT process. The SKY13380-350LF features integrated logic that uses only two control lines for switch operation. The low current consumption makes the device suitable for battery-operated applications.

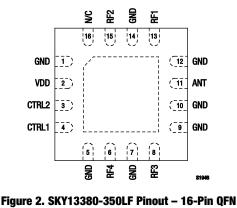

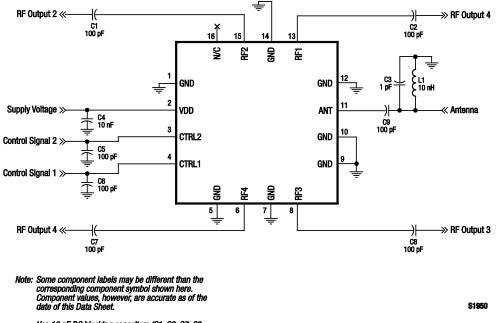

The SKY13380-350LF SP4T switch is provided in a compact Quad Flat No-Lead (QFN)  $3 \times 3$  mm package. A functional block diagram is shown in Figure 1. The pin configuration and package are shown in Figure 2. Signal pin assignments and functional pin descriptions are provided in Table 1.

(Top View)

| Table 1. SKY13380-350LF Signal Descrip | ptions |

|----------------------------------------|--------|

|----------------------------------------|--------|

| Pin # | Name  | Description                                                                                                                                                                                   | Pin #                                                       | Name | Description                                                                                                                                                                                   |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GND   | Ground                                                                                                                                                                                        | 9                                                           | GND  | Ground                                                                                                                                                                                        |

| 2     | VDD   | Supply voltage input. The voltage may be<br>switched. The switching time must be no longer<br>than the start-up time.                                                                         | 10 GND Ground                                               |      | Ground                                                                                                                                                                                        |

| 3     | CTRL2 | Control signal 2. The logic level applied to this<br>pin, along with the logic level applied to pin 4,<br>controls the state of the switch.                                                   | exclusively to pin 6, 8, 13,<br>the control voltage applied |      | Antenna. This pin is connected directly and exclusively to pin 6, 8, 13, or 15 depending on the control voltage applied to pins 3 and 4. A DC blocking capacitor is required.                 |

| 4     | CTRL1 | Control signal 1. The logic level applied to this<br>pin, along with the logic level applied to pin 3,<br>controls the state of the switch.                                                   | 12                                                          | GND  | Ground                                                                                                                                                                                        |

| 5     | GND   | Ground                                                                                                                                                                                        | 13                                                          | RF1  | RF output 1. This pin is either connected directly<br>to or is disconnected from pin 11, depending on<br>the control voltage applied to pins 3 and 4. A DC<br>blocking capacitor is required. |

| 6     | RF4   | RF output 4. This pin is either connected directly<br>to or is disconnected from pin 11, depending on<br>the control voltage applied to pins 3 and 4. A DC<br>blocking capacitor is required. | 14                                                          | GND  | Ground                                                                                                                                                                                        |

| 7     | GND   | Ground                                                                                                                                                                                        | 15                                                          | RF2  | RF output 2. This pin is either connected directly<br>to or is disconnected from pin 11, depending on<br>the control voltage applied to pins 3 and 4. A DC<br>blocking capacitor is required. |

| 8     | RF3   | RF output 3. This pin is either connected directly<br>to or is disconnected from pin 11, depending on<br>the control voltage applied to pins 3 and 4. A DC<br>blocking capacitor is required. | 16                                                          | N/C  | No connection.                                                                                                                                                                                |

#### Table 2. SKY13380-350LF Absolute Maximum Ratings

| Parameter                                                | Symbol       | Minimum | Maximum | Units |

|----------------------------------------------------------|--------------|---------|---------|-------|

| Supply voltage                                           | Vdd          |         | 3       | V     |

| Input power (20 MHz to 3.0 GHz, $V_{DD} = 2.5$ to 3.0 V) | Pin          |         | +40     | dBm   |

| Control voltage                                          | CTRL1, CTRL2 |         | 3       | V     |

| Operating temperature                                    | Тор          | -40     | +85     | °C    |

| Storage temperature                                      | Тята         | -50     | +100    | °C    |

Note: Exposure to maximum rating conditions for extended periods may reduce device reliability. There is no damage to device with only one parameter set at the limit and all other parameters set at or below their nominal value. Exceeding any of the limits listed here may result in permanent damage to the device.

*CAUTION*: Although this device is designed to be as robust as possible, Electrostatic Discharge (ESD) can damage this device. This device must be protected at all times from ESD. Static charges may easily produce potentials of several kilovolts on the human body or equipment, which can discharge without detection. Industry-standard ESD precautions should be used at all times.

## **Functional Description**

The SKY13380-350LF is comprised of a CMOS decoder that enables two TTL-compatible DC lines to control four RF ports. The decoder is internally connected to a GaAs pHEMT RF switch. Depending on the logic voltage level applied to the control pins, the ANT pin is connected to one of four switched RF outputs (RF1, RF2, RF3, or RF4) by a low insertion loss path, while maintaining a high isolation path to the alternate port.

Startup time is defined as the time from when VDD is applied to when the switch is active. Once the startup time has passed, the control voltages CTRL1 and CTRL2 can be applied. RF power should not be applied during the startup time or damage to the device could result.

Table 3. SKY13380-350LF Electrical Specifications (1 of 2) (Note 1)

The recommended startup sequence is:

Step 1: Apply VDD.

Step 2: Apply CTRL1 and CTRL2

Step 3: Apply RF input.

The device must be turned off in the reverse order.

When VDD is not applied, the device is considered off or inactive. All arms of the switch remain on in this state, creating a poor four-way power splitter. The return loss of all RF ports is very low in this state. RF should not be applied when VDD is not present and should only be used to conserve current.

## **Electrical and Mechanical Specifications**

The absolute maximum ratings of the SKY13380-350LF are provided in Table 2. Electrical specifications are provided in Table 3.

The state of the SKY13380-350LF is determined by the logic provided in Table 4.

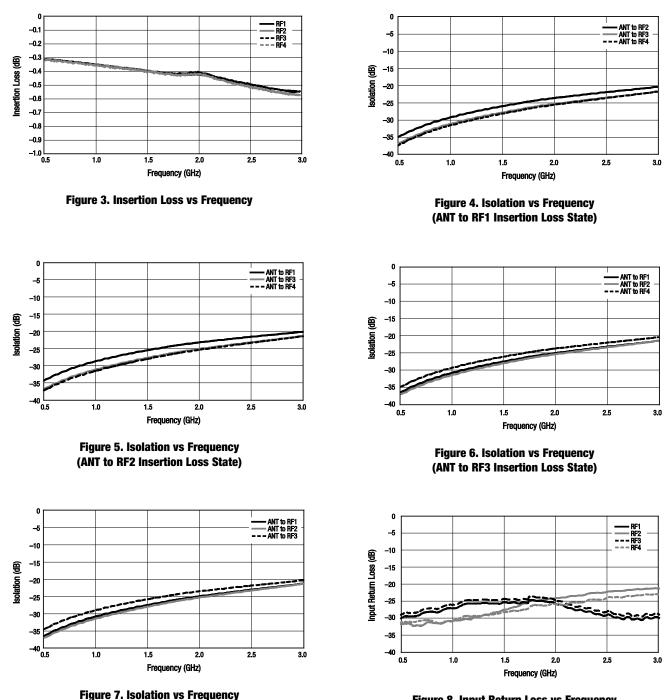

Typical performance characteristics of the SKY13380-350LF are illustrated in Figures 3 through 8.

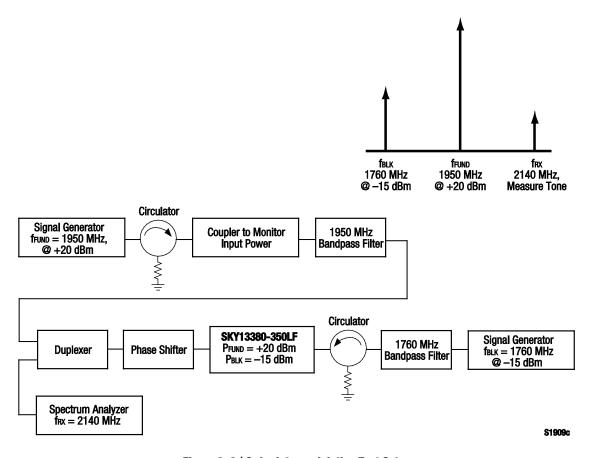

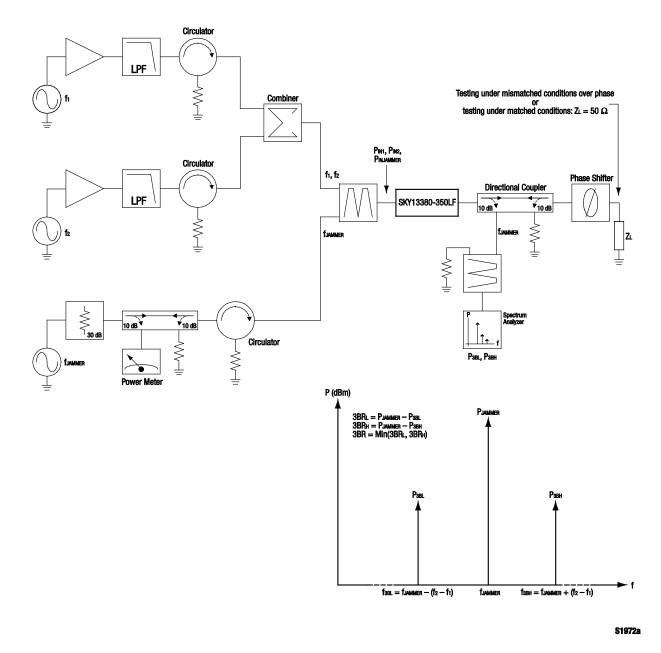

Figure 9 illustrates the test setup used to measure data for 3<sup>rd</sup> Order Intermodulation Distortion (IMD3) testing. Figure 10 illustrates the test setup used to measure triple beat ratio data.

| Parameter                                        | Symbol | Test Condition                                                                                                                                                                                   | Min            | Typical              | Max                  | Units          |

|--------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|----------------------|----------------|

| RF Specifications                                |        |                                                                                                                                                                                                  |                |                      |                      |                |

| Insertion loss                                   | IL     | 0.02 to 1.0 GHz<br>1.0 to 2.0 GHz<br>2.0 to 2.7 GHz                                                                                                                                              |                | 0.40<br>0.45<br>0.60 | 0.50<br>0.60<br>0.80 | dB<br>dB<br>dB |

| Isolation                                        | ISO    | 0.02 to 1.0 GHz<br>1.0 to 2.0 GHz<br>2.0 to 2.7 GHz                                                                                                                                              | 25<br>19<br>19 | 28<br>22<br>21       |                      | dB<br>dB<br>dB |

| Return loss                                      | S11    | 0.02 to 2.7 GHz, all RF ports, insertion loss state                                                                                                                                              |                | 20                   |                      | dB             |

| Second harmonic                                  | 2fo    | $f_{FUND} = 900 \text{ MHz},$<br>$P_{IN} = +35 \text{ dBm}$                                                                                                                                      |                | +80                  |                      | dBc            |

|                                                  |        | $f_{FUND} = 1800 \text{ MHz},$<br>$P_{IN} = +33 \text{ dBm}$                                                                                                                                     |                | +75                  |                      | dBc            |

| Third harmonic                                   | 3fo    | ffund = 900 MHz,<br>Pin = +35 dBm                                                                                                                                                                |                | +80                  |                      | dBc            |

|                                                  |        | $f_{FUND} = 1800 \text{ MHz},$<br>$P_{IN} = +33 \text{ dBm}$                                                                                                                                     |                | +75                  |                      | dBc            |

| Input 0.1 dB compression point                   | P0.1dB | @ 900 MHz, 1800 MHz                                                                                                                                                                              |                | +39                  |                      | dBm            |

| 3 <sup>rd</sup> Order Intermodulation Distortion | IMD3   | $      f_{FUND} = 1.95 \text{ GHz } @ \\ +20 \text{ dBm}, \\ f_{BLK} = 1.76 \text{ GHz} \\ @ -15 \text{ dBm}, \\ f_{RX} = 2.14 \text{ GHz}, \text{ worst} \\ case over phase. See \\ Figure 9. $ |                | 100                  |                      | dBm            |

#### (VDD = 2.65 V, CTRL1 = CTRL2 = VDD, TOP = +25 °C, All Unused RF Ports are Terminated in a 50 Ω Load, Unless Otherwise Noted)

## Table 3. SKY13380-350LF Electrical Specifications (2 of 2) (Note 1)

#### (VDD = 2.65 V, CTRL1 = CTRL2 = VDD, TOP = +25 °C, All Unused RF Ports are Terminated in a 50 Ω Load, Unless Otherwise Noted)

| Parameter                       | Symbol       | Test Condition                                                                            | Min  | Typical    | Max        | Units    |

|---------------------------------|--------------|-------------------------------------------------------------------------------------------|------|------------|------------|----------|

| RF Specifications (continued)   | •            |                                                                                           |      |            |            |          |

| Switching speed                 |              | 10/90% RF rise/fall time                                                                  |      | 1          |            | μs       |

| Startup time                    |              | Wait time required from<br>when Vod is applied until<br>control voltage can be<br>applied |      | 25         |            | μs       |

| DC/Control Specifications       | •            |                                                                                           |      |            |            |          |

| Switched supply voltage         | Vdd          |                                                                                           | 1.60 | 2.65       | 3.00       | V        |

| Switched supply current         | lod          |                                                                                           |      | 0.3        |            | mA       |

| Control voltage:<br>High<br>Low | CTRL1, CTRL2 |                                                                                           | 1.60 | 2.0<br>0   | Vdd<br>0.3 | V<br>V   |

| Control current:<br>High<br>Low | ICTL         |                                                                                           |      | 0.5<br>0.5 |            | μΑ<br>μΑ |

Note 1: Performance is guaranteed only under the conditions listed in this Table.

#### Table 4. SKY13380-350LF Truth Table

| State | CTRL1 (Pin 4) | CTRL2 (Pin 3) | RF Path    |

|-------|---------------|---------------|------------|

| 1     | Vlow          | Vlow          | ANT to RF1 |

| 2     | Vlow          | Vніgh         | ANT to RF2 |

| 3     | Vніgн         | Vlow          | ANT to RF3 |

| 4     | Vнigh         | Vhigh         | ANT to RF4 |

Note: VHIGH = 1.6 V to VDD

VLOW = 0 to 0.3 V

Any state other than described in this Table places the switch into an undefined state.

## **Typical Performance Characteristics**

(ANT to RF4 Insertion Loss State)

(VDD = 2.5 to 3.0 V, CTRL1 = CTRL2 = VDD, TOP = +25 °C, All Unused RF Ports are Terminated in a 50 Ω Load, Unless Otherwise Noted)

Figure 8. Input Return Loss vs Frequency

Figure 9. 3rd Order Intermodulation Test Setup

Figure 10. Triple Beat Ratio (3BR) Test Setup

## **Evaluation Board Description**

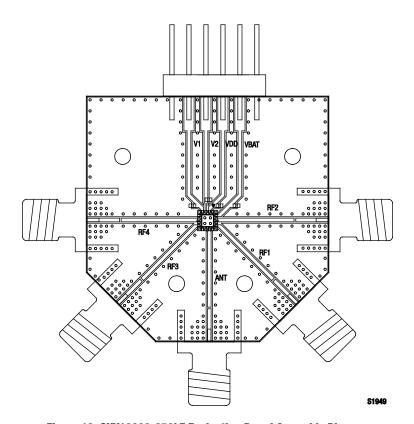

The SKY13380-350LF Evaluation Board is used to test the performance of the SKY13380-350LF SP4T Switch. An Evaluation Board schematic diagram is provided in Figure 11. An assembly drawing for the Evaluation Board is shown in Figure 12.

Components C3 and L1 constitute an ESD filter. This topology and the component values noted in Figure 11 may vary according to the ESD requirement and acceptable insertion loss for a specific application. Decoupling capacitors (C3 through C6) are recommended to suppress noise and to prevent RF leakage into the DC control circuits.

DC blocking capacitors C1, C2, C7, C8, and C9 determine the low frequency operation of the switch. Increase the capacitor values to lower operation frequency.

Use 10 nF DC blocking capacitors (C1, C2, C7, C8, and C9) for <50 MHz operation.

Figure 12. SKY13380-350LF Evaluation Board Assembly Diagram

# **Package Dimensions**

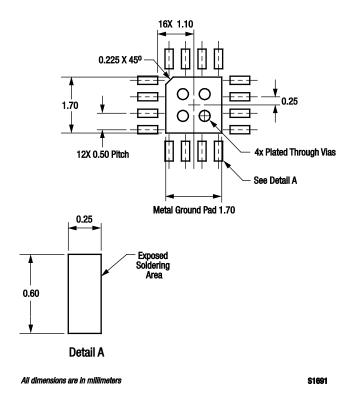

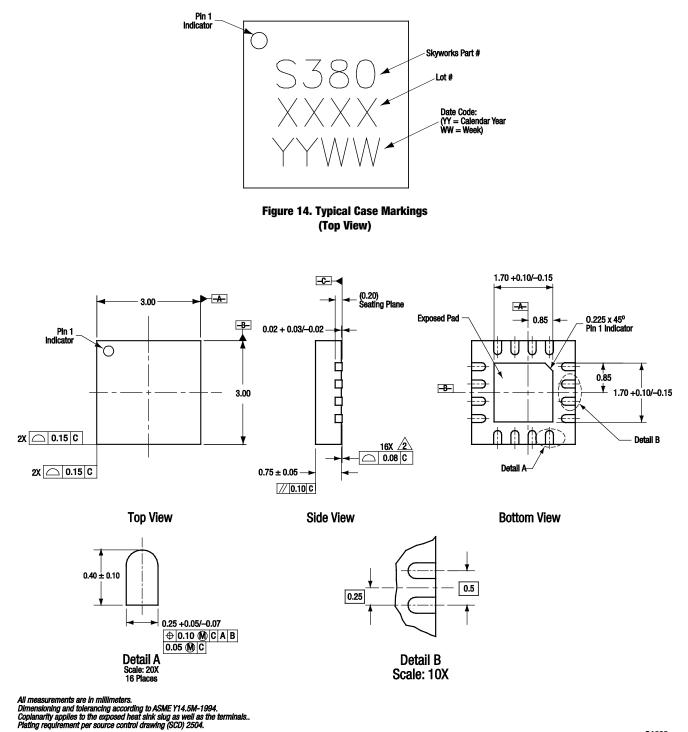

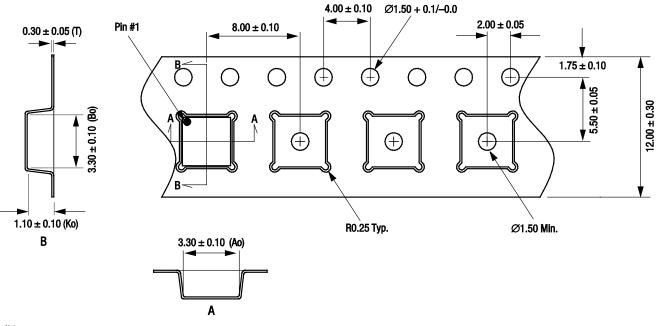

The PCB layout footprint for the SKY13380-350LF is provided in Figure 13. Typical case markings are shown in Figure 14. Package dimensions for the 16-pin QFN are shown in Figure 15, and tape and reel dimensions are provided in Figure 16.

# **Package and Handling Information**

Instructions on the shipping container label regarding exposure to moisture after the container seal is broken must be followed. Otherwise, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly. THE SKY13380-350LF is rated to Moisture Sensitivity Level 1 (MSL1) at 260 °C. It can be used for lead or lead-free soldering. For additional information, refer to the Skyworks Application Note, *Solder Reflow Information*, document number 200164.

Care must be taken when attaching this product, whether it is done manually or in a production solder reflow environment. Production quantities of this product are shipped in a standard tape and reel format.

## Figure 13. SKY13380-350LF PCB Layout Footprint (Top View)

S1692

uus: 1. Carrier tape: black conductive polystyrene, non-bakeable material. 2. Cover tape material: transparent conductive HSA. 3. Cover tape size: 9.20 mm width. 4. All maasumements are in millimotars.

S1698