#### **DATA SHEET**

# SKY73212-11: 1700-2000 MHz Diversity Downconversion Mixer with Integrated Integer-N PLL and VCO

# **Applications**

- Cellular base station systems: GSM/EDGE, CDMA2000, WCDMA, TD-SCDMA

- Other wireless communication systems

## **Features**

RF frequency range: 1700 to 2000 MHz

IF frequency range: 40 to 300 MHz

• Conversion gain: 9 dB

• IIP3: +24 dBm; OIP3: +33 dBm

Noise Figure: 11 dB

Integrated RF balun

• High linearity IF amplifier

• Integer-N frequency synthesizer

Low phase-noise VCO

• Low RF output comparison spurs

• Programmable 18-bit N-counter and 11-bit R-counter

• Wide range of reference frequencies

Programmable charge pump currents

Flexible configuration that allows connection to an external VCO or PLL

· Digital lock detector

Optional adjustment of the core, divider, and charge pump currents by external resistor

Power supply for mixer: 5 V; power supply for synthesizer: 3.3 V

Small, low-cost MCM (44-pin, 10 x 6 mm) SMT package (MSL3, 260 °C per JEDEC J-STD-020)

Skyworks Pb-free products are compliant with all applicable legislation. For additional information, refer to *Skyworks Definition of Lead (Pb)-Free*, document number SQ04-0073.

# **Description**

Skyworks SKY73212-11 is a fully integrated diversity downconverter that includes a high linearity mixer, large dynamic range Intermediate Frequency (IF) amplifier, and a complete Voltage Controlled Oscillator (VCO), synthesizer, and Local Oscillator (LO) chain. Low loss RF baluns have also been included to reduce design complications and to lower system cost.

The SKY73212-11 features a 3<sup>rd</sup> Order Input Intercept Point (IIP3) of +24 dBm and a Noise Figure (NF) of 11 dB, which make the device an ideal solution for high dynamic range systems such as 2G/3G base station receivers.

The SKY73212-11 also includes a fully integrated wideband VCO/Integer-N frequency synthesizer. By applying internal VCO division, the output LO frequency can be set to the desired value while minimizing the phase noise.

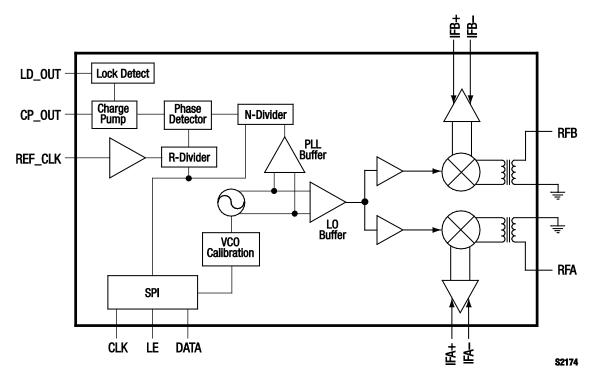

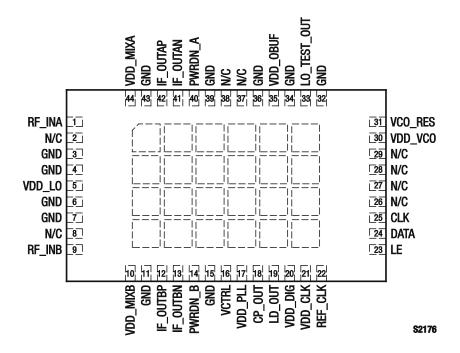

The SKY73212-11 is controlled by a Serial Peripheral Interface (SPI) and is manufactured using a robust silicon BiCMOS process. The device has been designed for optimum long-term reliability. It is manufactured in a compact, 44-pin 10 x 6 mm Multi-Chip Module (MCM). A functional block diagram is shown in Figure 1. The pin configuration and package are shown in Figure 2. Signal pin assignments and functional pin descriptions are provided in Table 1.

Figure 1. SKY73212-11 Block Diagram

Figure 2. SKY73212-11 Pinout – 44-Pin MCM (Top View)

**Table 1. SKY73212-11 Signal Descriptions**

| Pin# | Name     | Description                       | Pin# | Name        | Description                           |  |

|------|----------|-----------------------------------|------|-------------|---------------------------------------|--|

| 1    | RF_INA   | RF input, channel A               | 23   | LE          | Latch enable input for the SPI        |  |

| 2    | N/C      | No connection                     | 24   | DATA        | Data input for the SPI                |  |

| 3    | GND      | Ground                            | 25   | CLK         | Clock input for the SPI               |  |

| 4    | GND      | Ground                            | 26   | N/C         | No connection                         |  |

| 5    | VDD_L0   | LO DC supply, +5 V                | 27   | N/C         | No connection                         |  |

| 6    | GND      | Ground                            | 28   | N/C         | No connection                         |  |

| 7    | GND      | Ground                            | 29   | N/C         | No connection                         |  |

| 8    | N/C      | No connection                     | 30   | VDD_VCO     | VCO supply, +3.3 V                    |  |

| 9    | RF_INB   | RF input, channel B               | 31   | VCO_RES     | External resistor to set VCO bias     |  |

| 10   | VDD_MIXB | Channel B mixer DC supply, +5 V   | 32   | GND         | Ground                                |  |

| 11   | GND      | Ground                            | 33   | LO_TEST_OUT | LO test port                          |  |

| 12   | IF_OUTBP | Positive IF output, channel B     | 34   | GND         | Ground                                |  |

| 13   | IF_OUTBN | Negative IF output, channel B     | 35   | VDD_OBUF    | Dividers and LO buffer supply, +3.3 V |  |

| 14   | PWRDN_B  | Mixer power down, channel B       | 36   | GND         | Ground                                |  |

| 15   | GND      | Ground                            | 37   | N/C         | No connection                         |  |

| 16   | VCTRL    | VCO tuning voltage                | 38   | N/C         | No connection                         |  |

| 17   | VDD_PLL  | PLL supply, +3.3 V                | 39   | GND         | Ground                                |  |

| 18   | CP_OUT   | Charge pump output                | 40   | PWRDN_A     | Mixer power down, channel A           |  |

| 19   | LD_OUT   | Lock detect output                | 41   | IF_OUTAN    | Negative IF output, channel A         |  |

| 20   | VDD_DIG  | Supply for digital blocks, +3.3 V | 42   | IF_OUTAP    | Positive IF output, channel A         |  |

| 21   | VDD_CLK  | Reference buffer supply, +3.3 V   | 43   | GND         | Ground                                |  |

| 22   | REF_CLK  | Reference clock input             | 44   | VDD_MIXA    | Channel A mixer DC supply, +5 V       |  |

# **Functional Description**

The SKY73212-11 is comprised of three main functional blocks:

- · RF balun and passive mixer

- IF amplifier

- Synthesizer

- VCO

- . VCO dividers and LO chain

## **RF Balun and Passive Mixer**

The RF baluns provide a single ended input, which can easily be matched to 50  $\Omega$  using a simple external matching circuit. The RF baluns offer very low loss, and excellent amplitude and phase balance.

The high linearity SKY73212-11 integrates a passive, double balanced mixer that provides a very low conversion loss, and an excellent 3<sup>rd</sup> Order Input Insertion Point (IIP3).

Additionally, the balanced nature of the mixer provides for high port-to-port isolation.

## **LO Buffers**

The LO section is optimized for low-side LO injection. The LO can be driven over a wide frequency range with only slight degradation in performance.

## **IF Amplifier**

The SKY73212-11 includes high dynamic range IF amplifiers that follow the passive mixers in the signal path. The outputs require a supply voltage connection using inductive chokes. These choke inductors should be high-Q and have the ability to handle 200 mA or greater. A simple matching network allows the output ports to be matched to a balanced 200  $\Omega$  impedance.

The IF amplifiers are optimized for IF frequencies between 40 and 300 MHz. The IF amplifiers can be operated outside of this range, but with a slight degradation in performance.

#### **Mixer Power Down**

A power-down function for each IF amplifier and corresponding L0 buffer is available in the SKY73212-11. The power-down function

is controlled through the PWRDN\_A and PWRDN\_B signals (pins 40 and 14, respectively):

| PWRDN_A and PWRDN_B Input | Enable/Disable        |

|---------------------------|-----------------------|

| High                      | Channels A/B disabled |

| Low                       | Channels A/B enabled  |

## **Synthesizer**

The frequency synthesizer is composed of the R-divider, N-divider, phase detector, charge pump, and lock detector.

#### R-Divider

The 11-bit programmable R-divider divides the reference input frequency and generates the reference input for the phase detector. The R-divider range varies from 1 to  $2^{11} - 1(2047)$ .

#### N-Divider

The N-divider consists of a selectable 16/17 or 32/33 prescaler, 13-bit main counter, and 5-bit swallow counter. The 18 bit N-divider ratio is calculated as:

$$N = P \times M - S$$

Where: P = Prescaler value

M = Main counter valueS = Swallow counter value

The N-divider range is from  $P^2$  to  $2^{18} - 1$ . For a 32/33 prescaler, the N-divider range varies from 1024 to 262143.

#### Phase Detector

The phase detector is an edge-controlled digital circuit. The circuit has two inputs: the reference signal (*Ref*) and the N-divider output. There are two digital outputs (*Up* and *Dn*) that drive the charge pump.

When the input phase difference is positive, the Up output is pulled up to VDD. When the input phase difference is negative, the Dn output is pulled down to ground. This type of phase detector acts only on the positive edges of the input signals.

#### Charge Pump

The charge pump is used to convert the logic levels of the *Up* and *Dn* pulses, carrying the phase error between the reference and the divided signal into analog quantities/current pulses.

The output of the SKY73212-11 charge pump is programmable and varies between 1.2 mA and 7.2 mA. Additional adjustment of the charge pump current can be accomplished by changing the value of the external PLL bias resistor.

#### Lock Detector

The lock detector circuit is activated when the phase difference between the *Up* and *Dn* phase detector signals for a given number of comparison cycles is shorter than a fixed delay. The CMOS output is active high when the loop is locked. The lock detector can be monitored from pin 19 (LD\_OUT).

#### VCO

The VCO is designed to generate the LO signal with the tuning function controlled by the synthesizer.

## **VCO Dividers and LO Chain**

The divider chain consists of dividers and LO drivers. The LO section is optimized for low-side LO injection at an RF frequency of 1700 to 2000 MHz.

# **Digital Interface**

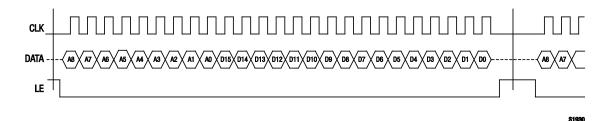

A three-wire SPI provides mode and bias control, and control of the PLL. The serial interface consists of three signals: the bus clock (CLK), latch enable (LE), and the serial data line (DATA).

A write data stream consists of 25 bits:

Bits[15:0] provide the 16-bit data block.

Bits[20:16] provide the register address.

Bits[24:21] provide the device address (the SKY73212-11 is 0110b).

A timing diagram for the SPI write cycle is shown in Figure 3.

**Figure 3. SPI Write Cycles**

## **Serial Bus Timing**

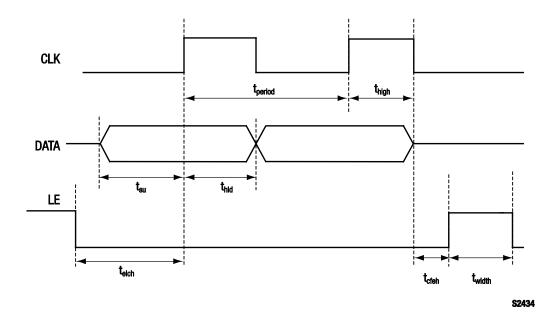

The SPI bus speed is programmable. Timing requirements for the CLK, DATA, and LE signals are provided in Table 2. A serial data input timing diagram is shown in Figure 4.

## **PLL Control Registers (R-Divider and N-Divider)**

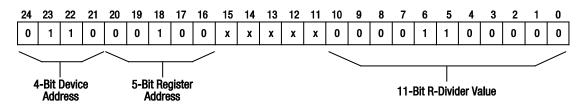

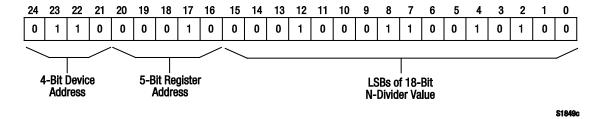

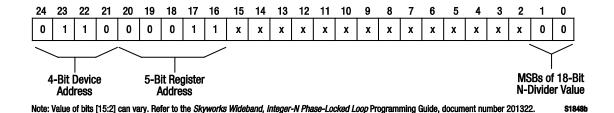

There are three digital PLL control registers that are used to store the R-divider and N-divider values: R\_DIV, N\_DIV1, and N\_DIV2. By default, all registers are 25 bits wide. Bits[20:16] are the address bits of the registers. The 16 least significant bits (LSBs) represent the data bits.

Three values are needed to calculate the three PLL dividers: the desired frequency ( $F_{RF}$ ), the VCO divider (D), and the frequency step size ( $F_{STEP}$ ).

The VCO frequency (Fvco) has a range of 2.7 GHz to 4.0 GHz, and is defined by the product of the desired frequency (FRF) and the VCO divider, D:

$$F_{VCO} = F_{RF} \times D \tag{1}$$

The VCO divider (equal to 1, 2, 3, 4, or 8) is chosen so that the product of  $F_{RF} \times D$  is within the specified VCO range.

**Table 2. SPI Timing Requirements**

| Timing             | Description               | Minimum Time<br>(ns) |  |  |

|--------------------|---------------------------|----------------------|--|--|

| tperiod            | Clock period              | 25                   |  |  |

| thigh              | Clock high time           | 10                   |  |  |

| t <sub>su</sub>    | Data setup to clock rise  | 5                    |  |  |

| t <sub>hld</sub>   | Data hold from clock rise | 5                    |  |  |

| telch              | Enable low to clock rise  | 10                   |  |  |

| t <sub>width</sub> | Enable high width         | 10                   |  |  |

| t <sub>efeh</sub>  | Clock fall to enable high | 20                   |  |  |

**Figure 4. SPI Input Timing Diagram**

The frequency step size (*FSTEP*) is a user-defined value. Given *FSTEP* and *D*, the comparison frequency (*FCOMP*) can be calculated by:

$$F_{COMP} = F_{STEP} \times D \tag{2}$$

The R\_DIV register stores the value of the 16-bit R-divider that produces the desired comparison frequency (*FcomP*) for the RF PLL according to the following equation:

$$R = \frac{F_{REF}}{F_{COMP}} \tag{3}$$

Where *Free* is the reference frequency provided to the device.

The N\_DIV1 and N\_DIV2 registers store the value of the N-divider according to the following equation:

$$N = \frac{F_{VCO}}{F_{REF}} \times R \tag{4}$$

Bits[1:0] of the N\_DIV2 register are the most significant bits (MSBs) of the 18-bit representation of the N number.

Bits[15:0] of the N\_DIV1 register are the LSBs of the 18-bit binary representation of the N number.

The calculated R-divider and N-divider values are programmed into the SKY73212-11 using the SPI interface.

## Example:

A desired RF output frequency of 1800 MHz is required using a reference frequency of 76.8 MHz and a desired frequency step size of 400 kHz. If the VCO divider is equal to 2, the VCO frequency is 3600 MHz from Equation 1 and the comparison frequency is equal to 800 kHz from Equation 2.

From Equations 3 and 4, the R and N values become:

R = 96 = 1100000b

N = 4500 = 1000110010100b

These values would be programmed through the SPI interface.

Figure 5 represents the bits of the R\_DIV register with the value of R=96. Figures 6 and 7 represent the bits of the N\_DIV1 and N\_DIV2 registers, respectively, with the value of N=4500.

# **Electrical and Mechanical Specifications**

The absolute maximum ratings of the SKY73212-11 are provided in Table 3. The recommended operating conditions are specified in Table 4 and electrical specifications are provided in Table 5.

Note: Value of bits [15:11] can vary. Refer to the Skyworks Wideband, Integer-N Phase-Locked Loop Programming Guide, document number 201322.

S1847b

Figure 5. R\_DIV Register Showing an R-Divider Value of 96

Figure 6. N DIV1 Register Showing an N-Divider Value of 4500 (LSBs)

Figure 7. N DIV2 Register Showing an N-Divider Value of 4500 (MSBs)

**Table 3. SKY73212-11 Absolute Maximum Ratings**

| Parameter                                                                          | Symbol             | Minimum | Typical | Maximum    | Units    |

|------------------------------------------------------------------------------------|--------------------|---------|---------|------------|----------|

| Mixer supply voltage (VDD_MIXA, VDD_MIXB, VDD_LO pins)                             | VDD_5v             | 4.5     | 5.0     | 5.5        | V        |

| Synthesizer supply voltage (VDD_VCO, VDD_OBUF, VDD_PLL, VDD_CLK, and VDD_DIG pins) | VDD_3.3v           |         | 3.3     | 3.6        | V        |

| Supply current: Mixer supply Synthesizer supply                                    | ldd_5v<br>ldd_3.3v |         |         | 440<br>150 | mA<br>mA |

| RF input power                                                                     | Pin                |         |         | +20        | dBm      |

| Operating case temperature                                                         | Tc                 | -40     |         | +85        | °C       |

| Junction temperature                                                               | TJ                 |         |         | +150       | °C       |

| Storage case temperature                                                           | Тѕтс               | -40     |         | +125       | °C       |

**Notes:** Exposure to maximum rating conditions for extended periods may reduce device reliability. There is no damage to device with only one parameter set at the limit and all other parameters set at or below their nominal value. Exceeding any of the limits listed here may result in permanent damage to the device.

**CAUTION**: Although this device is designed to be as robust as possible, Electrostatic Discharge (ESD) can damage this device. This device must be protected at all times from ESD. Static charges may easily produce potentials of several kilovolts on the human body or equipment, which can discharge without detection. Industry-standard ESD precautions should be used at all times.

**Table 4. SKY73212-11 Recommended Operating Conditions**

| Parameter                                                                          | Symbol             | Minimum        | Typical    | Maximum        | Units    |

|------------------------------------------------------------------------------------|--------------------|----------------|------------|----------------|----------|

| Mixer supply voltage (VDD_MIXA, VDD_MIXB, VDD_LO pins)                             | <b>V</b> DD_5v     | 4.75           | 5.00       | 5.25           | V        |

| Synthesizer supply voltage (VDD_VCO, VDD_OBUF, VDD_PLL, VDD_CLK, and VDD_DIG pins) | VDD_3.3v           | 3.0            | 3.3        | 3.6            | V        |

| RF frequency range                                                                 | fre                | 1700           |            | 2000           | MHz      |

| IF frequency range                                                                 | fir                | 40             |            | 300            | MHz      |

| Supply current: Mixer supply Synthesizer supply                                    | ldd_5v<br>ldd_3.3v |                | 360<br>125 | 400<br>140     | mA<br>mA |

| Operating case temperature                                                         | Tc                 | -40            |            | +85            | °C       |

| SPI logic levels (CLK, DATA, LE):<br>Low<br>High                                   | VIL<br>VIH         | 0.8 x Vdd_3.3v |            | 0.2 x Vdd_3.3v | V<br>V   |

Table 5. SKY73212-11 Electrical Specifications (1 of 2) (Note 1)  $(V_{DD}_{5V} = +5 V, V_{DD}_{3.3V} = +3.3 V, T_{c} = +25 °C, RF Frequency = 1950 MHz, IF Frequency = 150 MHz, LO Frequency = 1800 MHz, Unless Otherwise Noted)$

| Parameter                                   | Symbol           | Test Condition                                                                                                                                                                                                                                                                                                                 | Min   | Typical    | Max        | Units      |

|---------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------------|------------|

| Mixer                                       |                  |                                                                                                                                                                                                                                                                                                                                |       |            |            |            |

| Conversion gain                             | G                | $\begin{array}{l} \text{frf} = 1920 \text{ to } 1980 \text{ MHz}, \\ \text{VbD\_5v} = 4.75 \text{ to } 5.25 \text{ V}, \\ \text{VbD\_3.3v} = 3.0 \text{ to } 3.6 \text{ V} \end{array}$                                                                                                                                        | 7.5   | 8.5        |            | dB         |

| Gain variation over temperature             |                  | Tc = −40 to +85 °C                                                                                                                                                                                                                                                                                                             |       | ±0.7       |            | dB         |

| Noise Figure                                | NF               | $\begin{array}{l} \text{fr} = 1920 \text{ to } 1980 \text{ MHz}, \\ \text{V}_{\text{DD}}\_\text{5v} = 4.75 \text{ to } 5.25 \text{ V}, \\ \text{V}_{\text{DD}}\_3.3\text{v} = 3.0 \text{ to } 3.6 \text{ V} \end{array}$                                                                                                       |       | 11         | 13         | dB         |

| Noise Figure variation over temperature     |                  | Tc = −40 to +85 °C                                                                                                                                                                                                                                                                                                             |       | ±1.0       |            | dB         |

| 3 <sup>rd</sup> order input intercept point | IIP3             | $\label{eq:frf} \begin{split} &\text{frf} = 1920 \text{ to } 1980 \text{ MHz}, \\ &\text{PIN} = -10 \text{ dBm}, 800 \text{ kHz} \\ &\text{tone spacing}, \\ &\text{VbD\_5V} = 4.75 \text{ to } 5.25 \text{ V}, \\ &\text{VDD\_3.3V} = 3.0 \text{ to } 3.6 \text{ V} \end{split}$                                              | +21.5 | +24.0      |            | dBm        |

| IIP3 variation over temperature             |                  | Tc = −40 to +85 °C                                                                                                                                                                                                                                                                                                             |       | ±1.0       |            | dB         |

| Third order output intercept point          | OIP3             | $\label{eq:free} \begin{split} &\text{frf} = 1920 \text{ to } 1980 \text{ MHz}, \\ &\text{P}_{\text{IN}} = -10 \text{ dBm}, 800 \text{ kHz} \\ &\text{tone spacing}, \\ &\text{V}_{\text{DD}}\_5\text{V} = 4.75 \text{ to } 5.25 \text{ V}, \\ &\text{V}_{\text{DD}}\_3.3\text{V} = 3.0 \text{ to } 3.6 \text{ V} \end{split}$ | +29.5 | +33.0      |            | dBm        |

| 2RF - 2L0                                   | 2x2              | $P_{IN} = -10 \text{ dBm}$                                                                                                                                                                                                                                                                                                     |       | -65        | -50        | dBc        |

| 3RF – 3L0                                   | 3x3              | P <sub>IN</sub> = −10 dBm                                                                                                                                                                                                                                                                                                      |       | -75        | -67        | dBc        |

| 1 dB Input Compression Point                | IP1dB            | $\begin{array}{l} \text{frf} = 1920 \text{ to } 1980 \text{ MHz}, \\ \text{Vdd\_5v} = 4.75 \text{ to } 5.25 \text{ V}, \\ \text{Vdd\_3.3v} = 3.0 \text{ to } 3.6 \text{ V} \end{array}$                                                                                                                                        | +10   | +13        |            | dBm        |

| 1 dB Output Compression Point               | OP1dB            | $\label{eq:frf} \begin{split} &\text{frf} = 1920 \text{ to } 1980 \text{ MHz}, \\ &\text{Vdd\_5v} = 4.75 \text{ to } 5.25 \text{ V}, \\ &\text{Vdd\_3.3v} = 3.0 \text{ to } 3.6 \text{ V} \end{split}$                                                                                                                         | +19.0 | +20.5      |            | dBm        |

| Channel-to-channel isolation                |                  |                                                                                                                                                                                                                                                                                                                                | 50    |            |            | dB         |

| RF-to-IF isolation                          |                  |                                                                                                                                                                                                                                                                                                                                | 30    |            |            | dB         |

| LO leakage<br>@ RF port<br>@ IF port        |                  |                                                                                                                                                                                                                                                                                                                                |       |            | -27<br>-45 | dBm<br>dBm |

| Input return loss:<br>RF port<br>IF port    | Zin_rf<br>Zin_if | With external matching components                                                                                                                                                                                                                                                                                              |       | -12<br>-12 | -7<br>-7   | dB<br>dB   |

Table 5. SKY73212-11 Electrical Specifications (2 of 2) (Note 1) ( $V_{DD}_{5V} = +5 \text{ V}$ ,  $V_{DD}_{3.3V} = +3.3 \text{ V}$ ,  $T_{C} = +25 \,^{\circ}\text{C}$ , RF Frequency = 1950 MHz, IF Frequency = 150 MHz, LO Frequency = 1800 MHz, Unless Otherwise Noted)

| Parameter                   | Symbol | Test Condition                             | Min  | Typical              | Max                 | Units                      |

|-----------------------------|--------|--------------------------------------------|------|----------------------|---------------------|----------------------------|

| Synthesizer                 |        |                                            |      |                      |                     |                            |

| Reference input frequency   | fref   |                                            | 10.0 | 153.6                | 200.0               | MHz                        |

| Reference input sensitivity |        |                                            | 0.2  | 1.5                  |                     | Vp-p                       |

| Charge pump current         | ICP    |                                            | 1.2  | 4.8                  | 7.2                 | mA                         |

| Comparison spurs            |        |                                            |      | -70                  | -66                 | dBc                        |

| Locking time                |        | 20 kHz bandwidth, 1 ppm<br>frequency error |      |                      | 1                   | ms                         |

| Phase noise                 |        | @ 100 kHz<br>@ 1 MHz<br>@ 10 MHz           |      | -100<br>-133<br>-150 | -83<br>-128<br>-145 | dBc/Hz<br>dBc/Hz<br>dBc/Hz |

| RMS phase error             |        |                                            |      | 0.9                  | 1.1                 | deg                        |

Note 1: Performance is guaranteed only under the conditions listed in this Table.

# **Evaluation Board Description**

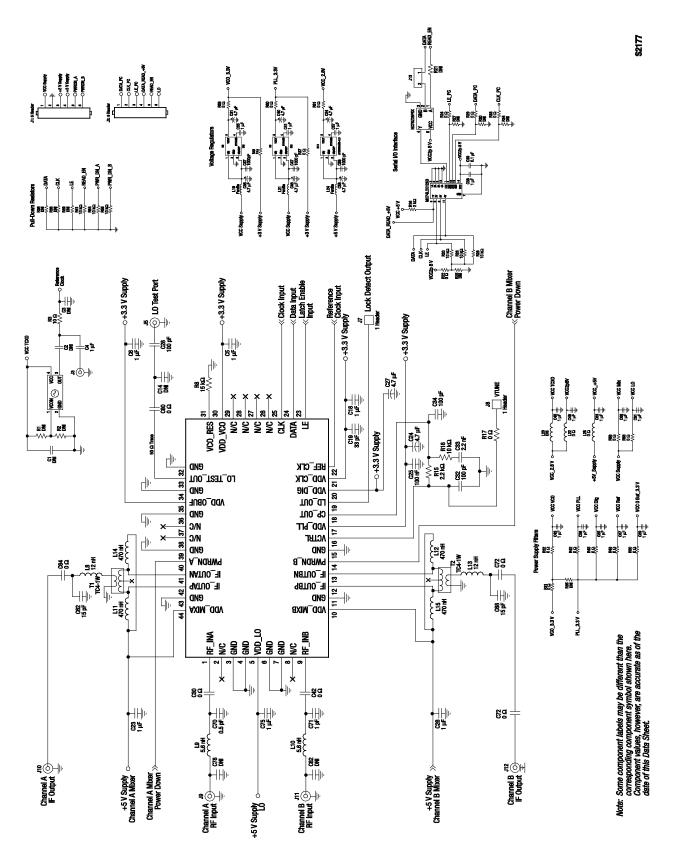

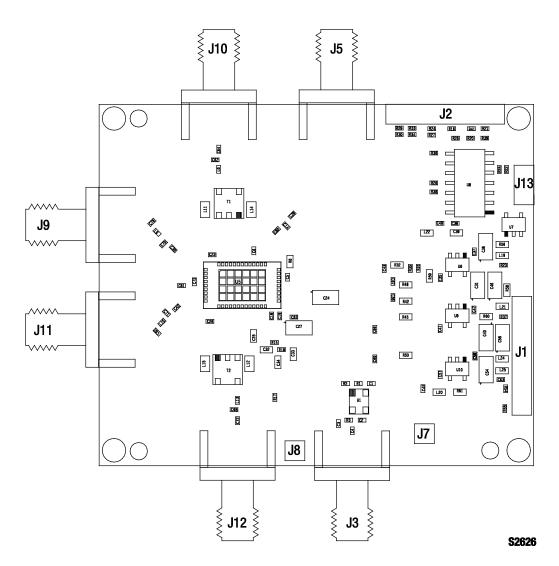

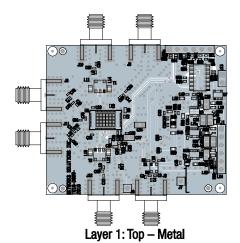

The SKY73212-11 Evaluation Board is used to test the performance of the SKY73212-11 mixer. An Evaluation Board schematic diagram is provided in Figure 8. An assembly drawing for the Evaluation Board is shown in Figure 9 and the layer detail is provided in Figure 10.

## **Circuit Design Configurations**

The following design considerations are general in nature and must be followed regardless of final use or configuration:

- 1. Paths to ground should be made as short as possible.

- The ground pad of the SKY73212-11 has special electrical and thermal grounding requirements. This pad is the main thermal conduit for heat dissipation. Since the circuit board acts as the heat sink, it must shunt as much heat as possible from the device. Therefore, design the connection to the ground pad to dissipate the maximum wattage produced by the circuit board.

- 3. Skyworks recommends including external bypass capacitors on the V<sub>DD</sub> voltage inputs of the device.

# **Package Dimensions**

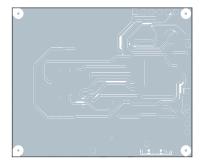

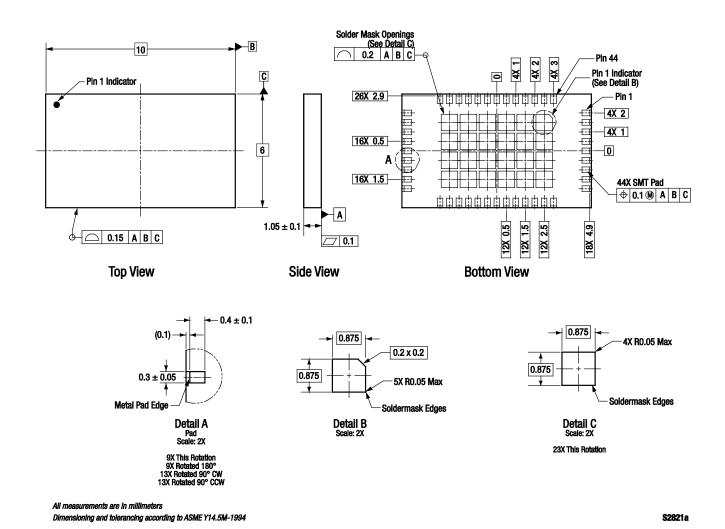

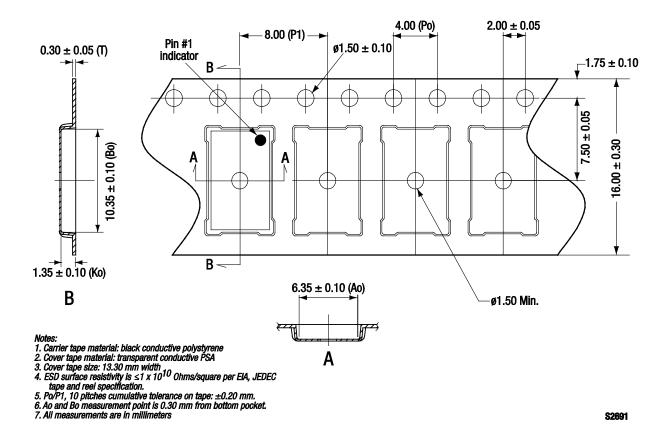

The PCB layout footprint for the SKY73212-11 is provided in Figure 11. Figure 12 shows the package dimensions for the 48-pin MCM and Figure 13 provides the tape and reel dimensions.

# **Package and Handling Information**

Since the device package is sensitive to moisture absorption, it is baked and vacuum packed before shipping. Instructions on the shipping container label regarding exposure to moisture after the container seal is broken must be followed. Otherwise, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly.

THE SKY73212-11 is rated to Moisture Sensitivity Level 3 (MSL3) at 260 °C. It can be used for lead or lead-free soldering. For additional information, refer to the Skyworks Application Note, *PCB Design & SMT Assembly/Rework Guidelines for MCM-L Packages*, document number 101752.

Care must be taken when attaching this product, whether it is done manually or in a production solder reflow environment. Production quantities of this product are shipped in a standard tape and reel format.

Figure 8. SKY73212-11 Evaluation Board Schematic

Figure 9. SKY73212-11 Evaluation Board Assembly Drawing

Layer 2: Ground

Layer 3: Power Plane

Layer 4: Solid Ground Plane

S2627

Figure 10. SKY73212-11 Evaluation Board Layer Detail

Figure 11. SKY73212-11 PCB Layout Footprint

Figure 12. SKY73212-11 44-Pin MCM Package Dimensions

Figure 13. SKY73212-11 Tape and Reel Dimensions