# ST25R3916B ST25R3917B

## NFC reader for payment, consumer and industrial applications

#### Datasheet - production data

### **Features**

- Operating modes

- Reader/writer

- Card emulation

- Active and passive peer to peer

- RF communication

- EMVCo® 3.1a analog and digital compliant

- NFC-A / ISO14443A up to 848 kbit/s

- NFC-B / ISO14443B up to 848 kbit/s

- NFC-F / FeliCa™ up to 424 kbit/s

- NFC-V / ISO15693 up to 53 kb/s

- NFC-A / ISO14443A (106 kbit/s) and NFC-F / FeliCa™ (212/424 kbit/s) card emulation

- Active and passive peer to peer initiator and target modes, up to 424 kbit/s

- Low level modes to implement MIFARE Classic<sup>®</sup> compliant or other custom protocols

- Key features

- Dynamic power output (DPO) controls the field strength to stay within given limits

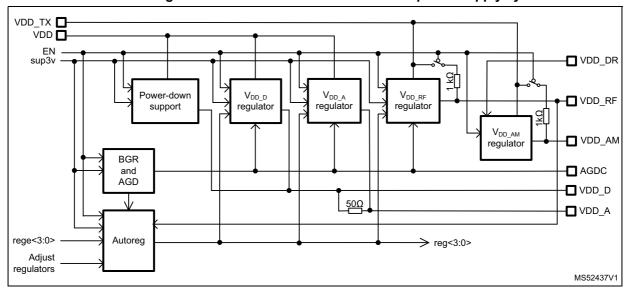

- Active wave shaping (AWS) reduces overand under-shoots

- Noise suppression receiver (NSR) allows reception in noisy environment

- Automatic antenna tuning (AAT) via variable capacitor

- Integrated EMVCo<sup>®</sup> 3.1a compliant EMD handling

- Automatic gain control and squelch feature to maximize SNR

- Low power NFC active and passive target modes

- Adjustable ASK modulation depth, from 0 to 82%

- Integrated regulators to boost system PSRR

- AM/PM and I/Q demodulator with baseband channel summation or automatic channel selection

- Possibility to drive two independent single ended antennas

- Measurement of antenna voltage amplitude and phase, RSSI, on-chip supply and regulated voltages

- · External communication interfaces

- 512-byte FIFO

- Serial peripheral interface (SPI) up to 10 Mbit/s

- I2C with up to 400 kbit/s in Fast-mode,

1 Mbit/s in Fast-mode Plus, and 3.4 Mbit/s in High-speed mode

- · Electrical characteristics

- Wide supply voltage and ambient temperature range (2.6 to 5.5 V from -40 °C to +105 °C, 2.4 to 5.5 V from -20 °C to +105 °C)

- Wide peripheral communication supply range, from 1.65 to 5.5 V

- Quartz oscillator capable of operating with 27.12 MHz crystal with fast start-up

## **Contents**

| 1 | Appl  | lications | S                               | 11 |

|---|-------|-----------|---------------------------------|----|

| 2 | Desc  | cription  |                                 | 12 |

|   | 2.1   | System    | n diagram                       | 13 |

|   | 2.2   | Block o   | diagram                         | 15 |

|   |       | 2.2.1     | Transmitter                     | 15 |

|   |       | 2.2.2     | Receiver                        | 16 |

|   |       | 2.2.3     | Phase and amplitude detector    | 16 |

|   |       | 2.2.4     | Automatic antenna tuning (AAT)  | 16 |

|   |       | 2.2.5     | A/D converter                   | 16 |

|   |       | 2.2.6     | External field detector         | 16 |

|   |       | 2.2.7     | Quartz crystal oscillator       | 17 |

|   |       | 2.2.8     | Power supply regulators         | 17 |

|   |       | 2.2.9     | POR and bias                    | 17 |

|   |       | 2.2.10    | RC oscillator and Wake-up timer | 17 |

|   |       | 2.2.11    | TX encoding                     | 17 |

|   |       | 2.2.12    | RX decoding                     | 17 |

|   |       | 2.2.13    | FIFO                            | 18 |

|   |       | 2.2.14    | Control logic                   | 18 |

|   |       | 2.2.15    | Host interface                  | 18 |

|   |       | 2.2.16    | Passive target memory           | 18 |

|   |       | 2.2.17    | P2RAM                           | 18 |

| 3 | Pin a | and sign  | nal description                 | 19 |

| 4 | Appl  | lication  | information                     | 23 |

|   | 4.1   | Power-    | -on sequence                    | 23 |

|   | 4.2   |           | ting modes                      |    |

|   |       | 4.2.1     | Transmitter                     |    |

|   |       | 4.2.2     | Receiver                        |    |

|   |       | 4.2.3     | Antenna tuning                  |    |

|   |       | 4.2.4     | Wake-up mode                    |    |

|   |       | 4.2.5     | Quartz crystal oscillator       |    |

|   |       | 4.2.6     | Timers                          |    |

|   |       |           |                                 |    |

|     | 4.2.7    | A/D converter                               | . 35 |

|-----|----------|---------------------------------------------|------|

|     | 4.2.8    | Phase and amplitude detector                | . 35 |

|     | 4.2.9    | External field detector                     | . 36 |

|     | 4.2.10   | Power supply system                         | . 37 |

|     | 4.2.11   | Overshoot / undershoot protection           | . 40 |

|     | 4.2.12   | Active wave shaping                         | . 41 |

|     | 4.2.13   | Reader operation                            | . 45 |

|     | 4.2.14   | Listen mode                                 | . 46 |

| 4.3 | Commu    | unication with an external microcontroller  | 49   |

|     | 4.3.1    | Interrupt interface                         | . 49 |

|     | 4.3.2    | Communication interface selection           | . 51 |

|     | 4.3.3    | Serial peripheral interface (SPI)           | . 51 |

|     | 4.3.4    | I2C interface                               | . 57 |

| 4.4 | Direct o | commands                                    | 61   |

|     | 4.4.1    | Set default                                 | . 62 |

|     | 4.4.2    | Stop all activities                         | . 63 |

|     | 4.4.3    | Clear FIFO                                  | . 63 |

|     | 4.4.4    | Transmit commands                           | . 63 |

|     | 4.4.5    | NFC field ON commands                       | . 64 |

|     | 4.4.6    | Mask receive data and Unmask receive data   | . 65 |

|     | 4.4.7    | Change AM modulation state                  | . 66 |

|     | 4.4.8    | Measure amplitude                           | . 66 |

|     | 4.4.9    | Reset RX gain                               | . 66 |

|     | 4.4.10   | Adjust regulators                           | . 66 |

|     | 4.4.11   | Measure phase                               | . 67 |

|     | 4.4.12   | Clear RSSI                                  | . 67 |

|     | 4.4.13   | Transparent mode                            | . 67 |

|     | 4.4.14   | Measure power supply                        | . 67 |

|     | 4.4.15   | Trigger RC calibration                      | . 67 |

|     | 4.4.16   | Test access                                 | . 68 |

| 4.5 | Registe  | ers                                         | 69   |

|     | 4.5.1    | IO configuration register 1                 | . 73 |

|     | 4.5.2    | IO configuration register 2                 | . 74 |

|     | 4.5.3    | Operation control register                  | . 75 |

|     | 4.5.4    | Mode definition register                    | . 76 |

|     | 4.5.5    | Bit rate definition register                | . 78 |

|     | 4.5.6    | ISO14443A and NFC 106kb/s settings register | . 79 |

| 4.5.7  | ISO14443B settings register 1              | . 80 |

|--------|--------------------------------------------|------|

| 4.5.8  | ISO14443B and FeliCa settings register     | . 81 |

| 4.5.9  | NFCIP-1 passive target definition register | . 82 |

| 4.5.10 | Stream mode definition register            | . 83 |

| 4.5.11 | Auxiliary definition register              | . 84 |

| 4.5.12 | EMD suppression configuration register     | . 85 |

| 4.5.13 | Subcarrier start timer register            | . 86 |

| 4.5.14 | Receiver configuration register 1          | . 87 |

| 4.5.15 | Receiver configuration register 2          | . 88 |

| 4.5.16 | Receiver configuration register 3          | . 89 |

| 4.5.17 | Receiver configuration register 4          | . 89 |

| 4.5.18 | P2P receiver configuration register 1      | . 90 |

| 4.5.19 | Correlator configuration register 1        | . 91 |

| 4.5.20 | Correlator configuration register 2        | . 92 |

| 4.5.21 | Mask receive timer register                | . 93 |

| 4.5.22 | No-response timer register 1               | . 94 |

| 4.5.23 | No-response timer register 2               | . 94 |

| 4.5.24 | Timer and EMV control register             | . 95 |

| 4.5.25 | General purpose timer register 1           | . 96 |

| 4.5.26 | General purpose timer register 2           | . 96 |

| 4.5.27 | PPON2 field waiting register               | . 97 |

| 4.5.28 | Squelch timer register                     | . 98 |

| 4.5.29 | NFC field on guard timer register          | . 98 |

| 4.5.30 | Mask main interrupt register               | . 99 |

| 4.5.31 | Mask timer and NFC interrupt register      | . 99 |

| 4.5.32 | Mask error and wake-up interrupt register  | 100  |

| 4.5.33 | Mask passive target interrupt register     | 100  |

| 4.5.34 | Main interrupt register                    | 101  |

| 4.5.35 | Timer and NFC interrupt register           | 102  |

| 4.5.36 | Error and wake-up interrupt register       | 103  |

| 4.5.37 | Passive target interrupt register          | 104  |

| 4.5.38 | FIFO status register 1                     | 105  |

| 4.5.39 | FIFO status register 2                     | 105  |

| 4.5.40 | Collision display register                 | 106  |

| 4.5.41 | Passive target display register            | 107  |

| 4.5.42 | Number of transmitted bytes register 1     | 108  |

| 4543   | Number of transmitted bytes register 2     | 108  |

| 4.5.44 | Bit rate detection display register                     | . 109 |

|--------|---------------------------------------------------------|-------|

| 4.5.45 | A/D converter output register                           | . 110 |

| 4.5.46 | Antenna tuning control register 1                       | . 111 |

| 4.5.47 | Antenna tuning control register 2                       | . 111 |

| 4.5.48 | TX driver register                                      | . 112 |

| 4.5.49 | Auxiliary modulation setting register                   | . 114 |

| 4.5.50 | Passive target modulation register                      | . 115 |

| 4.5.51 | TX driver timing register                               | . 116 |

| 4.5.52 | External field detector activation threshold register   | . 117 |

| 4.5.53 | Resistive AM modulation register                        | . 118 |

| 4.5.54 | External field detector deactivation threshold register | . 120 |

| 4.5.55 | TX driver timing display register                       | . 122 |

| 4.5.56 | Regulator voltage control register                      | . 123 |

| 4.5.57 | Regulator display register                              | . 124 |

| 4.5.58 | RSSI display register                                   | . 125 |

| 4.5.59 | Gain reduction state register                           | . 126 |

| 4.5.60 | AWS Config 1 register                                   | . 127 |

| 4.5.61 | AWS Config 2 register                                   | . 128 |

| 4.5.62 | Auxiliary display register                              | . 129 |

| 4.5.63 | Overshoot protection configuration register 1           | . 130 |

| 4.5.64 | Overshoot protection configuration register 2           | . 130 |

| 4.5.65 | Undershoot protection configuration register 1          | . 131 |

| 4.5.66 | Undershoot protection configuration register 2          | . 132 |

| 4.5.67 | Wake-up timer control register                          | . 133 |

| 4.5.68 | Amplitude measurement configuration register            | . 134 |

| 4.5.69 | Amplitude measurement reference register                | . 134 |

| 4.5.70 | AWS time 1 register                                     | . 135 |

| 4.5.71 | AWS time 2 register                                     | . 135 |

| 4.5.72 | AWS time 3 register                                     | . 136 |

| 4.5.73 | AWS time 4 register                                     | . 136 |

| 4.5.74 | AWS time 5 register                                     | . 137 |

| 4.5.75 | AWS time 6 register                                     | . 137 |

| 4.5.76 | Amplitude measurement auto-averaging display register   | . 138 |

| 4.5.77 | Amplitude measurement display register                  | . 138 |

| 4.5.78 | Phase measurement configuration register                | . 139 |

| 4.5.79 | Phase measurement reference register                    | . 139 |

| 4.5.80 | Phase measurement auto-averaging display register       | . 140 |

|   |      | 4.5.81     | Phase measurement display register             | 140 |

|---|------|------------|------------------------------------------------|-----|

|   |      | 4.5.82     | Measurement TX delay                           | 141 |

|   |      | 4.5.83     | IC identity register                           | 143 |

| 5 | Elec | trical cha | aracteristics                                  | 144 |

|   | 5.1  | Absolut    | e maximum ratings                              | 144 |

|   | 5.2  | Operati    | ng conditions                                  | 145 |

|   | 5.3  | DC/AC      | characteristics for digital inputs and outputs | 146 |

|   | 5.4  | Electric   | al specifications                              | 147 |

|   | 5.5  | SPI inte   | rface characteristics                          | 150 |

|   | 5.6  | I2C inte   | rface characteristics                          | 152 |

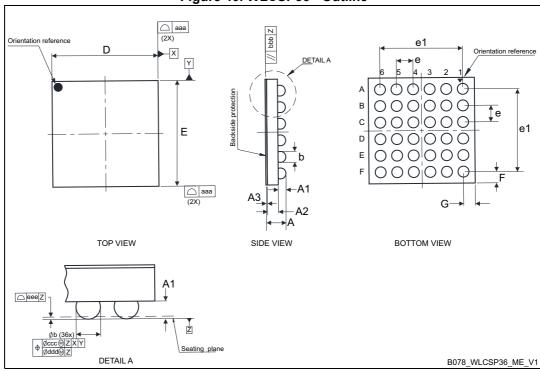

| 6 | Pacl | kage info  | rmation                                        | 157 |

|   | 6.1  | VFQFP      | N32 package information                        | 157 |

|   | 6.2  | WLCSF      | 36 package information                         | 159 |

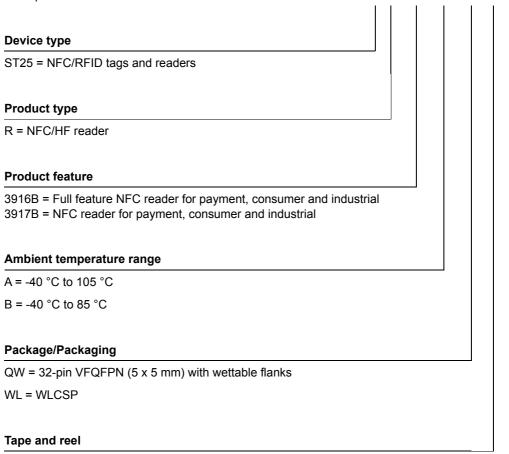

| 7 | Orde | ering info | ormation                                       | 161 |

| 8 | Revi | sion his   | ory                                            | 162 |

# List of tables

| Table 1.  | List of features                                                          | 11 |

|-----------|---------------------------------------------------------------------------|----|

| Table 2.  | ST25R3916B - VFQFPN32 and WLCSP36 pin assignment                          |    |

| Table 3.  | ST25R3917B VFQFPN32 pin assignment                                        |    |

| Table 4.  | RX channel selection                                                      |    |

| Table 5.  | Low-pass control                                                          | 27 |

| Table 6.  | First and third zero setting                                              |    |

| Table 7.  | Typical preset values for slow, medium and fast transients in OOK and ASK |    |

| Table 8.  | PT_Memory address space                                                   |    |

| Table 9.  | NFC-212/424k SENS_RES format                                              |    |

| Table 10. | IRQ output                                                                |    |

| Table 11. | Serial data interface (4-wire interface) signal lines                     |    |

| Table 12. | SPI operation modes                                                       |    |

| Table 13. | I2C interface and interrupt signal lines                                  |    |

| Table 14. | List of direct commands                                                   |    |

| Table 15. | Timing parameters of NFC field ON commands                                | 65 |

| Table 16. | Analog test and observation register 1                                    | 68 |

| Table 17. | Test access register - Signal selection of TAD1 and TAD2 pins             | 68 |

| Table 18. | List of registers - Space A                                               |    |

| Table 19. | List of registers - Space B                                               |    |

| Table 20. | IO configuration register 1                                               | 73 |

| Table 21. | IO configuration register 2                                               | 74 |

| Table 22. | Operation control register                                                | 75 |

| Table 23. | Mode definition register                                                  | 76 |

| Table 24. | Initiator operation modes                                                 | 76 |

| Table 25. | Target operation modes                                                    | 76 |

| Table 26. | Bit rate definition register                                              | 78 |

| Table 27. | Bit rate coding                                                           |    |

| Table 28. | ISO14443A and NFC 106kb/s settings register                               |    |

| Table 29. | Modulation pulse width                                                    | 79 |

| Table 30. | ISO14443B settings register 1                                             | 80 |

| Table 31. | ISO14443B and FeliCa settings register                                    | 81 |

| Table 32. | Minimum TR1 codings                                                       |    |

| Table 33. | NFCIP-1 passive target definition register                                | 82 |

| Table 34. | Stream mode definition register                                           | 83 |

| Table 35. | Sub-carrier frequency definition for Sub-Carrier stream mode              | 83 |

| Table 36. | Definition of time period for Stream mode Tx modulator control            | 83 |

| Table 37. | Auxiliary definition register                                             |    |

| Table 38. | EMD suppression configuration register                                    | 85 |

| Table 39. | Subcarrier start timer register                                           |    |

| Table 40. | Receiver configuration register 1                                         | 87 |

| Table 41. | Receiver configuration register 2                                         | 88 |

| Table 42. | Receiver configuration register 3                                         | 89 |

| Table 43. | Receiver configuration register 4                                         | 89 |

| Table 44. | P2P receiver configuration register 1                                     | 90 |

| Table 45. | OOK threshold level settings                                              |    |

| Table 46. | Correlator configuration register 1                                       | 91 |

| Table 47. | Correlator configuration register 2                                       | 92 |

| Table 48. | Mask receive timer register                                               | 93 |

| Table 49.  | No-response timer register 1                                            |       |

|------------|-------------------------------------------------------------------------|-------|

| Table 50.  | No-response timer register 2                                            | 94    |

| Table 51.  | Timer and EMV control register                                          | 95    |

| Table 52.  | Trigger sources                                                         | 95    |

| Table 53.  | General purpose timer register 1                                        |       |

| Table 54.  | General purpose timer register 2                                        | 96    |

| Table 55.  | PPON2 field waiting register                                            | 97    |

| Table 56.  | Squelch timer register                                                  | 98    |

| Table 57.  | NFC field on guard timer register                                       | 98    |

| Table 58.  | Mask main interrupt register                                            | 99    |

| Table 59.  | Mask timer and NFC interrupt register                                   |       |

| Table 60.  | Mask error and wake-up interrupt register                               | . 100 |

| Table 61.  | Mask passive target interrupt register                                  | . 100 |

| Table 62.  | Main interrupt register                                                 |       |

| Table 63.  | Timer and NFC interrupt register                                        |       |

| Table 64.  | Error and wake-up interrupt register                                    |       |

| Table 65.  | Passive target interrupt register                                       |       |

| Table 66.  | FIFO status register 1                                                  |       |

| Table 67.  | FIFO status register 2                                                  |       |

| Table 68.  | Collision display register                                              |       |

| Table 69.  | Passive target display register                                         |       |

| Table 70.  | Number of transmitted bytes register 1                                  |       |

| Table 71.  | Number of transmitted bytes register 2                                  |       |

| Table 72.  | Bit rate detection display register                                     |       |

| Table 73.  | A/D converter output register                                           |       |

| Table 74.  | Antenna tuning control register 1                                       |       |

| Table 75.  | Antenna tuning control register 2                                       |       |

| Table 76.  | TX driver register                                                      |       |

| Table 77.  | AM modulation index                                                     |       |

| Table 78.  | RFO driver resistance                                                   |       |

| Table 79.  | Auxiliary modulation setting register                                   |       |

| Table 80.  | Passive target modulation register                                      |       |

| Table 81.  | Passive target modulated and unmodulated state driver output resistance |       |

| Table 82.  | TX driver timing register                                               |       |

| Table 83.  | External field detector activation threshold register                   |       |

| Table 84.  | Resistive AM modulation register                                        |       |

| Table 85.  | Resistive AM modulated state driver output resistance                   |       |

| Table 86.  | External field detector deactivation threshold register                 |       |

| Table 87.  | Peer detection threshold as seen on RFI1 input.                         |       |

| Table 88.  | Collision avoidance threshold as seen on RFI1 input                     |       |

| Table 89.  | TX driver timing display register                                       |       |

| Table 90.  | Regulator voltage control register                                      |       |

| Table 91.  | Regulator display register                                              |       |

| Table 92.  | Regulated voltages                                                      |       |

| Table 93.  | RSSI display register                                                   |       |

| Table 94.  | RSSI                                                                    |       |

| Table 95.  | Gain reduction state register                                           |       |

| Table 96.  | AWS configuration 1                                                     |       |

| Table 90.  | AWS configuration 2                                                     |       |

| Table 98.  | Auxiliary display register                                              |       |

| Table 99.  | Overshoot protection configuration register 1                           |       |

| Table 100. | Overshoot protection configuration register 2                           |       |

| Table 100. | O voi on out proteotion domingulation regioter 2                        |       |

| Table 101. | Undershoot protection configuration register 1                     |

|------------|--------------------------------------------------------------------|

| Table 102. | Undershoot protection configuration register 2                     |

| Table 103. | Wake-up timer control register                                     |

| Table 104. | Typical wake-up time                                               |

| Table 105. | Amplitude measurement configuration register                       |

| Table 106. | Amplitude measurement reference register                           |

| Table 107. | AWS time 1 register                                                |

| Table 108. | AWS time 2 register                                                |

| Table 109. | AWS time 3 register                                                |

| Table 110. | AWS time 4 register                                                |

| Table 111. | AWS time 5 register                                                |

| Table 112. | AWS time 6 register                                                |

| Table 113. | Amplitude measurement auto-averaging display register              |

| Table 114. | Amplitude measurement display register                             |

| Table 115. | Phase measurement configuration register                           |

| Table 116. | Phase measurement reference register                               |

| Table 117. | Phase measurement auto-averaging display register                  |

| Table 118. | Phase measurement display register                                 |

| Table 119. | Measurement TX delay141                                            |

| Table 120. | Wake-up time and wake-up pulse prolongation                        |

| Table 121. | IC identity register                                               |

| Table 122. | Absolute maximum ratings                                           |

| Table 123. | Operating conditions                                               |

| Table 124. | Characteristics of CMOS I/Os146                                    |

| Table 125. | ST25R3916B and ST25R3917B electrical characteristics (VDD = 3.3 V) |

| Table 126. | ST25R3916B and ST25R3917B electrical characteristics (VDD = 5.5 V) |

| Table 127. | ST25R3916B and ST25R3917B electrical characteristics (VDD = 2.4 V) |

| Table 128. | SPI characteristics (5 MHz)                                        |

| Table 129. | SPI characteristics (5 MHz < 1/TSCLK < 10 MHz)                     |

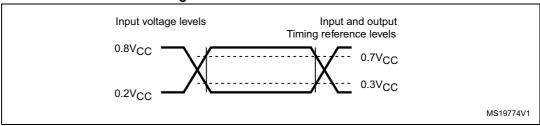

| Table 130. | AC measurement conditions                                          |

| Table 131. | AC measurement conditions - I2C configuration                      |

| Table 132. | Input parameters152                                                |

| Table 133. | DC characteristics152                                              |

| Table 134. | 100 kHz AC characteristics                                         |

| Table 135. | 400 kHz AC characteristics                                         |

| Table 136. | 1 MHz AC characteristics                                           |

| Table 137. | 3.4 MHz AC characteristics                                         |

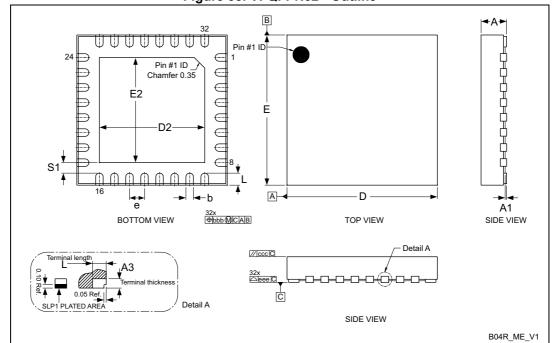

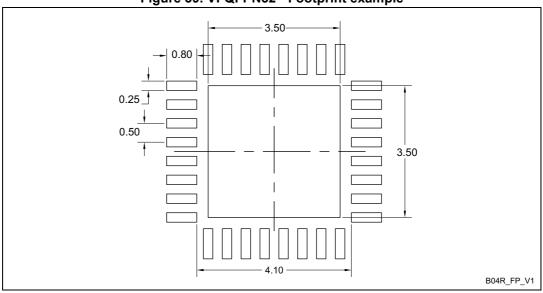

| Table 138. | VFQFPN32 - Mechanical data                                         |

| Table 139. | WLCSP36 - Mechanical data                                          |

| Table 140. | Ordering information scheme                                        |

| Table 141. | Document revision history                                          |

DS13541 Rev 6 9/163

# **List of figures**

| Figure 1.  | Minimum system configuration - Single sided antenna driving    |    |

|------------|----------------------------------------------------------------|----|

| Figure 2.  | Minimum system configuration - Differential antenna driving    |    |

| Figure 3.  | ST25R3916B and ST25R3917B block diagram                        |    |

| Figure 4.  | ST25R3916B QFN32 pinout (top view)                             |    |

| Figure 5.  | ST25R3917B QFN32 pinout (top view)                             | 19 |

| Figure 6.  | ST25R3916B WLCSP36 (top view)                                  |    |

| Figure 7.  | Receiver block diagram                                         |    |

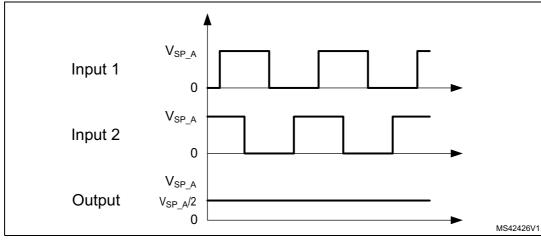

| Figure 8.  | Phase detector inputs and output in case of 90° phase shift    | 36 |

| Figure 9.  | Phase detector inputs and output in case of 135° phase shift   |    |

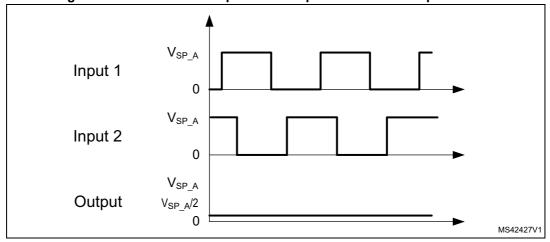

| Figure 10. | ST25R3916B and ST25R3917B power supply system                  | 38 |

| Figure 11. | AWS mechanism                                                  |    |

| Figure 12. | Bit and timing relation for OOK waveform                       |    |

| Figure 13. | Bit and timing relation for ASK waveform                       | 14 |

| Figure 14. | Exchange of signals with a microcontroller                     | 52 |

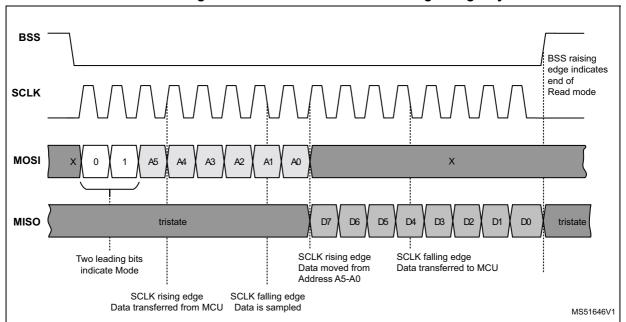

| Figure 15. | SPI communication: writing a single byte                       | 53 |

| Figure 16. | SPI communication: writing multiple bytes                      | 54 |

| Figure 17. | SPI communication: reading a single byte                       | 54 |

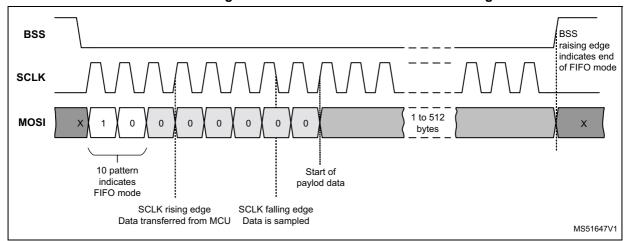

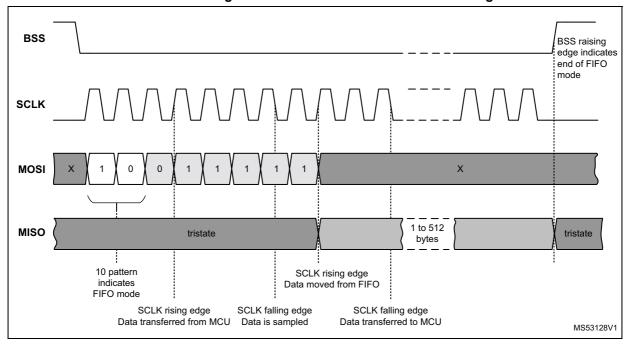

| Figure 18. | SPI communication: FIFO loading                                | 55 |

| Figure 19. | SPI communication: FIFO reading                                | 56 |

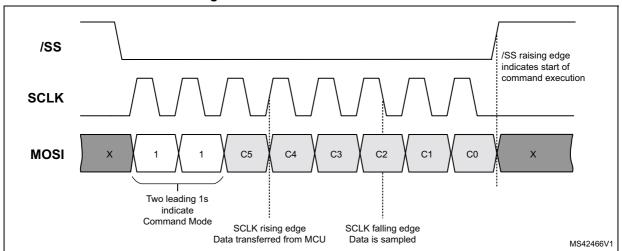

| Figure 20. | SPI communication: direct command                              | 56 |

| Figure 21. | SPI communication: direct command chaining                     | 57 |

| Figure 22. | Writing a single register                                      | 58 |

| Figure 23. | Writing register data with auto-incrementing address           | 58 |

| Figure 24. | Reading a single byte from a register                          | 58 |

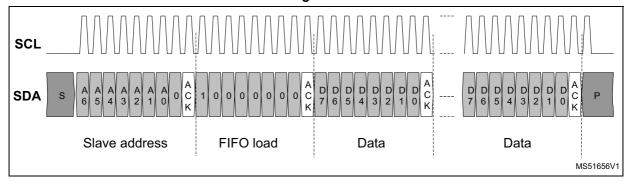

| Figure 25. | FIFO load                                                      | 59 |

| Figure 26. | FIFO read                                                      | 59 |

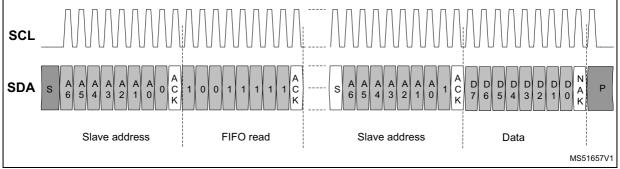

| Figure 27. | Sending a direct command                                       | 30 |

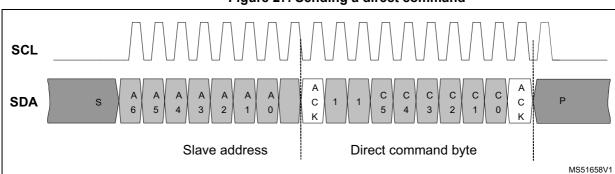

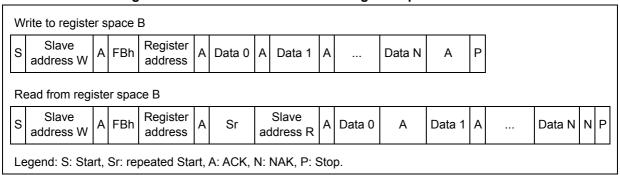

| Figure 28. | Read and Write mode for register space-B access                | 30 |

| Figure 29. | I2C master reads slave immediately after the first byte        |    |

| Figure 30. | Direct command NFC initial field ON                            | 35 |

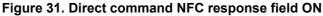

| Figure 31. | Direct command NFC response field ON                           | 35 |

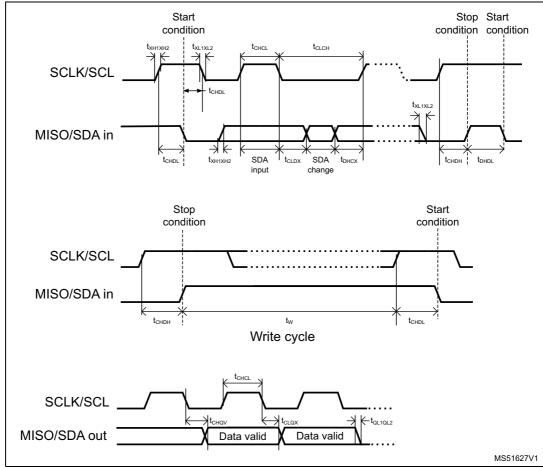

| Figure 32. | SPI timing diagram - General operation                         | 51 |

| Figure 33. | SPI timing diagram - Read operation                            | 51 |

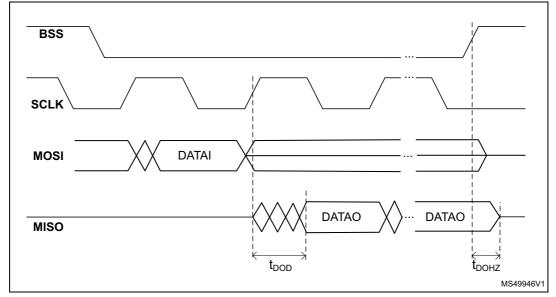

| Figure 34. | RPmin vs. VDD, fc = 3.4 MHz                                    | 55 |

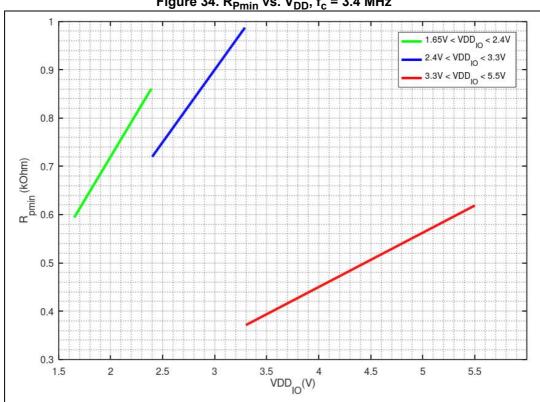

| Figure 35. | Maximum Rbus value vs. bus parasitic capacitance, fc = 3.4 MHz | 55 |

| Figure 36. | I2C AC waveforms                                               | 56 |

| Figure 37. | I2C AC measurements                                            | 56 |

| Figure 38. | VFQFPN32 - Outline                                             | 57 |

| Figure 39. | VFQFPN32 - Footprint example                                   | 58 |

| Figure 40. | WLCSP36 - Outline                                              |    |

| Figure 41. | WLCSP36 - Footprint example                                    | 30 |

|            |                                                                |    |

## 1 Applications

The ST25R3916B and ST25R3917B devices are suitable for a wide range of NFC and HF RFID applications, among them

- NFC Forum compliant NFC universal device

- EMVCo 3.1a compliant contactless payment terminal

- ISO14443 and ISO15693 compliant general purpose NFC device

- FeliCa™ reader / writer

- Support all five NFC Forum Tag types in reader mode

- Support all common proprietary protocols, such as Kovio, CTS, B'.

The main differences between the two devices are detailed in *Table 1*.

Table 1. List of features

| Feature                                        | ST25R3916B                                                                             | ST25R3917B |  |

|------------------------------------------------|----------------------------------------------------------------------------------------|------------|--|

| ISO/IEC 14443 Type-A                           | Yes                                                                                    |            |  |

| ISO/IEC 14443 Type-B                           | Yes                                                                                    |            |  |

| ISO/IEC 15693                                  | Ye                                                                                     | es         |  |

| FeliCa™                                        | Ye                                                                                     | es         |  |

| NFC Tag read support                           | NFC Type 1 Tag<br>NFC Type 2 Tag<br>NFC Type 3 Tag<br>NFC Type 4 Tag<br>NFC Type 5 Tag |            |  |

| ISO/IEC 18092 Passive Initiator mode           | Yes                                                                                    |            |  |

| ISO/IEC 18092 Passive Target mode              | Yes                                                                                    | No         |  |

| ISO/IEC 18092 Active Initiator and Target mode | Yes                                                                                    | No         |  |

| Automatic antenna tuning (AAT)                 | Yes                                                                                    | No         |  |

| Card emulation                                 | Yes No                                                                                 |            |  |

| Inductive sensor wakeup                        | Ye                                                                                     | es         |  |

## 2 Description

The ST25R3916B and ST25R3917B are high performance NFC universal devices supporting NFC initiator, NFC target, NFC reader and NFC card emulation modes when applicable.

Being fully compliant with EMVCo 3.1a analog and digital, this NFC IC is optimized for POS terminal applications, and enables fast EMVCo certification cycles, even under harsh conditions, with antenna around noisy LCD displays.

The ST25R3916B device includes an advanced analog front end (AFE) and a highly integrated data framing system for ISO 18092 passive and active initiator, ISO 18092 passive and active target, NFC-A/B (ISO 14443A/B) reader including higher bit rates, NFC-F (FeliCa™) reader, NFC-V (ISO 15693) reader up to 53 kbps, and NFC-A / NFC-F card emulation. The ST25R3917B provides a reduced feature set compared to the ST25R3916B.

Special stream and transparent modes of the AFE and framing system is used to implement other custom protocols in reader or card emulation mode.

The ST25R3916B and ST25R3917B feature high RF output power to directly drive antennas at high efficiency.

The ST25R3916B and ST25R3917B include additional features, making them incomparable for low power applications. The presence of a card is detected by performing a measurement of the amplitude or phase of the antenna signal. They also contain a low power RC oscillator and wake-up timer to automatically wake-up the ST25R3916B and ST25R3917B after a selected time period and check for a presence of a tag using one or more techniques of low power detection of card presence (phase or amplitude).

The ST25R3916B and ST25R3917B are designed to operate from a wide power supply range (2.6 to 5.5 V from -40 °C to +105 °C, 2.4 to 5.5 V from -20 °C to +105 °C), and a wide peripheral IO voltage range (from 1.65 to 5.5 V).

Due to this combination of high RF output power, low power modes and wide supply range these devices are perfectly suited for infrastructure NFC applications.

## 2.1 System diagram

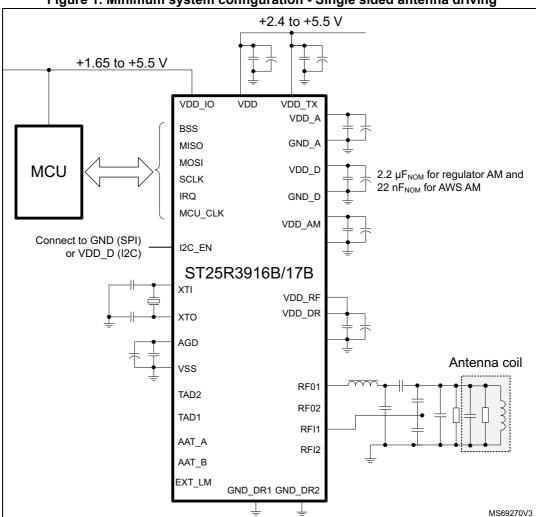

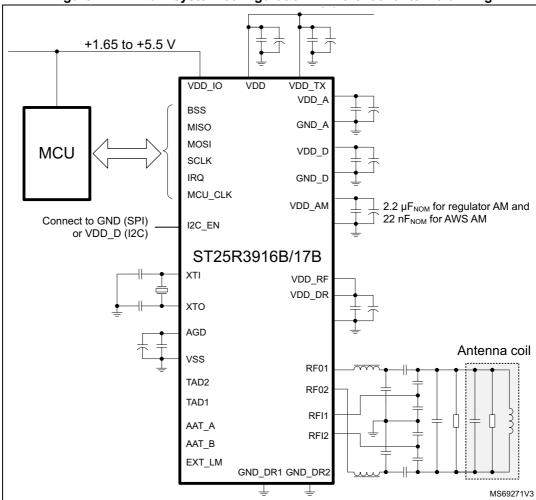

*Figure 1* and *Figure 2* show the minimum system configuration for, respectively, single ended and differential antenna configurations. Both include the EMC filter.

Figure 1. Minimum system configuration - Single sided antenna driving

Figure 2. Minimum system configuration - Differential antenna driving

4

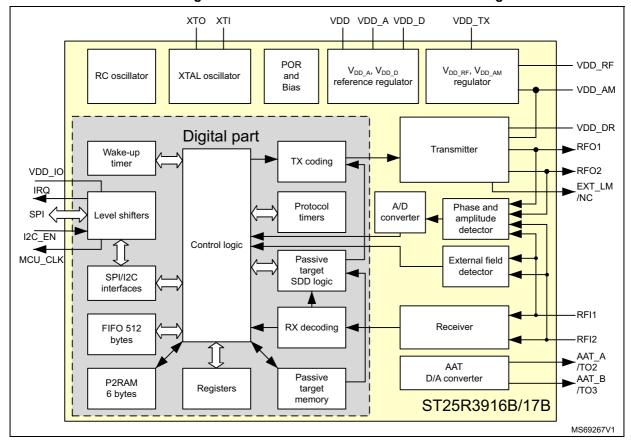

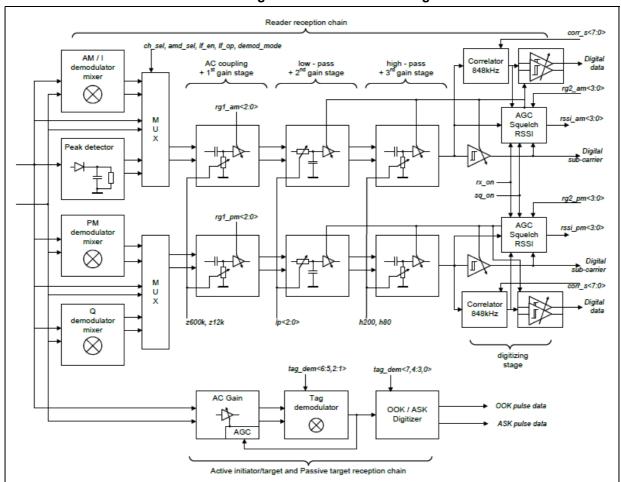

## 2.2 Block diagram

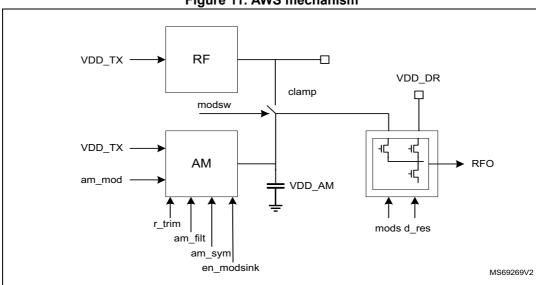

The ST25R3916B and ST25R3917B block diagram is shown in *Figure 3*, the main functions are described in the following subsections.

Figure 3. ST25R3916B and ST25R3917B block diagram

### 2.2.1 Transmitter

In reader mode the transmitter drives an external antenna through pins RFO1 and RFO2 to generate the RF field. Single sided and differential antenna configurations are supported. The transmitter block also generates the OOK or AM modulation of the transmitted RF signal.

The transmitter can either operate RFO1 and RFO2 independently to drive up to two antennas in single ended configuration or operate RFO1 and RFO2 combined to drive one antenna in differential configuration. The drivers are designed to directly drive antenna(s) integrated on the PCB as well as antennas connected with 50  $\Omega$  cables. Some of the advanced features (such as antenna diagnostics) are not fully usable if the antenna is connected with a 50  $\Omega$  cable.

In card emulation mode the transmitter generates the load modulation signal by changing the resistance of the internal antenna driver connected to the antenna via RFO1 and RFO2. The transmitter can also drive an external MOS transistor via the EXT\_LM pin to generate the load modulation signal.

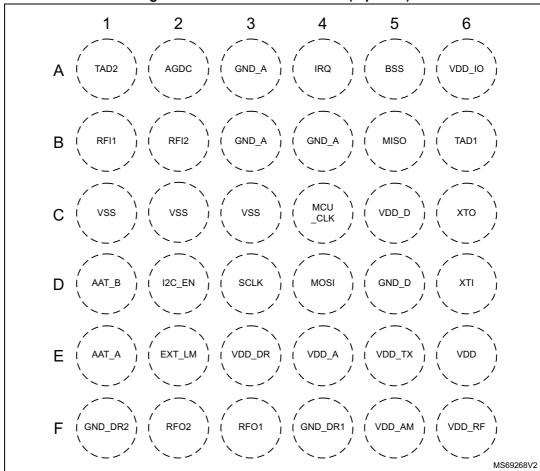

#### 2.2.2 Receiver

The receiver detects card modulation superimposed on the 13.56 MHz carrier signal. The receiver consists of two receive chains that are built from a set of demodulators, followed by two gain and filtering stages and a final digitizer stage. The demodulators operate as AM/PM demodulator or as I/Q demodulator. The filter characteristics can be adjusted to match the selected RF mode and bit rate to optimize performance (subcarrier frequencies from 212 to 848 kHz are supported). Apart from the filter stage the receiver incorporates several other features (AGC, squelch) that enable reliable operation in noisy conditions.

The receiver is connected to the antenna via the pins RFI1 and RFI2. The output of the receiver is connected to the framing block that decodes the demodulated and digitized subcarrier signal.

## 2.2.3 Phase and amplitude detector

The phase detector measures the phase difference between the transmitter output signals (RFO1 and RFO2) and the receiver input signals (RFI1 and RFI2).

The amplitude detector measures the amplitude of the differential RF carrier signal between the receiver inputs RFI1 and RFI2. This differential amplitude signal is directly proportional to the amplitude of the RF signal on the antenna LC tank.

The phase- and amplitude detectors are used for several purposes:

- PM demodulation, by observing RFI1 and RFI2 phase variations (LF signal is fed to the receiver)

- Average phase difference between RFOx pins and RFIx pins, to check antenna tuning

- Measure amplitude of signal present on pins RFI1 and RFI2, proportional to the antenna voltage

## 2.2.4 Automatic antenna tuning (AAT)

The AAT block consists of two independent 8-bit D/A converters. These converters generate a programmable voltage (from 0 to 3.3 V) to control external variable capacitors.

#### 2.2.5 A/D converter

The ST25R3916B and ST25R3917B feature a built in A/D converter. Their input can be multiplexed from different sources and it is used for the diagnostic functions and the low power card detection. The result of the A/D conversion is stored in a register that can be read through the host interface.

#### 2.2.6 External field detector

This is a low power block used in the active or passive target mode to detect the presence of an external RF field. It supports two different external field detection thresholds, namely Peer detection and Collision avoidance threshold.

The Peer detection threshold is used in the active and passive peer to peer modes to detect when the peer device turns on its RF field.

The Collision avoidance threshold is used to detect the presence of an external RF field during the RF collision avoidance procedure.

## 2.2.7 Quartz crystal oscillator

The quartz crystal oscillator operates with 27.12 MHz crystals. At start-up the transconductance of the oscillator is increased to achieve a fast start-up. Since the start-up time varies with crystal type, temperature and other parameters, the oscillator amplitude is observed and an interrupt is generated when stable oscillator operation is reached.

The oscillator block also provides a clock signal to the external microcontroller (MCU\_CLK), according to the settings in the *IO configuration register 1*.

## 2.2.8 Power supply regulators

The integrated power supply regulators ensures a high power supply rejection ratio (PSRR) for the complete system.

Three voltage regulators, one for the analog block, one for the digital block, and one for the RF output drivers, are available to decouple noise sources from the ST25R3916B and ST25R3917B. A fourth voltage regulator generates the reference voltage for the analog receivers (AGDC, analog ground).

The RF output driver voltage regulator is configured automatically by the ST25R3916B and ST25R3917B based on the systems power supply stability and RF output power (see *Section 4.4.10: Adjust regulators* for more details).

#### 2.2.9 POR and bias

This block provides bias currents and reference voltages to all other blocks. It also incorporates a Power on Reset (POR) circuit that provides a reset at power-up and at low supply levels.

## 2.2.10 RC oscillator and Wake-up timer

The ST25R3916B and ST25R3917B have two possibilities for low power detection of a card presence (phase measurement, amplitude measurement). The RC oscillator and the register configurable Wake-up timer are used to periodically trigger the card presence detection in the low power card detection modes.

## 2.2.11 TX encoding

This block encodes the transmit frames according to the selected RF mode and bit rate. The SOF (start of frame), EOF (end of frame), CRC and parity bits are generated automatically. The data to transmit are taken from the FIFO.

In Stream mode the framing is bypassed. The FIFO data directly defines the modulation data sent to the transmitter.

In Transparent mode, the framing and FIFO are bypassed, and the MOSI pin directly drives the modulation of the transmitter.

## 2.2.12 RX decoding

This block decodes received frames according to the selected RF mode and bitrate. The received data is written to the FIFO.

In Stream mode the framing is bypassed. The digitized subcarrier signal is directly stored in the FIFO.

4

DS13541 Rev 6 17/163

In Transparent mode the framing and FIFO are bypassed. The digitized subcarrier signal directly drives the MISO pin.

### 2.2.13 FIFO

The ST25R3916B and ST25R3917B contain a 512-byte FIFO. Depending on the direction of the data transfer, it contains either data which has been received or data which is to be transmitted.

In reader mode the ST25R3916B and ST25R3917B can transmit frames of up to 8191 bytes length and receive frames of arbitrary length.

## 2.2.14 Control logic

The control logic contains I/O registers that define the operation of device.

#### 2.2.15 Host interface

A 4-wire serial peripheral interface (SPI) and a 2-wire I2C interface are available to communicate with an external microcontroller. The pins for the SPI and the I2C interface are shared, and pin I2C EN is used to select the active interface.

## 2.2.16 Passive target memory

The device contains a 48-byte RAM to store configuration data for the passive target and card emulation mode.

### 2.2.17 P2RAM

The P2RAM stores information on wafer number, die position, device subversion, and I2C address. The P2RAM is programmed during production.

## 3 Pin and signal description

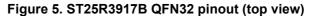

MCU CLK GND FAD1 AGDC VDD\_IO RFI2 TAD2 RFI1 VDD\_D 22 хто vss VFQFPN32 XTI I2C\_EN GND\_D AAT\_B VDD\_A AAT\_A 33 l VDD EXT\_LM VDD\_RF VDD\_TX VDD\_AM VDD\_DR RF02 GND\_DR1 RF01 GND\_DR2 MS68598V2

Figure 4. ST25R3916B QFN32 pinout (top view)

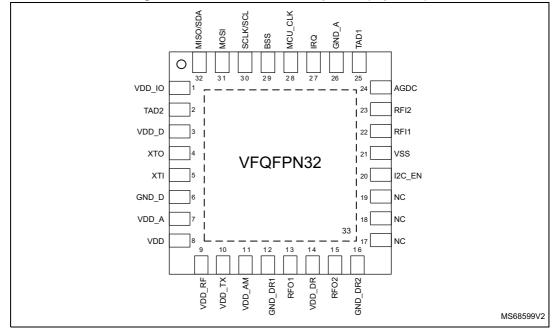

Figure 6. ST25R3916B WLCSP36 (top view)

Table 2. ST25R3916B - VFQFPN32 and WLCSP36 pin assignment

| VFQFPN32 | WLCSP | Name    | Type <sup>(1)</sup> | Description                                                          |

|----------|-------|---------|---------------------|----------------------------------------------------------------------|

| 1        | A6    | VDD_IO  | Р                   | Positive supply for peripheral communication                         |

| 2        | В6    | TAD1    | AO                  | Test output 2                                                        |

| 3        | C5    | VDD_D   | AO                  | Digital supply regulator output                                      |

| 4        | C6    | XTO     | AO                  | Crystal oscillator output                                            |

| 5        | D6    | XTI     | AI/DI               | Crystal oscillator input, in test mode used as digital input (clock) |

| 6        | D5    | GND_D   | Р                   | Digital ground                                                       |

| 7        | E4    | VDD_A   | AO                  | Analog supply regulator output                                       |

| 8        | E6    | VDD     | Р                   | External positive supply                                             |

| 9        | F6    | VDD_RF  | AO                  | Regulated driver supply for antenna drivers                          |

| 10       | E5    | VDD_TX  | Р                   | External positive supply for the TX part                             |

| 11       | F5    | VDD_AM  | AO                  | Regulated driver supply for AM modulation                            |

| 12       | F4    | GND_DR1 | Р                   | Antenna driver ground, including driver V <sub>SS</sub>              |

Table 2. ST25R3916B - VFQFPN32 and WLCSP36 pin assignment (continued)

| VFQFPN32 | WLCSP      | Name    | Type <sup>(1)</sup> | Description                                             |

|----------|------------|---------|---------------------|---------------------------------------------------------|

| 13       | F3         | RFO1    | AO                  | Antenna driver output                                   |

| 14       | E3         | VDD_DR  | Р                   | Antenna driver positive supply input                    |

| 15       | F2         | RFO2    | AO                  | Antenna driver output                                   |

| 16       | F1         | GND_DR2 | Р                   | Antenna driver ground, including driver V <sub>SS</sub> |

| 17       | E2         | EXT_LM  | AO                  | External load modulation MOS gate driver                |

| 18       | E1         | AAT_A   | AO                  | AAT tune voltage for variable capacitor AAT_A           |

| 19       | D1         | AAT_B   | AO                  | AAT tune voltage for variable capacitor AAT_B           |

| 20       | D2         | I2C_EN  | DI                  | I2C interface enable                                    |

| 21       | C1, C2, C3 | VSS     | Р                   | Ground, die substrate potential                         |

| 22       | B1         | RFI1    | Al                  | Receiver input                                          |

| 23       | B2         | RFI2    | Al                  | Receiver input                                          |

| 24       | A2         | AGDC    | AIO                 | Analog reference voltage                                |

| 25       | A1         | TAD2    | AIO                 | Test output 1                                           |

| 26       | A3, B3, B4 | GND_A   | Р                   | Analog ground                                           |

| 27       | A4         | IRQ     | DO                  | Interrupt request output                                |

| 28       | C4         | MCU_CLK | DO                  | Clock output for MCU                                    |

| 29       | A5         | BSS     | DI                  | SPI enable (active low)                                 |

| 30       | D3         | SCLK    | DI                  | SPI clock / I2C clock                                   |

| 31       | D4         | MOSI    | DI                  | SPI data input                                          |

| 32       | B5         | MISO    | DO_T                | Serial peripheral interface data output / I2C data line |

| 33       | NA         | NA      | Р                   | Thermal pad (GND)                                       |

Table 3. ST25R3917B VFQFPN32 pin assignment

| VFQFPN32 | Name   | Type <sup>(1)</sup> | Description                                                          |

|----------|--------|---------------------|----------------------------------------------------------------------|

| 1        | VDD_IO | Р                   | Positive supply for peripheral communication                         |

| 2        | TAD2   | AO/DO               | Test analog digital                                                  |

| 3        | VDD_D  | AO                  | Digital supply regulator output                                      |

| 4        | XTO    | AO                  | Crystal oscillator output                                            |

| 5        | XTI    | AI/DI               | Crystal oscillator input, in test mode used as digital input (clock) |

| 6        | GND_D  | Р                   | Digital ground                                                       |

| 7        | VDD_A  | AO                  | Analog supply regulator output                                       |

| 8        | VDD    | Р                   | External positive supply                                             |

| 9        | VDD_RF | AO                  | Regulated driver supply for antenna drivers                          |

DS13541 Rev 6 21/163

P: Power supply pin

AIO: analog I/O, AI: analog input, AO: analog output

DI: digital input, DIPD: digital input with pull-down, DO: digital output, DO\_T: digital output/tri-state, DIO: digital bidirectional.

Table 3. ST25R3917B VFQFPN32 pin assignment (continued)

| Table 5. 51251755 VI QI I 1152 pili assignment (Continued) |         |                     |                                                         |  |

|------------------------------------------------------------|---------|---------------------|---------------------------------------------------------|--|

| VFQFPN32                                                   | Name    | Type <sup>(1)</sup> | Description                                             |  |

| 10                                                         | VDD_TX  | Р                   | External positive supply for the TX part                |  |

| 11                                                         | VDD_AM  | AO                  | Regulated driver supply for AM modulation               |  |

| 12                                                         | GND_DR1 | Р                   | Antenna driver ground, including driver V <sub>SS</sub> |  |

| 13                                                         | RFO1    | AO                  | Antenna driver output                                   |  |

| 14                                                         | VDD_DR  | Р                   | Antenna driver positive supply input                    |  |

| 15                                                         | RFO2    | AO                  | Antenna driver output                                   |  |

| 16                                                         | GND_DR2 | Р                   | Antenna driver ground, including driver V <sub>SS</sub> |  |

| 17                                                         | NC      | ı                   | Pin must be not connected                               |  |

| 18                                                         | NC      | 1                   | Pin must be not connected                               |  |

| 19                                                         | NC      | 1                   | Pin must be not connected                               |  |

| 20                                                         | I2C_EN  | DI                  | I2C interface enable (VDD_D level)                      |  |

| 21                                                         | VSS     | Р                   | Ground, die substrate potential                         |  |

| 22                                                         | RFI1    | Al                  | Receiver input                                          |  |

| 23                                                         | RFI2    | Al                  | Receiver input                                          |  |

| 24                                                         | AGDC    | AIO                 | Analog reference voltage                                |  |

| 25                                                         | TAD1    | AO/DO               | Test analog digital                                     |  |

| 26                                                         | GND_A   | Р                   | Analog ground                                           |  |

| 27                                                         | IRQ     | DO                  | Interrupt request output                                |  |

| 28                                                         | MCU_CLK | DO                  | Clock output for MCU                                    |  |

| 29                                                         | BSS     | DI                  | SPI enable (active low)                                 |  |

| 30                                                         | SCLK    | DI                  | SPI clock / I2C clock                                   |  |

| 31                                                         | MOSI    | DI                  | SPI data input                                          |  |

| 32                                                         | MISO    | DO_T                | Serial peripheral interface data output / I2C data line |  |

| 33                                                         | NA      | Р                   | Thermal pad (GND)                                       |  |

P: Power supply pin

AlO: analog I/O, Al: analog input, AO: analog output, DI: digital input,

DIPD: digital input with pull-down, DO: digital output, DO\_T: digital output/tri-state, DIO: digital bidirectional.

## 4 Application information

## 4.1 Power-on sequence

Once powered, the device enters the Power-down mode where the content of all registers is set to its default state.

The next steps are basic configurations of the IC:

- 1. The *IO configuration register 1* and *IO configuration register 2* must be properly configured.

- 2. The internal voltage regulators have to be configured. It is recommended to use direct command Adjust regulators to improve the system PSRR.

- 3. If AAT is used the tuning procedure must be performed.

- 4. After device power-on and direct command set default, release the direct command Trigger RC calibration.

After the sequence of events mentioned above the devices are ready to operate.

## 4.2 Operating modes

The ST25R3916B and ST25R3917B operating mode is defined by the contents of the *Operation control register*. At power-on all its bits are set to 0, the ST25R3916B and ST25R3917B are in Power-down mode. In this mode, the AFE static power consumption is minimized, as only the POR and part of the bias are active. The regulator itself is disabled.

The SPI/I2C is still functional in this mode and all required settings on the configuration registers can be done. The PT\_memory and FIFO are not accessible in this mode.

Bit en (bit 7 of the *Operation control register*) is controlling the quartz crystal oscillator, regulators and AAT control output pins. When this bit is set, the device enters in Ready mode and the quartz crystal oscillator and regulators are enabled. An interrupt is sent to inform the microcontroller when the oscillator amplitude and frequency is stable. The PT\_memory and FIFO are accessible in this mode.

The enable of the receiver and the transmitter block are separated, it is possible to operate one without switching on the other (control bits rx\_en and tx\_en). This feature is used when the reader field has to be maintained while no response from a tag is expected. Another example is NFCIP-1 active communication in receive mode configuration. The RF field is generated by the initiator on one side while the other side is only in receive operation.

Asserting the *Operation control register* bit wu while the other bits are set to 0 puts the ST25R3916B and ST25R3917B into the Wake-up mode that is used to perform low power detection of card presence. In this mode the low power RC oscillator and register configurable wake-up timer are used to schedule periodic measurement(s). When a difference to the predefined reference is detected an interrupt is sent to wake-up the MCU. Phase and amplitude measurement are available to trigger the wake-up.

DS13541 Rev 6 23/163

#### 4.2.1 Transmitter

The transmitter contains two identical push-pull driver blocks connected to pins RFO1 and RFO2. These drivers are differentially driving the external antenna LC tank. It is also possible to operate only one of the two drivers by setting the *IO configuration register 1* bit single and selecting which RFO/RFI to be use on bit rfo2.

#### **Output resistance**

Each driver is composed of eight segments having binary weighted output resistance. The MSB segment typical ON resistance is 4  $\Omega$ . When all segments are turned on, the output resistance is typically 2  $\Omega$ . Usually all segments are turned on to define the normal transmission (non-modulated) level. It is also possible to switch off certain MSB segments when driving the non-modulated level to drive the circuitry with a higher impedance driver.

The bits d\_res<3:0> in the *TX driver register* define the resistance during the normal transmission. The default setting is minimum available resistance.

When using the single driver mode, the number and therefore the cost of the antenna LC tank components is halved, but also the output power is reduced. In single mode it is possible to connect two antenna LC tanks to the two RFO outputs and multiplex between them by controlling the *IO configuration register 1* bit rfo2.

To transmit data, the transmitter output level needs to be modulated. AM and OOK modulation principles are supported. The type of modulation is defined by setting bit tr\_am in the *Mode definition register*.

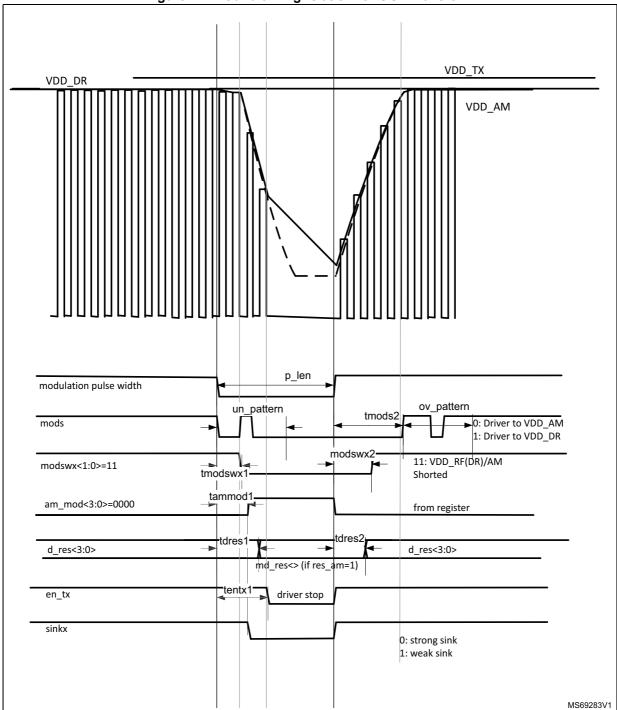

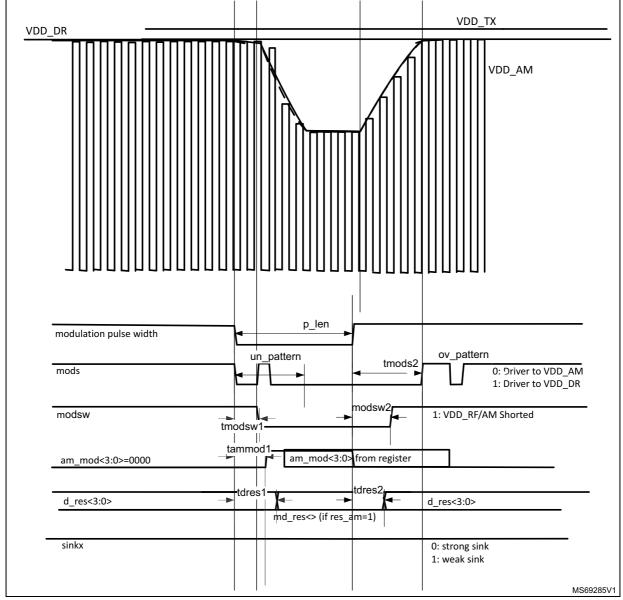

#### **Driver TX modulation**

During the OOK modulation (e.g. for ISO14443A) the transmitter drivers stop driving the carrier frequency. As a consequence the amplitude of the antenna LC tank oscillation decays, the time constant of the decay is defined with the LC tank Q factor.

AM modulation (for example ISO14443B) is done via an additional regulator providing the supply voltage  $V_{DD\ AM}$ , used as the driver supply voltage during the modulation state.

The AM modulation level is set by am\_mod3:0 bits in the TX driver register.

AM modulation has to be manually enabled and the level to be set correctly for the following protocols:

- ISO14443B

- FeliCa

- ISO15693 (if not OOK)

- NFCIP-1 212 and 424 kb/s initiator or active target.

Depending on the applicable standard the modulation index is set in a range between 0 and 82% in the *TX driver register*.

## **Passive load modulation**

The ST25R3916B and ST25R3917B enable passive load modulation using two different methods

- Internal driver load modulation

- Load modulation with an external MOS transistor and a diode that directly loads the antenna circuit

The driver load modulation is selected by bit Im\_dri and the external MOS modulation is selected by Im\_ext option bits.

Normally, the internal driver or the external load modulation should be used exclusively, but the device also allows simultaneous modulation.

The driver load modulation is based on the change of driver impedance. Typically, a high impedance during non-modulated state and a lower impedance for the modulated state is used. This yields modulation phase equal to passive tag modulation. It is also possible to reverse the polarity of the driver load modulation by using low impedance during non-modulated state and higher impedance for the modulated state.

During the non-modulated state the output impedance is defined by pt\_res3:0 option bits. During modulation the output impedance is defined by ptm\_res3:0 option bits.

Load modulation through an external MOS transistor and a diode is selected by the Im\_ext option bit. In this case the EXT\_LM pin is driven by the digital representation of the load modulation signal (848 kHz subcarrier or 424 / 212 kHz modulation signal). The EXT\_LM is used to drive a gate of the external modulation MOS. The bit Im\_ext\_pol sets inverse polarity for the external load modulation.

The pt\_res3:0 and ptm\_res3:0 bits must be set prior entering passive target mode (reg 03h), because in passive target mode the resistance value propagates through the TX driver only when the extracted clock is available.

Driver load modulation is based on change of the driver impedance. Typically high impedance is used during non-modulated state, and decreased for modulated state, resulting in modulation phase equal to Passive tag modulation.

It is also possible to set inverse polarity driver load modulation by using low impedance during non-modulated state and higher impedance for the modulated state.

During non-modulated / modulated state the output impedance is defined, respectively, by pt res3:0 / ptm res3:0 option bits.

An external MOS transistor and a diode modulation is selected by Im\_ext option bit. In this case the EXT\_LM pin is driven by digital representation of the load modulation signal (848 kHz subcarrier or 424 / 212 kHz modulation signal). The EXT\_LM is used to drive a gate of the external modulation MOS.

Bit Im\_ext\_pol sets inverse polarity for the External load modulation.

Bits pt\_res<3:0> and ptm\_res<3:0> must be set before entering Passive target mode (reg 03h), as in Passive target mode the resistance value propagates through the TX driver only when extracted clock is available (during PT data transmission, including FDT).

### 4.2.2 Receiver

The receiver performs demodulation of the tag subcarrier modulation that is superimposed on the 13.56 MHz carrier frequency. It performs AM/PM or I/Q demodulation, amplification, band-pass filtering and digitalization of subcarrier signals. It also performs RSSI measurement, automatic gain control (AGC) and Squelch function.

The reception chain has two separate channels for AM and PM demodulation. When both channels are active the selection for reception framing is done automatically by the receiver logic. The receiver is switched on when *Operation control register* bit rx\_en is set to 1.

DS13541 Rev 6 25/163

The *Operation control register* contains bits rx\_chn and rx\_man, which define whether only one or both demodulation channels are active:

- bit rx\_man defines the channel selection mode when both channels are active (automatic or manual)

- bit ch\_sel defines which channel is used for decoding.

Table 4. RX channel selection

| rx_chn | rx_man | ch_sel | Selected reception channel |

|--------|--------|--------|----------------------------|

| 0      | 0      | х      | Automatic selection        |

| 0      | 1      | 0      | AM or I channel            |

| 0      | 1      | 1      | PM or Q channel            |

| 1      | х      | 0      | AM or I channel            |

| 1      | х      | 1      | PM or Q channel            |

Figure 7. Receiver block diagram

4

### **Demodulation stage**

The first stage performs demodulation of the tag subcarrier response signal, superimposed on the HF field carrier. Two different blocks are implemented for the AM demodulation:

- peak detector

- AM/I or PM/Q demodulator mixer.

The choice of the used demodulator is made by the *Receiver configuration register 2* bit amd\_sel.

The peak detector performs AM demodulation using a peak follower. Both the positive and negative peaks are tracked to suppress any common mode signals. Its demodulation gain is G = 0.7 and the input is taken from RFI1 demodulator input only.

The AM demodulator mixer uses synchronous rectification of both receiver inputs (RFI1 and RFI2). Its gain is G = 0.55. The PM demodulation is also done by a mixer. The PM demodulator mixer has differential outputs with 60 mV differential signal for 1% phase change (16.67 mV / °).

The I/Q demodulation is composed of two mixer circuits, driven with a 90° shifted local oscillator (LO) signals derived from the crystal oscillator. The outputs of the two mixers are connected to two equal base band reception chains and to the decoding logic.

### Filtering and gain stages

The receiver chain has band pass filtering characteristics. The filtering is optimized to pass subcarrier frequencies while rejecting carrier frequency, low frequency noise and DC component. Filtering and gain is implemented in three stages, the first and the last stage have first order high pass characteristics while the mid stage has second order low-pass characteristic.

The gain and filtering characteristics can be optimized depending on the application by writing the *Receiver configuration register 1* (filtering), *Receiver configuration register 3* (primarily gain in first stage) and *Receiver configuration register 4* (gain in second and third stage).

The gain of first stage is around 20 dB and can be reduced in six 2.5 dB steps. There is also a special boost mode available, which increases the max gain by additional 5.5 dB. The first stage gain can only be modified by writing *Receiver configuration register 3*. The default setting of this register is the minimum gain. Default first stage zero is located at 60 kHz, it can also be lowered to 40 or 12 kHz by writing option bits in the *Receiver configuration register 1*. The first stage can be reconfigured to second order high-pass at 600 kHz by option bit z600k. The control of the first and third stage zeros is done with common control bits (see *Table 6*).

rec1<5>lp2 rec1<4>lp1 rec1<3>lp0 -1 dB point 0 0 0 1200 kHz 0 0 1 600 kHz 0 0 1 300 kHz 1 0 0 2 MHz

Table 5. Low-pass control

DS13541 Rev 6 27/163

Table 5. Low-pass control (continued)

| rec1<5>lp2 | rec1<4>lp1 | rec1<3>lp0 | -1 dB point |  |

|------------|------------|------------|-------------|--|

| 1          | 0          | 1          | 7 MHz       |  |

|            | Not used   |            |             |  |

Table 6. First and third zero setting

| rec1<3>z600k | rec1<2>h200 | rec1<1>h80 | rec1<0>z12k | First stage zero | Third stage zero |

|--------------|-------------|------------|-------------|------------------|------------------|

| 0            | 0           | 0          | 0           | 60 kHz           | 400 kHz          |

| 0            | 1           | 0          | 0           | 00 KHZ           | 200 kHz          |

| 0            | 0           | 1          | 0           | 40 kHz           | 80 kHz           |

| 0            | 0           | 0          | 1           |                  | 200 kHz          |

| 0            | 0           | 1          | 1           | 12 kHz           | 80 kHz           |

| 0            | 1           | 0          | 1           |                  | 200 kHz          |

| 1            | 0           | 0          | 0           | 600 kHz          | 400 kHz          |

| 1            | 1           | 0          | 0           | OOU KHZ          | 200 kHz          |

|              | Oth         | Not used   |             |                  |                  |

The gain in the second and third stage is 23 dB and can be reduced in six 3 dB steps. Gain of these two stages is included in AGC and Squelch loops or can be manually set in *Receiver configuration register 4*. Sending of direct command Reset RX Gain is necessary to initialize the AGC, Squelch and RSSI block. Sending this command clears the current Squelch setting and loads the manual gain reduction from *Receiver configuration register 4*. Second stage has a second order low-pass filtering characteristic, the pass band is adjusted according to subcarrier frequency using the bits lp2 to lp0 of the *Receiver configuration register 1*. See *Table 5* for -1 dB cut-off frequency for different settings.

#### Digitizing stage

The digitizing stage produces a digital representation of the sub-carrier signal coming from the receiver. This digital signal is then processed by the receiver framing logic. The digitizing stage consists of a window comparator with adjustable digitizing window (five possible settings, 3 dB steps, adjustment range from ±33 to ±120 mV). The adjustment of the digitizing window is included in the AGC and Squelch loops. The digitizing window can also be set manually in the *Receiver configuration register 4*.

#### AGC, Squelch and RSSI

As mentioned above, the second and third gain stage gain and the digitizing stage window are included in the AGC and Squelch loops. Eleven settings are available. The default state features minimum digitizer window and maximum gain. The first four steps increase the digitizer window in 3 dB steps, the next six steps reduce the gain in the second and third gain stage, again in 3 dB steps. The initial start setting for Squelch and AGC is defined in Receiver configuration register 4. The Gain reduction state register displays the actual state of gain resulting from Squelch, AGC and initial settings in Receiver configuration register 4.

### Squelch

This feature is designed for operation in noisy environments. The noise may be misinterpreted as the start of tag response, resulting in decoding errors.

Automatic squelch is enabled by option bit sqm\_dyn in the *Receiver configuration register 2*. It is activated automatically 18.88 µs after end of TX and is terminated at the moment the Mask receive timer (MRT) reaches the value defined in the *Squelch timer register*. This mode is primarily intended to suppress noise generated by tag processing during the time when the tag response is not expected (covered by MRT).

Squelch can operate in two modes, namely with ratios 1 and 6, selectable by pulz\_61 bit in the *Receiver configuration register 2*.

Squelch ratio 1 means that system observes the subcarrier signal from the main digitizer and decrease the system gain to decrease the frequency of transitions. If there are more than two transitions on this output in a 50  $\mu$ s time period, gain is reduced by 3 dB and output is observed during the following 50  $\mu$ s. This procedure is repeated until number of transitions in 50  $\mu$ s is lower or equal to 2 or until the maximum gain reduction is reached. This mode is intended for protocols where digitized subcarrier outputs are used.

Squelch ratio 6 means the system similarly observes and decreases the frequency seen at the window comparator set to 6 times the digitizing window. This mode is intended for protocols where output from correlators are used (ISO-A, ISO-B correlated reception).

The gain setting acquired by squelch is cleared by sending direct command Reset RX gain.

#### **AGC**

The AGC (automatic gain control) reduces the gain to keep the receiver chain and input to the digitizing stage out of saturation. The demodulation process is also less influenced by system noise when the gain is properly adjusted.

The AGC logic starts operating when the signal rx\_on is asserted to high and is reset when it is reset to low. The state of the receiver gain is stored in the *Gain reduction state register* during a high to low transition of bit rx\_on. Reading this register later on gives information of the gain setting used during the last reception.

The AGC system comprises a window comparator and an AGC ratio that can be set to 3 or to 6. As an example, when the AGC ratio is set to 6 the window is six times larger than the data digitalization window comparator. When the AGC function is enabled the gain is reduced until there are no transitions on its output. Such procedure assures that the input to digitalization window comparator is up to 6 times larger than its window.

If the AGC ratio is set to three, the input to the digitalization window comparator is set to be up to 3 times larger than its window.

The AGC operation is controlled by the control bits agc\_en, agc\_m, agc\_alg, and agc6\_3 in Receiver configuration register 2.

The bit agc\_m defines the AGC mode when two AGC modes are available. The AGC can operate during the complete RX process as long as the signal rx\_on is high and it can be enabled only during first eight subcarrier pulses.

There are two AGC algorithms to choose from bit agc\_alg. The AGC can start either by pre-setting (maximum digitizer window and maximum gain) or by resetting (minimum digitizer window and maximum gain) it. The algorithm with preset is faster and therefore recommended for protocols with short SOF (like ISO14443A at 106 kbps).

DS13541 Rev 6 29/163

#### Correlator

The correlators correlate the incoming filtered subcarrier with 848 kHz. The aim of the correlation is to maximize the system sensitivity at 848 kHz, while rejecting other frequencies. There are two correlators in the system for AM (or I) channel and PM (or Q) channel.

Correlator settings are defined in Correlator configuration register 1 and Correlator configuration register 2.

#### **RSSI**

The receiver also performs the RSSI (received signal strength indicator) measurement for both channels. The RSSI measurement is started after the rising edge of rx on. It stays active while the signal rx on is high and frozen while rx on is low. It is a peak hold system where the value can only increase from initial 0 value. Every time the AGC reduces the gain the RSSI measurement is reset and starts from 0. The result of RSSI measurements is a 4-bit value that can be observed by reading the RSSI display register. The LSB step is 2.8 dB, the maximum value is Dh (13d).

Since the RSSI measurement is of peak hold type, the result does not follow any variations in the signal strength (the highest value will be kept). To follow RSSI variation it is possible to reset RSSI bits and restart the measurement by sending direct command Clear RSSI.

#### Clock extractor

The clock extractor observes the RFI1 and RFI2 differential signal and provides a clock signal synchronous with the incoming RF field. The extracted clock is used for synchronous demodulation, for correct frame delay time and for correct data timing during passive transmission. The clock extractor is active down to 60 mV<sub>PP</sub> input signal.

#### 4.2.3 Antenna tuning

The ST25R3916B and ST25R3917B support antenna tuning through external variable capacitors. The variable capacitor is connected on its position in the matching network, and the tuning control voltage is connected to one of the control output pins (AAT A, AAT B).

The variable capacitors can be connected in series and parallel configurations in the matching network. Further information on the various configuration options can be found in the application note AN5322, available on www.st.com.

The phase and amplitude detector block is used for resonance frequency checking. The algorithm in the MCU evaluates the result and adjusts the tuning voltages at AAT A and AAT B output pins via the Antenna tuning control register 1 and Antenna tuning control register 2 according to the procedure in the MCU firmware.

The AAT A/B pin voltages are actively set according to Antenna tuning control register 1 and Antenna tuning control register 2 when en and aat\_en option bits are both set.

If aat en=1 and en=0, the AAT A/B voltages are set to a fixed value between 1.5 and 2.2 V (typically 1.9 V).

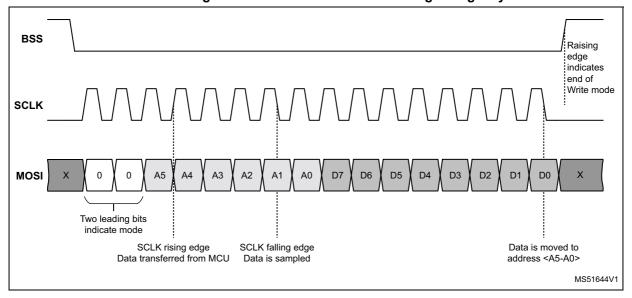

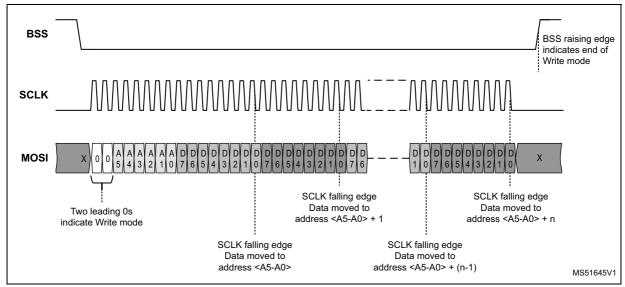

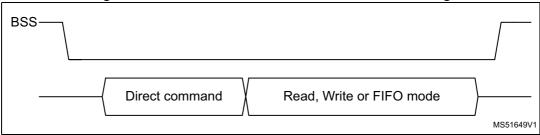

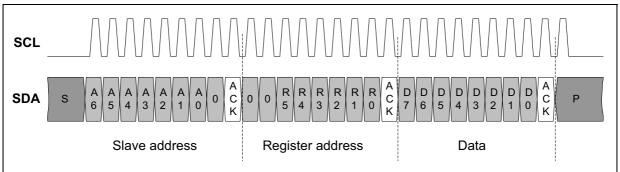

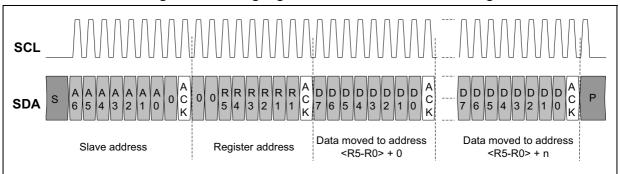

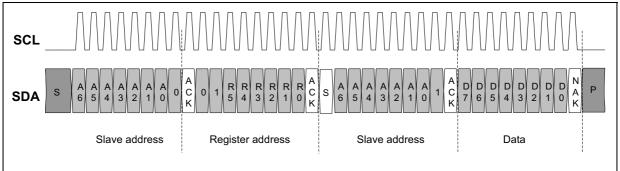

## 4.2.4 Wake-up mode