# **STMPE1801**

Xpander Logic™ 18-bit enhanced port expander with keypad controller

## Features

- 18 GPIOs configurable as GPI, GPO, keypad matrix, special key or dedicated key function

- Operating voltage: 1.65 3.6 V

- Hardware keypad controller (KPC) (10 x 8 matrix with 4 optional dedicated keys maximum)

- Keypad controller capable of detecting keypress in hibernation mode

- Interrupt output (open drain) pin

- Advanced power management system

- Ultra-low standby mode current

- Programmable pull-up resistors for all GPIO pins

- ESD performance on GPIO pins:

- ± 8 kV human body model (JESD22 A114-C)

- ESD performance on V<sub>CC</sub>, GND, INT<sub>B</sub>, R<sub>STB</sub>, SCL, SDA pins:

- ± 3 kV human body model (JESD22 A114-C)

## Description

The STMPE1801 is a GPIO (general purpose input/output) port expander capable of interfacing a main digital ASIC via the two-line bidirectional bus (I<sup>2</sup>C). A separate GPIO expander IC is often used in mobile multimedia platforms to resolve the problem of the limited number of GPIOs typically available on digital engines. The STMPE1801 offers high flexibility, as each I/O can be configured as input, output, special key, keypad matrix or dedicated key function. This device is designed to include very low quiescent current, and a wakeup feature for each I/O, to optimize the power consumption of the device. Potential applications for the STMPE1801 include portable media players, game consoles, mobile and smart phones.

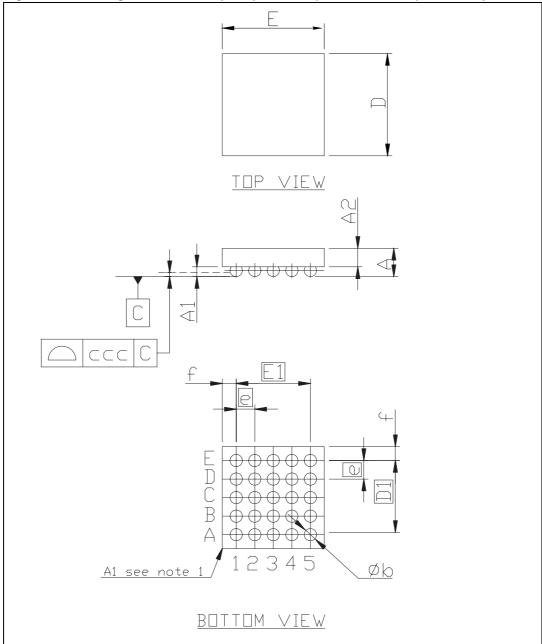

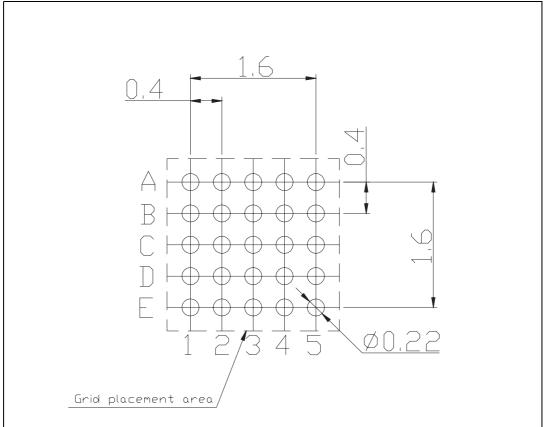

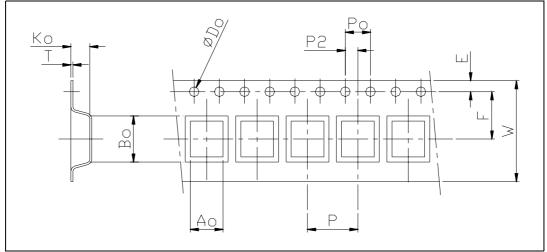

#### Table 1. Device summary

| Order code   | Package                                           | Packaging     |

|--------------|---------------------------------------------------|---------------|

| STMPE1801BJR | Flip-chip CSP 25 (2.03 x 2.03 mm)<br>0.4 mm pitch | Tape and reel |

# Contents

| 1 | Block  | diagram                                                             |

|---|--------|---------------------------------------------------------------------|

| 2 | Pin se | ettings                                                             |

|   | 2.1    | Pin connection                                                      |

|   | 2.2    | Pin description                                                     |

|   | 2.3    | GPIO pin functions                                                  |

| 3 | Maxin  | num ratings                                                         |

|   | 3.1    | Absolute maximum ratings                                            |

|   | 3.2    | Thermal data                                                        |

| 4 | Electi | rical specification                                                 |

|   | 4.1    | DC electrical characteristics                                       |

|   | 4.2    | Input/Output DC electrical characteristics                          |

| 5 | Regis  | ter address                                                         |

| 6 | l2C sp | pecification                                                        |

|   | 6.1    | I2C related pins 14                                                 |

|   | 6.2    | I2C addressing 14                                                   |

|   | 6.3    | Start condition 14                                                  |

|   | 6.4    | Stop condition                                                      |

|   | 6.5    | Acknowledge bit (ACK) 15                                            |

|   | 6.6    | Data input                                                          |

|   | 6.7    | Memory addressing                                                   |

|   | 6.8    | Operation modes 15                                                  |

|   | 6.9    | General call address 17                                             |

| 7 | Syste  | m controller                                                        |

|   | 7.1    | System level registers                                              |

|   | 7.2    | States of operation                                                 |

|   |        | 7.2.1Auto-hibernate 207.2.2Keypress detect in the Hibernate mode 21 |

|   |        |                                                                     |

Doc ID 17884 Rev 3

| 8  |       |          | Clocking system 2                            | 2        |

|----|-------|----------|----------------------------------------------|----------|

|    |       | 8.0.1    | Clock source                                 | 2        |

|    |       | 8.0.2    | Power mode programming sequence2             | 3        |

| 9  | Inter | rupt sy  | stem                                         | 4        |

|    | 9.1   | Interru  | pt system register map 2                     | 5        |

|    | 9.2   | Interru  | pt latency for the GPIO hot keys             | 5        |

|    | 9.3   | Progra   | mming sequence                               | 1        |

| 10 | GPIC  | ) contro | oller                                        | 2        |

|    | 10.1  | GPIO     | control registers                            | 3        |

|    |       | 10.1.1   | Bit description                              | 3        |

|    | 10.2  | Hotkey   | <sup>,</sup> feature                         | 4        |

|    |       | 10.2.1   | Programming sequence for Hotkey              | 4        |

|    |       | 10.2.2   | Minimum pulse width                          | 4        |

| 11 | Кеур  | ad con   | troller                                      | 5        |

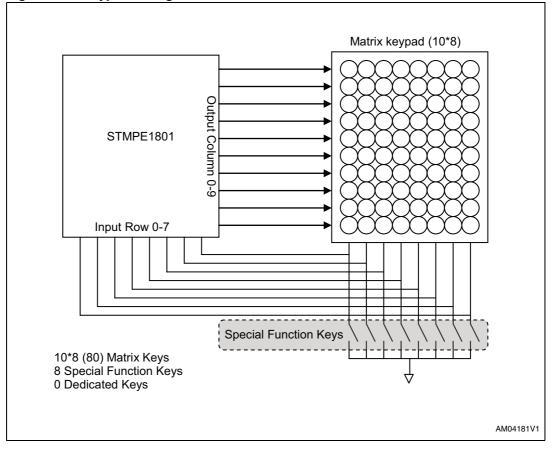

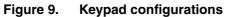

|    | 11.1  | Keypa    | d configurations                             | 8        |

|    | 11.2  | Keypa    | d controller registers 4                     | 0        |

|    | 11.3  | Data r   | egisters                                     | 6        |

|    | 11.4  | Keypa    | d combination key registers 5                | 0        |

|    | 11.5  | Using    | the keypad controller                        | 1        |

|    |       | 11.5.1   | Ghost key handling5                          | 51       |

|    |       | 11.5.2   | Key detection priority5                      | <b>1</b> |

|    |       | 11.5.3   | Keypad wakeup from Hibernate mode            | 2        |

|    |       | 11.5.4   | Keypad controller combination key interrupt5 | 2        |

| 12 | Misc  | ellaneo  | us features                                  | 3        |

|    | 12.1  | Reset    |                                              | 3        |

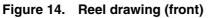

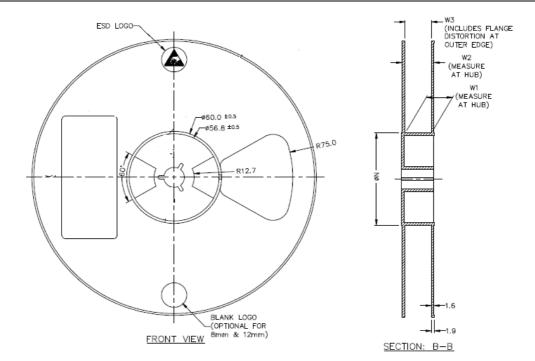

| 13 | Pack  | age me   | chanical data                                | 4        |

| 14 | Revis | sion his | story                                        | 9        |

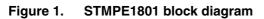

# 1 Block diagram

# 2 Pin settings

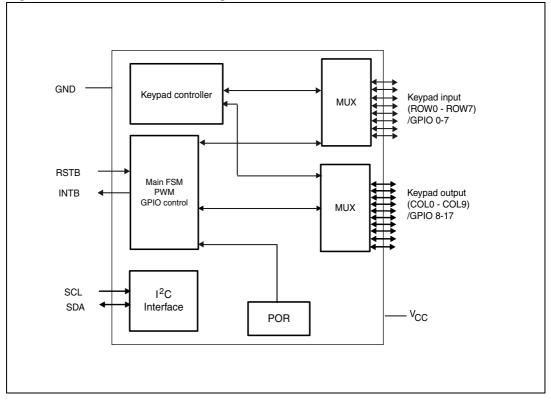

### 2.1 Pin connection

## 2.2 Pin description

| Table 2.   | riii uesci | iption |                   |

|------------|------------|--------|-------------------|

| Pin number | Туре       | Symbol | Name and function |

| D4         | I/O        | GPIO0  | GPIO0/ROW0        |

| C4         | I/O        | GPIO1  | GPIO1/ROW1        |

| A4         | I/O        | GPIO2  | GPIO2/ROW2        |

| E5         | I/O        | GPIO3  | GPIO3/ROW3        |

| D5         | I/O        | GPIO4  | GPIO4/ROW4        |

| C5         | I/O        | GPIO5  | GPIO5/ROW5        |

| B5         | I/O        | GPIO6  | GPIO6/ROW6        |

| A5         | I/O        | GPIO7  | GPIO7/ROW7        |

| E4         | I/O        | GPIO8  | GPIO8/COL0        |

| A3         | I/O        | GPIO9  | GPIO9/COL1        |

| B3         | I/O        | GPIO10 | GPIO10/COL2       |

|            |            |        |                   |

#### Table 2. Pin description

| Pin number | Туре | Symbol          | Name and function                                                                                                                                                                       |  |  |  |

|------------|------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| C3         | I/O  | GPIO11          | GPIO11/COL3                                                                                                                                                                             |  |  |  |

| D3         | I/O  | GPIO12          | GPIO12/COL4                                                                                                                                                                             |  |  |  |

| E3         | I/O  | GPIO13          | GPIO13/COL5                                                                                                                                                                             |  |  |  |

| A2         | I/O  | GPIO14          | GPIO14/COL6                                                                                                                                                                             |  |  |  |

| B2         | I/O  | GPIO15          | GPIO15/COL7                                                                                                                                                                             |  |  |  |

| C2         | I/O  | GPIO16          | GPIO16/COL8                                                                                                                                                                             |  |  |  |

| D2         | I/O  | GPIO17          | GPIO17/COL9                                                                                                                                                                             |  |  |  |

| E1         | 0    | INTB            | Open drain interrupt output pin. Programmable active low (a pull-up resistor is required) or active high (a pull-down resistor is required). Fail safe. Pull to $V_{CC}$ if not in use. |  |  |  |

| A1         | I    | RSTB            | External reset input. Active low. Fail safe. Reset pulse width must be more than 500 $\mu s$ to be valid.                                                                               |  |  |  |

| C1         | А    | SDA             | I <sup>2</sup> C data. Fail safe                                                                                                                                                        |  |  |  |

| D1         | А    | SCL             | I <sup>2</sup> C clock. Fail safe                                                                                                                                                       |  |  |  |

| B4         | -    | NC              | No connect                                                                                                                                                                              |  |  |  |

| B1         | -    | V <sub>CC</sub> | Power supply                                                                                                                                                                            |  |  |  |

| E2         | -    | GND             | Ground                                                                                                                                                                                  |  |  |  |

Table 2.

Pin description (continued)

## 2.3 GPIO pin functions

| Table 3. GPIO pin function | on               |                    |

|----------------------------|------------------|--------------------|

| Name                       | Primary function | Alternate function |

| GPIO0                      | GPIO             | Keypad row 0       |

| GPIO1                      | GPIO             | Keypad row 1       |

| GPIO2                      | GPIO             | Keypad row 2       |

| GPIO3                      | GPIO             | Keypad row 3       |

| GPIO4                      | GPIO             | Keypad row 4       |

| GPIO5                      | GPIO             | Keypad row 5       |

| GPIO6                      | GPIO             | Keypad row 6       |

| GPIO7                      | GPIO             | Keypad row 7       |

| GPIO8                      | GPIO             | Keypad column 0    |

| GPIO9                      | GPIO             | Keypad column 1    |

| GPIO10                     | GPIO             | Keypad column 2    |

| GPIO11                     | GPIO             | Keypad column 3    |

| GPIO12                     | GPIO             | Keypad column 4    |

| Table 3. | GPIO p | oin function |

|----------|--------|--------------|

|          |        |              |

Doc ID 17884 Rev 3

|        | •                | •                  |

|--------|------------------|--------------------|

| Name   | Primary function | Alternate function |

| GPIO13 | GPIO             | Keypad column 5    |

| GPIO14 | GPIO             | Keypad column 6    |

| GPIO15 | GPIO             | Keypad column 7    |

| GPIO16 | GPIO             | Keypad column 8    |

| GPIO17 | GPIO             | Keypad column 9    |

#### Table 3.GPIO pin function

The default function is always GPIO. As soon as the key scanning is enabled through the keypad registers, the function is then switched to the key function and then any configuration made in the GPIO registers is ignored.

## 3 Maximum ratings

Stressing the device above the rating listed in the "absolute maximum ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 3.1 Absolute maximum ratings

| Symbol           | Parameter                                                              | Value | Unit |  |

|------------------|------------------------------------------------------------------------|-------|------|--|

| V <sub>CC</sub>  | Supply voltage                                                         | 4.5   | V    |  |

| V <sub>IN</sub>  | Input voltage on GPIO pin                                              | 4.5   | V    |  |

| V <sub>ESD</sub> | Minimum ESD protection on each GPIO<br>pin (HBM model - JESD22 A114-C) | ±8    | kV   |  |

| V <sub>ESD</sub> | ESD protection on other pins (HBM model - JESD22 A114-C)               | ±3    | kV   |  |

Table 4. Absolute maximum ratings

## 3.2 Thermal data

| Symbol            | Parameter                           | Min | Тур | Мах | Unit |  |

|-------------------|-------------------------------------|-----|-----|-----|------|--|

| R <sub>thJA</sub> | Thermal resistance junction-ambient | -   | 100 | -   | °C/W |  |

| T <sub>A</sub>    | Operating ambient temperature       | -40 | 25  | 85  | °C   |  |

| Т <sub>Ј</sub>    | Operating junction temperature      | -40 | 25  | 125 | °C   |  |

#### Table 5. Thermal data

# 4 Electrical specification

## 4.1 DC electrical characteristics

| Symbol           | Parameter                    | Test conditions                                                                                              |       |      | - Unit |     |              |

|------------------|------------------------------|--------------------------------------------------------------------------------------------------------------|-------|------|--------|-----|--------------|

| Symbol           | Parameter                    |                                                                                                              |       | Min  | Тур    | Max | Unit         |

| V <sub>CC</sub>  | Supply voltage               | -                                                                                                            |       | 1.65 | _      | 3.6 | V            |

|                  | Active current (core         | 1.8                                                                                                          | V     | _    | 28     | 55  | μA           |

| I <sub>CC</sub>  | and analog) - 1 key<br>press | 3.3 V                                                                                                        |       | _    | 90     | 140 | μA           |

|                  | Hibernate current            | 1.8 V                                                                                                        | 25 °C | _    | _      | 0.5 | - μA<br>- μA |

| 1                |                              |                                                                                                              | 85 °C | _    | _      | 1   |              |

| HIBERNATE        |                              | 3.3 V                                                                                                        | 25 °C | _    | -      | 0.5 |              |

|                  |                              | 5.5 V                                                                                                        | 85 °C | _    | Ι      | 1   |              |

| I <sub>NTB</sub> | Open drain output<br>current | V <sub>OL(max)</sub> =0.45<br>V <sub>CC</sub> =1.8 V<br>V <sub>OL(max)</sub> =0.83<br>V <sub>CC</sub> =3.3 V |       | _    | 4      | _   | mA           |

Table 6.

DC electrical characteristics

# 4.2 Input/Output DC electrical characteristics

| Cumhal            | Parameter                   | Test conditions                                                                                                        |                     | Unit |                     |    |

|-------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------|------|---------------------|----|

| Symbol            |                             | Test conditions                                                                                                        | Min                 | Тур  | Max                 |    |

| V                 |                             | V <sub>CC</sub> = 1.8 V                                                                                                | -                   | —    | 0.2 V <sub>CC</sub> | v  |

| $V_{IL}$          | Low level input voltage     | V <sub>CC</sub> = 3.3 V                                                                                                | _                   | _    | 0.2 V <sub>CC</sub> | v  |

| V <sub>IH</sub>   | High level input voltage    | V <sub>CC</sub> = 1.8 V                                                                                                | 0.8 V <sub>CC</sub> | _    | —                   | v  |

| чн                | I light lover input ventage | V <sub>CC</sub> = 3.3 V                                                                                                | 0.8 V <sub>CC</sub> | -    | -                   | •  |

| V <sub>HYST</sub> | Schmitt trigger hysteresis  | V <sub>CC</sub> = 1.8 V                                                                                                | —                   | 0.10 | —                   | v  |

| ▲HYST             |                             | V <sub>CC</sub> = 3.3 V                                                                                                | —                   | 0.20 | -                   | v  |

| V <sub>OL</sub>   | Low level output voltage    | I <sub>OL</sub> = 4 mA,<br>V <sub>CC</sub> = 1.8 V                                                                     | _                   | _    | 0.45                | V  |

|                   |                             | I <sub>OL</sub> = 4 mA,<br>V <sub>CC</sub> = 3.3 V                                                                     | _                   | _    | 0.45                |    |

| V                 |                             | I <sub>OH</sub> = -4 mA,<br>V <sub>CC</sub> = 1.8 V                                                                    | 1.35                | _    | _                   | V  |

| V <sub>OH</sub>   | High level output voltage   | I <sub>OH</sub> = -4 mA,<br>V <sub>CC</sub> = 3.3 V                                                                    | 2.48                | _    | _                   | v  |

| R <sub>UP</sub>   | Equivalent pull-up          | V <sub>CC</sub> = 3.3 V.<br>Active<br>implementation,<br>R value is<br>determined by the<br>current measured<br>at 0 V | 30                  | 60   | 90                  | kΩ |

|                   | resistance                  | $V_{CC}$ = 1.8 V. Active<br>implementation,<br>R value is<br>determined by the<br>current measured<br>at 0 V           | 50                  | 100  | 150                 | kΩ |

Table 7.

I/O DC electrical characteristics

# 5 Register address

| Addres<br>s | Register name             | Description                      | Auto-<br>increment | 7                   | 6                    | 5         | 4               | 3               | 2         | 1         | 0         |           |           |          |          |

|-------------|---------------------------|----------------------------------|--------------------|---------------------|----------------------|-----------|-----------------|-----------------|-----------|-----------|-----------|-----------|-----------|----------|----------|

| 00          | CHIP_ID                   | Chip<br>identification           | No                 | 8-bit CHIP ID       |                      |           |                 |                 |           |           |           |           |           |          |          |

| 01          | VERSION_ID                | Version<br>identification        | No                 | 8-bit VERSION ID    |                      |           |                 |                 |           |           |           |           |           |          |          |

| 02          | SYS_CTRL                  | System control                   | No                 | SF_<br>RST RESERVED |                      |           | GPI<br>_DB<br>1 | GPI<br>_DB<br>0 | RSV<br>D  |           |           |           |           |          |          |

| 04          | INT_CTRL_LOW              | Interrupt                        |                    | RE                  | SERV                 | ED        |                 | IC2             | IC1       | IC0       |           |           |           |          |          |

| 05          | INT_CTRL_HIGH             | control                          | Yes                |                     |                      |           | RESE            | RVED            |           |           |           |           |           |          |          |

| 06          | INT_EN_MASK_LOW           | Interrupt                        |                    | RE                  | SERV                 | ΈD        | IE4             | IE3             | IE2       | IE1       | IE0       |           |           |          |          |

| 07          | INT_EN_MASK_HIGH          | enable mask                      | Yes                | RESERVED            |                      |           |                 | 1               |           | L         |           |           |           |          |          |

| 08          | INT_STA_LOW               |                                  |                    | RE                  | RESERVED IE4 IE3 IE2 |           |                 |                 | IE2       | IE1       | IE0       |           |           |          |          |

| 09          | INT_STA_HIGH              | Interrupt status                 | Yes                | RESERVED            |                      |           |                 |                 |           | L         |           |           |           |          |          |

| 0A          | INT_EN_GPIO_MASK<br>_LOW  | Interrupt<br>enable GPIO<br>mask |                    | IEG<br>7            | IEG<br>6             | IEG<br>5  | IEG<br>4        | IEG<br>3        | IEG<br>2  | IEG<br>1  | IEG<br>0  |           |           |          |          |

| 0B          | INT_EN_GPIO_MASK<br>_MID  |                                  | Yes                | IEG<br>15           | IEG<br>14            | IEG<br>13 | IEG<br>12       | IEG<br>11       | IEG<br>10 | IEG<br>9  | IEG<br>8  |           |           |          |          |

| 0C          | INT_EN_GPIO_MASK<br>_HIGH | maan                             |                    |                     | •                    | RESE      | RVED            |                 |           | IEG<br>17 | IEG<br>16 |           |           |          |          |

| 0D          | INT_STA_GPIO_LOW          |                                  |                    | ISG<br>7            | ISG<br>6             | ISG<br>5  | ISG<br>4        | ISG<br>3        | ISG<br>2  | ISG<br>1  | ISG<br>0  |           |           |          |          |

| 0E          | INT_STA_GPIO_MID          | Interrupt status<br>GPIO         |                    |                     |                      |           | Yes             | ISG<br>15       | ISG<br>14 | ISG<br>13 | ISG<br>12 | ISG<br>11 | ISG<br>10 | ISG<br>9 | ISG<br>8 |

| 0F          | INT_STA_GPIO_HIGH         |                                  |                    |                     |                      |           | RESE            | RVED            |           |           | ISG<br>17 | ISG<br>16 |           |          |          |

| 10          | GPIO_SET_LOW              |                                  |                    | 107                 | 106                  | IO5       | IO4             | IO3             | 102       | 101       | IO0       |           |           |          |          |

| 11          | GPIO_SET_MID              | GPIO set pin<br>state            | Yes                | IO15                | IO14                 | IO13      | IO12            | IO11            | IO10      | 109       | IO8       |           |           |          |          |

| 12          | GPIO_SET_HIGH             |                                  |                    |                     |                      | RESE      | RVED            |                 |           | 1017      | IO16      |           |           |          |          |

| 13          | GPIO_CLR_LOW              |                                  |                    | 107                 | 106                  | 105       | IO4             | IO3             | 102       | IO1       | 100       |           |           |          |          |

| 14          | GPIO_CLR_MID              | GPIO clear pin<br>state          | Yes                | IO15                | IO14                 | IO13      | IO12            | IO11            | IO10      | 109       | IO8       |           |           |          |          |

| 15          | GPIO_CLR_HIGH             | 0.010                            |                    | RESERVED            |                      |           |                 |                 | IO17      | IO16      |           |           |           |          |          |

| 16          | GPIO_MP_LOW               |                                  |                    | 107                 | 106                  | 105       | 104             | IO3             | 102       | 101       | 100       |           |           |          |          |

| 17          | GPIO_MP_MID               | GPIO monitor<br>pin state        |                    | Yes                 | IO15                 | 1014      | IO13            | IO12            | IO11      | IO10      | 109       | IO8       |           |          |          |

| 18          | GPIO_MP_HIGH              | F                                |                    |                     |                      | RESE      | RVED            |                 |           | IO17      | IO16      |           |           |          |          |

#### Table 8. STMPE1801 register summary table

| Table 8.    | SIMPE1801 register summary table |                               |                    |                              |                          |          |          |           |          |                 |          |

|-------------|----------------------------------|-------------------------------|--------------------|------------------------------|--------------------------|----------|----------|-----------|----------|-----------------|----------|

| Addres<br>s | Register name                    | Description                   | Auto-<br>increment | 7                            | 6                        | 5        | 4        | 3         | 2        | 1               | 0        |

| 19          | GPIO_SET_DIR_LOW                 |                               |                    | 107                          | 106                      | 105      | IO4      | IO3       | 102      | 101             | 100      |

| 1A          | GPIO_SET_DIR_MID                 | GPIO set pin<br>direction     | Yes                | IO15                         | IO14                     | IO13     | IO12     | IO11      | IO10     | 109             | 108      |

| 1B          | GPIO_SET_DIR_HIG<br>H            | register                      |                    |                              |                          | RESE     | RVED     |           |          | IO17            | IO16     |

| 1C          | GPIO_RE_LOW                      |                               |                    | 107                          | 106                      | 105      | 104      | IO3       | 102      | 101             | 100      |

| 1D          | GPIO_RE_MID                      | GPIO rising<br>edge           | Yes                | IO15                         | IO14                     | IO13     | IO12     | 1011      | IO10     | 109             | IO8      |

| 1E          | GPIO_RE_HIGH                     | Ū                             |                    |                              |                          | RESE     | RVED     |           |          | IO17            | IO16     |

| 1F          | GPIO_FE_LOW                      |                               |                    | 107                          | 106                      | 105      | IO4      | IO3       | 102      | 101             | 100      |

| 20          | GPIO_FE_MID                      | GPIO falling<br>edge          | Yes                | IO15                         | IO14                     | IO13     | IO12     | IO11      | IO10     | 109             | 108      |

| 21          | GPIO_FE_HIGH                     |                               |                    |                              | •                        | RESE     | RVED     | •         | •        | IO17            | IO16     |

| 22          | GPIO_PULL_UP_LO<br>W             |                               |                    | 107                          | IO6                      | IO5      | 104      | IO3       | 102      | 101             | IO0      |

| 23          | GPIO_PULL_UP_MID                 | GPIO pull up                  | IO pull up Yes     | IO15                         | IO14                     | IO13     | IO12     | IO11      | IO10     | 109             | 108      |

| 24          | GPIO_PULL_UP_HIG<br>H            |                               |                    |                              |                          | RESE     | RVED     |           |          | IO17            | IO16     |

| 30          | KPC_ROW                          | Keypad row<br>scanning        | Yes                | RO<br>W7                     | RO<br>W6                 | RO<br>W5 | RO<br>W4 | RO<br>W3  | RO<br>W2 | RO<br>W1        | RO<br>W0 |

| 31          | KPC_COL_LOW                      | Keypad column                 | Keypad column      |                              | COLCOLCOLCOLCOLCOL765432 |          |          |           |          | COL<br>1        | COL<br>0 |

| 32          | KPC_COL_HIGH                     | scanning                      |                    | RESERVED                     |                          |          |          |           |          | COL<br>9        | COL<br>8 |

| 33          | KPC_CTRL_LOW                     |                               |                    | SC                           | AN_C                     | OUNT     | 0-3      |           | DKE      | Y 0-3           |          |

| 34          | KPC_CTRL_MID                     | Key config:<br>Scan count and | Yes                | DB6                          | DB5                      | DB4      | DB3      | DB2       | DB1      | DB0             | Rsv<br>d |

| 35          | KPC_CTRL_HIGH                    | dedicated key                 |                    | Rsv CM<br>B_K RESERVED<br>EY |                          |          |          | SCAI<br>E | _        |                 |          |

| 36          | KPC_CMD                          | Keypad<br>command             | Yes                |                              |                          | RESE     | RVED     |           |          | KPC<br>_LC<br>K | SCA<br>N |

| 37          | KPC_COMB_KEY_0                   | Keypad                        |                    | C4                           | C3                       | C2       | C1       | C0        | R2       | R1              | R0       |

| 38          | KPC_COMB_KEY_1                   | combination                   | Yes                | C4                           | C3                       | C2       | C1       | C0        | R2       | R1              | R0       |

| 39          | KPC_COMB_KEY_2                   | key mask                      |                    | C4                           | C3                       | C2       | C1       | C0        | R2       | R1              | R0       |

|             |                                  |                               |                    |                              |                          |          |          |           |          |                 |          |

#### Table 8. STMPE1801 register summary table

| Addres<br>s | Register name  | Description | Auto-<br>increment | 7              | 6   | 5   | 4   | 3                   | 2   | 1   | 0   |

|-------------|----------------|-------------|--------------------|----------------|-----|-----|-----|---------------------|-----|-----|-----|

| ЗА          | KPC_DATA_BYTE0 |             |                    | UP/<br>DW<br>N | C3  | C2  | C1  | C0                  | R2  | R1  | R0  |

| 3B          | KPC_DATA_BYTE1 | Keynad data | Yes                | UP/<br>DW<br>N | C3  | C2  | C1  | C0                  | R2  | R1  | R0  |

| 3C          | KPC_DATA_BYTE2 | Keypad data | 100                | UP/<br>DW<br>N | C3  | C2  | C1  | C0                  | R2  | R1  | R0  |

| 3D          | KPC_DATA_BYTE3 |             |                    | SF7            | SF6 | SF5 | SF4 | SF3                 | SF2 | SF1 | SF0 |

| 3E          | KPC_DATA_BYTE4 |             |                    | RESERVED       |     |     |     | Dedicated Key 0 - 3 |     |     | - 3 |

### Table 8. STMPE1801 register summary table

# 6 I<sup>2</sup>C specification

The features supported by the I<sup>2</sup>C interface are listed below:

- I<sup>2</sup>C slave device

- Operates at V<sub>CC</sub> (1.8 3.6 V)

- Compliant to Philips I<sup>2</sup>C specification version 2.1

- Supports standard (up to 100 kbps) and fast (up to 400 kbps) modes

- 7-bit device addressing modes

- General call

- Start/Restart/Stop

## 6.1 I<sup>2</sup>C related pins

- SCL

- SDA

The device supports both 1.8 V I<sup>2</sup>C and 3.3 V I<sup>2</sup>C operations. It is recommended that Vpullup at SCL and SDA externally is greater or equal to  $V_{CC}$ .

# 6.2 I<sup>2</sup>C addressing

The STMPE1801 7-bit addressing is set to 40h.

## 6.3 Start condition

A Start condition is identified by a falling edge of SDA while SCL is stable at high state. A Start condition must precede any data/command transfer. The device continuously monitors for a Start condition and does not respond to any transaction unless one is encountered.

The first byte is scanned after the START command is detected to check for device ID. Ensure that all state machines are flushed when START instruction is issued.

## 6.4 Stop condition

A Stop condition is identified by a rising edge of SDA while SCL is stable at high state. A Stop condition terminates the communication between the slave device and bus master. A read command that is followed by NoAck can be followed by a Stop condition to force the slave device into idle mode. When the slave device is in idle mode, it is ready to receive the next I<sup>2</sup>C transaction. A Stop condition at the end of a write command stops the write operation to the registers.

Once the Stop condition is detected, the device should release the bus and go to Hibernate mode if there is no more activity.

An  $I^2C$  transaction with a START bit followed immediately by a STOP condition should not cause any  $I^2C$  lock-up.

### 6.5 Acknowledge bit (ACK)

The acknowledge bit is used to indicate a successful byte transfer. The bus transmitter releases the SDA after sending eight bits of data. During the ninth bit, the receiver pulls the SDA low to acknowledge the receipt of the eight bits of data. The receiver may leave the SDA in high state if it does not acknowledge the receipt of the data.

#### 6.6 Data input

The device samples the data input on SDA on the rising edge of the SCL. The SDA signal must be stable during the rising edge of SCL and the SDA signal must change only when SCL is driven low.

### 6.7 Memory addressing

For the bus master to communicate to the slave device, the bus master must initiate a Start condition and be followed by the slave device address. Accompanying the slave device address, there is a Read/Write bit (R/W). The bit is set to 1 for Read and 0 for Write operation.

If a match occurs on the slave device address, the corresponding device gives an acknowledgement on the SDA during the 9th bit time. If there is no match, it deselects itself from the bus by not responding to the transaction.

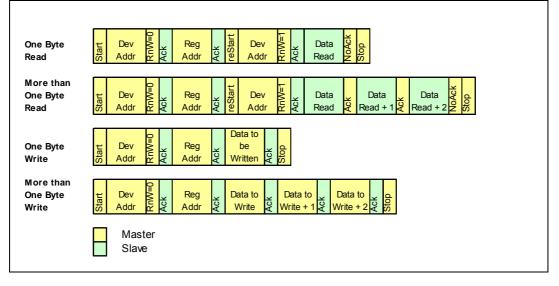

## 6.8 **Operation modes**

| Mode | Byte | Programming sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      | START, Device address, R/W<br>=0, Register Address to be read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |      | RESTART, Device Address, R/W<br>=1, Data Read, STOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Read | ≥1   | If no STOP is issued, the Data Read can be continuously performed. If the register address falls within the range that allows address auto-<br>increment, then register address auto-increments internally after every byte of data being read. For register address that fails within a non-<br>incremental address range, the address is kept static throughout the entire read operation. Refer to <i>Table 8.: STMPE1801 register summary table</i> for the address ranges that are auto-increment and non-increment.<br>An example of such a non-increment address is FIFO. |

#### Table 9. Operating modes

|       | porading |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode  | Byte     | Programming sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |          | START, Device Address, R/W<br>=0, Register Address to be written, Data Write, STOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Write | ≥1       | If no STOP is issued, the Data Write can be continuously performed. If<br>the register address falls within the range that allows address auto-<br>increment, then register address auto-increment internally after every<br>byte of data being written. For those register addresses that fall within a<br>non-incremental address range, the address will be kept static<br>throughout the entire write operation. Refer to <i>Table 8.: STMPE1801</i><br><i>register summary table</i> for the address ranges that are auto-increment<br>and non-increment. An example of a non-increment address is Data<br>Port for initializing the PWM. |

## 6.9 General call address

A general call address is a transaction with the slave address of 0x00 and R/W = 0. When a general call address is asserted, the STMPE1801 responds to this transaction with an acknowledgement and behaves as a slave-receiver mode. The meaning of a general call address is defined in the second byte sent by the master-transmitter.

| Table 10. | General call address |

|-----------|----------------------|

|           |                      |

| R/W | Second byte value | Definition                                                                                                                                                 |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0x06              | A 2-byte transaction in which the second byte tells the slave device to reset<br>and write (or latch in) the 2-bit programmable part of the slave address. |

| 0   | 0x00              | Not allowed as second byte.                                                                                                                                |

Note: All other second byte values are ignored.

# 7 System controller

## 7.1 System level registers

The system controller is the heart of the STMPE1801. It contains the registers for power control and chip identification.

The system registers are:

| Address | Register name |

|---------|---------------|

| 00      | CHIP_ID       |

| 01      | VERSION_ID    |

| 02      | SYS_CTRL      |

#### CHIP\_ID

### Chip identification register

| 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |  |

|---|---------------|---|---|---|---|---|---|--|--|--|--|--|--|

|   | 8-bit CHIP_ID |   |   |   |   |   |   |  |  |  |  |  |  |

| R | R             | R | R | R | R | R | R |  |  |  |  |  |  |

| 1 | 1             | 0 | 0 | 0 | 0 | 0 | 1 |  |  |  |  |  |  |

#### **VERSION\_ID**

## Version identification register

| 7 | 6                | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |  |  |

|---|------------------|---|---|---|---|---|---|--|--|--|--|--|--|--|

|   | 8-bit VERSION_ID |   |   |   |   |   |   |  |  |  |  |  |  |  |

| R | R                | R | R | R | R | R | R |  |  |  |  |  |  |  |

| 0 | 0                | 0 | 1 | 0 | 0 | 0 | 0 |  |  |  |  |  |  |  |

### SYS\_CTRL

### System control register

| 7      | 6 | 5     | 4    | 3 | 2       | 1       | 0    |

|--------|---|-------|------|---|---------|---------|------|

| SF_RST |   | RESEF | RVED |   | GPI_DB1 | GPI_DB0 | RSVD |

| W      | R | R     | R    | R | RW      | RW      | R    |

| 0      | 0 | 0     | 0    | 0 | 1       | 1       | 0    |

| 02 |

|----|

| 1  |

| Type: | R/W |

|-------|-----|

| - ,   |     |

| Reset: | 0x06 |

|--------|------|

|        |      |

#### **Description:** System control register.

[7] SF\_RST: Soft Reset Writing a '1' to this bit will do a soft reset of the device. Once the reset is done, this bit is cleared to '0' by the HW.

#### [6:3] RESERVED

[2:1] GPI\_DB [1:0]

GPI [17:0] operational mode de-bounce time

- '00' = 30 μs

- '01' = 90 μs

- '10' = 150 μs

- '11' = 210 µs (default)

- [0] RESERVED

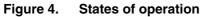

### 7.2 States of operation

The device has two main modes of operation:

- Operational mode: This is the mode, whereby normal operation of the device takes place. In this mode, the main finite state machine (FSM) unit routes 32 kHz clock to all the device blocks.

- Hibernate mode: This mode is entered automatically in auto-hibernate mode. When the device is in Hibernate mode, the 32 kHz clock is disabled. If there is a keypad activity, interrupt event, hotkey activity or I<sup>2</sup>C transaction, the device switches to operational mode. A reset event brings back the system to operational mode.

#### 7.2.1 Auto-hibernate

The STMPE1801 is set to go into Hibernate mode automatically if there is a period of inactivity (~ 100  $\mu$ s) following the completion of I<sup>2</sup>C transaction with the host. The STMPE1801 will continue counting down for hibernation mode activation even if there is an I<sup>2</sup>C transaction sent by the host to other slave devices. Any I<sup>2</sup>C transaction from the host to the STMPE1801 resets the hibernate counter.

Auto-hibernate mode occurs only when all the keys are released and FIFO is emptied through reading. This is to prevent any loss of data.

The hibernate mode counter should start when any of the following conditions is detected:

- Once the I<sup>2</sup>C transaction is completed or a STOP condition is detected.

- If the device ID in the I<sup>2</sup>C transaction is invalid.

When there is a keypad activity, the device should go into Hibernate mode ONLY when all the previously pressed keys are released.

Any keypad activity, interrupt event, hotkey activity or VALID I<sup>2</sup>C transaction wakes up the device from Hibernate mode and switches to operational mode automatically.

#### 7.2.2 Keypress detect in the Hibernate mode

When in Hibernate mode, any keypress detected causes the system to go into operational mode (~48  $\mu$ s). The system will then de-bounce the key to detect a valid key. If the keypress detected is valid, the system stays in operation mode. If the key detected is invalid, the system goes back into Hibernate mode.

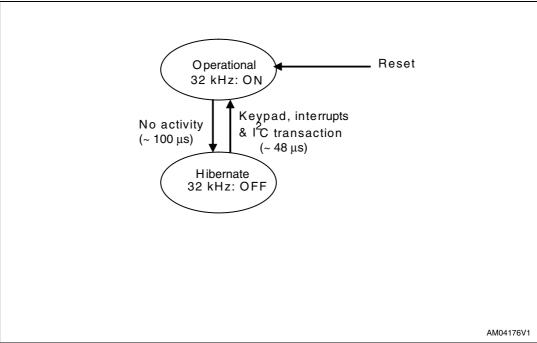

## 8 Clocking system

In order to reduce the power consumption, the STMPE1801 turns off the oscillator during Hibernate mode.

#### 8.0.1 Clock source

By default, when the STMPE1801 powers up, it derives a 32 kHz clock from the internal RC oscillator for its operation.

There are 4 sources of reset:

- RSTB pin

- Low voltage detect (LVD) reset

- Soft reset bit of the SYS\_CTRL register

- I<sup>2</sup>C reset from the I<sup>2</sup>C block.

#### 8.0.2 Power mode programming sequence

The device enters auto Hibernate mode when there is inactivity for a fixed period of time.

To wake up the device, the host is required to:

- Send an I<sup>2</sup>C transaction to the device.

To do a soft reset to the device, the host needs to do the following:

Write a '1' to bit 7 of the SYS\_CTRL register. This bit is automatically cleared upon reset.

To come out of the Hibernate mode, the following needs to be done by the host:

- Assert a system reset

- Or put a wakeup on the I<sup>2</sup>C transaction

- Interrupt activity

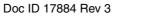

## 9 Interrupt system

The STMPE1801 uses a highly flexible interrupt system. It allows the host system to configure the type of system events that should result in an interrupt, and pinpoints the source of interrupt by status registers. The INT pin can be configured as active high (a pull-down resistor is required), or active low (a pull-up resistor is required). If INT pin is not in use, it is necessary to pull INT pin to  $V_{CC}$ .

Once asserted, the INT pin would de-assert when a read is done to the corresponding bit either in the INT\_STA register or INT\_STA\_GPIO register.

Figure 6. Interrupt system

### 9.1 Interrupt system register map

Table 11.

Interrupt system register map

| Address | Register name         | Description                         | Auto-increment<br>(during sequential R/W) |  |  |

|---------|-----------------------|-------------------------------------|-------------------------------------------|--|--|

| 04      | INT_CTRL_LOW          | Interrupt control register          | Yes                                       |  |  |

| 05      | INT_CTRL_HIGH         | Interrupt control register          | Yes                                       |  |  |

| 06      | INT_EN_MASK_LOW       | Interrupt anable mask register      | Yes                                       |  |  |

| 07      | INT_EN_MASK_HIGH      | Interrupt enable mask register      | Yes                                       |  |  |

| 08      | INT_STA_LOW           | Interrupt status register           | Yes                                       |  |  |

| 09      | INT_STA_HIGH          | Interrupt status register           | Yes                                       |  |  |

| 0A      | INT_EN_GPIO_MASK_LOW  |                                     | Yes                                       |  |  |

| 0B      | INT_EN_GPIO_MASK_MID  | Interrupt enable GPIO mask register | Yes                                       |  |  |

| 0C      | INT_EN_GPIO_MASK_HIGH |                                     | Yes                                       |  |  |

| 0D      | INT_STA_GPIO_LOW      |                                     | Yes                                       |  |  |

| 0E      | INT_STA_GPIO_MID      | Interrupt status GPIO register      | Yes                                       |  |  |

| 0F      | INT_STA_GPIO_HIGH     |                                     | Yes                                       |  |  |

## 9.2 Interrupt latency for the GPIO hot keys

When the generation of interrupts by the GPIO as input is enabled for the hot keys, the latency (time taken from actual transition at GPIO to time of INT pin assertion) is shown in the following table:

| State of operation | Interrupt latency | Comments                                                 |  |  |  |

|--------------------|-------------------|----------------------------------------------------------|--|--|--|

| Hibernation        | >200 μs (default) | Latency can be programmed by the GPI_DB bits of SYS_CTRL |  |  |  |

| Active             | >200 µs (default) | register                                                 |  |  |  |

## INT\_CTRL

## Interrupt control register

| 15              | 14     | 13     | 12                                                                                                                                                                                                                                               | 11       | 10        | 9       | 8 | 7            | 6 | 5 | 4 | 3 | 2   | 1   | 0   |

|-----------------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|---------|---|--------------|---|---|---|---|-----|-----|-----|

|                 |        |        | INT_CTR                                                                                                                                                                                                                                          | L_HIGH   |           |         |   | INT_CTRL_LOW |   |   |   |   |     |     |     |

|                 |        |        |                                                                                                                                                                                                                                                  |          | R         | eserved |   |              |   |   |   |   | IC2 | IC1 | IC0 |

| R               | R      | R      | R                                                                                                                                                                                                                                                | R        | R         | R       | R | R            | R | R | R | R | RW  | RW  | RW  |

| Address: 04, 05 |        |        |                                                                                                                                                                                                                                                  |          |           |         |   |              |   |   |   |   |     |     |     |

| Туре:           |        |        | R, R/W                                                                                                                                                                                                                                           | R, R/W   |           |         |   |              |   |   |   |   |     |     |     |

| Reset: 0x00     |        |        |                                                                                                                                                                                                                                                  |          |           |         |   |              |   |   |   |   |     |     |     |

| Descr           | iption | :      | The interrupt control register is used to configure the interrupt controller. It has global enable interrupt mask bit that controls the interruption to the host.                                                                                |          |           |         |   |              |   |   |   |   |     |     |     |

|                 |        | [15:3] | RESERVED                                                                                                                                                                                                                                         |          |           |         |   |              |   |   |   |   |     |     |     |

|                 |        | [2]    | IC2: Ou<br>'0' = Ac<br>'1' = Ac                                                                                                                                                                                                                  | tive lov | v/falling | l edge  | / |              |   |   |   |   |     |     |     |

|                 |        | [1]    | <ul> <li>IC1: Output Interrupt type</li> <li>'0' = Level interrupt</li> <li>'1' = Edge interrupt (Pulse width of 200µs)</li> </ul>                                                                                                               |          |           |         |   |              |   |   |   |   |     |     |     |

|                 |        | [0]    | IC0: Global interrupt mask bit<br>When this bit is written a '1', it allows interruption to the host. If it is written with a '0', then, it<br>disables all interruption to the host. Writing to this bit does not affect the INT_EN_MASK value. |          |           |         |   |              |   |   |   |   |     |     |     |

### INT\_EN\_MASK

### Interrupt enable mask register

| 15    | 14                                                                                                                                       | 13 | 12      | 11      | 10      | 9 | 8 | 7               | 6 | 5 | 4        | 3   | 2   | 1   | 0   |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|----|---------|---------|---------|---|---|-----------------|---|---|----------|-----|-----|-----|-----|--|

|       |                                                                                                                                          | IN | IT_EN_M | ASK_HIG | θH      |   |   | INT_EN_MASK_LOW |   |   |          |     |     |     |     |  |

|       |                                                                                                                                          |    |         | RI      | ESERVEI | C |   |                 |   |   | IE4      | IE3 | IE2 | IE1 | IE0 |  |

| R     | R                                                                                                                                        | R  | R       | R       | R       | R | R | R               | R | R | RW       | RW  | RW  | RW  | RW  |  |

| 0     | 0                                                                                                                                        | 0  | 0       | 0       | 0       | 0 | 0 | 0               | 0 | 0 | 0        | 0   | 0   | 0   | 0   |  |

| Addre | Address: 06, 07                                                                                                                          |    |         |         |         |   |   |                 |   |   |          |     |     |     |     |  |

| Type: |                                                                                                                                          |    | R, R/V  | V       |         |   |   |                 |   |   |          |     |     |     |     |  |

| Reset | :                                                                                                                                        |    | 0x00    |         |         |   |   |                 |   |   |          |     |     |     |     |  |

| Descr | <b>Description:</b> The interrupt enable mask register is used to enable the interruption from a particula interrupt source to the host. |    |         |         |         |   |   |                 |   |   | rticular |     |     |     |     |  |

- [15:4] RESERVED

- [4:0] IE[x]:

Interrupt Enable Mask (where x = 3 to 0)

IE0: Default value is 0.

IE1: Keypad controller interrupt mask

IE2: Keypad controller FIFO overflow interrupt mask

IE3: GPIO controller interrupt mask

IE4: Combination key interrupt enable

Writing a '1' to the IE[x] bit enables the interruption to the host.

#### INT\_STA

### Interrupt status register

| 15           | 14                | 13 | 12 | 11 | 10 | 9 | 8 | 7            | 6 | 5 | 4   | 3   | 2   | 1   | 0   |

|--------------|-------------------|----|----|----|----|---|---|--------------|---|---|-----|-----|-----|-----|-----|

| INT_STA_HIGH |                   |    |    |    |    |   |   | INT_STA _LOW |   |   |     |     |     |     |     |

|              | RESERVED          |    |    |    |    |   |   |              |   |   | IS4 | IS3 | IS2 | IS1 | IS0 |

| R            | R R R R R R R R R |    |    |    |    |   |   |              | R | R | R   | R   | R   | R   |     |

| 0            | 0                 | 0  | 0  | 0  | 0  | 0 | 0 | 0            | 0 | 0 | 0   | 0   | 0   | 0   | 1   |

| Address:     | 08, 09                                                                                                                                                                                                               |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре:        | R                                                                                                                                                                                                                    |

| Reset:       | 0x00                                                                                                                                                                                                                 |

| Description: | The interrupt status register monitors the status of the interruption from a particular interrupt source to the host. The INT_STA bits are constantly updated regardless whether the INT_EN bits are enabled or not. |

| [15:4]       | RESERVED                                                                                                                                                                                                             |

| [4:0]        | IS[x]<br>Interrupt status (where x = 3 to 0)<br>Read:                                                                                                                                                                |

IS0: Wake-up interrupt status

IS1: Keypad controller interrupt status

IS2: Keypad controller FIFO overflow interrupt status

IS3: GPIO controller interrupt status

IS4: Combination key interrupt status

Reading the INT\_STA register clears all interrupt status bits to '0' which had been set to '1' prior to the read event.

### INT\_EN\_GPIO\_MASK

### Interrupt enabled GPIO mask register

| 7    | 6                    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |  |  |  |

|------|----------------------|------|------|------|------|------|------|--|--|--|--|--|--|

|      | INT_EN_GPIO_MASK_LOW |      |      |      |      |      |      |  |  |  |  |  |  |

| IEG7 | IEG6                 | IEG5 | IEG4 | IEG3 | IEG2 | IEG1 | IEG0 |  |  |  |  |  |  |

| RW   | RW                   | RW   | RW   | RW   | RW   | RW   | RW   |  |  |  |  |  |  |

| 0    | 0                    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |  |  |  |  |

| 15    | 14                   | 13    | 12    | 11    | 10    | 9    | 8    |  |  |  |  |  |  |

|-------|----------------------|-------|-------|-------|-------|------|------|--|--|--|--|--|--|

|       | INT_EN_GPIO_MASK_MID |       |       |       |       |      |      |  |  |  |  |  |  |

| IEG15 | IEG14                | IEG13 | IEG12 | IEG11 | IEG10 | IEG9 | IEG8 |  |  |  |  |  |  |

| RW    | RW                   | RW    | RW    | RW    | RW    | RW   | RW   |  |  |  |  |  |  |

| 0     | 0                    | 0     | 0     | 0     | 0     | 0    | 0    |  |  |  |  |  |  |

| 23                    | 22 | 21    | 20    | 19 | 18 | 17 | 16 |  |  |  |  |  |

|-----------------------|----|-------|-------|----|----|----|----|--|--|--|--|--|

| INT_EN_GPIO_MASK_HIGH |    |       |       |    |    |    |    |  |  |  |  |  |

|                       |    | IEG17 | IEG16 |    |    |    |    |  |  |  |  |  |

| R                     | R  | RW    | RW    |    |    |    |    |  |  |  |  |  |

| 0                     | 0  | 0     | 0     | 0  | 0  | 0  | 0  |  |  |  |  |  |

| Address: 0 | A, 0B, 0C |

|------------|-----------|

|------------|-----------|

Type: R/W

Reset: 0x00

**Description:** The interrupt enable GPIO mask register is used to enable the interruption from a particular GPIO interrupt source to the host. The IEG[17:0] bits are the interrupt enable mask bits correspond to the GPIO[17:0] pins.

[17:0 IEG[x]: Interrupt enable GPIO mask (where x = 17 to 0)Writing a '1' to the IEG[x] bit enables the interruption to the host.

#### NT\_STA\_GPIO

## Interrupt status GPIO register

| 7    | 6                | 5    | 4    | 3    | 2    | 1    | 0    |  |

|------|------------------|------|------|------|------|------|------|--|

|      | INT_STA_GPIO_LOW |      |      |      |      |      |      |  |

| ISG7 | ISG6             | ISG5 | ISG4 | ISG3 | ISG2 | ISG1 | ISG0 |  |

| R    | R                | R    | R    | R    | R    | R    | R    |  |

| 0    | 0                | 0    | 0    | 0    | 0    | 0    | 0    |  |

| 15    | 14               | 13    | 12    | 11    | 10    | 9    | 8    |  |

|-------|------------------|-------|-------|-------|-------|------|------|--|

|       | INT_STA_GPIO_MID |       |       |       |       |      |      |  |

| ISG15 | ISG14            | ISG13 | ISG12 | ISG11 | ISG10 | ISG9 | ISG8 |  |

| R     | R                | R     | R     | R     | R     | R    | R    |  |

| 0     | 0                | 0     | 0     | 0     | 0     | 0    | 0    |  |

| 23                | 22        | 21    | 20    | 19 | 18 | 17 | 16 |

|-------------------|-----------|-------|-------|----|----|----|----|

| INT_STA_GPIO_HIGH |           |       |       |    |    |    |    |

|                   |           | ISG17 | ISG16 |    |    |    |    |

| R                 | R R R R R |       |       |    |    |    | R  |

| 0                 | 0         | 0     | 0     | 0  | 0  | 0  | 0  |

| Address: | 0D, 0E, 0F |

|----------|------------|

|----------|------------|

Type: R

Reset:

**Description:** The interrupt status GPIO register monitors the status of the interruption from a particular GPIO pin interrupt source to the host. The INT\_STA\_GPIO bits are constantly updated regardless whether the INT\_EN\_GPIO\_MASK bits are enabled or not. The ISG[17:0] bits are the interrupt status bits correspond to the GPIO[17:0] pins.

[17:0 ISG[x]

0x00

Interrupt status GPIO (where x = 17 to 0)

ISG[x] will be set to '1' if an interrupt is detected on the corresponding GPIO pin. Reading the INT\_STA\_GPIO register clears all interrupt status GPIO bits to '0' which had been set to '1' prior to the read event.

### 9.3 **Programming sequence**

To configure and initialize the interrupt controller to allow interruption to host, observe the following steps:

- 1. Set the INT\_EN\_MASK and INT\_EN\_GPIO\_MASK registers to the desired values to enable the interrupt sources that are to be expected to receive from.

- 2. Configure the output interrupt type and polarity and enable the global interrupt mask by writing to the INT\_CTRL.

- 3. Wait for interrupt.

- 4. Upon receiving an interrupt, the corresponding INT bit is asserted.

- 5. The host comes to read the INT\_STA register through the I<sup>2</sup>C interface. A '1' in the INT\_STA bits indicates that the corresponding interrupt source is triggered.

- 6. If the IS3 bit in INT\_STA register is set, the interrupt is coming from the GPIO controller. Then, a subsequent read is performed on the INT\_STA\_GPIO register to obtain the interrupt status of all 18 GPIOs to locate the GPIO that triggers the interrupt. This is a 'Hot Key' feature.

- 7. After obtaining the interrupt source that triggers the interrupt, the host performs the necessary processing and operations related to the interrupt source.

- 8. All IS[x] bits in INT\_STA register and ISG[x] bits in INT\_STA\_GPIO register which are set to '1' prior to the read event are cleared to '0' automatically once the reading of the registers are completed.

- 9. Any interrupt inputs received between reading and auto clearing of the registers are kept in a shadow register and updated into the INT\_STA and INT\_STA\_GPIO registers once the auto clearing is completed.

- 10. Once the interrupt is cleared, the INT pin is also de-asserted if the interrupt type is level interrupt. An edge interrupt only asserts a pulse width of 200 µs.

- 11. When the interrupt function is no longer required, the IC0 bit in INT\_CTRL may be set to '0' to disable the global interrupt mask bit.

# 10 GPIO controller

A total of 18 GPIOs are available in the STMPE1801 port expander device. Most of the GPIOs are sharing physical pins with alternate functions. The GPIO controller contains the registers that allow the host system to configure each of the pins into either a GPIO, or one of the alternate functions. Unused GPIOs should be configured as outputs to minimize the power consumption.

| Address | Register name     | Description                     | Auto-increment<br>(during sequential<br>R/W) |

|---------|-------------------|---------------------------------|----------------------------------------------|

| 10      | GPIO_SET_LOW      |                                 | Yes                                          |

| 11      | GPIO_SET_MID      | GPIO set pin state register     | Yes                                          |

| 12      | GPIO_SET_HIGH     |                                 | Yes                                          |

| 13      | GPIO_CLR_LOW      |                                 | Yes                                          |

| 14      | GPIO_CLR_MID      | GPIO clear pin state register   | Yes                                          |

| 15      | GPIO_CLR_HIGH     |                                 | Yes                                          |

| 16      | GPIO_MP_LOW       |                                 | Yes                                          |

| 17      | GPIO_MP_MID       | GPIO monitor pin state register | Yes                                          |

| 18      | GPIO_MP_HIGH      |                                 | Yes                                          |

| 19      | GPIO_SET_DIR_LOW  |                                 | Yes                                          |

| 1A      | GPIO_SET_DIR_MID  | GPIO set pin direction register | Yes                                          |

| 1B      | GPIO_SET_DIR_HIGH |                                 | Yes                                          |

| 1C      | GPIO_RE_LOW       |                                 | Yes                                          |

| 1D      | GPIO_RE_MID       | GPIO rising edge register       | Yes                                          |

| 1E      | GPIO_RE_HIGH      |                                 | Yes                                          |

| 1F      | GPIO_FE_LOW       |                                 | Yes                                          |

| 20      | GPIO_FE_MID       | GPIO falling edge register      | Yes                                          |

| 21      | GPIO_FE_HIGH      |                                 | Yes                                          |

| 22      | GPIO_PULL_UP_LOW  |                                 | Yes                                          |

| 23      | GPIO_PULL_UP_MID  | GPIO pull up register           | Yes                                          |

| 24      | GPIO_PULL_UP_HIGH |                                 | Yes                                          |

Table 13. GPIO controller registers

### 10.1 GPIO control registers

A group of registers is used to control the exact function of each of the 18 GPIOs.

All the GPIO registers are named as GPIO\_xxx\_yyy, where:

- xxx represents the functional group

- yyy represents the byte position of the GPIO (LOW/MID/HIGH)

- LOW registers control GPIO[7:0]

- MID registers control GPIO[8:15]

- HIGH registers control GPIO[17:16]

#### 10.1.1 Bit description

|               | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| GPIO_xxx_HIGH |       |       | RES   | ERVED |       |       | IO-16 | IO-17 |

| GPIO_xxx_MID  | IO-15 | IO-14 | IO-13 | IO-12 | IO-11 | IO-10 | IO-9  | IO-8  |

| GPIO_xxx_LOW  | IO-7  | IO-6  | IO-5  | IO-4  | IO-3  | IO-2  | IO-1  | IO-0  |

The function of each bit is shown in the following table:

| Register name    | Description            | Function                                                                                             |

|------------------|------------------------|------------------------------------------------------------------------------------------------------|

| GPIO_MP_yyy      | GPIO monitor pin state | Reading this bit yields the current state of the bit. Writing has no effect.                         |

| GPIO_SET_yyy     | GPIO set pin state     | Writing '1' to this bit causes the corresponding GPIO to go to '1' state. Writing '0' has no effect. |

| GPIO_CLR_yyy     | GPIO clear pin state   | Writing '1' to this bit causes the corresponding GPIO to go to '0' state. Writing '0' has no effect. |

| GPIO_SET_DIR_yyy | GPIO set pin direction | '0' sets the corresponding GPIO to input state, and '1' sets it to output state.                     |

| GPIO_RE_yyy      | GPIO rising edge       | Set to '1' enable rising edge detection on the corresponding GPIO.                                   |

| GPIO_FE_yyy      | GPIO falling edge      | Set to '1' enable falling edge detection on the corresponding GPIO.                                  |

| GPIO_PULL_UP_yyy | GPIO pull up           | Set to '1' enable internal pull-up resistor.                                                         |

### 10.2 Hotkey feature

A GPIO is known as 'Hotkey' when it is configured to trigger an interruption to the host whenever the GPIO input is being asserted. This feature is applicable in operational mode as well as in Hibernate mode.

#### 10.2.1 Programming sequence for Hotkey

- 1. Configure the GPIO pin into input direction by setting the corresponding bit in the GPIO set pin direction registers [GPIO\_SET\_DIR\_yyy].

- Set the GPIO rising edge registers [GPIO\_RE\_yyy] and GPIO falling edge registers [GPIO\_FE\_yyy] to the desired values to enable the rising edge or falling edge detection.

- 3. Configure and enable the interrupt controller to allow the interruption to the host.