# STW81200

# Wideband RF PLL fractional/integer frequency synthesizer with integrated VCOs and LDOs

Datasheet - production data

#### **Features**

- Output frequency range: 46.875 to 6000 MHz

- · Very low noise

- Normalized in band phase noise floor:

-227 dBc/Hz

- VCO phase noise: -135 dBc/Hz @ 1 MHz offset. 4.0 GHz carrier

- Noise floor: -160 dBc/Hz

- Dual architecture frequency synthesizer: Fractional-N and Integer-N

- Integrated VCOs with automatic center frequency calibration

- Programmable RF output dividers by 1/2/4/8/16/32/64

- Dual RF Output broadband matched with programmable power level and mute function

- External VCO option with 5 V charge pump

- Integrated low noise LDO voltage regulators

- Maximum phase detector frequency: 100 MHz

- Exact frequency mode

- Fast lock and cycle slip reduction

- Differential reference clock input (LVDS and LVECPL compliant) supporting up to 800 MHz

- 13-bit programmable reference frequency divider

- Programmable charge pump current

- Digital lock detector

- · Integrated reference crystal oscillator core

- · R/W SPI interface

- Logic compatibility/tolerance 1.8 V/3.3 V

- Low power functional mode

- Supply voltage: 3.0 V to 5.4 V

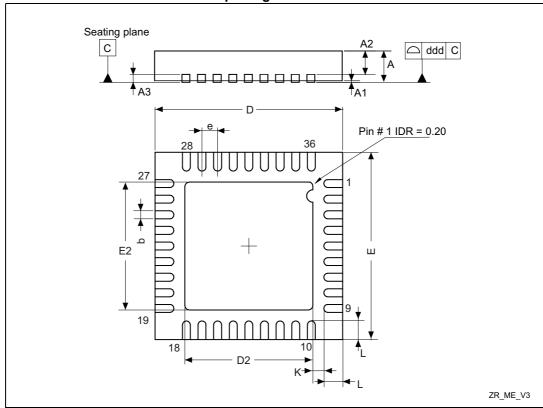

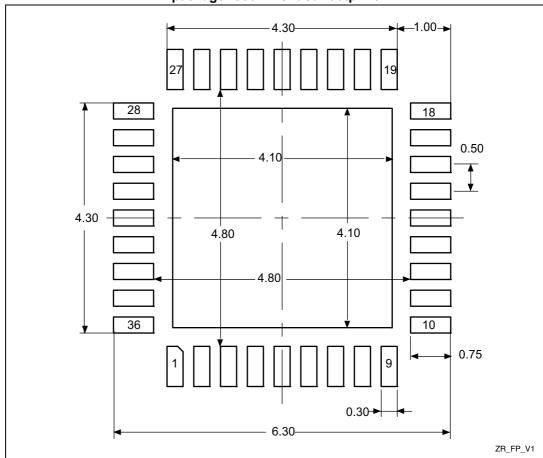

- Small size exposed pad VFQFPN36 package 6 x 6 x 1.0 mm

- Process: BICMOS 0.25 µm SiGe

## **Applications**

- · Cellular/4G infrastructure equipment

- · Instrumentation and test equipment

- Cable TV

- Other wireless communication systems

Table 1. Device summary

|            |          | ,             |

|------------|----------|---------------|

| Order Code | Package  | Packing       |

| STW81200T  | VFQFPN36 | Tray          |

| STW81200TR | VFQFPN36 | Tape and reel |

### Description

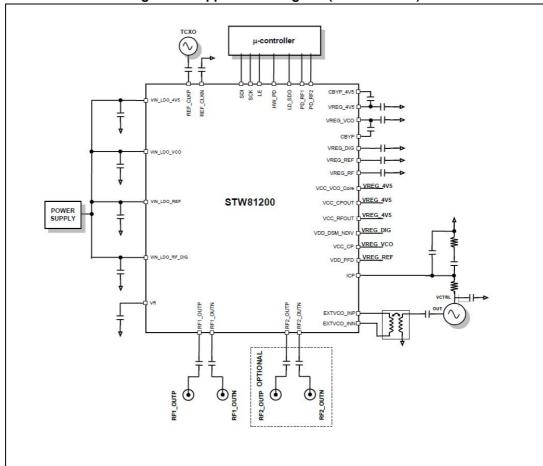

The STW81200 is a dual architecture frequency synthesizer (Fractional-N and Integer-N), that features three low phase-noise VCOs with a fundamental frequency range of 3.0 GHz to 6.0 GHz and a programmable dual RF output divider stage which allows coverage from 46.875 MHz to 6 GHz.

The STW81200 optimizes size and cost of the final application thanks to the integration of low-noise LDO voltage regulators and internally-matched broadband RF outputs.

The STW81200 is compatible with a wide range of supply voltages (from 3.0 V to 5.4 V) providing to the end user a very high level of flexibility which trades off excellent performance with power dissipation requirements. A low-power functional mode (software controlled) gives an extra power saving.

Additional features include crystal oscillator core, external VCO mode and output-mute function.

Contents STW81200

# **Contents**

| 1 | Func  | tional block diagram                              |

|---|-------|---------------------------------------------------|

| 2 | Pin d | efinitions 7                                      |

| 3 | Abso  | olute maximum ratings10                           |

| 4 | Oper  | ating conditions                                  |

| 5 | Elect | rical specifications                              |

| 6 | Туріс | cal performance characteristics                   |

| 7 | Circu | uit description                                   |

|   | 7.1   | Reference input stage                             |

|   | 7.2   | Reference divider                                 |

|   | 7.3   | PLL N divider                                     |

|   |       | 7.3.1 Fractional spurs and compensation mechanism |

|   | 7.4   | Phase frequency detector (PFD)                    |

|   | 7.5   | Lock detect                                       |

|   | 7.6   | Charge pump                                       |

|   | 7.7   | Fast lock mode                                    |

|   | 7.8   | Cycle slip reduction                              |

|   | 7.9   | Voltage controlled oscillators (VCOs)             |

|   | 7.10  | RF output divider stage 30                        |

|   | 7.11  | Low-power functional modes                        |

|   | 7.12  | LDO voltage regulators 32                         |

|   | 7.13  | STW81200 register programming                     |

|   | 7.14  | STW81200 register summary                         |

|   | 7.15  | STW81200 register descriptions                    |

|   | 7.16  | Power ON sequence                                 |

|   | 7.17  | Example of register programming 51                |

|   |       |                                                   |

| STW81200 | Contents |

|----------|----------|

| STW81200 | Contents |

| 8  | Application information 52            |

|----|---------------------------------------|

|    | 8.1 Application diagrams              |

|    | 8.2 Thermal PCB design considerations |

| 9  | Evaluation kit                        |

| 10 | Package information                   |

|    | 10.1 VFQFPN36 package information     |

| 11 | Revision history 59                   |

List of figures STW81200

# **List of figures**

| Figure 1.  | Functional block diagram                                                                    | . 6 |

|------------|---------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Top view                                                                                    |     |

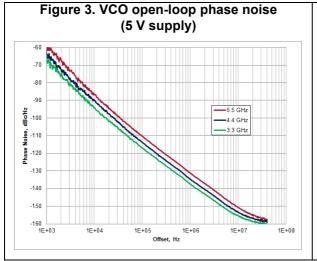

| Figure 3.  | VCO open-loop phase noise (5 V supply)                                                      |     |

| Figure 4.  | Closed-loop phase noise at 4.8 GHz, divided by 1 to 64 (5 V supply)                         | 19  |

| Figure 5.  | VCO open-loop phase noise at 4.4 GHz vs. supply                                             |     |

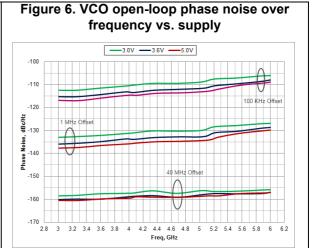

| Figure 6.  | VCO open-loop phase noise over frequency vs. supply                                         | 19  |

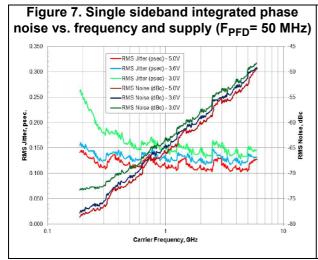

| Figure 7.  | Single sideband integrated phase noise vs. frequency and supply (F <sub>PFD</sub> = 50 MHz) | 20  |

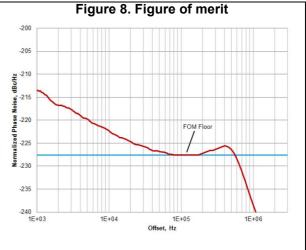

| Figure 8.  | Figure of merit                                                                             |     |

| Figure 9.  | Phase noise and fractional spurs at 2646.96 MHz vs. supply (FPFD = 61.44 MHz)               | 20  |

| Figure 10. | Phase noise and fractional spurs at 2118.24 MHz vs. supply (FPFD = 61.44 MHz)               | 20  |

| Figure 11. | Phase noise and fractional spurs at 2118.24 MHz at 5.0 V supply (FPFD = 61.44 MHz) .        | 20  |

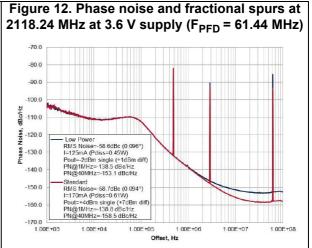

| Figure 12. | Phase noise and fractional spurs at 2118.24 MHz at 3.6 V supply (FPFD = 61.44 MHz) .        | 20  |

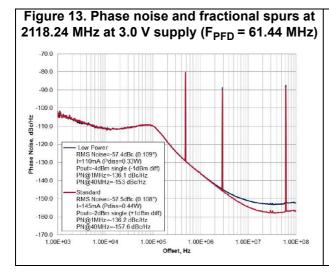

| Figure 13. | Phase noise and fractional spurs at 2118.24 MHz at 3.0 V supply (FPFD = 61.44 MHz) .        | 21  |

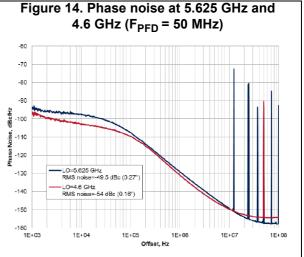

| Figure 14. | Phase noise at 5.625 GHz and 4.6 GHz (FPFD = 50 MHz)                                        |     |

| Figure 15. | Typical VCO control voltage after VCO calibration (3.6 V supply)                            |     |

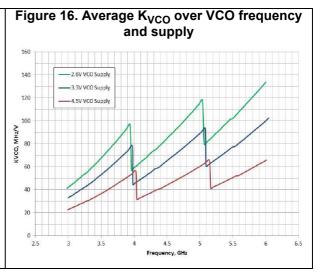

| Figure 16. | Average K <sub>VCO</sub> over VCO frequency and supply                                      | 21  |

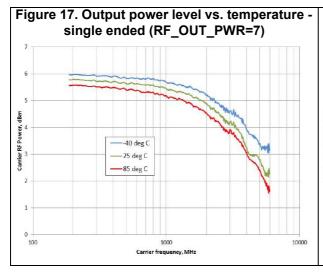

| Figure 17. | Output power level vs. temperature - single ended (RF_OUT_PWR=7)                            | 21  |

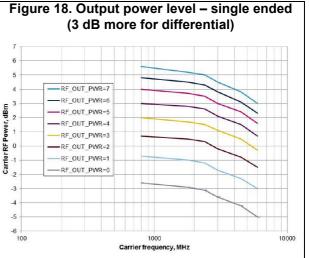

| Figure 18. | Output power level – single ended (3 dB more for differential)                              | 21  |

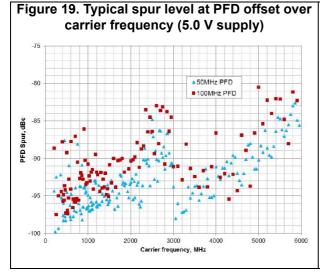

| Figure 19. | Typical spur level at PFD offset over carrier frequency (5.0 V supply)                      | 22  |

| Figure 20. | Typical spur level vs. offset from 4.5 GHz (5.0 V supply, F <sub>PFD</sub> =50MHz)          | 22  |

| Figure 21. | 10 kHz fractional spur (integer boundary) vs. temperature                                   |     |

|            | (5.0 V supply, F <sub>PFD</sub> = 50 MHz)                                                   | 22  |

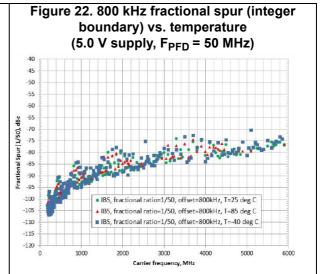

| Figure 22. | 800 kHz fractional spur (integer boundary) vs. temperature                                  |     |

|            | (5.0 V supply, F <sub>PFD</sub> = 50 MHz)                                                   | 22  |

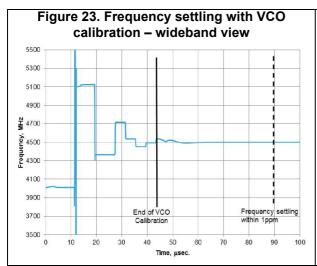

| Figure 23. | Frequency settling with VCO calibration – wideband view                                     | 22  |

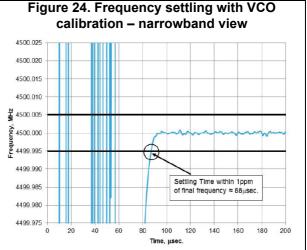

| Figure 24. | Frequency settling with VCO calibration – narrowband view                                   |     |

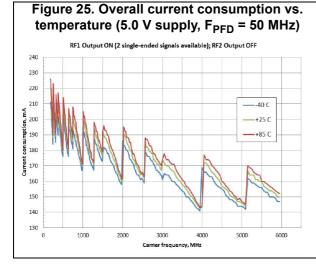

| Figure 25. | Overall current consumption vs. temperature (5.0 V supply, F <sub>PFD</sub> = 50 MHz)       |     |

| Figure 26. | Current consumption – standard vs. low power (5.0 V supply, F <sub>PFD</sub> = 50 MHz)      |     |

| Figure 27. | Current consumption – standard vs. low power (3.6 V supply, F <sub>PFD</sub> = 50 MHz)      |     |

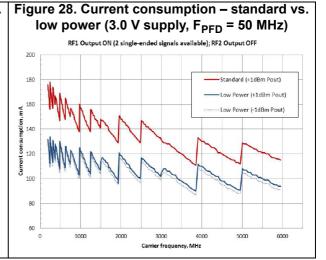

| Figure 28. | Current consumption – standard vs. low power (3.0 V supply, F <sub>PFD</sub> = 50 MHz)      |     |

| Figure 29. | Reference clock buffer configurations: single-ended (A), differential (B), crystal mode (C) |     |

| Figure 30. | PFD diagram                                                                                 |     |

| Figure 31. | SPI Protocol                                                                                |     |

| Figure 32. | SPI timing diagram                                                                          |     |

| Figure 33. | Application diagram (internal VCO)                                                          |     |

| Figure 34. | Application diagram (external VCO)                                                          | 53  |

| Figure 35. | VFQFPN - 36 pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat                |     |

|            | package outline                                                                             | 56  |

| Figure 36. | VFQFPN - 36 pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat                |     |

|            | package recommended footprint                                                               | 58  |

STW81200 List of tables

# List of tables

| Table 1.  | Device summary                                                               | 1  |

|-----------|------------------------------------------------------------------------------|----|

| Table 2.  | Pin description                                                              |    |

| Table 3.  | Absolute maximum ratings                                                     | 10 |

| Table 4.  | Operating conditions                                                         | 11 |

| Table 5.  | Digital logic levels                                                         | 12 |

| Table 6.  | Electrical specifications                                                    | 13 |

| Table 7.  | Phase noise specifications                                                   | 17 |

| Table 8.  | Current value vs. selection                                                  | 29 |

| Table 9.  | Blocks with programmable current and related performance                     | 31 |

| Table 10. | SPI timings                                                                  | 34 |

| Table 11. | SPI Register map (address 12 to 15 not available)                            |    |

| Table 12. | STW81200 order codes                                                         |    |

| Table 13. | VFQFPN - 36 pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat |    |

|           | package mechanical data                                                      | 57 |

| Table 14  | Document revision history                                                    | 59 |

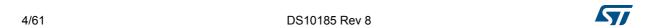

# 1 Functional block diagram

Figure 1. Functional block diagram

STW81200 Pin definitions

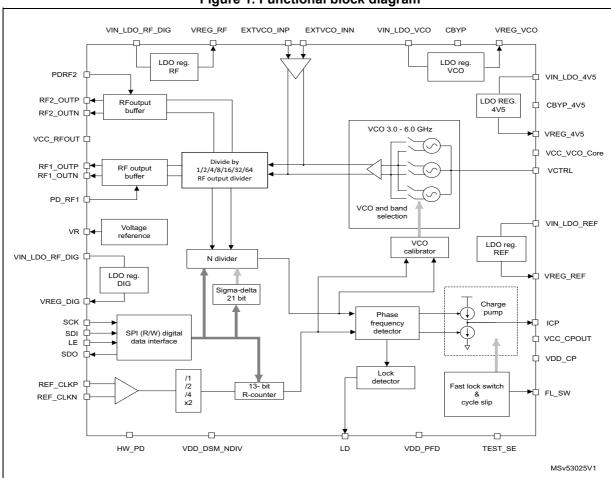

# 2 Pin definitions

Figure 2. Top view

Pin definitions STW81200

Table 2. Pin description

| Pin No | Name         | Description                                               | Observation                                                                                                                                                          |

|--------|--------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | CBYP_4V5     | Connection for 4.5 V regulator bypass capacitor           | -                                                                                                                                                                    |

| 2      | VREG_4V5     | Regulated output voltage for 4.5V regulator               | Adjustable output voltage: 5.0 V, 4.5 V, 2.6 V, 3.3 V                                                                                                                |

| 3      | VCC_VCO_Core | Supply voltage for VCO Core                               | Must be connected to VREG_4V5 or VREG_VCO                                                                                                                            |

| 4      | HW_PD        | HW Power Down                                             | CMOS Schmitt Triggered Input, 1.8 V compatible, 3.3 V tolerant                                                                                                       |

| 5      | PD_RF1       | RF1 output stage Power Down control                       | CMOS Schmitt Triggered Input, 1.8 V compatible, 3.3 V tolerant                                                                                                       |

| 6      | PD_RF2/FL_SW | RF2 output stage Power Down<br>Control / Fast Lock switch | CMOS Schmitt Triggered Input, 1.8 V compatible, 3.3V tolerant (with Fast lock feature disabled); High impedance/ GND shorted output (with Fast Lock feature enabled) |

| 7      | СВҮР         | Connection for VCO circuitry regulator bypass capacitor   | -                                                                                                                                                                    |

| 8      | VREG_VCO     | Regulated output voltage for VCO circuitry regulator      | -                                                                                                                                                                    |

| 9      | VIN_LDO_VCO  | Supply voltage for VCO circuitry regulator                | -                                                                                                                                                                    |

| 10     | VR           | Connection for reference voltage filtering capacitor      | -                                                                                                                                                                    |

| 11     | VCTRL        | VCO control voltage                                       | -                                                                                                                                                                    |

| 12     | EXTVCO_INP   | External VCO positive input                               | This pin must be connected to ground if external VCO is not used                                                                                                     |

| 13     | EXTVCO_INN   | External VCO negative input                               | This pin must be connected to ground if external VCO is not used                                                                                                     |

| 14     | VDD_CP       | Supply voltage for Charge Pump bias                       | This pin must be connected to VREG_VCO                                                                                                                               |

| 15     | ICP          | PLL charge pump output                                    | -                                                                                                                                                                    |

| 16     | VCC_CPOUT    | Supply voltage for Charge Pump output stage               | This pin must be connected to VREG_4V5 or VREG_VCO                                                                                                                   |

| 17     | VDD_PFD      | Supply voltage for PFD                                    | This pin must be connected to VREG_REF                                                                                                                               |

| 18     | VIN_LDO_REF  | Supply voltage for PLL regulator                          | -                                                                                                                                                                    |

| 19     | VREG_REF     | Regulated output voltage for Reference Clock regulator    | -                                                                                                                                                                    |

| 20     | REF_CLKN     | Reference clock negative input                            | -                                                                                                                                                                    |

| 21     | REF_CLKP     | Reference clock positive input                            | -                                                                                                                                                                    |

STW81200 Pin definitions

Table 2. Pin description (continued)

| Pin No | Name           | Description                                                       | Observation                                                                             |

|--------|----------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 22     | LD_SDO         | Lock Detector/SPI Data output                                     | CMOS push-pull Output 2.5V with slew rate control or open drain (1.8V to 3.3V tolerant) |

| 23     | SDI            | SPI Data input                                                    | CMOS Schmitt triggered Input, 1.8 V compatible, 3.3 V tolerant                          |

| 24     | SCK            | SPI clock                                                         | CMOS Schmitt triggered Input, 1.8 V compatible, 3.3 V tolerant                          |

| 25     | LE             | SPI load enable                                                   | CMOS Schmitt triggered Input, 1.8 V compatible, 3.3 V tolerant                          |

| 26     | VDD_DSM_NDIV   | Supply voltage for DSM and N divider                              | This pin must be connected to VREG_DIG                                                  |

| 27     | VREG_DIG       | Regulated output voltage for digital circuitry regulator          | -                                                                                       |

| 28     | VIN_LDO_RF_DIG | Supply voltage for RF Output divider stage and digital regulators | -                                                                                       |

| 29     | VREG_RF        | Regulated output voltage for RF<br>Output Divider stage regulator | -                                                                                       |

| 30     | RF1_OUTN       | Main RF negative output                                           | 50 Ω output impedance                                                                   |

| 31     | RF1_OUTP       | Main RF positive output                                           | 50 Ω output impedance                                                                   |

| 32     | VCC_RFOUT      | Supply voltage for RF Output stages                               | Connected to VREG_DIV, VREG_4V5 or external 5V                                          |

| 33     | RF2_OUTN       | Auxiliary RF negative output                                      | 50 Ω output impedance                                                                   |

| 34     | RF2_OUTP       | Auxiliary RF positive output                                      | 50 Ω output impedance                                                                   |

| 35     | TEST_SE        | Test pin                                                          | This pin must be connected to ground                                                    |

| 36     | VIN_LDO_4V5    | Supply voltage for 4.5 V regulator                                | -                                                                                       |

# 3 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol | Parameter                                                            | Value           | Unit |

|--------|----------------------------------------------------------------------|-----------------|------|

|        | Supply voltage pins #14, #17, #26                                    | -0.3 to 2.7     | V    |

| VCC    | Supply voltage LDOs pins #9, #18, #28, #36                           | -0.3 to 5.4     | V    |

| VCC    | Supply voltage pins #3                                               | -0.3 to 5       | V    |

|        | Supply voltage pins #16, #32                                         | -0.3 to 5.4     | V    |

| Tstg   | Storage temperature                                                  | +150            | °C   |

| ESD    | Electrical Static Discharge HBM <sup>(1)</sup> CDM-JEDEC Standard MM | 2<br>0.5<br>0.2 | kV   |

<sup>1.</sup> The maximum rating of the ESD protection circuitry on pin 21 (REF\_CLKP) is 1.5 kV.

#### **Operating conditions** 4

**Table 4. Operating conditions**

| Symbol            | Parameter                                                              | Test conditions                                           | Min | Тур | Max | Unit |

|-------------------|------------------------------------------------------------------------|-----------------------------------------------------------|-----|-----|-----|------|

|                   | Supply voltage pins #14, #17, #26                                      | -                                                         | 2.5 | -   | 2.7 | V    |

| V <sub>CC</sub>   | Supply voltage (LDOs inputs) pins #9, #18, #28, #36                    | -                                                         | 3.0 | -   | 5.4 | V    |

|                   | Supply voltage pin #3, #16, #32                                        | -                                                         | 2.5 | -   | 5   | V    |

|                   | Current Consumption Pin #3,<br>#16 and #32 supplied at 4.5 V           | DIV2 ON, Main Output only,<br>4 GHz VCO, max. performance | -   | 84  | -   | mA   |

| I <sub>CC</sub>   | Current Consumption Pin #3,<br>#16 and #32 supplied at 2.6 V           |                                                           | -   | 50  | -   | mA   |

|                   | Current consumption other blocks an supplies at 2.6 V                  |                                                           | -   | 110 | -   | mA   |

| T <sub>A</sub>    | Operating ambient temperature                                          | -                                                         | -40 | -   | 85  | °C   |

| TJ                | Maximum junction temperature                                           | -                                                         | -   | -   | 125 | °C   |

| $\Theta_{\sf JA}$ | Junction to ambient package thermal resistance <sup>(1)</sup>          | Multilayer JEDEC board                                    | -   | 33  | -   | °C/W |

| ОЈВ               | Junction to board package thermal resistance <sup>(1)</sup>            | Multilayer JEDEC board                                    | -   | 18  | -   | °C/W |

| Θιс               | Junction to case package thermal resistance <sup>(1)</sup>             | Multilayer JEDEC board                                    | -   | 3   | -   | °C/W |

| Ψ <sub>ЈВ</sub>   | Thermal characterization parameter junction to board <sup>(1)</sup>    | Multilayer JEDEC board                                    | -   | 17  | -   | °C/W |

| Ψуτ               | Thermal characterization parameter junction to top case <sup>(1)</sup> | Multilayer JEDEC board                                    | -   | 0.3 | -   | °C/W |

Refer to JEDEC standard JESD 51-12 for a detailed description of the thermal resistances and thermal parameters. Data here presented are referring to a Multilayer board according to JEDEC standard.

T<sub>J</sub> = T<sub>A</sub> + QJ<sub>A</sub> \* P<sub>diss</sub> (in order to estimate T<sub>J</sub> if ambient temperature T<sub>A</sub> and dissipated power P<sub>diss</sub> are known)

T<sub>J</sub> = T<sub>B</sub> + Y<sub>JB</sub> \* P<sub>diss</sub> (in order to estimate T<sub>J</sub> if ambient temperature T<sub>B</sub> and dissipated power P<sub>diss</sub> are known)

T<sub>J</sub> = T<sub>T</sub> + Y<sub>JT</sub> \* P<sub>diss</sub> (in order to estimate T<sub>J</sub> if ambient temperature T<sub>T</sub> and dissipated power P<sub>diss</sub> are known)

Operating conditions STW81200

# Table 5. Digital logic levels

| Symbol | Parameter                            | Test conditions        | Min     | Тур | Max | Unit |

|--------|--------------------------------------|------------------------|---------|-----|-----|------|

| Vdd    | Internal Supply for digital circuits | -                      | -       | 2.6 | -   | V    |

| Vil    | Low level input voltage              | Schmitt input          | 0       | -   | 0.6 | V    |

| Vih    | High level input voltage             | Schmitt input          | 1.2     | -   | 3.6 | V    |

| Vol    | Low level output voltage             | I <sub>OL</sub> = 4 mA | -       | -   | 0.2 | V    |

| Voh    | High level output voltage            | I <sub>OH</sub> = 4 mA | Vdd-0.2 | -   | -   | V    |

# 5 Electrical specifications

All electrical specifications are given at 25  $^{\rm o}{\rm C}$   ${\rm T}_{\rm AMB}$  and in a full-current mode, unless otherwise stated.

**Table 6. Electrical specifications**

| Symbol              | Parameter                                | Condition                                             | Min    | Тур  | Max    | Units  |

|---------------------|------------------------------------------|-------------------------------------------------------|--------|------|--------|--------|

| Output freq         | uency range                              |                                                       | •      |      |        | •      |

|                     |                                          | Direct output                                         | 3000   | -    | 6000   | MHz    |

| _                   | Output Fraguesia                         | Divider by 2 output                                   | 1500   | -    | 3000   | MHz    |

| F <sub>OUT</sub>    | Output Frequency                         |                                                       |        | -    |        | MHz    |

|                     |                                          | Divider by 64 output                                  | 46.875 | -    | 93.75  | MHz    |

| VCO divide          | rs                                       |                                                       |        |      |        |        |

|                     |                                          | Integer Mode                                          | 24     | -    | 131071 | -      |

|                     |                                          | Fractional mode (DSM 1 <sup>st</sup> Order)           | 24     | -    | 510    | -      |

| N                   | VCO Divider Ratio                        | Fractional mode (DSM 2 <sup>nd</sup> Order)           | 25     | -    | 509    | -      |

|                     |                                          | Fractional mode (DSM 3 <sup>rd</sup> Order)           | 27     | -    | 507    | -      |

|                     |                                          | Fractional mode (DSM 4 <sup>st</sup> Order)           | 31     | -    | 503    | -      |

| Xtal oscilla        | tor                                      |                                                       |        |      |        |        |

| F <sub>XTAL</sub>   | XTAL frequency range                     | -                                                     | 10     | -    | 50     | MHz    |

| ESR <sub>XTAL</sub> | XTAL ESR                                 | -                                                     | -      | -    | 50     | Ω      |

| P <sub>XTAL</sub>   | XTAL Power Dissipation                   | -                                                     | -      | -    | 5      | mW     |

| CIN <sub>XTAL</sub> | XTAL Oscillator Input capacitance        | Single ended                                          | 0.6    | -    | -      | pF     |

| PN <sub>XTAL</sub>  | XTAL Oscillator Phase<br>Noise Floor     | 50 MHz XTAL                                           | -      | -162 | -      | dBc/Hz |

| TOL <sub>XTAL</sub> | XTAL Oscillator accuracy                 | @12 MHz, 25 °C                                        | -      | -    | 10     | ppm    |

| Reference           | clock and phase frequency                | detector                                              |        |      |        |        |

|                     | Reference input frequency <sup>(1)</sup> | -                                                     | 10     | -    | 800    | MHz    |

| F <sub>ref</sub>    | Defendance in a few will it              | Differential Mode                                     | 0.2    | 1    | 1.25   | Vp     |

|                     | Reference input sensitivity              | Single Ended Mode                                     | 0.35   | 1    | 1.25   | Vp     |

| DN                  | Reference Input Buffer Phase             | Single Ended Mode @100 MHz, sinusoidal signal 1.25 Vp | -      | -163 | -      | dBc/Hz |

| PN <sub>REFIN</sub> | Noise Floor                              | LVDS signal @100 MHz<br>400 mVp                       | -      | -159 | -      | dBc/Hz |

Table 6. Electrical specifications (continued)

| Symbol                 | Parameter                                    | Condition                        | Min  | Тур    | Max                  | Units |  |

|------------------------|----------------------------------------------|----------------------------------|------|--------|----------------------|-------|--|

|                        |                                              | Differential Mode                | -    | 10     | -                    |       |  |

| I <sub>REF</sub>       | Current consumption <sup>(2)</sup>           | Single Ended Mode                | -    | 3      | -                    | mA    |  |

|                        |                                              | XTAL oscillator Mode             | -    | 5      | -                    |       |  |

| R                      | Reference Divider Ratio                      | -                                | 1    | -      | 8191                 |       |  |

| F <sub>PFD</sub>       | PFD input frequency <sup>(3)</sup>           | -                                | -    | -      | 100                  | MHz   |  |

|                        |                                              | LO direct output                 | -    | 47.5   | -                    | Hz    |  |

| _                      | Frequency step <sup>(3)</sup>                | LO with divider by 2             | -    | 23.75  | -                    | Hz    |  |

| F <sub>STEP</sub>      | Frequency step                               |                                  | -    |        | -                    | Hz    |  |

|                        |                                              | LO with divider by 64            | -    | 0.7422 | -                    | Hz    |  |

| Charge pum             | p                                            |                                  |      |        |                      |       |  |

| VCC <sub>CPOUT</sub>   | CP Supply                                    | Pin # 16 (VCC_CPOUT)             | 2.5  | -      | 5                    | V     |  |

| I <sub>CP</sub>        | ICP sink/source                              | 5-bit programmable               | -    | -      | 4.9                  | mA    |  |

| V <sub>ICP</sub>       | Output voltage range on ICP pin (pin#14)     | -                                | 0.4  | -      | VCC <sub>CPOUT</sub> | V     |  |

| -                      | Comparison frequency<br>Spurs <sup>(4)</sup> | -                                | -    | -85    | - dBc                |       |  |

| -                      | In-Band Fractional Spurs                     | -                                | -    | -50    | -                    | UBC   |  |

| VCOs                   |                                              |                                  | •    |        |                      |       |  |

| VCC <sub>VCOCore</sub> | VCO Core Supply                              | Pin # 3 (VCC_VCO_Core)           | 2.5  | -      | 5                    | ٧     |  |

|                        |                                              | @ 4 GHz and 4.5 V supply         | -    | 52     | -                    | mA    |  |

| I <sub>VCOCore</sub>   | Oscillator Core current consumption          | @ 4 GHz and 3.3 V supply         | -    | 35     | -                    |       |  |

|                        |                                              | @ 4 GHz and 2.6 V supply         | -    | 30     | -                    |       |  |

| I <sub>VCOBUF</sub>    | VCO buffer consumption                       | Pin # 3 (VCC_VCO_Core)           | -    | 35     | -                    | mA    |  |

| K <sub>VCO</sub>       | VCO gain                                     | -                                | -    | 35-95  | -                    | MHz/V |  |

|                        | Maximum temperature                          | Pin #16 @4.5/5 V                 | -125 | -      | 125                  | °С    |  |

| $\Delta T_{LK}$        | variation for continuous                     | Pin #16 @3.3 V                   | -125 | -      | 125                  | °С    |  |

|                        | lock <sup>(6)(7)</sup>                       | Pin #16 @2.6 V                   | -125 | -      | 115                  | °С    |  |

| RF output st           | tage                                         |                                  |      |        |                      |       |  |

| VCC <sub>RFOUT</sub>   | RF Output supply                             | Pin # 35 (VCC_RFOUT)             | 2.5  | -      | 5                    | ٧     |  |

|                        | Output level                                 | Differential 3.3 V to 5 V supply | -1   | -      | +7                   |       |  |

| P <sub>OUT</sub>       | -                                            | Differential 2.6 V supply        | -1   | -      | +1                   | dBm   |  |

| 7                      |                                              | Differential                     | -    | 100    | -                    | Ω     |  |

| Z <sub>OUT</sub>       | Output impedance                             | Single Ended                     | -    | 50     | -                    | Ω     |  |

| R <sub>L</sub>         | Return Loss                                  | Matched to 50-ohm Single Ended   | -    | 15     | -                    | dB    |  |

Table 6. Electrical specifications (continued)

| Symbol                | Parameter                                           | Condition                                                              | Min | Тур     | Max | Units |

|-----------------------|-----------------------------------------------------|------------------------------------------------------------------------|-----|---------|-----|-------|

|                       |                                                     | Direct output (single/differential)                                    | -   | -30/-40 | -   | dBc   |

| H <sub>2</sub>        | LO 2 <sup>nd</sup> Harmonic                         | Divided output (single/differential)                                   | -   | -30/-35 | -   | dBc   |

|                       |                                                     | Direct output (single/differential)                                    | -   | -15/-15 | -   | dBc   |

| H <sub>3</sub>        | LO 3 <sup>rd</sup> Harmonic                         | Divided output (single/differential)                                   | -   | -15/-15 | -   | dBc   |

| D                     | Level of Signal with RF                             | Direct output @4 GHz<br>(single/diff)                                  | -   | -45/-60 | -   | dBm   |

| P <sub>MUTE</sub>     | Mute Enabled                                        | Divided output @2 GHz (single/diff)                                    | -   | -45/-60 | -   | dBm   |

| P <sub>ISO</sub>      | Main/aux port isolation                             | Direct output @4 GHz<br>(single/diff)                                  | -   | -35/-40 | -   | dBc   |

|                       | iviain/aux port isolation                           | Divided output @2 GHz (single/diff)                                    | -   | -40/-45 | -   | dBc   |

|                       | RF Divider Current<br>Consumption <sup>(8)</sup>    | Direct output (1 differential output)                                  | -   | 28      | -   | mA    |

|                       |                                                     | DIV2 buff (1 differential output)                                      | -   | 47      | -   |       |

|                       |                                                     | DIV4 buff (1 differential output)                                      | -   | 56      | -   |       |

| I <sub>DIV</sub>      |                                                     | DIV8 buff (1 differential output)                                      | -   | 65      | -   |       |

| 2                     |                                                     | DIV16 buff (1 differential output)                                     | -   | 75      | -   |       |

|                       |                                                     | DIV32 buff (1 differential output)                                     | -   | 83      |     |       |

|                       |                                                     | DIV64 buff (1 differential output)                                     | -   | 92      | -   |       |

|                       |                                                     | Auxiliary path enabled                                                 | -   | 19      | -   |       |

| I <sub>RFOUTBUF</sub> | RF Output Buffer Current Consumption <sup>(8)</sup> | 3.3 V to 5 V supply (1 differential output; P <sub>OUT</sub> = +7 dBm) | -   | 25      | -   |       |

|                       |                                                     | 3.3 V to 5 V Auxiliary path enabled                                    | -   | 25      | -   | mA    |

|                       |                                                     | 2.6 V supply (1 differential output; P <sub>OUT</sub> = +1 dBm)        | -   | 12      | -   |       |

|                       |                                                     | 2.6 V Auxiliary path enabled                                           | -   | 12      | -   |       |

#### Table 6. Electrical specifications (continued)

| Symbol           | Parameter                                                   | Condition                          | Min | Тур | Max | Units |

|------------------|-------------------------------------------------------------|------------------------------------|-----|-----|-----|-------|

| PLL miscella     | aneous                                                      |                                    |     |     |     |       |

| I <sub>PLL</sub> | PLL current<br>Consumption <sup>(8)</sup>                   | Prescaler, digital dividers, misc. | -   | 20  | -   | mA    |

| I <sub>DSM</sub> | $\Delta\Sigma$ Modulator current consumption <sup>(8)</sup> | -                                  | -   | 3.5 | -   | mA    |

- 1. The maximum frequency of the Reference Divider is 200 MHz; when using higher reference clock frequency (up to the max. value of 800 MHz) the internal divider by 2 or divider by 4 must be enabled. The fractional mode is allowed in the full frequency range only with reference clock frequency >11.93 MHz With reference clock frequency in the range 10 MHz to 11.93 MHz, due to the limits of N value in fractional mode, the full VCO frequencies would not be addressed in fractional mode; in this case the frequency doubler in the reference path can be enabled.

- 2. Reference clock signal @ 100 MHz, R=2

- 3. The minimum frequency step is obtained as F<sub>PFD</sub> / (2^21); these typical values are obtained considering F<sub>PFD</sub> = 100 MHz.

- 4. PFD frequency leakage.

- This is the level inside the PLL loop bandwidth due to the contribution of the ΔΣ Modulator. In order to obtain the fractional spurs level for a specific frequency offset, the attenuation provided by the loop filter at such offset should be subtracted.

- Once a VCO is programmed at the initial temperature T<sub>0</sub> inside the operating temperature range (-40 °C to +85 °C), the synthesizer is able to maintain the lock status only if the temperature drift (in either direction) is within the limit specified by ΔT<sub>LK</sub>, provided that the final temperature T<sub>f</sub> is still inside the nominal range.

- 7. In order to guarantee the performance of  $\Delta T_{LK}$  the bit CAL\_TEMP\_COMP in register ST6 must be set to '1'.

- 8. Current consumption measured with PLL locked in following conditions: Reference clock signal @ 100 MHz; PFD @50 MHz (R=2); VCO @ 4005 MHz

**47**/

Table 7. Phase noise specifications

| Parameter                                                                                    | Min          | Тур       | Max          | Units  |  |  |  |  |

|----------------------------------------------------------------------------------------------|--------------|-----------|--------------|--------|--|--|--|--|

| Normalized In-Band Phase Noise <sup>(1)</sup> Floor <sup>(2)</sup>                           | -            | -227      | -            | dBc/Hz |  |  |  |  |

| VCO Open Loop Phase Noise <sup>(1)</sup> at F <sub>OUT</sub> @ 4 GHz – VIN=5.0 V, VREG=4.5 V |              |           |              |        |  |  |  |  |

| Phase Noise @ 1 kHz                                                                          | -            | -64       | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 10 kHz                                                                         | -            | -91       | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 100 kHz                                                                        | -            | -114      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 1 MHz                                                                          | -            | -135      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 10 MHz                                                                         | -            | -154      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 100 MHz                                                                        | -            | -160      | -            | dBc/Hz |  |  |  |  |

| VCO Open Loop Phase Noise <sup>(1)</sup> at F <sub>OUT</sub> @ 4 GHz/2 = 2GHz – VIN=5.       | 0 V, VREG=   | 4.5 V     | •            | -      |  |  |  |  |

| Phase Noise @ 1 kHz                                                                          | -            | -70       | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 10 kHz                                                                         | -            | -97       | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 100 kHz                                                                        | -            | -120      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 1 MHz                                                                          | -            | -141      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 10 MHz                                                                         | -            | -156      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 40 MHz                                                                         | -            | -159      | -            | dBc/Hz |  |  |  |  |

| VCO Open Loop Phase Noise <sup>(1)</sup> at F <sub>OUT</sub> @ 4 GHz/4 = 1 GHz – VIN=5       | 5.0 V, VREG  | =4.5 V    | •            |        |  |  |  |  |

| Phase Noise @ 1 kHz                                                                          | -            | -76       | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 10 kHz                                                                         | -            | -103      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 100 kHz                                                                        | -            | -126      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 1 MHz                                                                          | -            | -146      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 10 MHz                                                                         | -            | -159      | -            | dBc/Hz |  |  |  |  |

| Phase Noise Floor                                                                            | -            | -160      | -            | dBc/Hz |  |  |  |  |

| VCO Open Loop Phase Noise <sup>(1)</sup> at F <sub>OUT</sub> @ 4 GHz/32 = 125 MHz – VI       | IN=5.0 V, VF | REG=4.5 \ | /            | ı      |  |  |  |  |

| Phase Noise @ 1 kHz                                                                          | -            | -92       | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 10 kHz                                                                         | -            | -121      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 100 kHz                                                                        | -            | -144      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 1 MHz                                                                          | -            | -161      | -            | dBc/Hz |  |  |  |  |

| Phase Noise @ 10 MHz                                                                         | -            | -163      | -            | dBc/Hz |  |  |  |  |

| Phase Noise Floor                                                                            |              | -164      | <del> </del> | dBc/Hz |  |  |  |  |

DS10185 Rev 8 17/61

Table 7. Phase noise specifications

| Parameter                                                                                    | Min | Тур    | Max | Units  |  |  |  |

|----------------------------------------------------------------------------------------------|-----|--------|-----|--------|--|--|--|

| VCO Open Loop Phase Noise <sup>(1)</sup> at F <sub>OUT</sub> @ 4 GHz – VIN=3.6V , VREG=3.3 V |     |        |     |        |  |  |  |

| Phase Noise @ 1 kHz                                                                          | -   | -62    | -   | dBc/Hz |  |  |  |

| Phase Noise @ 10 kHz                                                                         | -   | -89    | -   | dBc/Hz |  |  |  |

| Phase Noise @ 100 kHz                                                                        | -   | -113.2 | -   | dBc/Hz |  |  |  |

| Phase Noise @ 1 MHz                                                                          | -   | -133.6 | -   | dBc/Hz |  |  |  |

| Phase Noise @ 10 MHz                                                                         | -   | -152.4 | -   | dBc/Hz |  |  |  |

| Phase Noise @ 100 MHz                                                                        | -   | -158.5 | -   | dBc/Hz |  |  |  |

| VCO Open Loop Phase Noise <sup>(1)</sup> at F <sub>OUT</sub> @ 4 GHz – VIN=3.0 V, VREG=2.6 V |     |        |     |        |  |  |  |

| Phase Noise @ 1 kHz                                                                          | -   | -60.5  | -   | dBc/Hz |  |  |  |

| Phase Noise @ 10 kHz                                                                         | -   | -88    | -   | dBc/Hz |  |  |  |

| Phase Noise @ 100 kHz                                                                        | -   | -110.3 | -   | dBc/Hz |  |  |  |

| Phase Noise @ 1 MHz                                                                          | -   | -131   | -   | dBc/Hz |  |  |  |

| Phase Noise @ 10 MHz                                                                         | -   | -150   | -   | dBc/Hz |  |  |  |

| Phase Noise @ 100 MHz                                                                        | -   | -157   | -   | dBc/Hz |  |  |  |

<sup>1.</sup> Phase Noise SSB unless otherwise specified. The VCO Open loop figures are specified at 4.5/5 V on VCC\_VCO\_Core (pin #3).

<sup>2.</sup> Normalized PN = Measured PN  $- 20log(N) - 10log(F_{PFD})$  where N is the VCO divider ratio and  $F_{PFD}$  is the comparison frequency at the PFD input.

# **6** Typical performance characteristics

Figure 4. Closed-loop phase noise at 4.8 GHz, divided by 1 to 64 (5 V supply)

-70.0

-80.0

-90.0

-100.0

-100.0

-100.0

-100.0

-150.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-160.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-170.0

-17

19/61

DS10185 Rev 8

Figure 9. Phase noise and fractional spurs at 2646.96 MHz vs. supply (F<sub>PFD</sub> = 61.44 MHz)

-70.0

-80.0

-90.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

-100.0

Figure 10. Phase noise and fractional spurs at 2118.24 MHz vs. supply  $(F_{PFD} = 61.44 \text{ MHz})$ -80.0 -90.0 -110.0 =VIN=3.0V (VREG\_4V5=2.6V) RMS Noise=-57.5dBc (0.108°) I=145mA (Pdiss=0.44VV) Pout=-2dBm single (+1dBm diff) PN@1MHz=-136.2 dBc/Hz -120.0 VIN=3.6V (VREG\_4V5=3.3V) RMS Noise=-58.7dBc (0.094°) I=170m4 (Pdiss=0.61VV) Pout=+4dBm single (+7dBm diff PN@1MHz=-138.8 dBc/Hz -150.0 PN@ IMHZ--138.8 dBC/H2 VIN-5.0V (VREG\_4V5-4.5V) RMS Noise=-59.5dBc (0.088\*) I=185rrA (Pdiss=0.93W) Pout=+4dBm single (+7dBm diff) PN@1MHz=-140.6 dBc/H2 -160.0 -170.0 1E+05 Offset, Hz 1E+03 1E+04 1E+07 1E+08

Figure 11. Phase noise and fractional spurs at 2118.24 MHz at 5.0 V supply  $(F_{PFD} = 61.44 \text{ MHz})$ -80.0 100.0 -110.0 -120.0 Low Power RMS Noise=-59.4dB: (0.087°) I=140mA (Pdiss=0.7W) Pout=-2dBm single (+1dBm diff) PN@10H1z=-140.3 dBc/Hz PN@40MHz=-153.2 dBc/Hz **8** -130.0 -140.0 Standard RMS Noise=-59.5dBc (0.086°) 1=185mA (Pdiss=0.93W) Pout=+4d6m single (+7dBm di PN@1MHz=-140.6 dBc/Hz PN@40MHz=-158.3 dBc/Hz Standard -150.0 -170.0 1.00E+03 1.00E+05 1. Offset, Hz 1.00E+04 1.00E+07 1.00E+08

21/61

577

DS10185 Rev 8

Figure 20. Typical spur level vs. offset from

4.5 GHz (5.0 V supply, F<sub>PFD</sub>=50MHz)

577

Figure 27. Current consumption – standard vs. low power (3.6 V supply, F<sub>PFD</sub> = 50 MHz)

RF1 Output ON (2 single-ended signals available); RF2 Output OFF

220

Standard (+7dBm Pout)

Low Power (+7dBm Pout)

Low Power (+1dBm Pout)

120

120

Carrier frequency, MHz

DS10185 Rev 8

# 7 Circuit description

### 7.1 Reference input stage

The reference input stage provides different modes for the reference clock signal.

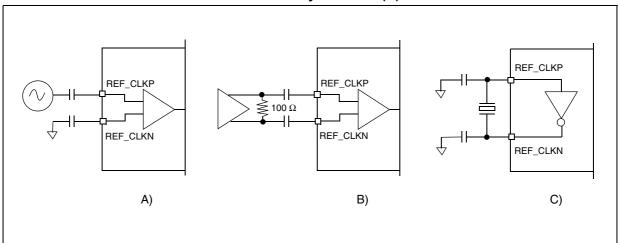

Both single-ended and differential modes (LVDS, LVECPL) are supported; a crystal mode is also provided in order to build a Pierce type crystal oscillator. *Figure* 29 shows the connections required for the different configurations supported.

In single-ended and differential modes the inputs must be AC coupled as the REF\_CLKP and REF\_CLKN pins are internally biased to an optimal DC operating point. The input resistance is 100 ohms differential and the best performance for phase noise is obtained for signals with a higher slew rate, such as a square wave.

Figure 29. Reference clock buffer configurations: single-ended (A), differential (B), crystal mode (C)

#### 7.2 Reference divider

The 13-bit programmable reference counter is used to divide the input reference frequency to the desired PFD frequency. The division ratio is programmable from 1 to 8191.

The maximum allowed input frequency of the R-Counter is 200 MHz.

The reference clock can be extended up to 400 MHz enabling the divide-by-2 stage or up to 800 MHz enabling the divide-by-4 stage.

A frequency doubler is provided in order to double low reference frequencies and increase the PFD operating frequency thus allowing an easier filtering of the out-of-band noise of the Delta-Sigma Modulator; the doubler is introducing a noise degradation in the in-band PLL noise thus this feature should be carefully used.

When the doubler is enabled, the maximum reference frequency is limited to 25 MHz.

STW81200 Circuit description

#### 7.3 PLL N divider

The N divider sets the division ratio in the PLL feedback path.

Both Integer-N and Fractional-N PLL architectures are implemented in order to ensure the best overall performance of the synthesizer.

The Fractional-N division is achieved combining the integer divider section with a Delta-Sigma modulator (DSM) which sets the fractional part of the overall division ratio.

The DSM is implemented as a MASH structure with programmable order (2 bit; 1<sup>st</sup>, 2<sup>nd</sup>, 3<sup>rd</sup> and 4<sup>th</sup> order), programmable MODULUS (21 bit).

It includes also a DITHERING function (1 bit) which can be used to reduce fractional spur tones by spreading the DSM sequence and consequently the energy of the spurs over a wider bandwidth.

The overall division ratio N is given by:

$$N = N_{INT} + N_{FRAC}$$

The integer part  $N_{INT}$  is 17-bit programmable and can range from 24 to 131071 in Integer Mode. For  $N_{INT} \ge 512$  the fractional mode is not allowed and the setting used for DSM does not have any effect.

Based upon the selected order of the Delta-Sigma Modulator the allowed range of  $N_{\text{INT}}$  values changes as follows:

- 24 to 510 1st Order DSM

- 25 to 509 2nd Order DSM

- 27 to 507 3rd Order DSM

- 31 to 503 4th Order DSM

The fractional part N<sub>FRAC</sub> of the division ratio is controlled by setting the values FRAC and MOD (21 bits each) and it depends also on the value of DITHERING (1 bit):

$$N_{FRAC} = \frac{FRAC}{MOD} + \frac{DITHERING}{2 \cdot MOD}$$

The MOD value can range from 2 to 2097151, while the range of FRAC is from 0 to MOD-1. If the DITHERING function is not used (DITHERING=0) the fractional part of N is simply achieved as ratio of FRAC over MOD.

DS10185 Rev 8 25/61

The resulting VCO frequency is:

$$F_{VCO} = \frac{F_{ref}}{R} \cdot \ N = \frac{F_{ref}}{R} \cdot \ \left( N_{INT} + \frac{FRAC}{MOD} + \frac{DITHERING}{2 \cdot MOD} \right)$$

where:

F<sub>VCO</sub> is the output frequency of VCO

F<sub>ref</sub> is the input reference frequency

R is the division ratio of reference chain

N is the overall division ratio of the PLL

The implementation with programmable modulus allows the user to select easily the desired fraction and the exact synthesized frequency without any approximation.

The MOD value can be set to very high values thus the frequency resolution of the synthesizer can reach very fine steps (down to a few hertz).

A 'low spur mode' could be configured by maximizing both FRAC and MOD values, keeping the same desired FRAC/MOD ratio, and setting the DITHERING bit to '1'. The drawback is a small frequency error, equal to  $F_{PFD}/(2*MOD)$ , on the synthesized frequency which is in the range of a few hertz, usually tolerated by most applications.

#### 7.3.1 Fractional spurs and compensation mechanism

The fractional PLL operation generates unwanted fractional spurs around the synthesized frequency.

The integer boundary spurs occur when the carrier frequency is close to an integer multiple of the PFD frequency. If the frequency difference between the carrier and the N\*F<sub>PFD</sub> falls inside the PLL loop bandwidth, the integer boundary spur is unfiltered and represents the worst case situation giving the highest spur level.

The channel spurs are generated by the delta-sigma modulator operations and depend on its settings (they are mainly related to the MOD value). The channel spurs appear at a frequency offset from the carrier, equal to  $F_{PFD}/MOD$  and its harmonics, and they are not integer boundary. If the MOD value is extremely high (close to the maximum value of  $2^{21}$ -1) the channel spur offset is of the order of a tenth of a Hertz and it appears as 'granular noise' shaped by the PLL around the carrier.

The STW81200 provides the user with three different mechanisms to compensate fractional spurs: PFD delay mode, charge pump leakage current and down-split current. These features should be adopted case-by-case as they give different results spur-level results depending on setup conditions (reference clock frequency, PFD frequency, DSM setup, VCO frequency, carrier frequency, charge pump current, VCO/charge pump supply voltage).

STW81200 Circuit description

#### PFD delay mode

The STW81200 implements two programmable differentiated delay lines in the reset path of the main flip-flop of the PFD. This allow different delay reset values to be set for VCO divided path and reference-clock divided path, allowing an offset value to be forced on the PFD and charge-pump characteristics, far enough from the zero in order to guarantee that the whole circuit works in a more linear region.

It is possible to set the sign of the delay through the PFD\_DEL\_MODE bit in the *ST3 Register* (no delay, VCO\_DIV\_delayed or REF\_DIV\_delayed). The delay value can be set through the PFD\_DEL bit in the *ST0 Register* (2 bit; 0=1.2 ns, 1=1.9 ns, 2=2.5 ns, 3=3.0 ns). Even though the for spur-compensation settings are best optimized case-by-case, the setup 'VCO\_DIV\_delayed + 1.2 ns delay' is strongly recommended for most conditions.

#### Charge pump leakage current

A different way to force an offset value on the PFD+CP characteristics is provided within the STW81200 by sourcing or sinking a DC leakage current from the charge pump (settings available in the ST3 Register). The leakage current is 5-bit programmable starting from a base DC current of 10  $\mu$ A (it can be doubled to 20 uA by setting bit CP\_LEAK\_x2 = 1b). The sign is set by CP\_LEAK\_DIR bit: 0b = down-leakage (sink), 1b = up-leakage (source).

The resulting delay offset can be calculated as follows:

$$delay = \frac{I_{LEAK}}{F_{PFD} \cdot I_{CP}}$$

Experimental results show that down-leakage currents are more effective than up-leakage. The user must be aware that the use of the leakage current mechanism might impact the overall phase noise performance by increasing the charge pump noise contribution.

#### **Down-split current**

This mechanism is enabled through the DNSPLIT\_EN bit (*ST3 Register*), is the injection of a down-split current pulse from the charge pump circuit. The current pulse is 16 VCO cycles wide while the current level is set by the PFD\_DEL bit (*ST0 Register*) among 4 different possible values: 0, 0.25\*ICP, 0.5\*ICP or 0.75\*ICP.

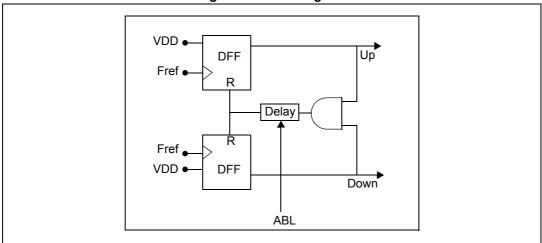

# 7.4 Phase frequency detector (PFD)

The PFD takes inputs from the reference and the VCO dividers and produces an output proportional to the phase error. The PFD includes a delay gate that controls the width of the anti-backlash pulse (1.2 to 3 ns). This pulse ensures that there is no dead zone in the PFD transfer function.

Figure 30 shows a simplified schematic of the PFD.

DS10185 Rev 8 27/61

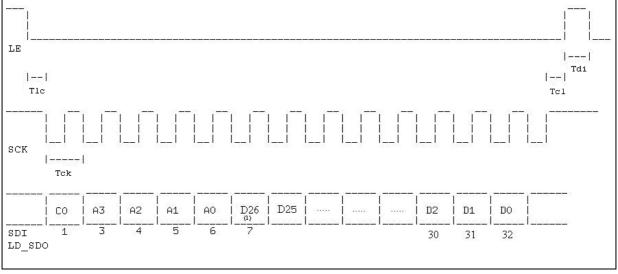

Figure 30. PFD diagram

#### 7.5 Lock detect

The lock detector indicates the lock state for the PLL. The lock condition is detected by comparing the UP and DOWN outputs of the digital Phase Frequency Detector

A CMOS logic output signal indicates the lock state; the polarity of the output signal can be inverted using the LD\_ACTIVELOW bit.

The lock condition occurs when the delay between the edges of UP and DOWN signals is lower than a specific value (3-bit programmable from 2 ns to 16 ns) and this condition is stable for a specific number of consecutive PFD cycles (3-bit programmable counter from 4 to 4096 cycles).

This flexibility is needed by the lock detector circuitry to work properly with all the possible different PLL setups (Integer-N, Fractional-N, different PFD frequencies and so on).

# 7.6 Charge pump

This block drives two matched current sources, lup and Idown, which are controlled respectively by the UP and DOWN PFD outputs. The nominal value of the output current  $(I_{CP})$  can be set by a 5-bit word.

The minimum value of the output current ( $I_{CP}$ ) is 158  $\mu$ A.

The charge pump also includes a compensation circuit to take into account the  $K_{VCO}$  variation versus VCO control voltage, which changes with temperature and process for a specified frequency. The  $K_{VCO}$  compensation block adjusts the nominal ICP value, minimizing the variation of the product  $I_{CP}$  x  $K_{VCO}$  to keep the PLL bandwidth constant for the specified frequency.

In order to compensate the change of  $K_{VCO}$  over frequency, the user should manually adjust the  $I_{CP}$  value to keep the PLL bandwidth constant.

In addition, the charge-pump output stage can operate with a 2.5 V to 5.0 V supply voltage. The LDO\_4V5 regulator, programmable at 2.6 V, 3.3 V and 4.5 V, can be used for this purpose. The CP\_SUPPLY\_MODE[1:0] field (*ST4 Register*) must be set according to the supply voltage.

STW81200 Circuit description

CPSEL4 CPSEL2 CPSEL1 **CPSEL0** CPSEL3 Current Value 0 0 0 0 0 0 0 0 0 158 uA  $I_{MIN}$  $2*I_{MIN}$ 0 0 316 µA \_ 1 1 0 1 1 29\*I<sub>MIN</sub> 4.58 mA 30\*I<sub>MIN</sub> 1 1 1 1 0 4.74 mA 1 1 1 1 1 4.9 mA 31\*I<sub>MIN</sub>

Table 8. Current value vs. selection

#### 7.7 Fast lock mode

The fast-lock feature can be enabled to trade fast settling time with spurs rejection, performances which generally require different settings of PLL bandwidth (narrow for better spurs rejection and wide for fast settling time).

A narrow bandwidth for lower spurs can be designed for the lock state while a wider bandwidth can be designed for the PLL transients.

The wider bandwidth is achieved during the transient by increasing the charge pump current and reducing accordingly the dumping resistor value of the loop filter in order to keep the phase margin of the PLL constant. The duration of the PLL wide band mode, in terms of number of PFD cycles, is set by programming the fast lock 13 bit counter.

## 7.8 Cycle slip reduction

The use of high  $F_{PFD}/PLL_BW$  ratios may lead to an increased settling time due to cycle slips.

A cycle slip compensation circuit is provided which automatically increases the charge pump current for high frequency errors and restores the programmed value at the end of the locking phase.

# 7.9 Voltage controlled oscillators (VCOs)

The STW81200 VCO section consists of three separate low-noise VCOs with different LC Tanks structures to cover a wide band from 3000 MHz to 6000 MHz.

Each VCO is implemented using a structure with multiple sub-bands to keep low the VCO sensitivity (Kvco), thus resulting in low phase noise and spurs performances.

The correct VCO and sub-band selection is automatically performed by dedicated digital circuitry (clocked by the PFD) at every new frequency programming. The VCO calibration starts when the *STO Register* is written.

During the selection procedure the VCTRL of the VCO is charged to a fixed reference voltage. A stable reference clock signal to the device must be present before the VCO calibration begins. The procedure for the VCO and sub-band selection takes approximately 11 CALB<sub>CLK</sub> cycles.

The calibrator clock frequency is linked to the PFD frequency (CALB<sub>CLK</sub> =  $F_{PFD}$ /CALDIV) and should be adjusted in order to achieve correct operation. The maximum allowed frequency is 250 kHz, therefore the calibrator divider ratio (CALDIV, *ST6 Register*) must be set accordingly.

When the PLL is configured in Integer mode only (NINT ≥ 512, see Section 7.3: PLL N divider) the calibrator divider should be bypassed (CALDIV = 1). In such a case, if the setup of the application requires a PFD frequency higher than 250 kHz the calibration procedure must be executed in two steps:

- VCO calibration. Configure all the device registers (see Section 7.17: Example of register programming) making sure to program the desired VCO frequency with proper settings of the values N (STO Register) and R (ST3 Register) so that F<sub>PFD</sub> is ≤ 250 kHz

- 2. **Final operating setup**. Adjust the values N and R properly in order to program the device with the desired setup configuration (VCO and PFD frequency), and also set the VCO CALB DISABLE bit to '1' (STO Register).

Once the correct VCO and sub-band are selected the normal PLL operations are resumed.

The VCO core can be supplied from 2.5 to 5 V. The LDO\_4V5 regulator (programmable to 4.5 V, 3.3 V and 2.6 V) is used for this purpose. Furthermore, the amplitude of oscillation, which trades current consumption for phase noise performance, is 4-bit programmable (*ST4 Register*, VCO\_AMP bit). *Section 7.15: STW81200 register descriptions* shows the allowed ranges of oscillation amplitude for each available supply setting. In order to achieve the best phase noise performance, the maximum amplitude setting is recommended.

## 7.10 RF output divider stage

The signal coming from the VCOs is fed to a flexible RF divider stage.

The divider ratio is programmable among different values (1, 2, 4, 8,16, 32 and 64) and allows the selection of the desired output frequency band:

- 3.0 to 6.0 GHz (divider ratio = 1)

- 1.5 to 3.0 GHz (divider ratio = 2)

- 0.75 to 1.5 GHz (divider ratio = 4)

- 375 to 750 MHz (divider ratio = 8)

- 187.5 to 375 MHz (divider ratio = 16)

- 93.75 to 187.5 MHz (divider ratio = 32)

- 46.875 to 93.75 MHz (divider ratio = 64)

The final output stage buffer (pins RF1\_OUTP, RF1\_OUTN) is internally broadband matched to 100-ohm differential (50-ohm single-ended) and it delivers up to +7 dBm of output power on a 100-ohm differential load (+4 dBm on 50-ohm from each single-ended output).

The final output stage buffer has a 3-bit programmable output level and can be powered down by software and/or hardware (pin PD\_RF1) while the internal PLL is locked. The related circuitry, together with VCO and charge pump, is compatible with supply voltages

STW81200 Circuit description

ranging from 2.5 V to 5 V. The regulator LDO\_4V5, which supplies this block, can be set to 4.5 V, 3.3 V or 2.6 V. When supplied at 2.6 V, only the lowest 2 power levels are allowed (see *ST4 Register* settings, RF\_OUT\_PWR bit)

An auxiliary output stage buffer (pins RF2\_OUTP and RF2\_OUTN) is available with the same features of the main one.

The RF division ratio of this auxiliary output can be set independently from the main output in order to increase the flexibility. Furthermore it is possible to get, on the auxiliary output, a signal in phase or in quadrature with the main one, if the same frequency is selected on both outputs.

The auxiliary output stage can also be powered down by software and/or hardware (pin PD RF2).

The output stage can be muted until the PLL achieves the lock status; this function can be activated by software.

### 7.11 Low-power functional modes

All the performance characteristics defined in the electrical specifications are achieved in full current mode. The STW81200 is able to provide a set of low power functional modes which allows control of the current consumption of the different blocks.

This feature can be helpful for those applications requiring low power consumption. The power saving modes trade the current consumption with the phase noise performance, and/or output level.

The current of the blocks defined in *Table 9* can be set by software, and the power saved on each block affect a specific performance as described in the same table.

| p                                            |                           |                                      |  |  |  |  |  |

|----------------------------------------------|---------------------------|--------------------------------------|--|--|--|--|--|

| Block                                        | Current Control bits      | Affected Performance                 |  |  |  |  |  |

| VCO Core                                     | ST4 Register bits[18:15]  | VCO phase noise (offset >PLL_BW)     |  |  |  |  |  |

| VCO Buffers and mux ST5 Register bits[12:11] |                           | Phase Noise Floor (offset > ~10 MHz) |  |  |  |  |  |

| RF Dividers Core                             | ST5 Register bits [10:4]  | Phase Noise Floor (offset > ~10 MHz) |  |  |  |  |  |

| RF output stage                              | ST4 Register bits [25:23] | RF output level                      |  |  |  |  |  |

Table 9. Blocks with programmable current and related performance

### 7.12 LDO voltage regulators

Low drop-out (LDO) voltage regulators are integrated to provide the synthesizer with stable supply voltages against input voltage, load and temperature variations. Five regulators are included to ensure proper isolation among circuit blocks. These regulators are listed below along with the target specifications for the regulated output voltage and current capability:

LDO\_DIG (to supply the digital circuitry),

Vreg = 2.6 V, Imax = 50 mA, Vin Range: 3.0 to 5.4 V

LDO\_REF (to supply the PLL),

Vreg = 2.6 V, Imax = 50 mA, Vin Range: 3.0 to 5.4 V

• LDO\_RF (to supply the rf blocks),

Vreg = 2.6 V, Imax = 100 mA, Vin Range: 3.0 to 5.4 V

LDO\_VCO (to supply the low-voltage VCO sub-blocks):

Vreg = 2.6 V, Imax = 100 mA, Vin Range: 3.0 to 5.4 V

LDO\_4V5 (to supply high-voltage sub-blocks):

Vreg = 4.5 V, 3.3 V and 2.6 V programmable, Imax = 150 mA