#### TDE1708DFT

#### Intelligent power switch

#### **Features**

- Low side or high side switch configuration

- 6 V to 48 V supply voltage range

- Overload and short circuit protections

- Internal voltage clamping

- Supply and output reversal protection

- Thermal shutdown

- GND and V<sub>S</sub> open wire protection

- Adjustable delay at switch on

- Indicator status led driver

- +5 V regulated aux. voltage

- High burst immunity

#### **Description**

The TDE1708DFT is an integrated power switch with up to 48 V power supply capability. Two output configurations are possible:

Load to GND (high side mode)

Load to V<sub>S</sub> (low side mode)

Especially dedicated to proximity detectors, its internal +5 V supply can be used to supply external circuits (See also AN495).

A signal is internally generated to block the In signal, and prevent activation of the output switch, as long as an abnormal condition is detected. The power-on transition, as well as the chip over temperature and the output overcurrent, concur to the generation of such signal. A minimum delay of 25 ms (Typ. value) is added to the trailing edge of such signal to ensure that a stable normal situation is present when the signal disappears. The delay (of the disappearance of the block signal; no delay at its on set) can be further increased connecting a capacitor between pin3 and ground. It can drive resistive or inductive loads.

Table 1. Device summary

| Order code Temp. range, °C  |  | Package   | Packing       |  |

|-----------------------------|--|-----------|---------------|--|

| TDE1708DFT -25 °C to +85 °C |  | DFN (4x4) | Tape and reel |  |

Contents TDE1708DFT

### **Contents**

| 1 | Bloc | k and pin connection diagrams                    | 3  |

|---|------|--------------------------------------------------|----|

| 2 | Elec | trical specifications                            | 5  |

|   | 2.1  | Thermal data                                     | 5  |

|   | 2.2  | Absolute maximum ratings                         | 5  |

|   | 2.3  | Electrical characteristics                       | 6  |

|   | 2.4  | Dynamic information                              | 7  |

| 3 | Арр  | lication information                             | 8  |

|   | 3.1  | Adjustable input hysteresis circuit              | 9  |

| 4 | Pack | kage mechanical data                             | 10 |

|   | 4.1  | Foot print recommended                           | 10 |

|   | 4.2  | DFN (4x4) mechanical data and package dimensions | 11 |

| 5 | Revi | sion history                                     | 13 |

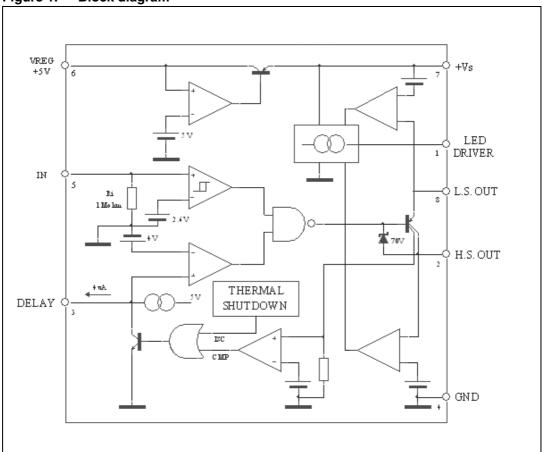

## 1 Block and pin connection diagrams

57

8 7 2 6 3 5

Pin connection diagram (top view) Figure 2.

Table 2. Pin functions

| Pin N <sup>o</sup> | Function                 |  |

|--------------------|--------------------------|--|

| 1                  | Led driver               |  |

| 2                  | High side output         |  |

| 3                  | Delay capacitance source |  |

| 4                  | Ground                   |  |

| 5                  | Input                    |  |

| 6                  | Reg. voltage source      |  |

| 7                  | Supply voltage           |  |

| 8                  | Low side output          |  |

Note: Lead frame can be connected to ground.

## 2 Electrical specifications

#### 2.1 Thermal data

Table 3. Thermal data

| Symbol            | Description                                | Value             | Unit |

|-------------------|--------------------------------------------|-------------------|------|

| R <sub>thJA</sub> | Thermal resistance junction-ambient. (max) | 32 <sup>(1)</sup> | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction-case. (max)    | 1.2               | °C/W |

<sup>1.</sup> Soldered to a 4 layer board with 4 vias in the pad.

## 2.2 Absolute maximum ratings

Table 4. Absolute maximum ratings

| Symbol             | Parameter                      | Value              | Unit |

|--------------------|--------------------------------|--------------------|------|

| V <sub>S</sub>     | Supply voltage                 | 50                 | V    |

| V <sub>S</sub>     | Supply reverse voltage         | 50                 | V    |

| Io                 | Output current                 | internally limited | Α    |

| V <sub>reg</sub>   | Regulated voltage pin          | 0 to 7             | V    |

| V <sub>delay</sub> | Delay cap. source pin          | 0 to 5             | V    |

| V <sub>o</sub>     | Output dif. voltage            | 55                 | V    |

| V <sub>i</sub>     | Input voltage                  | -10 to 50          | V    |

| $T_J$              | Junction operating temperature | Internally limited | °C   |

| T <sub>stg</sub>   | Storage temperature range      | -55 to 150         | °C   |

| P <sub>tot</sub>   | Power dissipation              | internally limited | mW   |

| E <sub>i</sub>     | Energy inductive load          | 100                | mJ   |

#### 2.3 Electrical characteristics

Table 5. Electrical characteristics  $(V_S = 24 \text{ V}; T_J = -25 \text{ to } +85 ^{\circ}\text{C} \text{ unless otherwise specified})$

| Symbol            | Parameter                                        | Test conditions                                                   | Min  | Тур | Max        | Unit                     |

|-------------------|--------------------------------------------------|-------------------------------------------------------------------|------|-----|------------|--------------------------|

| Vs                | Supply voltage                                   |                                                                   | 6    |     | 48         | V                        |

| I <sub>sr</sub>   | Supply reverse current                           | V <sub>SR</sub> = -48 V                                           |      |     | 1.5        | mA                       |

| Iq                | Quiescent current                                | $I_{reg} = I_{led} = 0; V_i < 2 V;$<br>V <sub>S</sub> = 6 to 48 V |      |     | 1.5        | mA                       |

| Io                | Output current                                   | V <sub>s</sub> = 6 to 48 V                                        |      |     | 250        | mA                       |

| V <sub>sat</sub>  | Output voltage drop                              | I <sub>o</sub> = 200 mA                                           |      | 1   | 1.5        | V                        |

| I <sub>SCLS</sub> | Short circuit current in low side configuration  |                                                                   | 0.3  | 0.4 | 0.6        | А                        |

| I <sub>SCHS</sub> | Short circuit current in high side configuration |                                                                   | 0.25 | 0.3 | 0.40       | Α                        |

| V <sub>cl</sub>   | Internal voltage clamp                           | I <sub>CL</sub> = 10 mA                                           | 55   |     | 70         | V                        |

| l <sub>olk</sub>  | Output leakage                                   | (Pin 2)<br>$V_i < 2 V; V_o = 0 \text{ to } V_s \text{ (Pin 8)}$   |      | 100 | 300<br>100 | μ <b>Α</b><br>μ <b>Α</b> |

| V <sub>ith</sub>  | Input voltage threshold                          |                                                                   | 2    |     | 3          | V                        |

| V <sub>ihis</sub> | Input threshold hysteresis                       |                                                                   |      | 300 |            | mV                       |

| I <sub>lk</sub>   | Input current                                    | V <sub>i</sub> = 5 V                                              |      | 2   | 5          | μА                       |

| V <sub>reg</sub>  | Regulated output voltage                         | I <sub>reg</sub> < 5 mA                                           | 4.5  | 5   | 5.5        | V                        |

| I <sub>scr</sub>  | Short circuit regulated                          |                                                                   | 6    | 30  | 50         | mA                       |

| I <sub>reg</sub>  | Output regulator current                         | V <sub>s</sub> = 35 V<br>V <sub>s</sub> = 48 V                    |      |     | 6<br>4     | mA<br>mA                 |

| I <sub>old</sub>  | Current source sink led driver                   | Output ON (±)                                                     | 2    | 3   | 4          | mA                       |

| V <sub>old</sub>  | Voltage drop led driver                          | I <sub>os</sub> = 2 mA (±)                                        |      | 1.2 | 1.6        | V                        |

| Oldlk             | LED driver (off) Leak.                           | $V_i$ < 2 V; $R_L$ < 1 k $\Omega$                                 |      |     | 10         | μА                       |

| I <sub>dch</sub>  | Del. cap. charge current                         | T 25 °C                                                           | 2    | 4   | 6          | μΑ                       |

| V <sub>dth</sub>  | Delay voltage trigger                            |                                                                   |      | 4   |            | V                        |

| T <sub>TSD</sub>  | Thermal shutdown temperature                     |                                                                   |      | 180 |            | °C                       |

### 2.4 Dynamic information

Table 6. Dynamic information (V<sub>S</sub> = 24 V; T<sub>J</sub> = 25 °C; R<sub>L</sub> = 48  $\Omega$ )

| Symbol             | Parameter                                              | Test conditions | Min  | Тур | Max | Unit |

|--------------------|--------------------------------------------------------|-----------------|------|-----|-----|------|

| t <sub>on</sub>    | Propagation turn on time                               | $V_i = 0$ to 5V |      | 15  |     | μS   |

| t <sub>off</sub>   | Propagation turn off time                              |                 |      | 15  |     | μS   |

| t <sub>don</sub>   | Delayed turn on time / nF delay capacitor              |                 | 0.65 | 1   | 2   | ms   |

| t <sub>d min</sub> | Minimum delayed t <sub>on</sub><br>Delay capacitor = 0 |                 |      | 25  |     | μS   |

**577**

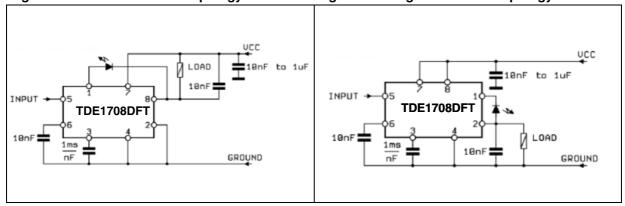

### 3 Application information

The LED driver tells the output status. It can source or sink current ( $I_{old\ typ} = 3\ mA$ ), according to the output configuration chosen. The thresholds, represented by the output comparator in the block diagram, are set at about 1.5 V - 2 V.

For instance, in the high side load case of the Application Circuit, when the voltage on pin 8 (the output) differs from  $V_{CC}$  less than 1.5 V, the output is sensed in "OFF" state and the LED driver is disabled.

If instead pin 8 differs from  $V_{CC}$  more than 3 V (the output comparator threshold value plus the drop voltage on the LED), then the output is sensed "ON" and the driver will force the current on the LED.

Figure 3. Low side driver topology

Figure 4. High side driver topology

TDE1708DFT Application information

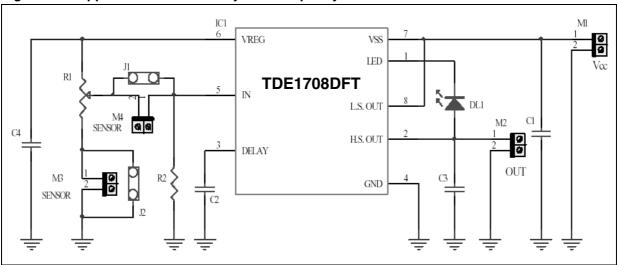

#### 3.1 Adjustable input hysteresis circuit

The TDE1708DFT is a device realized in bipolar technology and therefore it has the usual problems of temperature compensation that such technology involves; despite all it maintains an input dynamics within 1 V over industrial temperatures range.

In all input voltage range it will guarantee a high impedance of 1 M $\Omega$  determining an input current about 2  $\mu A$ .

Exploiting this input high impedance is possible connects a sensor directly on it and bypass the obstacle of active signal conditioning circuit using a voltage firm point as ground of sensor, the delay capacitor, connected on the pin 3, as low pass filter and capacitor on Vreg pin to minimize the noise on it and protect for errors the low-voltage internal circuits, according AN495.

In *Figure 5.* the input external network is optimized for accepting both a sensor with ground connected to the body and a sensor with independent ground.

In order to ground the body of the sensor, J1 has to be shorted, while J2 opened and connect the sensor on M3; in case of independent ground J1 must be opened, J2 shorted and the sensor connected on M4.

DL1 indicate commutation status of the device output and C3 realize a simple output filtering in case is used an inductive load. With C2 about 10 nF we obtain a good filtering and immunity from input voltage noise. C4 is 4,7nF according AN495.

R2 is an optional resistor plugged only when the sensor needs to adapt its impedance with the input impedance of device.

Figure 5. Application circuit for adjustable input hysteresis

### 4 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

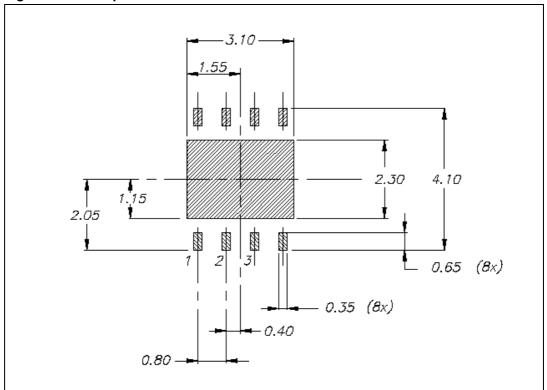

### 4.1 Foot print recommended

Figure 6. Foot print

47/

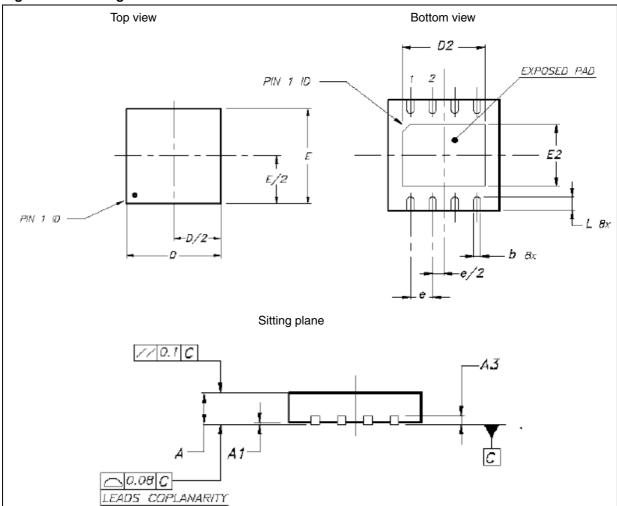

## 4.2 DFN (4x4) mechanical data and package dimensions

Table 7. Package dimensions

| Dim.   | mm   |      |      |  |

|--------|------|------|------|--|

| Dilli. | Тур  | Min  | Max  |  |

| Α      | 0.90 | 0.80 | 1    |  |

| A1     | 0.02 | 0    | 0.05 |  |

| A3     | 0.20 |      |      |  |

| b      | 0.30 | 0.23 | 0.38 |  |

| D      | 4    | 3.90 | 4.10 |  |

| D2     | 3    | 2.82 | 3.23 |  |

| E      | 4    | 3.90 | 4.10 |  |

| E2     | 2.20 |      | 2.30 |  |

| е      | 0.80 |      |      |  |

| L      | 0.50 | 0.40 | 0.60 |  |

**577**

Figure 7. Package dimension

TDE1708DFT Revision history

# 5 Revision history

Figure 8. Document revision history

| Date        | Revision | Changes                                                                                  |

|-------------|----------|------------------------------------------------------------------------------------------|

| 26-Jun-2006 | 1        | Initial release.                                                                         |

| 31-Oct-2006 | 2        | Updated package in cover page, inserted low/high side I <sub>SC</sub> in <i>Table</i> 5. |

| 09-Jan-2007 | 3        | Updated I <sub>SCHS</sub> in <i>Table 5 on page 6</i> .                                  |

| 27-Feb-2009 | 4        | Updated cover page                                                                       |