### **TGA2237-SM**

### 0.03-2.5 GHz 10 W GaN Power Amplifier

#### **Product Overview**

Qorvo's TGA2237-SM is a wideband distributed amplifier fabricated on Qorvo's production 0.25 um GaN on SiC process. The TGA2237-SM operates from 0.03–2.5 GHz and provides greater than 10 W of saturated output power with greater than 13 dB of large signal gain and greater than 50% power-added efficiency.

The TGA2237-SM is available in a low-cost, surface mount 32 lead 5 x 5 AlN QFN. It is ideally suited to support both radar and communication applications across defense and commercial markets as well as electronic warfare. The TGA2237-SM is fully matched to  $50\Omega$  at both RF ports allowing for simple system integration. DC blocks are required on both RF ports and the drain voltage must be injected through an off chip bias-tee on the RF output port.

Lead-free and RoHS compliant.

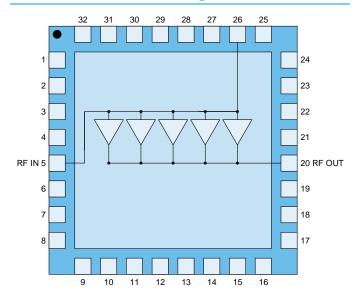

#### **Functional Block Diagram**

#### **Key Features**

Frequency Range: 0.03–2.5 GHz

P<sub>SAT</sub>: >40 dBm at P<sub>IN</sub> = 27 dBm

P1 dB: >33 dBmPAE: >50%

Large Signal Gain: >13 dB

Small Signal Gain: >19 dB

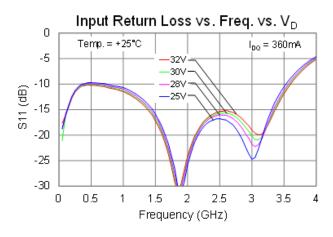

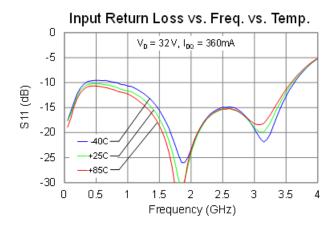

Input Return Loss: >10 dB

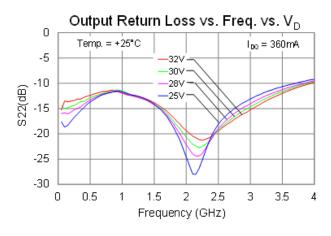

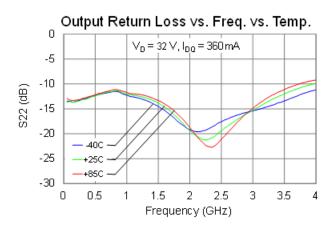

Output Return Loss: >12 dB

Bias: V<sub>D</sub> = 32 V, I<sub>DQ</sub> = 360 mA

Wideband Flat Power

• Package Dimensions: 5.0 x 5.0 x 1.45 mm

### **Applications**

· Commercial and Military Radar

Communications

• Electronic Warfare

### **Ordering Information**

| Part No.       | Description                              |  |

|----------------|------------------------------------------|--|

| TGA2237-SM     | 0.03–2.5 GHz 10 W GaN Power<br>Amplifier |  |

| TGA2237-SM EVB | Evaluation Board                         |  |

### **Absolute Maximum Ratings**

| Parameter                                                         | Value/Range           |  |

|-------------------------------------------------------------------|-----------------------|--|

| Drain Voltage (V <sub>D</sub> )                                   | 40 V                  |  |

| Gate Voltage Range (V <sub>G</sub> )                              | -8 to 0 V             |  |

| Drain Current (I <sub>D</sub> )                                   | 1.2 A                 |  |

| Gate Current (I <sub>G</sub> )                                    | -2.4 to 8.4 mA        |  |

| Power Dissipation (P <sub>DISS</sub> ), 85 °C                     | 19 W                  |  |

| Input Power (P <sub>IN</sub> ), CW, 50 Ω, 85 °C                   | 33 dBm <sup>(*)</sup> |  |

| Input Power ( $P_{IN}$ ), CW, VSWR 3:1, VD = 32V, 85 °C           | 33 dBm <sup>(*)</sup> |  |

| Max VSWR, CW, $P_{IN} = 27 \text{ dBm}$ , VD = 32 V, 85 °C (Load) | 10:1                  |  |

| Mounting Temperature (30 Seconds)                                 | 260 °C                |  |

| Storage Temperature                                               | -55 to 150 °C         |  |

Operation of this device outside the parameter ranges given above may cause permanent damage. These are stress ratings only, and functional operation of the device at these conditions is not implied

### **Recommended Operating Conditions**

| Parameter                       | Value/Range |  |  |

|---------------------------------|-------------|--|--|

| Drain Voltage (V <sub>D</sub> ) | 32 V        |  |  |

| Drain Current (IDQ)             | 360 mA      |  |  |

Electrical specifications are measured at specified test conditions. Specifications are not guaranteed over all recommended operating conditions.

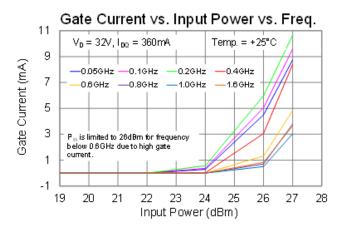

(\*) Operational input power must be limited to 26 dBm when operating below 0.6 GHz to prevent excessive forward gate current.

## **Electrical Specifications**

Test conditions unless otherwise noted: 25 °C,  $V_D$  = 32 V,  $I_{DQ}$  = 360 mA

| Parameter                                                     | Min   | Typical | Max | Units  |

|---------------------------------------------------------------|-------|---------|-----|--------|

| Operational Frequency Range                                   | 0.03  |         | 2.5 | GHz    |

| Small Signal Gain                                             |       | >19     |     | dB     |

| Input Return Loss                                             |       | >10     |     | dB     |

| Output Return Loss                                            |       | >12     |     | dB     |

| Output Power (P <sub>IN</sub> = 27 dBm)                       |       | >40     |     | dBm    |

| Power Added Efficiency (P <sub>IN</sub> = 27 dBm)             |       | >50     |     | %      |

| Power @ 1 dB Compression (P1 dB)                              |       | >33     |     | dBm    |

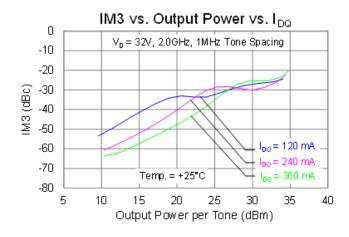

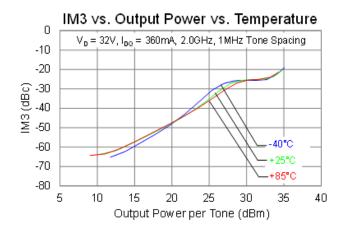

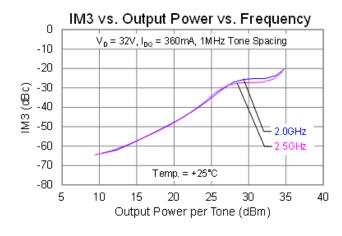

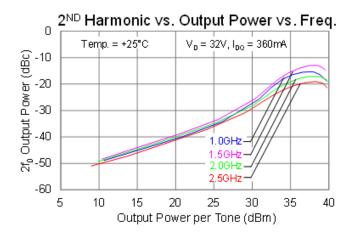

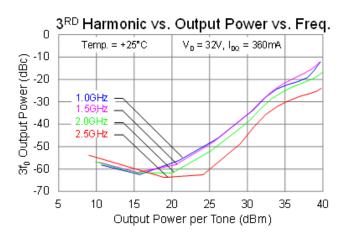

| IM3 @ POUT/tone = 30 dBm                                      |       | -25     |     | dBc    |

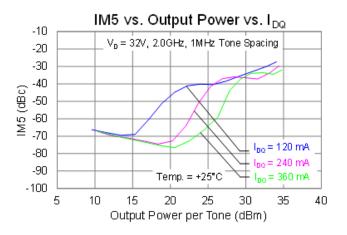

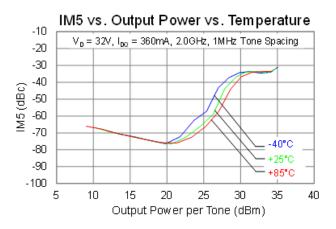

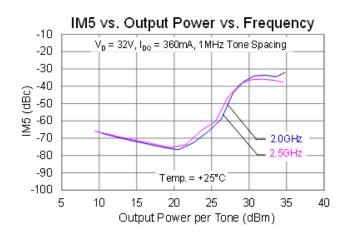

| IM5 @ POUT/tone = 30 dBm                                      |       | -33     |     | dBc    |

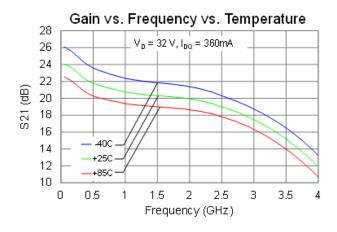

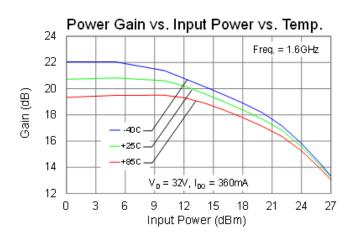

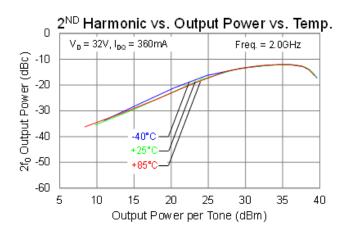

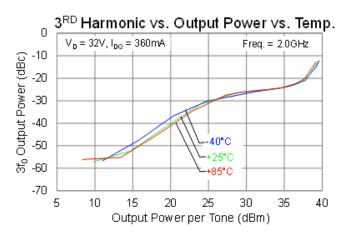

| Small Signal Gain Temperature Coefficient                     |       | -0.03   |     | dB/°C  |

| Output Power Temperature Coefficient                          |       | -0.002  |     | dBm/°C |

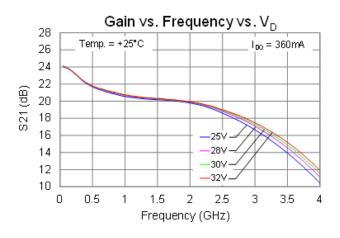

| Recommended Operating Voltage:                                | 20    | 32      |     | V      |

| Gate Leakage (V <sub>D</sub> = 10 V, V <sub>G</sub> = −3.7 V) | -2.64 |         |     | mA     |

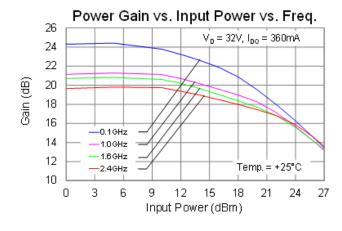

## **Typical Performance: Small Signal**

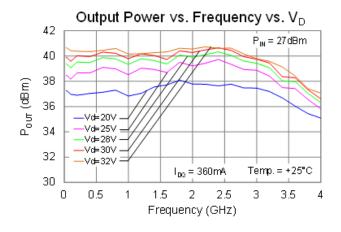

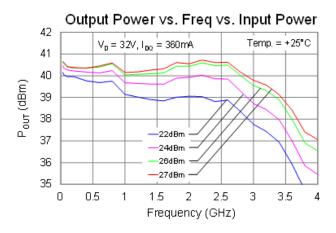

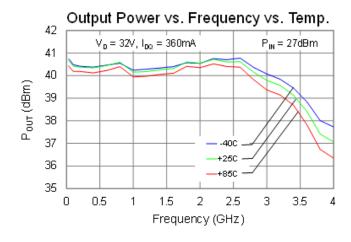

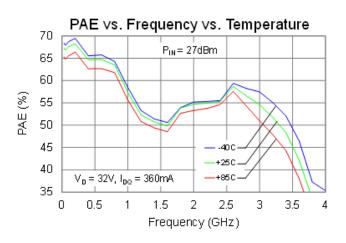

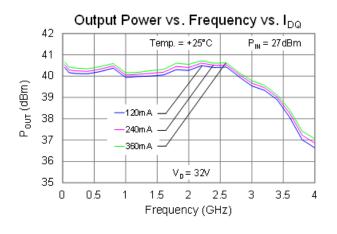

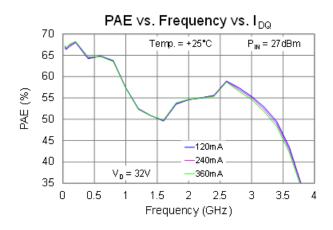

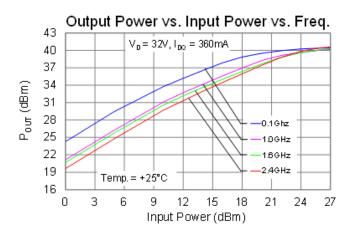

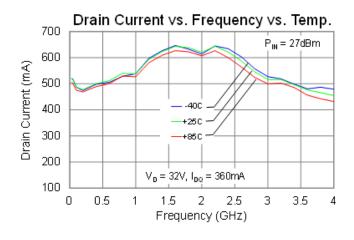

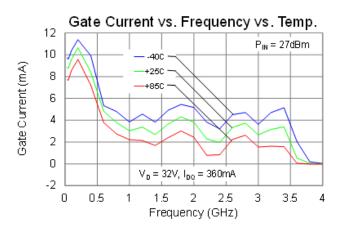

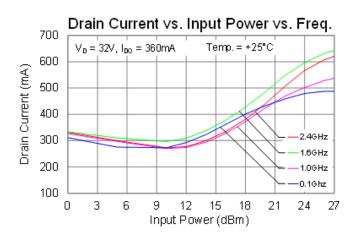

### **Typical Performance: Large Signal (CW)**

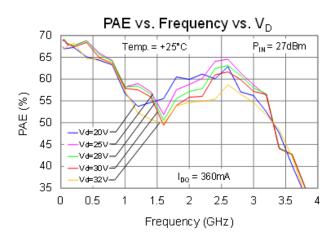

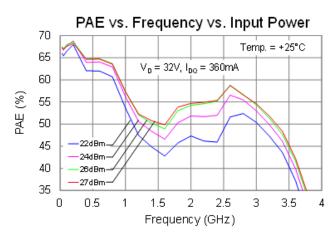

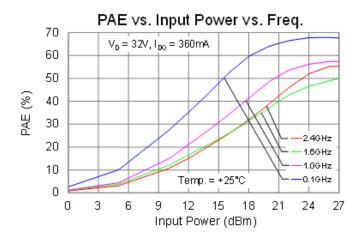

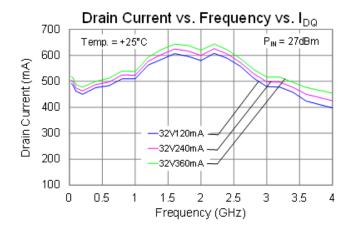

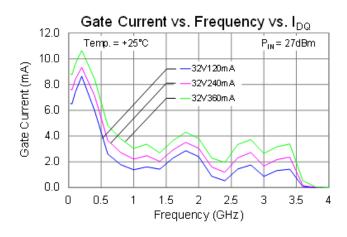

### **Typical Performance: Large signal (CW)**

### **Typical Performance: Large signal (CW)**

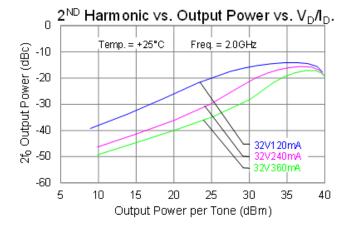

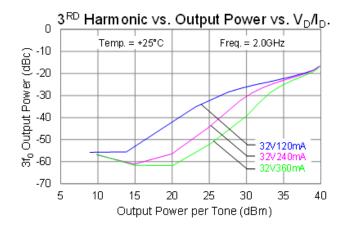

### **Typical Performance: Linearity**

### **Typical Performance: Linearity**

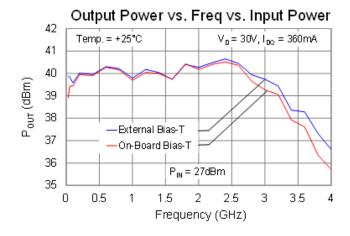

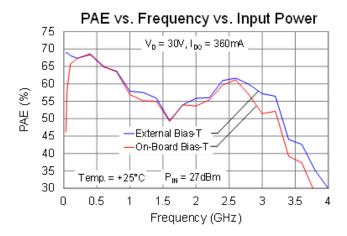

## Typical Performance: Large Signal (CW), On-board vs. External Coaxial Bias-T

The plots below reflect performance measured between external bias tee and on-board bias tee (See application circuit on pages 11 and 13)

## **Thermal and Reliability Information**

| Parameter                                                   | Test Conditions                                                                                                                                                                                                                                      | Value | Units |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|

| Thermal Resistance ( $\theta_{JC}$ ) (1)                    | $T_{\text{base}} = 85  ^{\circ}\text{C},  V_{\text{D}} = 32  \text{V},  I_{\text{DQ}} = 360  \text{mA},  I_{\text{D\_Drive}} = 630  \text{mA},  P_{\text{IN}} = 27  \text{dBm},  P_{\text{OUT}} = 40  \text{dBm},  P_{\text{DISS}} = 630  \text{mA}$ | 6.79  | °C/W  |

| Channel Temperature (T <sub>CH</sub> ) (Under RF drive) (2) | 10 W                                                                                                                                                                                                                                                 | 152.9 | °C    |

#### Notes:

- 1. Thermal resistance measured to back of package.

- 2. Refer to the following document: GaN Device Channel Temperature, Thermal Resistance, and Reliability Estimates

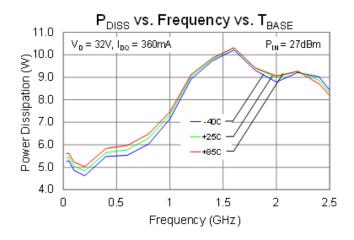

#### **Power Dissipation**

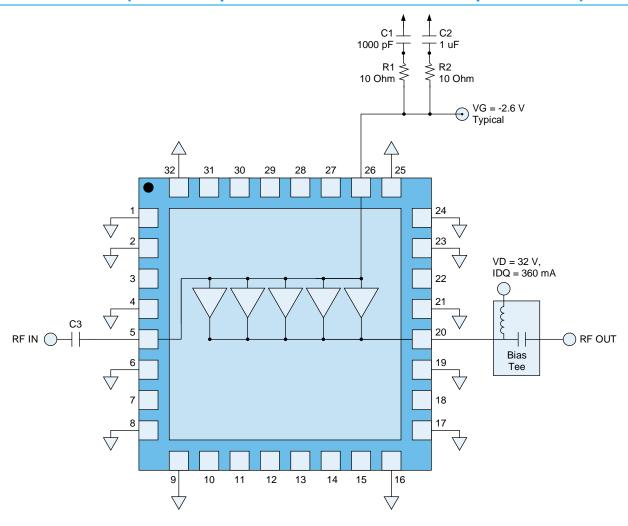

## Application Circuit (Coaxial input DC block and coaxial output bias tee)

#### Notes:

- 1. Coaxial input DC block (C3) is used for input port (RF In.)

- 2. External wide bandwidth Bias-Tee is used for output port (RF Out). V<sub>D</sub> is applied through the output Bias-Tee.

### **Bias-up Procedure**

| 1. Set I <sub>D</sub> limit to 700 mA, I <sub>G</sub> limit to 7 mA                                                       |

|---------------------------------------------------------------------------------------------------------------------------|

| 2. Set V <sub>G</sub> to -5.0 V                                                                                           |

| 3. Set V <sub>D</sub> +32 V                                                                                               |

| <ol> <li>Adjust V<sub>G</sub> more positive until I<sub>DQ</sub> = 360 mA<br/>(V<sub>G</sub> ~ -2.6 V Typical)</li> </ol> |

| 5. Apply RF signal *                                                                                                      |

#### **Bias-down Procedure**

- 1. Turn off RF signal

- 2. Reduce  $V_G$  to -5.0 V. Ensure  $I_{DQ} \sim 0$  mA

- 3. Set  $V_D$  to 0 V

- 4. Turn off V<sub>D</sub> supply

- 5. Turn off V<sub>G</sub> supply

- (\*) P<sub>IN</sub> is limited to 26 dBm for frequency < 0.6 GHz due to high gate current.

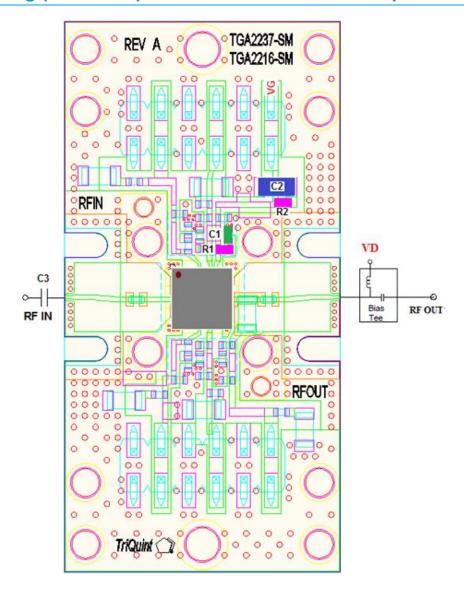

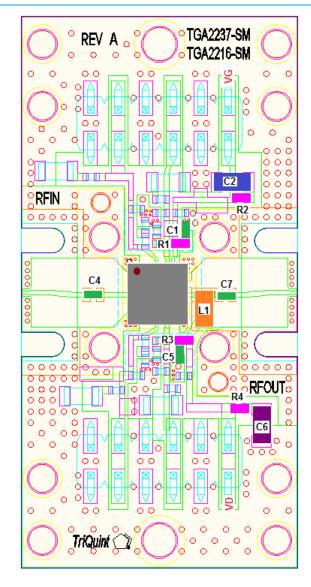

## Assembly Drawing (Coaxial input DC block and coaxial output bias tee)

#### **Bill of Materials**

| Reference Designator | Value   | Description                | Manufacturer | Part Number |

|----------------------|---------|----------------------------|--------------|-------------|

| C1                   | 1000 pF | Cap, 0402, 100 V, 10%, X7R | Various      |             |

| C2                   | 1 uF    | Cap, 1206, 50 V, 10%, X7R  | Various      |             |

| C3                   | 1000 pF | DC Block                   | Various      |             |

| R1 – R2              | 10 Ω    | Res, 0402                  | Various      |             |

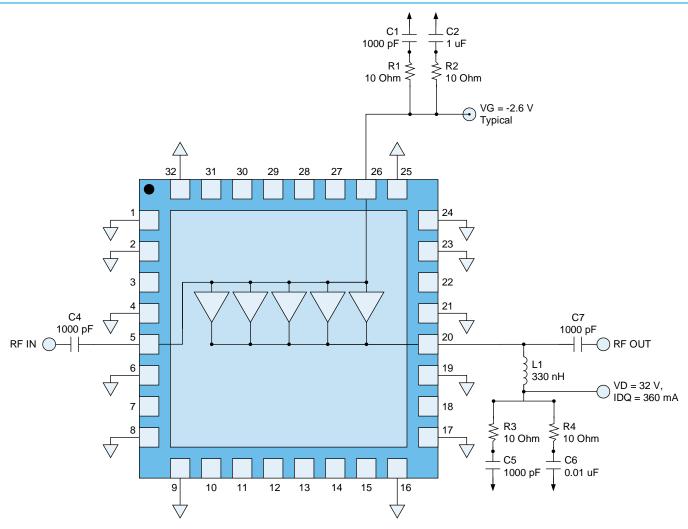

## Application Circuit (Option with board-level DC blocks and output bias tee)

#### Notes:

1. Performance of the DUT with surface mount DC blocks and bias tee components may be degraded relative to the coaxial option. These components should be optimized for the desired operational bandwidth.

## **Evaluation Board Layout with On-Board DC Blocks and Output Bias-T Option**

#### **Bill of Materials For On-Board Bias-Tee**

| Reference Designator | Value   | Description                | Manufacturer | Part Number |

|----------------------|---------|----------------------------|--------------|-------------|

| C1, C4, C5, C7       | 1000 pF | Cap, 0402, 100 V, 10%, X7R | Various      |             |

| C2                   | 1 uF    | Cap, 1206, 50 V, 10%, X7R  | Various      |             |

| C6                   | 0.01 uF | Cap, 1206, 100 V, 10%, X7R | Various      |             |

| L1                   | 330 nH  | Ind, 1206, 100 V, 10%, X7R | Various      |             |

| R1 – R4              | 10 Ω    | Res, 0402                  | Various      |             |

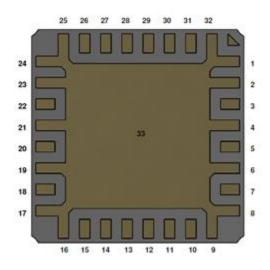

## **Pin Layout**

### **Pin Description**

| Pin No.                                  | Symbol        | Description                                                                                    |

|------------------------------------------|---------------|------------------------------------------------------------------------------------------------|

| 1-2, 4, 6, 8-9, 16-17, 19, 21, 23-25, 32 | GND           | Connected to ground paddle (pin 33); must be grounded on PCB.                                  |

| 3, 7, 10-15, 18, 22, 27-31               | NC            | No connection.                                                                                 |

| 5                                        | RF IN         | Input; matched to 50 Ω.                                                                        |

| 20                                       | RF OUT/ DRAIN | Output; matched to 50 Ω.                                                                       |

| 26                                       | GATE          | GATE voltage; bias network is required; see recommended Application Information on page 11.    |

| 33                                       | GND           | Ground Paddle. Multiple vias should be employed to minimize inductance and thermal resistance. |

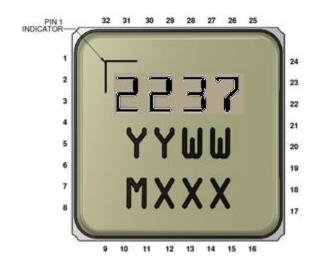

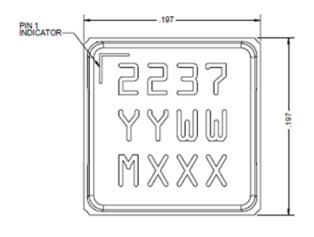

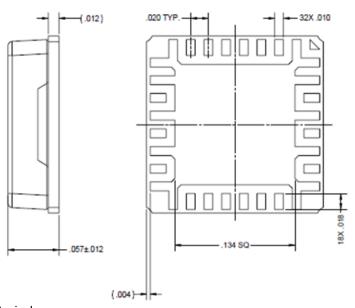

#### **Mechanical Information**

Units: inches

Tolerances: unless specified  $x.xx = \pm 0.01$

$x.xxx = \pm 0.005$ Materials:

Base: Ceramic Lid: Plastic

All metalized features are gold plated

Part is epoxy sealed

Marking:

2237: Part number YY: Part Assembly year WW: Part Assembly week MXXX: Batch ID

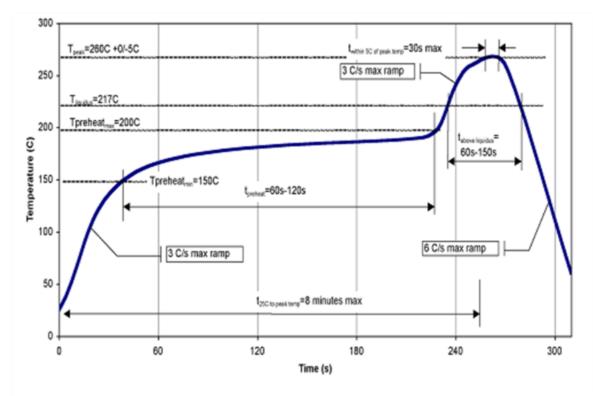

### **Assembly Notes**

Compatible with lead-free soldering processes with 260°C peak reflow temperature.

This package is air-cavity and non-hermetic, and therefore cannot be subjected to aqueous washing. The use of no-clean solder to avoid washing after soldering is highly recommended.

Contact plating: Ni-Au.

Solder rework not recommended.

Recommended Soldering Temperature Profile