# 1. General description

The TJA1081B is a FlexRay node transceiver that is fully compliant with the FlexRay electrical physical layer specification V3.0.1 (see <u>Ref. 1</u>). In order to meet the JASPAR-specific requirements, it implements the 'Bus driver increased voltage amplitude transmitter' functional class. It is primarily intended for communication systems from 2.5 Mbit/s to 10 Mbit/s and provides an advanced interface between the protocol controller and the physical bus in a FlexRay network.

The TJA1081B features enhanced low-power modes, optimized for ECUs that are permanently connected to the battery.

The TJA1081B provides differential transmit capability to the network and differential receive capability to the FlexRay controller. It offers excellent EMC performance as well as effective ESD protection.

The TJA1081B actively monitors system performance using dedicated error and status information (that can be read by any microcontroller), along with internal voltage and temperature monitoring.

The TJA1081B supports mode control as used in the TJA1080A (see <u>Ref. 3</u>) and is fully function and footprint compatible with the TJA1081 (see <u>Ref. 2</u>).

# 2. Features and benefits

### 2.1 Optimized for time triggered communication systems

- Compliant with FlexRay electrical physical layer specification V3.0.1 (see <u>Ref. 1</u>)

- Meets JASPAR requirements as described in the 'Bus driver increased voltage amplitude transmitter' functional class

- Automotive product qualification in accordance with AEC-Q100

- Data transfer rates from 2.5 Mbit/s to 10 Mbit/s

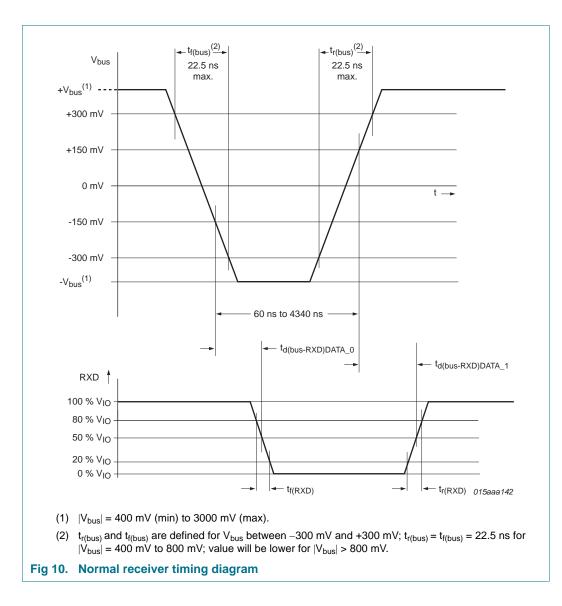

- Supports 60 ns minimum bit time at 400 mV differential input voltage

- Very low ElectroMagnetic Emissions (EME) to support unshielded cable, meeting latest industry standards

- Differential receiver with wide common-mode range for high ElectroMagnetic Immunity (EMI), meeting latest industry standards

- Auto I/O level adaptation to host controller supply voltage VIO

- Can be used in 14 V, 24 V and 48 V powered systems

- Instant transmitter shut-down interface (via BGE pin)

- Independent power supply ramp-up for V<sub>BAT</sub>, V<sub>CC</sub> and V<sub>IO</sub>

#### FlexRay node transceiver

#### 2.2 Low-power management

- Low-power management including inhibit switch

- Very low current in Sleep and Standby modes

- V<sub>BAT</sub> operating range: 4.75 V to 60 V

- Gap-free specification

- Local and remote wake-up

- Supports remote wake-up via dedicated data frames

- Wake-up source recognition

#### 2.3 Diagnosis (detection and signaling)

- Enhanced supply monitoring of V<sub>BAT</sub>, V<sub>CC</sub> and V<sub>IO</sub>

- Overtemperature detection

- Short-circuit detection on bus lines

- V<sub>BAT</sub> power-on flag (first battery connection and cold start)

- Clamping diagnosis on pin TXEN

- BGE status feedback

#### 2.4 Protection

- Bus pins protected against ±6 kV ESD pulses according to IEC61000-4-2 and HBM

- Pins V<sub>BAT</sub> and WAKE protected against ±6 kV ESD pulses according to IEC61000-4-2

- Bus pins protected against transients in automotive environment (according to ISO 7637 class C)

- Bus pins short-circuit proof to battery voltage (14 V, 24 V and 48 V) and ground

- Fail-silent behavior in the event of an undervoltage on pins V<sub>BAT</sub>, V<sub>CC</sub> or V<sub>IO</sub>

- Passive behavior of bus lines while the transceiver is not powered

- No reverse currents from the digital input pins to V<sub>IO</sub> or V<sub>CC</sub> when the transceiver is not powered

# 2.5 Functional classes according to FlexRay electrical physical layer specification (see <u>Ref. 1</u>)

- Bus driver voltage regulator control

- Bus driver bus guardian interface

- Bus driver logic level adaptation

- Bus driver remote wake-up

- Bus driver increased voltage amplitude transmitter (JASPAR)

# 3. Ordering information

#### Table 1.Ordering information

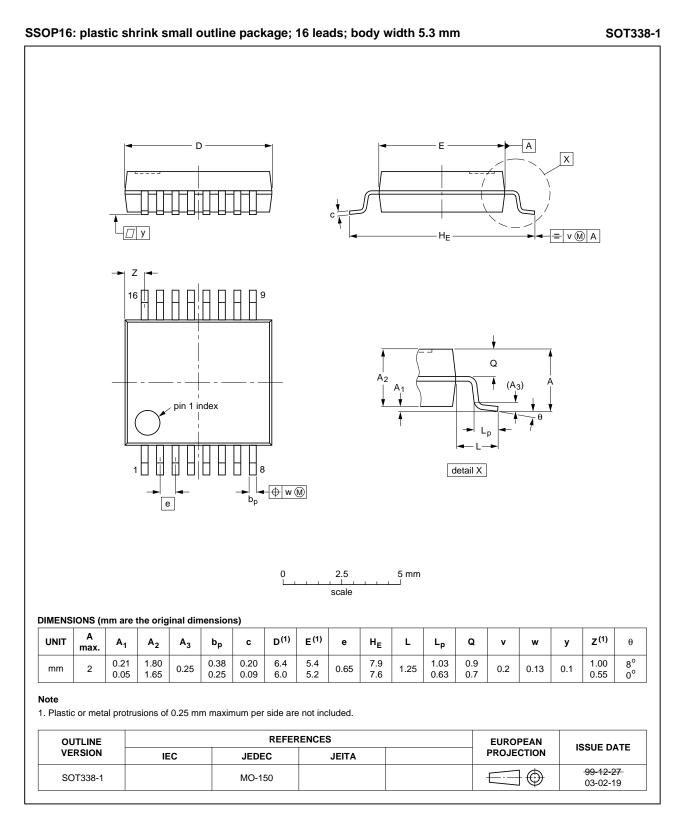

| Type number | Package |                                                                           |          |

|-------------|---------|---------------------------------------------------------------------------|----------|

|             | Name    | Description                                                               | Version  |

| TJA1081BTS  | SSOP16  | SSOP16: plastic shrink small outline package; 16 leads; body width 5.3 mm | SOT338-1 |

FlexRay node transceiver

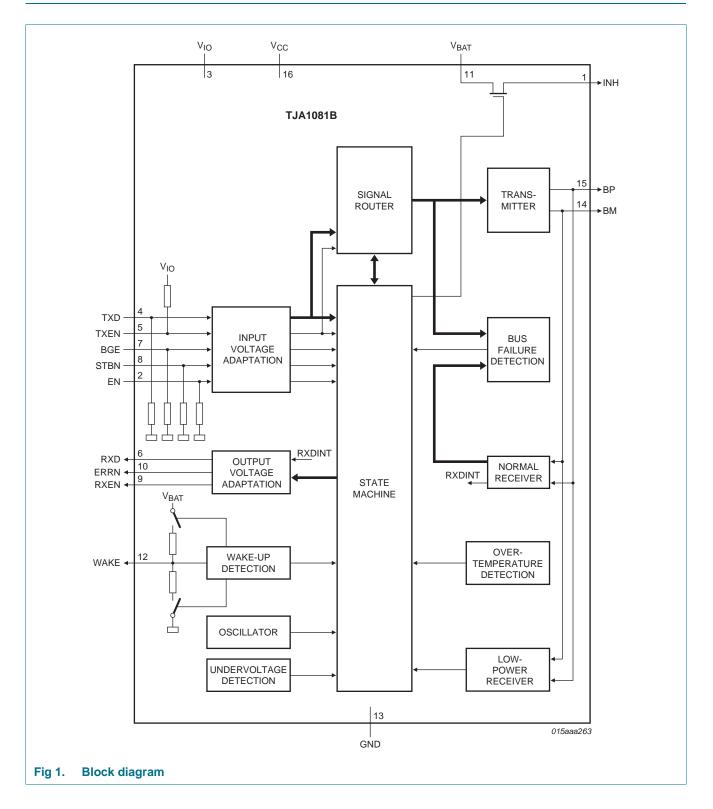

# 4. Block diagram

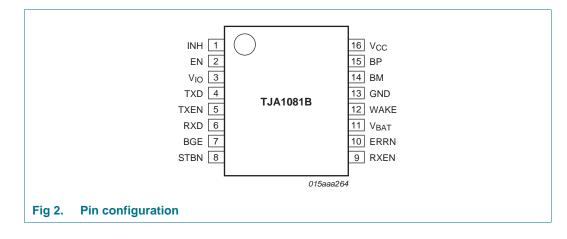

# 5. Pinning information

## 5.1 Pinning

# 5.2 Pin description

#### Table 2.Pin description

| Table 2.        | Fill des | scription |                                                                                     |

|-----------------|----------|-----------|-------------------------------------------------------------------------------------|

| Symbol          | Pin      | Туре      | Description                                                                         |

| INH             | 1        | 0         | inhibit output for switching external voltage regulator                             |

| EN              | 2        | I         | enable input; enabled when HIGH; internal pull-down                                 |

| V <sub>IO</sub> | 3        | Р         | supply voltage for $V_{\text{IO}}$ voltage level adaptation                         |

| TXD             | 4        | I         | transmit data input; internal pull-down                                             |

| TXEN            | 5        | I         | transmitter enable input; when HIGH transmitter disabled; internal pull-up          |

| RXD             | 6        | 0         | receive data output                                                                 |

| BGE             | 7        | I         | bus guardian enable input; when LOW transmitter disabled; internal pull-down        |

| STBN            | 8        | I         | standby input; low-power mode when LOW; internal pull-down                          |

| RXEN            | 9        | 0         | receive data enable output; when LOW bus activity detected                          |

| ERRN            | 10       | 0         | error diagnoses output; when LOW error detected                                     |

| $V_{BAT}$       | 11       | Р         | battery supply voltage                                                              |

| WAKE            | 12       | I         | local wake-up input; internal pull-up or pull-down (depends on voltage at pin WAKE) |

| GND             | 13       | Р         | ground                                                                              |

| BM              | 14       | I/O       | bus line minus                                                                      |

| BP              | 15       | I/O       | bus line plus                                                                       |

| V <sub>CC</sub> | 16       | Р         | supply voltage (+5 V)                                                               |

|                 |          |           |                                                                                     |

# 6. Functional description

The block diagram of the transceiver is shown in Figure 1.

## 6.1 Operating modes

The TJA1081B supports the following operating modes:

- Normal (normal-power mode)

- Receive-only (normal-power mode)

- Standby (low-power mode)

- Go-to-sleep (low-power mode)

- Sleep (low-power mode)

- PowerOff

### 6.1.1 Bus activity and idle detection

The following mechanisms for activity and idle detection are valid in normal-power modes:

- If the absolute differential voltage on the bus lines is higher than |V<sub>i(dif)det(act)</sub>| for t<sub>det(act)(bus)</sub>, activity is detected on the bus lines; pin RXEN is switched LOW, releasing pin RXD:

- if, after activity has been detected on the bus, the differential voltage on the bus lines is lower than V<sub>IL(dif)</sub>, pin RXD will go LOW

- if, after activity has been detected on the bus, the differential voltage on the bus lines is higher than  $V_{IH(dif)}$ , pin RXD will go HIGH

- If the absolute differential voltage on the bus lines is lower than  $|V_{i(dif)det(act)}|$  for  $t_{det(idle)(bus)}$ , idle is detected on the bus lines; pin RXEN is switched HIGH, blocking pin RXD (pin RXD is switched HIGH or remains HIGH)

### 6.1.2 Signaling on pin ERRN

Pin ERRN provides either error information or wake-up information. The behavior of ERRN is determined by the host (via pins STBN and EN) and not by the operating mode.

If STBN is LOW, pin ERRN is configured to signal a wake-up event; when STBN and EN are both HIGH, pin ERRN is configured to provide an error alert. Signaling on pin ERRN is described in <u>Table 3</u>.

If pin ERRN goes LOW in Standby or Sleep mode to signal a wake-up event, the host can switch the TJA1081B to Receive only mode (STBN  $\rightarrow$  H) to determine if the wake-up is local or remote. A LOW level on ERRN in Receive only mode (provided the transition to Receive only mode was not triggered by EN going LOW) indicates a remote wake-up was detected; a HIGH signals a local wake-up.

If EN was forced HIGH (to switch the TJA1081B to Normal mode) after an earlier wake-up event, then ERRN will always indicate the error detection status (in both Normal and Receive only modes).

| STBN   | EN        | Conditions                                                                                                                                | ERRN |

|--------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|------|

|        |           |                                                                                                                                           | ENNN |

| Norma  | I mode a  | ctive                                                                                                                                     |      |

| Н      | Н         | no error detected                                                                                                                         | HIGH |

| Н      | Н         | error detected                                                                                                                            | LOW  |

| Receiv | e only m  | ode active                                                                                                                                |      |

| Η      | L         | a wake-up was detected (ERRN went LOW in Standby/Sleep<br>mode; EN was not HIGH) before the TJA1081B was switched<br>to Receive only mode |      |

|        |           | local wake-up detected                                                                                                                    | HIGH |

|        |           | remote wake-up detected                                                                                                                   | LOW  |

| Н      | L         | EN was forced HIGH previously in response to an earlier wake-up event before the transition to Receive only mode                          |      |

|        |           | no error detected                                                                                                                         | HIGH |

|        |           | error detected                                                                                                                            | LOW  |

| Standb | y or Slee | p modes active                                                                                                                            |      |

| L      | Х         | no local or remote wake-up detected                                                                                                       | HIGH |

| L      | Х         | local or remote wake-up detected                                                                                                          | LOW  |

Table 3. Signaling on pin ERRN

ERRN is in a high-impedance state in PowerOff mode.

## 6.1.3 Signaling on pins RXEN and RXD

Signaling on pins RXEN and RXD is determined by the TJA1081B operating mode, as detailed in <u>Table 4</u>.

| Table 4. | RXEN and RXD signaling |  |

|----------|------------------------|--|

|----------|------------------------|--|

| Operating mode | RXEN                            |                                     | RXD                                                | Тх                                     | INH      |          |

|----------------|---------------------------------|-------------------------------------|----------------------------------------------------|----------------------------------------|----------|----------|

|                | LOW                             | HIGH                                | LOW                                                | HIGH                                   |          |          |

| Normal         | bus active                      | bus idle                            | DATA_0                                             | DATA_1 or idle                         | enabled  | HIGH     |

| Receive-only   |                                 |                                     |                                                    |                                        | disabled |          |

| Go-to-Sleep    | local or remote                 | no local or remote wake-up detected | local or remote<br>wake-up detected <sup>[1]</sup> | no local or remote<br>wake-up detected |          |          |

| Standby        | wake-up detected <sup>[1]</sup> |                                     |                                                    |                                        |          |          |

| Sleep          |                                 |                                     |                                                    |                                        |          | floating |

| PowerOff       | high impedance                  |                                     | HIGH                                               |                                        |          |          |

[1] Valid if  $V_{IO}$  and  $(V_{CC} \text{ or } V_{BAT})$  are present.

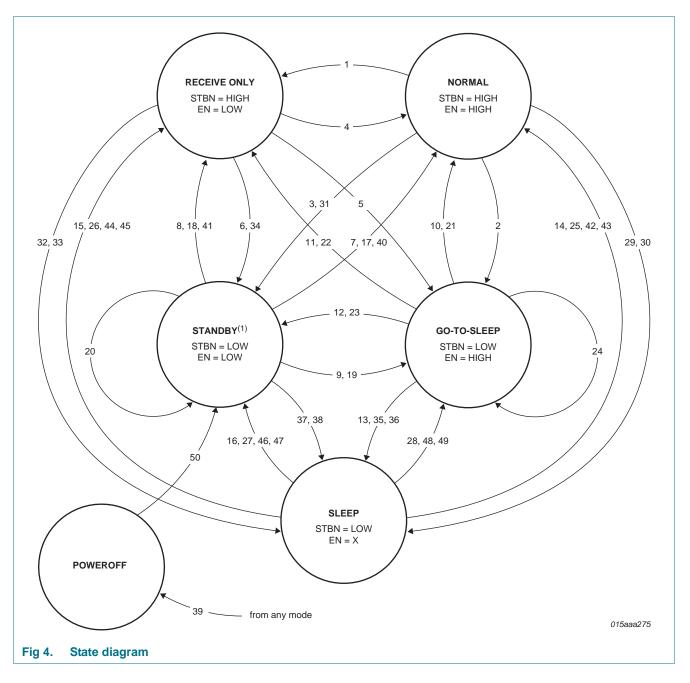

#### 6.1.4 Operating mode transitions

State transitions are summarized in the state transition diagram in Figure 4 and detailed in Table 5 to Table 8. Numbers are used to represent the state transitions. The numbers in the diagram correspond to the numbers in the third column in the tables.

8 of 45

#### TJA1081B Table 5. State transitions forced by EN and STBN

$\rightarrow$  indicates the action that initiates a transaction; 1 $\rightarrow$  and 2 $\rightarrow$  indicated the consequences of a transaction.

| Transition   | Direction to | Transition | Pin             |                 | Flag              |                    |                   |         |         | Notes |

|--------------|--------------|------------|-----------------|-----------------|-------------------|--------------------|-------------------|---------|---------|-------|

| from mode    | mode         | number     | STBN            | EN              | UV <sub>VIO</sub> | UV <sub>VBAT</sub> | UV <sub>VCC</sub> | PWON    | Wake    |       |

| Normal       | Receive-only | 1          | Н               | $\rightarrow$ L | cleared           | cleared            | cleared           | cleared | Х       |       |

|              | Go-to-sleep  | 2          | $\rightarrow$ L | Н               | cleared           | cleared            | cleared           | cleared | Х       |       |

|              | Standby      | 3          | $\rightarrow$ L | $\rightarrow$ L | cleared           | cleared            | cleared           | cleared | Х       |       |

| Receive-only | Normal       | 4          | Н               | $\rightarrow$ H | cleared           | cleared            | cleared           | Х       | Х       |       |

|              | Go-to-sleep  | 5          | $\rightarrow$ L | $\rightarrow$ H | cleared           | cleared            | cleared           | Х       | Х       |       |

| Stand        | Standby      | 6          | $\rightarrow$ L | L               | cleared           | cleared            | cleared           | Х       | Х       |       |

| Standby      | Normal       | 7          | $\rightarrow$ H | $\rightarrow$ H | cleared           | cleared            | cleared           | Х       | Х       |       |

|              | Receive-only | 8          | $\rightarrow$ H | L               | cleared           | cleared            | cleared           | Х       | Х       |       |

|              | Go-to-sleep  | 9          | L               | $\rightarrow$ H | cleared           | cleared            | Х                 | Х       | Х       |       |

| Go-to-sleep  | Normal       | 10         | $\rightarrow$ H | Н               | cleared           | cleared            | cleared           | Х       | Х       |       |

|              | Receive-only | 11         | $\rightarrow$ H | $\rightarrow$ L | cleared           | cleared            | cleared           | Х       | Х       |       |

|              | Standby      | 12         | L               | $\rightarrow$ L | cleared           | cleared            | Х                 | Х       | Х       |       |

| Sleep        | Sleep        | 13         | L               | Н               | cleared           | cleared            | Х                 | Х       | cleared |       |

| Sleep        | Normal       | 14         | $\rightarrow$ H | Н               | cleared           | cleared            | cleared           | Х       | Х       |       |

|              | Receive-only | 15         | $\rightarrow$ H | L               | cleared           | cleared            | cleared           | Х       | Х       |       |

|              | Standby      | 16         | $\rightarrow$ H | Х               | cleared           | cleared            | Х                 | Х       | Х       | ļ     |

[2] Hold time of go-to-sleep becomes greater than  $t_{h(gotosleep)}$ .

[3] Transition to a non-low-power mode is blocked when the voltage on pin V<sub>CC</sub> is below V<sub>uvd(VCC)</sub> for longer than t<sub>det(uv)(VCC)</sub>.

men

© NXP B.V. 2012. All rights reserved. 9 of 45

# TJA1081E

Table 6.State transitions forced by a wake-up $\rightarrow$  indicates the action that initiates a transaction; 1 $\rightarrow$  and 2  $\rightarrow$  indicated the consequences of a transaction.

| Transition  | <b>Direction to</b> | Transition | Pin  |    | Flag                    |                         |                         |      |                   | Note       |

|-------------|---------------------|------------|------|----|-------------------------|-------------------------|-------------------------|------|-------------------|------------|

| from mode   | mode                | number     | STBN | EN | UV <sub>VIO</sub>       | UV <sub>VBAT</sub>      | UV <sub>VCC</sub>       | PWON | Wake              |            |

| Standby     | Normal              | 17         | Н    | Н  | cleared                 | cleared                 | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set |            |

|             | Receive-only        | 18         | Н    | L  | cleared                 | cleared                 | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set |            |

|             | Go-to-sleep         | 19         | L    | Н  | cleared                 | cleared                 | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set | <u> </u>   |

|             | Standby             | 20         | L    | L  | cleared                 | cleared                 | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set |            |

| Go-to-sleep | Normal              | 21         | Н    | Н  | cleared                 | cleared                 | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set |            |

|             | Receive-only        | 22         | Н    | L  | cleared                 | cleared                 | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set |            |

|             | Standby             | 23         | L    | L  | cleared                 | cleared                 | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set |            |

|             | Go-to-sleep         | 24         | L    | Н  | cleared                 | cleared                 | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set | <u> </u>   |

| Sleep       | Normal              | 25         | Н    | Н  | $1 \rightarrow cleared$ | $1 \rightarrow cleared$ | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set | [1]        |

|             | Receive-only        | 26         | Н    | L  | $1 \rightarrow cleared$ | $1 \rightarrow cleared$ | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set | <u>[1]</u> |

|             | Standby             | 27         | L    | L  | $1 \rightarrow cleared$ | $1 \rightarrow cleared$ | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set |            |

|             | Go-to-sleep         | 28         | L    | Н  | $1 \rightarrow cleared$ | $1 \rightarrow cleared$ | $1 \rightarrow cleared$ | Х    | $\rightarrow$ set | [1]        |

[1] Setting the wake flag clears the  $UV_{VIO},\,UV_{VBAT}$  and  $UV_{VCC}$  flags.

[2] Transition via Standby mode.

document is subject to legal disclaim 4 June 2012

Rev. 1

Product data sheet

#### TJA1081 Table 7. State transitions forced by an undervoltage condition

$\rightarrow$  indicates the action that initiates a transaction; 1 $\rightarrow$  and 2 $\rightarrow$  indicated the consequences of a transaction.

| Transition from | Direction to | Transition | Flag              |                    |                   |         |                         | Note         |

|-----------------|--------------|------------|-------------------|--------------------|-------------------|---------|-------------------------|--------------|

| mode            | mode         | number     | UV <sub>VIO</sub> | UV <sub>VBAT</sub> | UVvcc             | PWON    | Wake                    |              |

| Normal          | Sleep        | 29         | $\rightarrow$ set | cleared            | cleared           | cleared | $1 \rightarrow cleared$ | Ī            |

|                 | Sleep        | 30         | cleared           | $\rightarrow$ set  | cleared           | cleared | $1 \rightarrow cleared$ | [            |

|                 | Standby      | 31         | cleared           | cleared            | $\rightarrow$ set | cleared | $1 \rightarrow cleared$ | <u>[1]</u> [ |

| Receive-only    | Sleep        | 32         | $\rightarrow$ set | cleared            | cleared           | Х       | $1 \rightarrow cleared$ |              |

|                 | Sleep        | 33         | cleared           | $\rightarrow$ set  | cleared           | Х       | $1 \rightarrow cleared$ |              |

|                 | Standby      | 34         | cleared           | cleared            | $\rightarrow$ set | Х       | $1 \rightarrow cleared$ | <u>[1]</u>   |

| Go-to-sleep     | Sleep        | 35         | $\rightarrow$ set | cleared            | cleared           | Х       | $1 \rightarrow cleared$ |              |

|                 | Sleep        | 36         | cleared           | $\rightarrow$ set  | cleared           | Х       | $1 \rightarrow cleared$ |              |

| Standby         | Sleep        | 37         | $\rightarrow$ set | cleared            | Х                 | Х       | $1 \rightarrow cleared$ | [1]          |

|                 | Sleep        | 38         | cleared           | $\rightarrow$ set  | Х                 | Х       | $1 \rightarrow cleared$ | <u>[1]</u>   |

| Х               | PowerOff     | 39         | Х                 | Х                  | Х                 | Х       | Х                       |              |

Rev. ed in this docun -4 June 2012 lent is

subjec

t to legal discla

Product data sheet

[1]  $UV_{VIO}$ ,  $UV_{VBAT}$  or  $UV_{VCC}$  detected clears the wake flag.

[2] Transition already completed when the voltage on pin V<sub>CC</sub> is below V<sub>uvd(VCC)</sub> for longer than t<sub>det(uv)(VCC)</sub>.

[3]  $UV_{VIO}$  overrules  $UV_{VCC}$ .

[4] UV<sub>VBAT</sub> overrules UV<sub>VCC</sub>.

[5]  $V_{DIG}$  (the internal digital supply voltage to the state machine) <  $V_{th(det)POR}$ .

© NXP B.V. 2012. All rights reserved. 11 of 45

#### TJA1081 Table 8. State transitions forced by an undervoltage recovery

$\rightarrow$  indicates the action that initiates a transaction;  $\rightarrow$ 1 and  $\rightarrow$ 2 are the consequences of a transaction.

| Transition | <b>Direction to</b> | Transition | Pin  |    | Flag                  |                       |                       |                   |      | Note |

|------------|---------------------|------------|------|----|-----------------------|-----------------------|-----------------------|-------------------|------|------|

| from mode  | mode                | number     | STBN | EN | UV <sub>VIO</sub>     | UV <sub>VBAT</sub>    | UV <sub>VCC</sub>     | PWON              | Wake |      |

| Standby    | Normal              | 40         | Н    | Н  | cleared               | cleared               | $\rightarrow$ cleared | Х                 | Х    |      |

|            | Receive-only        | 41         | Н    | L  | cleared               | cleared               | $\rightarrow$ cleared | Х                 | Х    |      |

| Sleep      | Normal              | 42         | Н    | Н  | cleared               | $\rightarrow$ cleared | cleared               | Х                 | Х    |      |

|            | Normal              | 43         | Н    | Н  | $\rightarrow$ cleared | cleared               | cleared               | Х                 | Х    |      |

|            | Receive-only        | 44         | Н    | L  | cleared               | $\rightarrow$ cleared | cleared               | Х                 | Х    |      |

|            | Receive-only        | 45         | Н    | L  | $\rightarrow$ cleared | cleared               | cleared               | Х                 | Х    |      |

|            | Standby             | 46         | L    | L  | cleared               | $\rightarrow$ cleared | cleared               | Х                 | Х    |      |

|            | Standby             | 47         | L    | L  | $\rightarrow$ cleared | cleared               | cleared               | Х                 | Х    |      |

|            | Go-to-sleep         | 48         | L    | Н  | cleared               | $\rightarrow$ cleared | cleared               | Х                 | Х    |      |

|            | Go-to-sleep         | 49         | L    | Н  | $\rightarrow$ cleared | cleared               | cleared               | Х                 | Х    |      |

| PowerOff   | Standby             | 50         | Х    | Х  | Х                     | Х                     | Х                     | $\rightarrow$ set | Х    |      |

[1] Transition already completed when the voltage on pin V<sub>CC</sub> is above V<sub>uvr(VCC)</sub> for longer than t<sub>rec(uv)(VCC)</sub>.

The voltage on pin VBAT is above Vuvr(VBAT) for longer than trec(uv)(VBAT) AND VDIG (the internal digital supply voltage to the state machine) > Vth(rec)POR.

4 June 2012

Rev. in this document is subject to legal disclaimer -

[2]

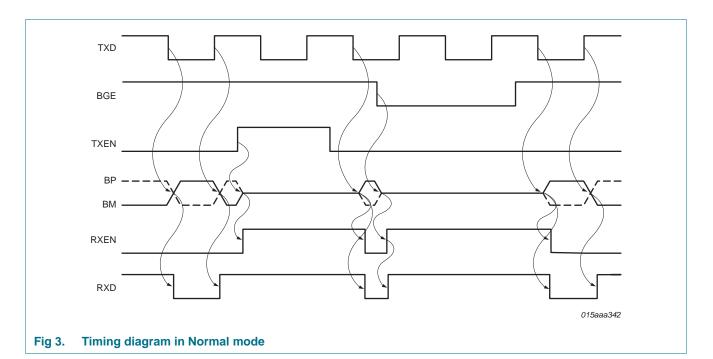

#### 6.1.5 Normal mode

In Normal mode, the transceiver is able to transmit and receive data via bus lines BP and BM. The output of the normal receiver is connected directly to pin RXD.

Transmitter behavior in Normal mode, with no TXEN time-out (see <u>Section 6.4.7</u>) and the temperature flag not set (TEMP HIGH = 0; see <u>Table 10</u>), is detailed in <u>Table 9</u>.

In this mode, pin INH is set HIGH.

| Table 9. | Trans | smitter f | unction table                                                                                     |

|----------|-------|-----------|---------------------------------------------------------------------------------------------------|

| BGE      | TXEN  | TXD       | Transmitter                                                                                       |

| L        | Х     | Х         | transmitter is disabled                                                                           |

| Х        | Н     | Х         | transmitter is disabled                                                                           |

| Н        | L     | Н         | transmitter is enabled; the bus lines are actively driven; BP is driven HIGH and BM is driven LOW |

| Η        | L     | L         | transmitter is enabled; the bus lines are actively driven; BP is driven LOW and BM is driven HIGH |

The transmitter is activated by the first LOW level detected on pin TXD when pin BGE HIGH and pin TXEN is LOW.

#### 6.1.6 Receive-only mode

In Receive-only mode, the transceiver can only receive data. The transmitter is disabled, regardless of the voltage levels on pins BGE and TXEN.

In this mode, pin INH is set HIGH.

#### 6.1.7 Standby mode

Standby mode is a low-power mode featuring very low current consumption. In this mode, the transceiver cannot transmit or receive data. The low-power receiver is activated to monitor the bus for wake-up patterns.

A transition to Standby mode can be triggered by applying the appropriate levels on pins EN and STBN (see Figure 4 and Table 5) or if an undervoltage is detected on pin  $V_{CC}$  (see Figure 4 and Section 6.1.9).

In this mode, pin INH is set HIGH.

If the wake flag is set, pins RXEN and RXD are driven LOW; otherwise pins RXEN and RXD are set HIGH (see <u>Section 6.2</u>).

#### 6.1.8 Go-to-sleep mode

In this mode, the transceiver behaves as in Standby mode. If Go-to-sleep mode remains active longer than the go-to-sleep hold time ( $t_{h(gotosleep)}$ ) and the wake flag has been cleared previously, the transceiver switches to Sleep mode regardless of the voltage on pin EN.

#### 6.1.9 Sleep mode

Sleep mode is a low-power mode. The only difference between Sleep mode and Standby mode is that pin INH is set floating in Sleep mode. A transition to Sleep mode is triggered from all other modes when the  $UV_{VIO}$  flag or the  $UV_{VBAT}$  flag is set (see <u>Table 7</u>).

TJA1081B Product data sheet When the wake flag is set, the undervoltage flags are reset and the transceiver switches from Sleep mode to the mode indicated by the levels on pins EN and STBN (see <u>Table 7</u>), provided  $V_{IO}$  is valid.

#### 6.2 Wake-up mechanism

From Sleep mode (pin INH floating), the transceiver enters Standby mode if the wake flag is set. Consequently, pin INH is switched on (HIGH).

If an undervoltage is not detected on pins  $V_{IO}$ ,  $V_{CC}$  or  $V_{BAT}$ , the transceiver switches immediately to the mode indicated by the levels on pins EN and STBN.

In Standby, Go-to-sleep and Sleep modes, pins RXD, RXEN and ERRN are driven LOW if the wake flag is set.

#### 6.2.1 Remote wake-up

#### 6.2.1.1 Bus wake-up via wake-up pattern

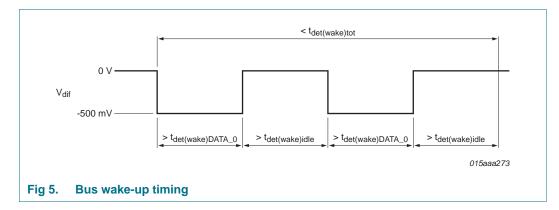

A valid wake-up pattern on the bus triggers a remote wake-up. A valid remote wake-up pattern consists of a DATA\_0, DATA\_1 or idle, DATA\_0, DATA\_1 or idle sequence. The DATA\_0 phases must last at least  $t_{det(wake)DATA_0}$  and the DATA\_1 or idle phases at least  $t_{det(wake)idle}$ . The entire sequence must be completed within  $t_{det(wake)iot}$ .

#### 6.2.1.2 Bus wake-up via dedicated FlexRay data frame

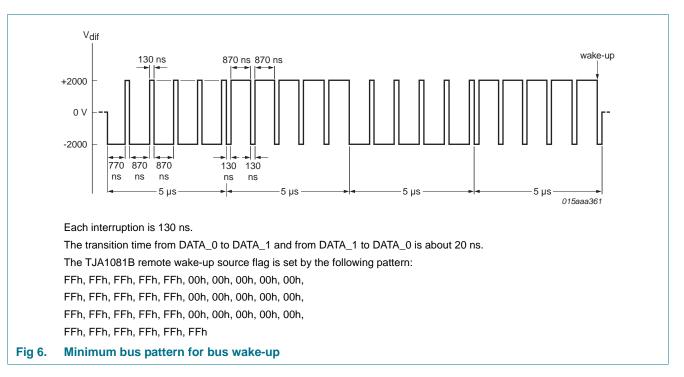

If the TJA1081B receives a dedicated data frame that emulates a valid wake-up pattern as detailed Figure 6, the remote wake-up source flag is set.

Due to the Byte Start Sequence (BSS) preceding each byte, the DATA\_0 and DATA\_1 phases for the wake-up symbol are interrupted every 1  $\mu$ s. For 10 Mbit/s the maximum interruption time is 130 ns. Such interruptions do not prevent the transceiver from recognizing the wake-up pattern in the payload of a data frame.

The remote wake-up source flag is not set if an invalid wake-up pattern is received.

### **NXP Semiconductors**

#### 6.2.2 Local wake-up via pin WAKE

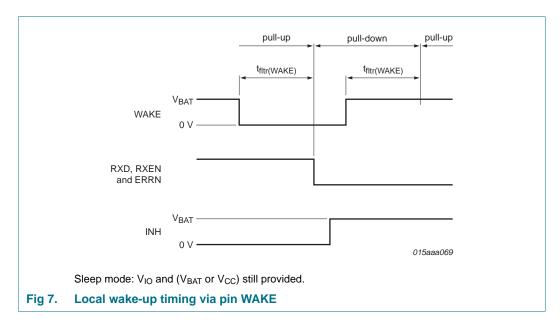

If the voltage on pin WAKE is lower than  $V_{th(det)(WAKE)}$  for longer than  $t_{fltr(WAKE)}$  (falling edge on pin WAKE) a local wake-up event on pin WAKE is detected. At the same time, the biasing of this pin is switched to pull-down.

If the voltage on pin WAKE is higher than  $V_{th(det)(WAKE)}$  for longer than  $t_{fltr(WAKE)}$ , the biasing of this pin is switched to pull-up, and a local wake-up is not detected.

**TJA1081B**

FlexRay node transceiver

#### 6.3 Fail-silent behavior

To ensure fail-silent behavior, a reset mechanism for the digital state machine has been implemented along with undervoltage detection.

If an undervoltage is detected on pins  $V_{CC}$ ,  $V_{IO}$  and/or  $V_{BAT}$ , the transceiver switches to a low-power mode. This action ensures that the transmitter and receiver are passive when an undervoltage is detected and that their behavior is defined.

The digital state machine is supplied by  $V_{CC}$ ,  $V_{IO}$  or  $V_{BAT}$ , depending on which voltage is available. Therefore, the digital state machine will be properly supplied as long as the voltage on pin  $V_{CC}$ ,  $V_{IO}$  or  $V_{BAT}$  remains above 4.5 V.

If the voltage on all pins (i.e.  $V_{CC}$ ,  $V_{IO}$  and  $V_{BAT}$ ) breaks down, a reset signal is transmitted to the digital state machine. The reset signal is transmitted as soon as the internal supply voltage to the digital state machine is no longer high enough to guarantee proper operation. This ensures that the digital state machine is passive, and its behavior defined, when an undervoltage is detected.

#### 6.3.1 V<sub>BAT</sub> undervoltage

If the  $UV_{VBAT}$  flag is set, the transceiver enters Sleep mode (pin INH is switched off) regardless of the voltage levels on pins EN and STBN. If the undervoltage recovers, the transceiver switches to the mode determined by the voltages on pins EN and STBN.

#### 6.3.2 V<sub>CC</sub> undervoltage

If the  $UV_{VCC}$  flag is set, the transceiver switches to Standby mode regardless of the voltage levels on pins EN and STBN. If the undervoltage recovers or the wake flag is set, mode switching via pins EN and STBN is again enabled.

#### 6.3.3 V<sub>IO</sub> undervoltage

If the voltage on pin V<sub>IO</sub> is lower than V<sub>uvd(VIO)</sub> for longer than t<sub>det(uv)(VIO)</sub> (even if the UV<sub>VIO</sub> flag is reset) pins EN, STBN, TXD and BGE are set LOW (internally) and pin TXEN is set HIGH (internally). If the UV<sub>VIO</sub> flag is set, the transceiver enters Sleep mode (pin INH is switched off). If the undervoltage recovers or the wake flag is set, mode switching via pins EN and STBN is again enabled.

### 6.4 Flags

#### 6.4.1 Local wake-up source flag

The local wake-up source flag can only be set in a low-power mode. When a wake-up event is detected on pin WAKE (see <u>Section 6.2.2</u>), the local wake-up source flag is set. The local wake-up source flag is reset by entering a low-power mode.

#### 6.4.2 Remote wake-up source flag

The remote wake-up source flag can only be set in a low-power mode if pin  $V_{BAT}$  is within its operating range. When a remote wake-up event is detected on the bus lines (see Section 6.2.1), the remote wake-up source flag is set. The remote wake-up source flag is reset by entering a low-power mode.

#### 6.4.3 Wake flag

The wake flag is set if the local or remote wake-up source flag is set. The wake flag is reset by entering a low-power mode or by setting one of the undervoltage flags.

#### 6.4.4 Power-on flag

If the internal supply voltage to the digital section rises above the minimum operating level, the PWON power-on flag is set. The PWON flag is reset when the TJA1081B enters Normal mode.

#### 6.4.5 Temperature medium flag

If the junction temperature exceeds  $T_{j(warn)(medium)}$  in a normal-power mode, the temperature medium flag is set. The temperature medium flag is reset when the junction temperature drops below  $T_{j(warn)(medium)}$  (in a normal-power mode or after the status register has been read in a low-power mode). No action is taken when this flag is set.

#### 6.4.6 Temperature high flag

If the junction temperature exceeds  $T_{j(dis)(high)}$  in a normal-power mode, the temperature high flag is set. If a negative edge is applied to pin TXEN while the junction temperature is below  $T_{j(dis)(high)}$  in a normal-power mode, the temperature high flag is reset.

The transmitter is disabled when the temperature high flag is set.

#### 6.4.7 TXEN clamped flag

The TXEN clamped flag is set if pin TXEN is LOW for longer than  $t_{detCL(TXEN)}$ . The TXEN clamped flag is reset if pin TXEN is HIGH. If the TXEN clamped flag is set, the transmitter is disabled.

#### 6.4.8 Bus error flag

The bus error flag is set if pin TXEN is LOW, pin BGE is HIGH and the data received on the bus lines (pins BP and BM) is different to that received on pin TXD. The transmission of any valid communication element, including a wake-up pattern, will not be detected as a bus error.

The bus error flag is reset if the data on the bus lines (pins BP and BM) is the same as on pin TXD or if the transmitter is disabled. No action is taken when the bus error flag is set.

#### 6.4.9 UV<sub>VBAT</sub> flag

The UV<sub>VBAT</sub> flag is set if the voltage on pin V<sub>BAT</sub> is lower than V<sub>uvd(VBAT)</sub> for longer than t<sub>det(uv)(VBAT)</sub>. The UV<sub>VBAT</sub> flag is reset if the voltage is higher than V<sub>uvr(VBAT)</sub> for longer than t<sub>to(uvr)(VBAT)</sub> or by setting the wake flag; see <u>Section 6.3.1</u>.

#### 6.4.10 UV<sub>VCC</sub> flag

In a non-low-power mode, the UV<sub>VCC</sub> flag is set if the voltage on pin V<sub>CC</sub> is lower than V<sub>uvd(VCC)</sub> for longer than t<sub>det(uv)(VCC)</sub>. In a low-power mode, the UV<sub>VCC</sub> flag is set if the voltage on pin V<sub>CC</sub> is lower than V<sub>uvd(VCC)</sub> for longer than t<sub>to(uvd)(VCC)</sub>. The UV<sub>VCC</sub> flag is reset if the voltage on pin V<sub>CC</sub> is higher than V<sub>uvr(VCC)</sub> for longer than t<sub>to(uvr)(VCC)</sub> or the wake flag is set; see <u>Section 6.3.2</u>.

11.40

#### 6.4.11 UV<sub>VIO</sub> flag

The UV<sub>VIO</sub> flag is set if the voltage on pin V<sub>IO</sub> is lower than V<sub>uvd(VIO)</sub> for longer than  $t_{to(uvd)(VIO)}$ . The flag is reset if the voltage on pin V<sub>IO</sub> is higher than V<sub>uvr(VIO)</sub> for longer than  $t_{to(uvr)(VIO)}$  or the wake flag is set; see <u>Section 6.3.3</u>.

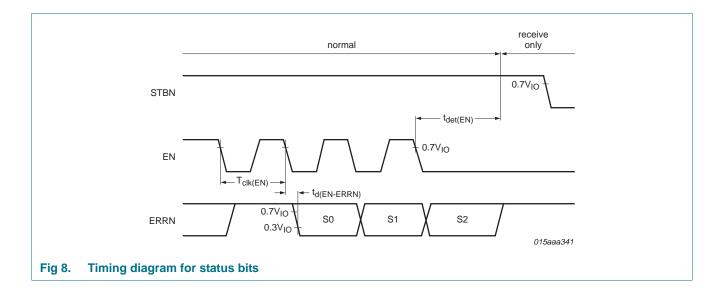

#### 6.5 Status register

Pin ERRN goes LOW when one or more of status bits S4 to S10 is set. The contents of the status register (<u>Table 10</u>) can be read out on pin ERRN using the input signal on pin EN as a clock. The timing diagram is shown in <u>Figure 8</u>.

The status register is accessible if:

- $UV_{VIO}$  flag is not set and the voltage on pin  $V_{IO}$  is between 4.75 V and 5.25 V

- $UV_{VCC}$  flag is not set and the voltage on pin  $V_{IO}$  is between 2.8 V and 4.75 V

After reading the status register, if an edge is not detected on pin EN for  $t_{det(EN)}$ , status bits S4 to S10 are cleared provided the corresponding flags have been reset.

| Status bit<br>LOCAL WAKEUP<br>REMOTE WAKEUP | Description<br>local wake-up source flag is redirected to this bit<br>remote wake-up source flag is redirected to this bit |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                                             |                                                                                                                            |

| REMOTE WAKEUP                               | romate wake up source flag is redirected to this bit                                                                       |

|                                             | remote wake-up source may is requested to this bit                                                                         |

| -                                           | not used; always set                                                                                                       |

| PWON                                        | status bit set means PWON flag has been set previously                                                                     |

| BUS ERROR                                   | status bit set means bus error flag has been set previously                                                                |

| TEMP HIGH                                   | status bit set means temperature high flag has been set previously                                                         |

| TEMP MEDIUM                                 | status bit set means temperature medium flag has been set previously                                                       |

| TXEN CLAMPED                                | status bit set means TXEN clamped flag has been set previously                                                             |

| UVVBAT                                      | status bit set means $UV_{VBAT}$ flag has been set previously                                                              |

| UVVCC                                       | status bit set means $UV_{VCC}$ flag has been set previously                                                               |

| UVVIO                                       | status bit set means $UV_{VIO}$ flag has been set previously                                                               |

| BGE FEEDBACK                                | BGE feedback (status bit reset if pin BGE LOW; status bit set if pin BGE HIGH)                                             |

| -                                           | not used; always reset                                                                                                     |

|                                             | BUS ERROR<br>TEMP HIGH<br>TEMP MEDIUM<br>TXEN CLAMPED<br>JVVBAT<br>JVVCC<br>JVVIO<br>BGE FEEDBACK                          |

## **NXP Semiconductors**

FlexRay node transceiver

FlexRay node transceiver

# 7. Limiting values

#### Table 11. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). All voltages are referenced to ground.

| Symbol               | Parameter                       | Conditions                                                                 |                | Min  | Max                    | Uni |

|----------------------|---------------------------------|----------------------------------------------------------------------------|----------------|------|------------------------|-----|

| V <sub>BAT</sub>     | battery supply voltage          | no time limit                                                              |                | -0.3 | +60                    | V   |

|                      |                                 | operating range                                                            |                | 4.75 | 60                     | V   |

| Vcc                  | supply voltage                  | no time limit                                                              |                | -0.3 | +5.5                   | V   |

|                      |                                 | operating range                                                            |                | 4.75 | 5.25                   | V   |

| V <sub>IO</sub>      | supply voltage on pin $V_{IO}$  | no time limit                                                              |                | -0.3 | +5.5                   | V   |

|                      |                                 | operating range                                                            |                | 2.8  | 5.25                   | V   |

| V <sub>INH</sub>     | voltage on pin INH              |                                                                            |                | -0.3 | V <sub>BAT</sub> + 0.3 | V   |

| O(INH)               | output current on pin INH       | no time limit                                                              |                | -1   | -                      | mA  |

| VWAKE                | voltage on pin WAKE             |                                                                            |                | -0.3 | V <sub>BAT</sub> + 0.3 | V   |

| I <sub>o(WAKE)</sub> | output current on pin WAKE      | pin GND not connected                                                      |                | -15  | -                      | mA  |

| V <sub>BGE</sub>     | voltage on pin BGE              | no time limit                                                              |                | -0.3 | +5.5                   | V   |

| V <sub>TXEN</sub>    | voltage on pin TXEN             | no time limit                                                              |                | -0.3 | +5.5                   | V   |

| V <sub>TXD</sub>     | voltage on pin TXD              | no time limit                                                              |                | -0.3 | +5.5                   | V   |

| V <sub>errn</sub>    | voltage on pin ERRN             | no time limit                                                              |                | -0.3 | V <sub>IO</sub> + 0.3  | V   |

| V <sub>RXD</sub>     | voltage on pin RXD              | no time limit                                                              |                | -0.3 | V <sub>IO</sub> + 0.3  | V   |

| V <sub>RXEN</sub>    | voltage on pin RXEN             | no time limit                                                              |                | -0.3 | V <sub>IO</sub> + 0.3  | V   |

| V <sub>EN</sub>      | voltage on pin EN               | no time limit                                                              |                | -0.3 | +5.5                   | V   |

| V <sub>STBN</sub>    | voltage on pin STBN             | no time limit                                                              |                | -0.3 | +5.5                   | V   |

| V <sub>BP</sub>      | voltage on pin BP               | no time limit; with resect to pins BM, $V_{\text{BAT}},$ WAKE, INH and GND |                | -60  | +60                    | V   |

| V <sub>BM</sub>      | voltage on pin BM               | no time limit; with resect to pins BP, $V_{BAT}$ , WAKE, INH and GND       |                | -60  | +60                    | V   |

| V <sub>trt</sub>     | transient voltage               | on pins BM and BP                                                          | [1]            | -100 | -                      | V   |

|                      | -                               |                                                                            | [2]            | -    | 75                     | V   |

|                      |                                 |                                                                            | [3]            | -150 | -                      | V   |

|                      |                                 |                                                                            | [4]            |      | 100                    | V   |

| T <sub>stg</sub>     | storage temperature             |                                                                            |                | -55  | +150                   | °C  |

| T <sub>vj</sub>      | virtual junction temperature    |                                                                            | [5]            | -40  | +150                   | °C  |

| T <sub>amb</sub>     | ambient temperature             |                                                                            |                | -40  | +125                   | °C  |

| V <sub>ESD</sub>     | electrostatic discharge voltage | HBM on pins BP and BM to ground                                            | [6]            | -6.0 | +6.0                   | kV  |

| 200                  | 5 5                             | HBM on pins V <sub>BAT</sub> and WAKE to ground                            |                | -4.0 | +4.0                   | kV  |

|                      |                                 | HBM at all other pins                                                      |                | -2.0 | +2.0                   | kV  |

|                      |                                 | MM on all pins                                                             |                | -100 | +100                   | V   |

|                      |                                 | CDM on corner pins                                                         | [8]            |      | +750                   | V   |

|                      |                                 | CDM on all other pins                                                      |                | -500 | +500                   | v   |

|                      |                                 | IEC61000-4-2 on pins BP and BM to ground                                   |                | -6.0 | +6.0                   | kV  |

|                      |                                 | IEC61000-4-2 on pin V <sub>BAT</sub> to ground                             | <u>[9][10]</u> | -6.0 | +6.0                   | kV  |

|                      |                                 | IEC61000-4-2 on pin WAKE to ground                                         | [9][11]        |      | +6.0                   | kV  |

### **NXP Semiconductors**

- [1] According to ISO7637, test pulse 1, class C; verified by an external test house.

- [2] According to ISO7637, test pulse 2a, class C; verified by an external test house.

- [3] According to ISO7637, test pulse 3a, class C; verified by an external test house.

- According to ISO7637, test pulse 3b, class C; verified by an external test house. [4]

- In accordance with IEC 60747-1. An alternative definition of  $T_{vj}$  is:  $T_{vj} = T_{amb} + P \times R_{th(j-a)}$ , where  $R_{th(j-a)}$  is a fixed value to be used for the [5] calculation of T<sub>vi</sub>. The rating for T<sub>vi</sub> limits the allowable combinations of power dissipation (P) and ambient temperature (T<sub>amb</sub>).

- HBM: C = 100 pF; R = 1.5 k $\Omega$ . [6]

- [7] MM: C = 200 pF; L = 0.75  $\mu$ H; R = 10  $\Omega$ .

- CDM: R = 1 Ω. [8]

- [9] IEC61000-4-2: C = 150 pF; R = 330  $\Omega$ ; verified by an external test house. The test result is equal to or better than ±6 kV (unaided).

- [10] With 100 nF from V<sub>BAT</sub> to GND.

- [11] With 3.3 k $\Omega$  in series.

#### Thermal characteristics 8.

#### Table 12. Thermal characteristics

| Symbol               | Parameter                                   | Conditions  | Тур | Unit |

|----------------------|---------------------------------------------|-------------|-----|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 118 | K/W  |

#### **Static characteristics** 9.

#### Table 13. Static characteristics

All parameters are guaranteed for  $V_{BAT} = 4.45$  V to 60 V;  $V_{CC} = 4.45$  V to 5.25 V;  $V_{IO} = 2.55$  V to 5.25 V;  $T_{vj} = -40$  °C to +150 °C;  $C_{bus} = 100 \text{ pF}$ ;  $R_{bus} = 40\Omega$  to 55  $\Omega$  unless otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol                   | Parameter                                                  | Conditions                                                                                         | Min   | Тур  | Max                 | Unit           |

|--------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------|------|---------------------|----------------|

| Pin V <sub>BAT</sub>     |                                                            |                                                                                                    |       |      |                     |                |

| I <sub>BAT</sub>         | battery supply current                                     | low-power modes;<br>no load on pin INH                                                             | -     | -    | 55                  | μΑ             |

|                          |                                                            | normal-power modes                                                                                 | -     | -    | 1                   | mA             |

| V <sub>uvd(VBAT)</sub>   | undervoltage detection voltage on pin V <sub>BAT</sub>     |                                                                                                    | 4.45  | -    | 4.715               | V              |

| V <sub>uvr(VBAT)</sub>   | undervoltage recovery voltage on<br>pin V <sub>BAT</sub>   |                                                                                                    | 4.475 | -    | 4.74                | V              |

| V <sub>uvhys(VBAT)</sub> | undervoltage hysteresis voltage on<br>pin V <sub>BAT</sub> |                                                                                                    | 25    | -    | 290                 | mV             |

| Pin V <sub>CC</sub>      |                                                            |                                                                                                    |       |      |                     |                |

| I <sub>CC</sub>          | supply current                                             | low-power modes                                                                                    | -1    | +2   | +10                 | μA             |

|                          |                                                            | Normal mode;<br>V <sub>BGE</sub> = 0 V; V <sub>TXEN</sub> = V <sub>IO</sub> ;<br>Receive-only mode | -     | 11   | 22                  | mA             |

|                          |                                                            | Normal mode;<br>V <sub>BGE</sub> = V <sub>IO</sub> ; V <sub>TXEN</sub> = 0 V                       | -     | 47   | 60                  | mA             |

|                          |                                                            | Normal mode;<br>$V_{BGE} = V_{IO}; V_{TXEN} = 0 V;$<br>$R_{bus} = \infty \Omega$                   | -     | 21   | 40                  | mA             |

| V <sub>uvd(VCC)</sub>    | undervoltage detection voltage on pin $V_{CC}$             |                                                                                                    | 4.45  | -    | 4.72                | V              |

| TJA1081B                 | All information provided                                   | n this document is subject to legal disclaimers.                                                   |       | © NX | P B.V. 2012. All ri | ghts reserved. |

| Product data sh          | neet Rev                                                   | 1 — 4 June 2012                                                                                    |       |      |                     | 21 of 45       |

All parameters are guaranteed for  $V_{BAT} = 4.45$  V to 60 V;  $V_{CC} = 4.45$  V to 5.25 V;  $V_{IO} = 2.55$  V to 5.25 V;  $T_{vj} = -40$  °C to +150 °C;  $C_{bus} = 100$  pF;  $R_{bus} = 40\Omega$  to 55  $\Omega$  unless otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol                  | Parameter                                                 | Conditions                                                                                                                                                                                | Min          | Тур | Max                 | Unit |

|-------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|---------------------|------|

| V <sub>uvr(VCC)</sub>   | undervoltage recovery voltage on pin $V_{CC}$             |                                                                                                                                                                                           | 4.47         | -   | 4.74                | V    |

| V <sub>uvhys(VCC)</sub> | undervoltage hysteresis voltage on pin $V_{CC}$           |                                                                                                                                                                                           | 20           | -   | 290                 | mV   |

| Pin V <sub>IO</sub>     |                                                           |                                                                                                                                                                                           |              |     |                     |      |

| I <sub>IO</sub>         | supply current on pin $V_{IO}$                            | low-power modes;<br>V <sub>TXEN</sub> = V <sub>IO</sub>                                                                                                                                   | -1           | +2  | +10                 | μA   |

|                         |                                                           | Normal and Receive-only modes; $V_{TXD} = V_{IO}$                                                                                                                                         | -            | -   | 1000                | μΑ   |

| I <sub>r(VIO)</sub>     | reverse current on pin V <sub>IO</sub>                    | from digital input pins;<br>PowerOff mode;<br>$V_{TXEN} = 5.25 V;$<br>$V_{TXD} = 5.25 V;$<br>$V_{BGE} = 5.25 V;$<br>$V_{EN} = 5.25 V;$<br>$V_{STBN} = 5.25 V;$<br>$V_{CC} = V_{IO} = 0 V$ | -5           | -   | +5                  | μΑ   |

| V <sub>uvd(VIO)</sub>   | undervoltage detection voltage on pin $V_{\text{IO}}$     |                                                                                                                                                                                           | 2.55         | -   | 2.765               | V    |

| V <sub>uvr(VIO)</sub>   | undervoltage recovery voltage on pin $V_{IO}$             |                                                                                                                                                                                           | 2.575        | -   | 2.79                | V    |

| V <sub>uvhys(VIO)</sub> | undervoltage hysteresis voltage on<br>pin V <sub>IO</sub> |                                                                                                                                                                                           | 25           | -   | 240                 | mV   |

| Pin EN                  |                                                           |                                                                                                                                                                                           |              |     |                     |      |

| V <sub>IH</sub>         | HIGH-level input voltage                                  |                                                                                                                                                                                           | $0.7 V_{IO}$ | -   | 5.5                 | V    |

| V <sub>IL</sub>         | LOW-level input voltage                                   |                                                                                                                                                                                           | -0.3         | -   | $0.3 V_{\text{IO}}$ | V    |

| I <sub>IH</sub>         | HIGH-level input current                                  | $V_{EN} = 0.7 V_{IO}$                                                                                                                                                                     | 3            | -   | 15                  | μΑ   |

| IIL                     | LOW-level input current                                   | V <sub>EN</sub> = 0 V                                                                                                                                                                     | -1           | 0   | +1                  | μΑ   |

| Pin STBN                |                                                           |                                                                                                                                                                                           |              |     |                     |      |

| V <sub>IH</sub>         | HIGH-level input voltage                                  |                                                                                                                                                                                           | $0.7 V_{IO}$ | -   | 5.5                 | V    |

| V <sub>IL</sub>         | LOW-level input voltage                                   |                                                                                                                                                                                           | -0.3         | -   | $0.3 V_{IO}$        | V    |

| I <sub>IH</sub>         | HIGH-level input current                                  | $V_{STBN} = 0.7 V_{IO}$                                                                                                                                                                   | 3            | -   | 15                  | μA   |

| IL                      | LOW-level input current                                   | V <sub>STBN</sub> = 0 V                                                                                                                                                                   | -1           | 0   | +1                  | μA   |

| Pin TXEN                |                                                           |                                                                                                                                                                                           |              |     |                     |      |

| V <sub>IH</sub>         | HIGH-level input voltage                                  |                                                                                                                                                                                           | $0.7 V_{IO}$ | -   | 5.5                 | V    |

| V <sub>IL</sub>         | LOW-level input voltage                                   |                                                                                                                                                                                           | -0.3         | -   | $0.3V_{IO}$         | V    |

| I <sub>IH</sub>         | HIGH-level input current                                  | $V_{TXEN} = V_{IO}$                                                                                                                                                                       | -1           | 0   | +1                  | μA   |

| IL                      | LOW-level input current                                   | $V_{TXEN} = 0.3 V_{IO}$                                                                                                                                                                   | -300         | -   | -50                 | μA   |

| IL                      | leakage current                                           | $V_{TXEN}$ = 5.25 V; $V_{IO}$ = 0 V                                                                                                                                                       | -1           | 0   | +1                  | μA   |

| Pin BGE                 |                                                           |                                                                                                                                                                                           |              |     |                     |      |

| V <sub>IH</sub>         | HIGH-level input voltage                                  |                                                                                                                                                                                           | $0.7 V_{IO}$ | -   | 5.5                 | V    |

| V <sub>IL</sub>         | LOW-level input voltage                                   |                                                                                                                                                                                           | -0.3         | -   | $0.3V_{IO}$         | V    |

| I <sub>IH</sub>         | HIGH-level input current                                  | $V_{BGE} = 0.7 V_{IO}$                                                                                                                                                                    | 3            | -   | 15                  | μA   |

| IIL                     | LOW-level input current                                   | V <sub>BGE</sub> = 0 V                                                                                                                                                                    | -1           | 0   | +1                  | μA   |

All information provided in this document is subject to legal disclaimers.

TJA1081B

All parameters are guaranteed for  $V_{BAT} = 4.45$  V to 60 V;  $V_{CC} = 4.45$  V to 5.25 V;  $V_{IO} = 2.55$  V to 5.25 V;  $T_{vj} = -40$  °C to +150 °C;  $C_{bus} = 100$  pF;  $R_{bus} = 40\Omega$  to 55  $\Omega$  unless otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol                        | Parameter                                                                         | Conditions                                                                                                                         |                          | Min                      | Тур             | Max                      | Unit |

|-------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|-----------------|--------------------------|------|

| V <sub>IH</sub>               | HIGH-level input voltage                                                          | normal-power modes                                                                                                                 |                          | 0.6V <sub>IO</sub>       | -               | V <sub>IO</sub> +<br>0.3 | V    |

| V <sub>IL</sub>               | LOW-level input voltage                                                           | normal-power modes                                                                                                                 |                          | -0.3                     | -               | $0.4 V_{IO}$             | V    |

| I <sub>IH</sub>               | HIGH-level input current                                                          | $V_{TXD} = V_{IO}$                                                                                                                 |                          | 3                        | -               | 15                       | μA   |

| IIL                           | LOW-level input current                                                           | normal-power modes;<br>V <sub>TXD</sub> = 0 V                                                                                      |                          | -5                       | 0               | +5                       | μA   |

|                               |                                                                                   | low-power modes                                                                                                                    |                          | -1                       | 0               | +1                       | μA   |

| I <sub>LI</sub>               | input leakage current                                                             | $V_{TXD} = 5.25 \text{ V}; V_{IO} = 0 \text{ V}$                                                                                   |                          | -1                       | 0               | +1                       | μA   |

| Ci                            | input capacitance                                                                 | not tested; with respect to<br>all other pins at ground;<br>V <sub>TXD</sub> = 100 mV; f = 5 MH                                    |                          | -                        | 5               | 10                       | pF   |

| Pin RXD                       |                                                                                   |                                                                                                                                    |                          |                          |                 |                          |      |

| I <sub>OH</sub>               | HIGH-level output current                                                         | $V_{RXD} = V_{IO} - 0.4 V;$<br>$V_{IO} = V_{CC}$                                                                                   |                          | -20                      | -               | -2                       | mA   |

| I <sub>OL</sub>               | LOW-level output current                                                          | $V_{RXD} = 0.4 V$                                                                                                                  |                          | 2                        | -               | 20                       | mA   |

| V <sub>OH</sub>               | HIGH-level output voltage                                                         | $I_{OH(RXD)} = -2 \text{ mA}$                                                                                                      | <u>[1]</u>               | V <sub>IO</sub> –<br>0.4 | -               | V <sub>IO</sub>          | V    |

| V <sub>OL</sub>               | LOW-level output voltage                                                          | $I_{OL(RXD)} = 2 \text{ mA}$                                                                                                       | [1]                      | -                        | -               | 0.4                      | V    |

| V <sub>O</sub> output voltage | when undervoltage on $V_{IO}; V_{CC} \ge 4.75 V;$ $R_L = 100 \ k\Omega$ to ground |                                                                                                                                    | -                        | -                        | 0.5             | V                        |      |

|                               | $R_L = 100 \text{ k}\Omega \text{ to } V_{IO};$ power off                         |                                                                                                                                    | V <sub>IO</sub> –<br>0.5 | -                        | V <sub>IO</sub> | V                        |      |

| Pin ERRN                      |                                                                                   |                                                                                                                                    |                          |                          |                 |                          |      |

| I <sub>OH</sub>               | HIGH-level output current                                                         |                                                                                                                                    |                          | -8                       | -3              | -0.5                     | mA   |

| I <sub>OL</sub>               | LOW-level output current                                                          | $V_{ERRN} = 0.4 V$                                                                                                                 |                          | 0.5                      | 2               | 8                        | mΑ   |

| V <sub>OH</sub>               | HIGH-level output voltage                                                         | $I_{OH(ERRN)} = -0.5 \text{ mA}$                                                                                                   | <u>[1]</u>               | V <sub>IO</sub> –<br>0.4 | -               | V <sub>IO</sub>          | V    |

| V <sub>OL</sub>               | LOW-level output voltage                                                          | $I_{OL(ERRN)} = 0.5 \text{ mA}$                                                                                                    | [1]                      | -                        | -               | 0.4                      | V    |

| lL                            | leakage current                                                                   | $0 V \le V_{ERRN} \le V_{IO};$ power off                                                                                           |                          | -5                       | 0               | +5                       | μA   |

| Vo                            | output voltage                                                                    | when undervoltage on $V_{IO}; V_{CC} > 4.75 V;$<br>$R_L = 100 k\Omega$ to ground                                                   |                          | -                        | -               | 0.5                      | V    |

|                               |                                                                                   | $R_L = 100 \text{ k}\Omega$ to ground; power off                                                                                   |                          | -                        | -               | 0.5                      | V    |

| Pin RXEN                      |                                                                                   |                                                                                                                                    |                          |                          |                 |                          |      |

| I <sub>OH</sub>               | HIGH-level output current                                                         | $\label{eq:VRXEN} \begin{array}{l} V_{\text{RXEN}} = V_{\text{IO}} - 0.4 \ \text{V}; \\ V_{\text{IO}} = V_{\text{CC}} \end{array}$ |                          | -8                       | -3              | -0.5                     | mA   |

| l <sub>oL</sub>               | LOW-level output current                                                          | $V_{RXEN} = 0.4 V$                                                                                                                 |                          | 0.5                      | 2               | 8                        | mA   |

| V <sub>OH</sub>               | HIGH-level output voltage                                                         | $I_{OH(RXEN)} = -0.5 \text{ mA}$                                                                                                   | <u>[1]</u>               | V <sub>IO</sub> –<br>0.4 | -               | V <sub>IO</sub>          | V    |

All parameters are guaranteed for  $V_{BAT} = 4.45$  V to 60 V;  $V_{CC} = 4.45$  V to 5.25 V;  $V_{IO} = 2.55$  V to 5.25 V;  $T_{vj} = -40$  °C to +150 °C;  $C_{bus} = 100$  pF;  $R_{bus} = 40\Omega$  to 55  $\Omega$  unless otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol                      | Parameter                                                                 | Conditions                                                                                                             |                   | Min                      | Тур                | Max                | Unit |