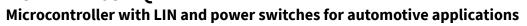

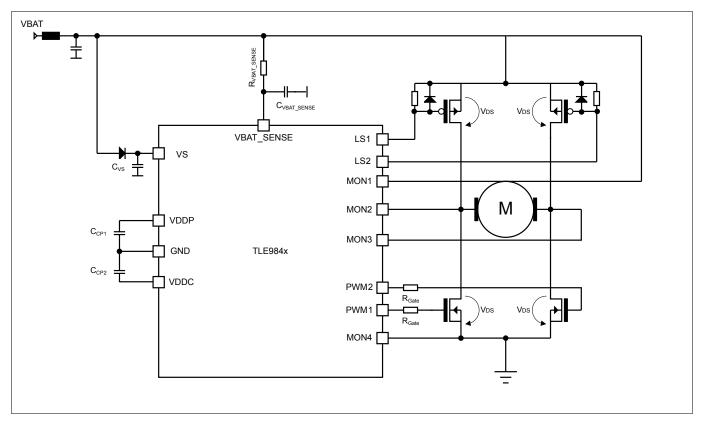

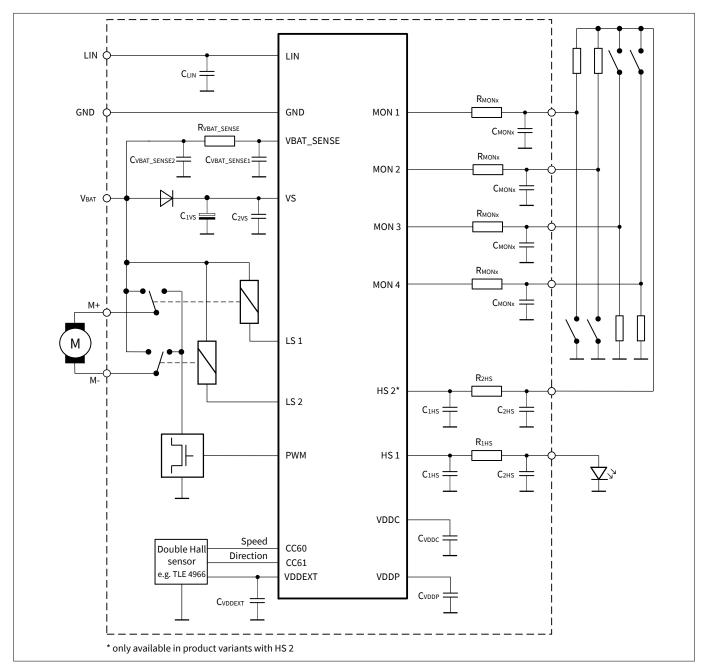

### Microcontroller with LIN and power switches for automotive applications

#### **About this document**

This user manual is addressed to embedded hardware and software developers. It provides the reader with detailed descriptions about the behavior of the MOTIX<sup>™</sup> TLE984xQX functional units and their interaction.

The manual describes the functionality of the superset device (TLE9844QX) of the MOTIX<sup>™</sup> TLE984xQX Embedded Power IC family. For the available functionality (features) of a specific MOTIX<sup>™</sup> TLE984xQX derivative (derivative device), please refer to the respective datasheet. For simplicity, the various device types are referenced by the collective term MOTIX<sup>™</sup> TLE984xQX throughout this manual.

## Microcontroller with LIN and power switches for automotive applications

#### **Table of contents**

|           | About this document                                                              | 1  |

|-----------|----------------------------------------------------------------------------------|----|

|           | Table of contents                                                                | 2  |

| 1         | Overview                                                                         | 26 |

| 1.1       | Abbreviations                                                                    |    |

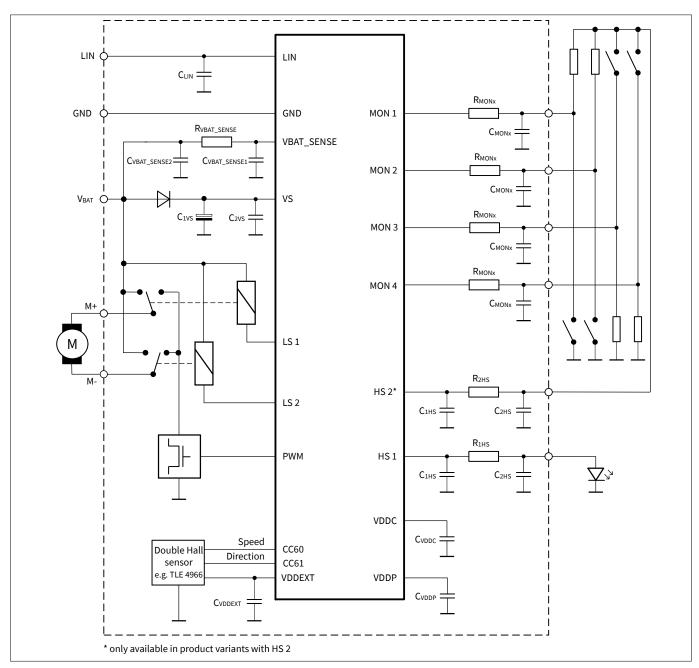

| 2         | Block diagram                                                                    | 31 |

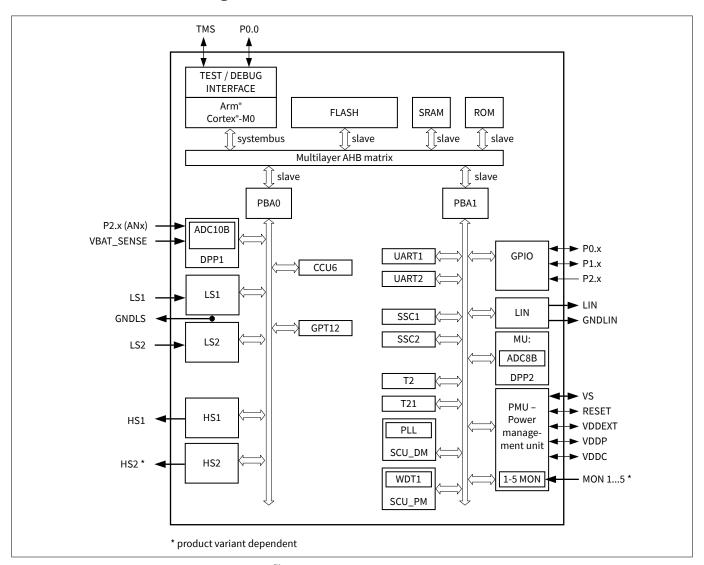

| 3         | Device pinout and pin configuration                                              | 32 |

| 3.1       | Device pinout                                                                    |    |

| 3.2       | Pin configuration                                                                |    |

| 4         | Introduction                                                                     | 36 |

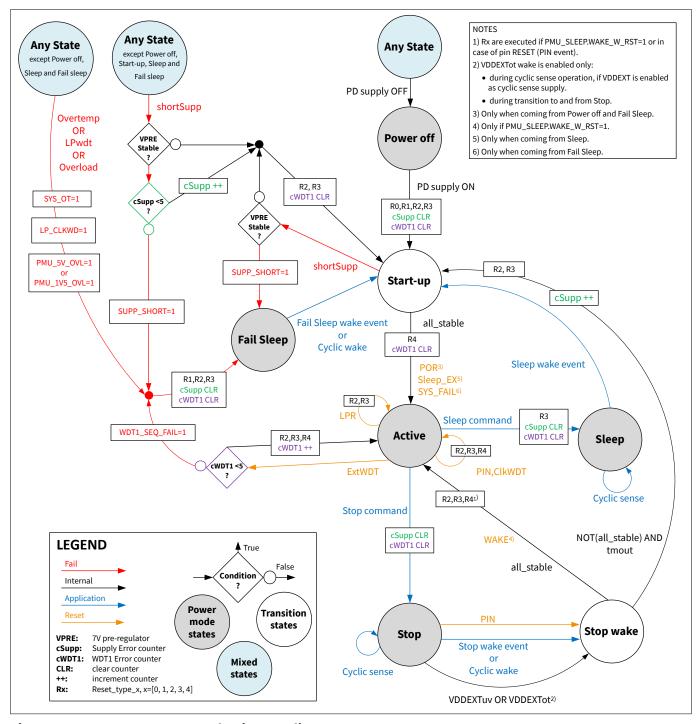

| 4.1       | SOC system power modes overview                                                  |    |

| 4.2       | Device register types                                                            |    |

| 4.3       | Device reset masks                                                               |    |

| 5         | Power management unit (PMU)                                                      | 41 |

| 5.1       | Features                                                                         |    |

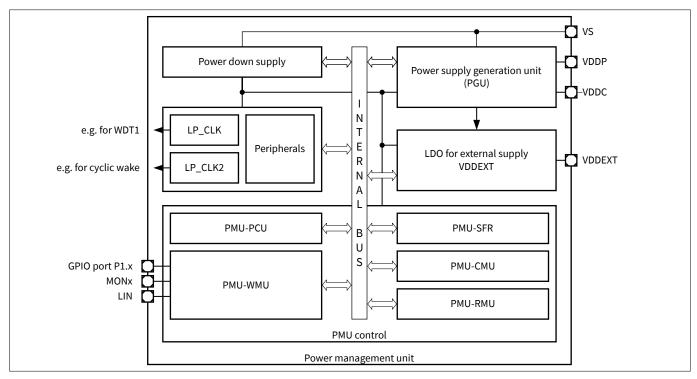

| 5.2       | Introduction                                                                     | 41 |

| 5.2.1     | Block diagram                                                                    | 42 |

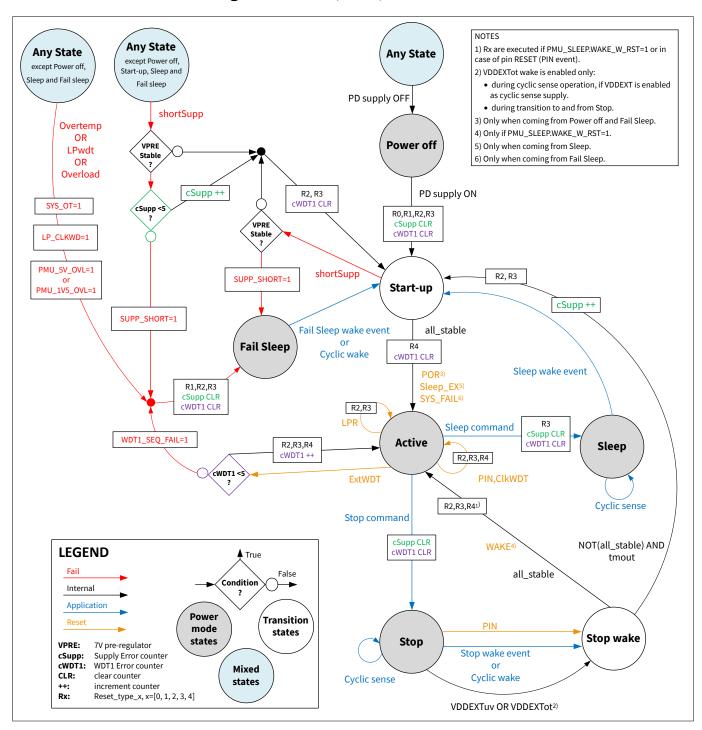

| 5.2.2     | PMU modes overview                                                               |    |

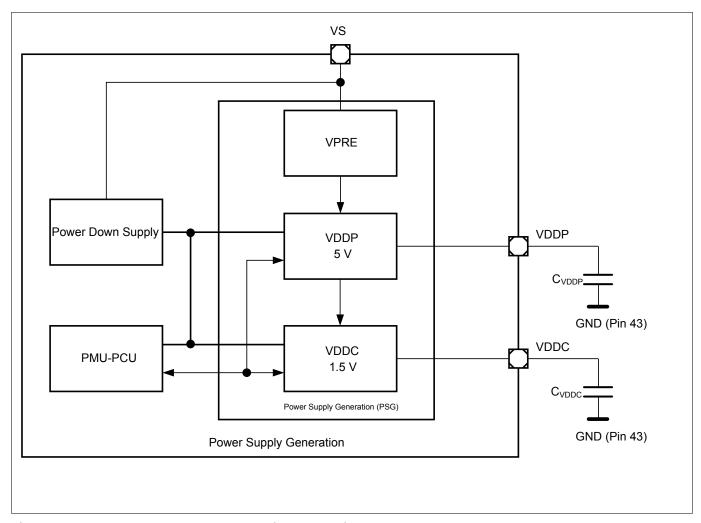

| 5.3       | Power supply generation (PGU)                                                    | 45 |

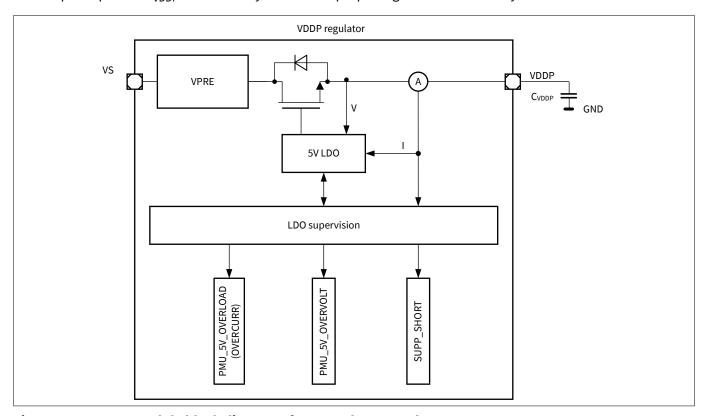

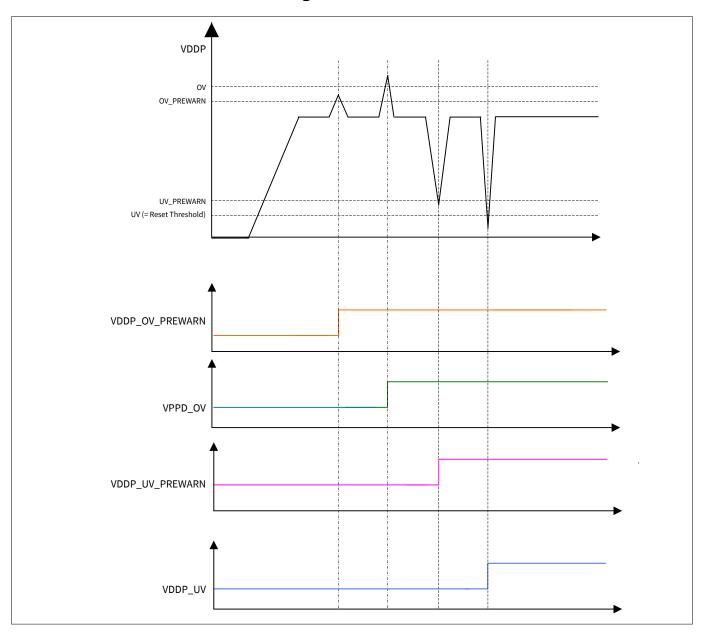

| 5.3.1     | Voltage regulator 5.0 V (VDDP)                                                   |    |

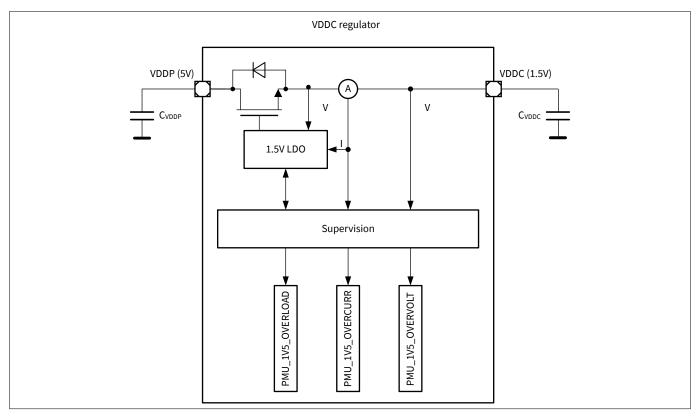

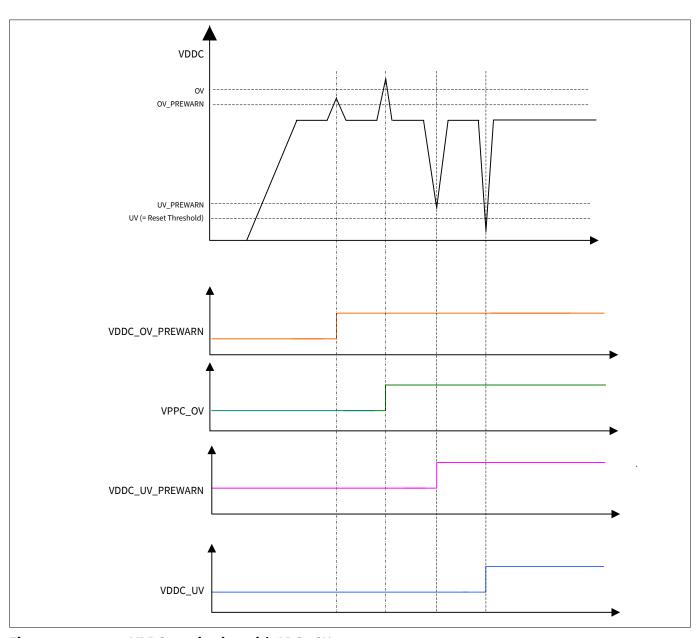

| 5.3.2     | Voltage regulator 1.5 V (VDDC)                                                   | 47 |

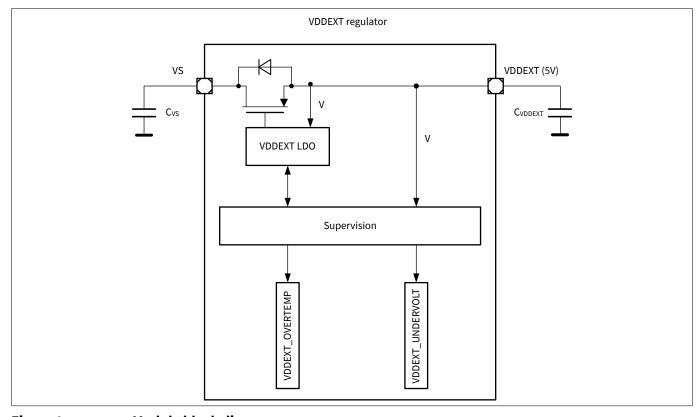

| 5.3.3     | External voltage regulator 5.0 V (VDDEXT)                                        | 48 |

| 5.3.3.1   | VDDEXT internal diagnosis                                                        | 49 |

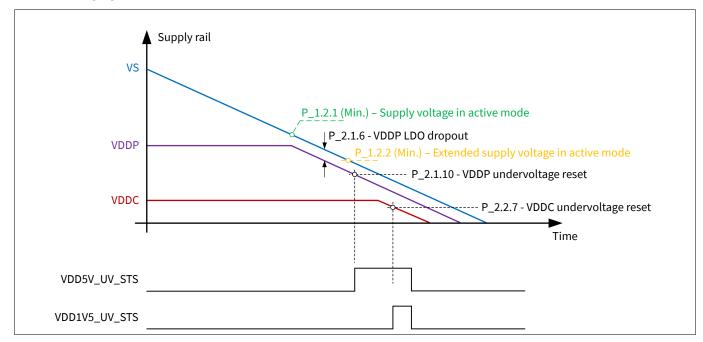

| 5.3.4     | Low-V <sub>S</sub> operation                                                     | 50 |

| 5.3.5     | PGU ADC2 monitoring                                                              | 51 |

| 5.3.6     | Power supply generation (PGU) registers                                          | 53 |

| 5.3.6.1   | Register overview - Power Supply Generation registers (ascending offset address) | 53 |

| 5.3.6.2   | Power supply generation register                                                 | 53 |

| 5.3.6.3   | VDDEXT control register                                                          | 53 |

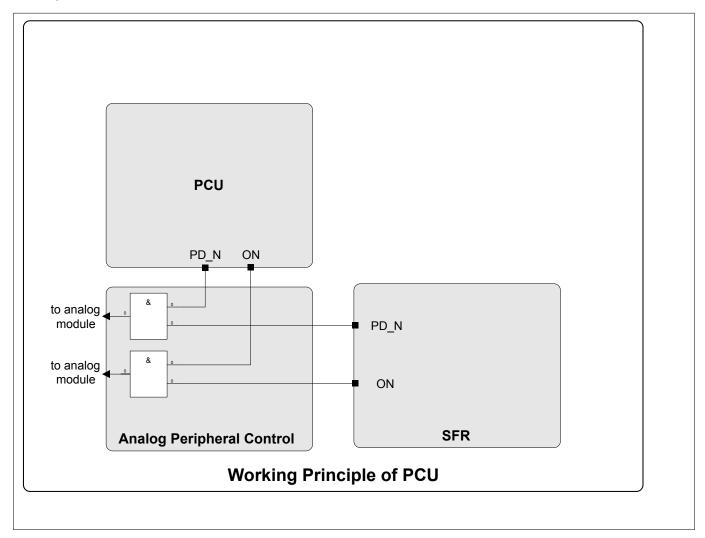

| 5.4       | Power control unit (PCU)                                                         | 54 |

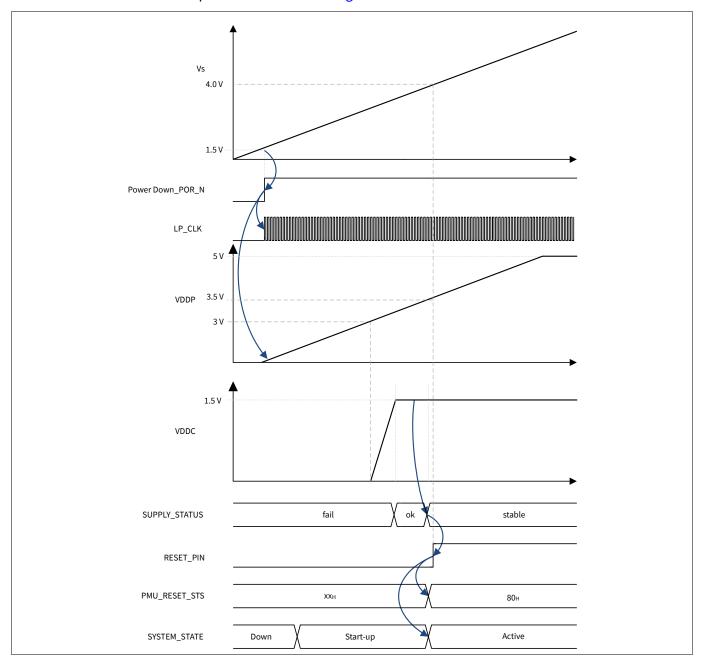

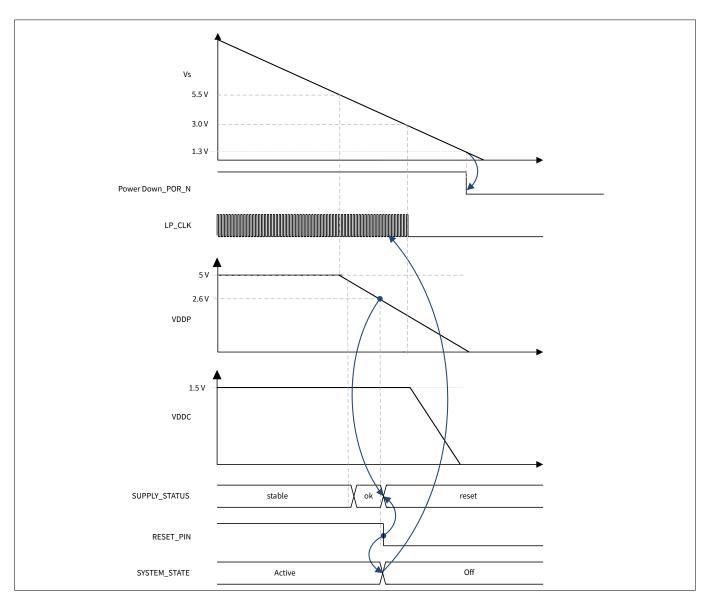

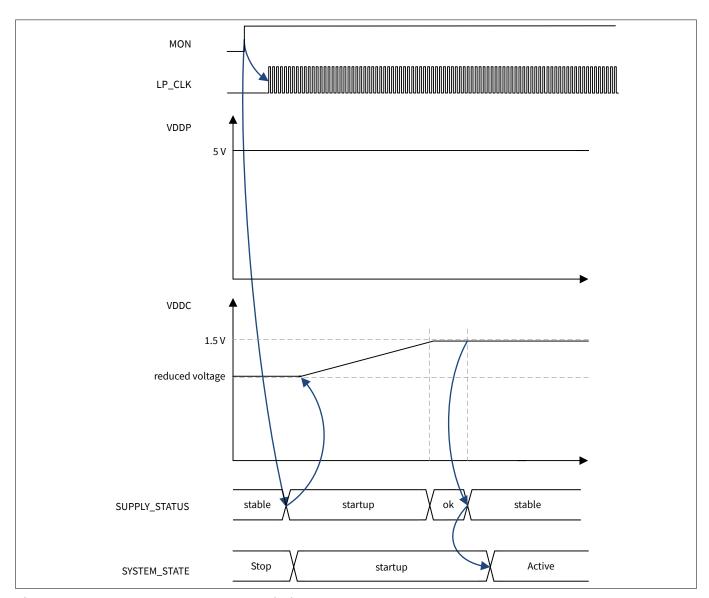

| 5.4.1     | Power-off and start-up                                                           | 56 |

| 5.4.2     | Active mode                                                                      | 57 |

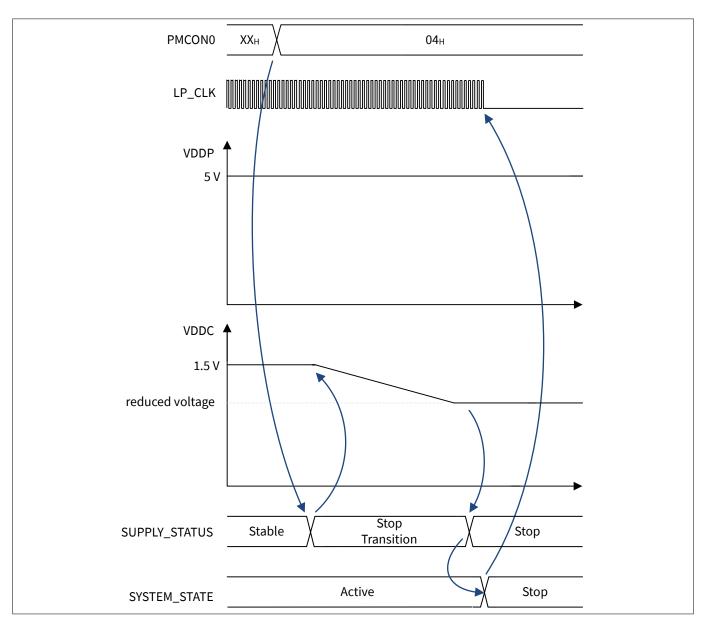

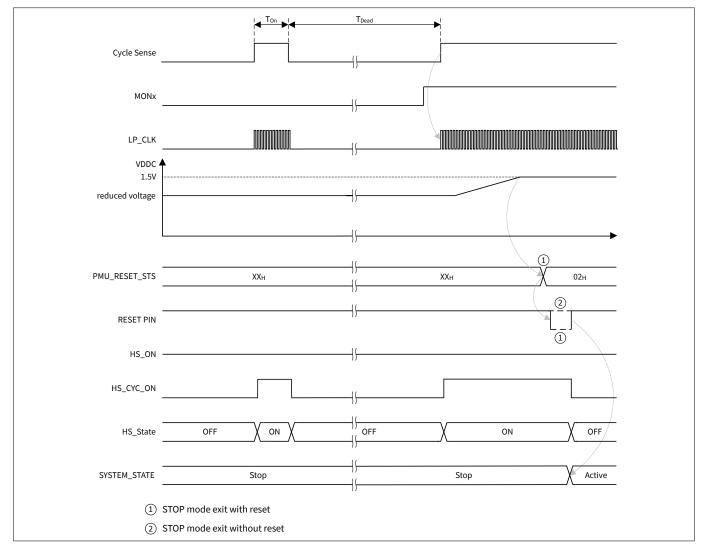

| 5.4.3     | Stop mode                                                                        | 58 |

| 5.4.4     | Stop wake                                                                        | 60 |

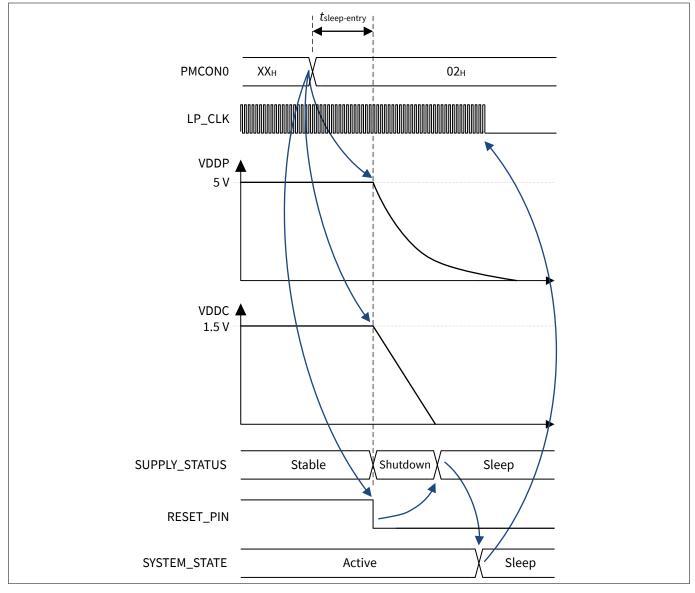

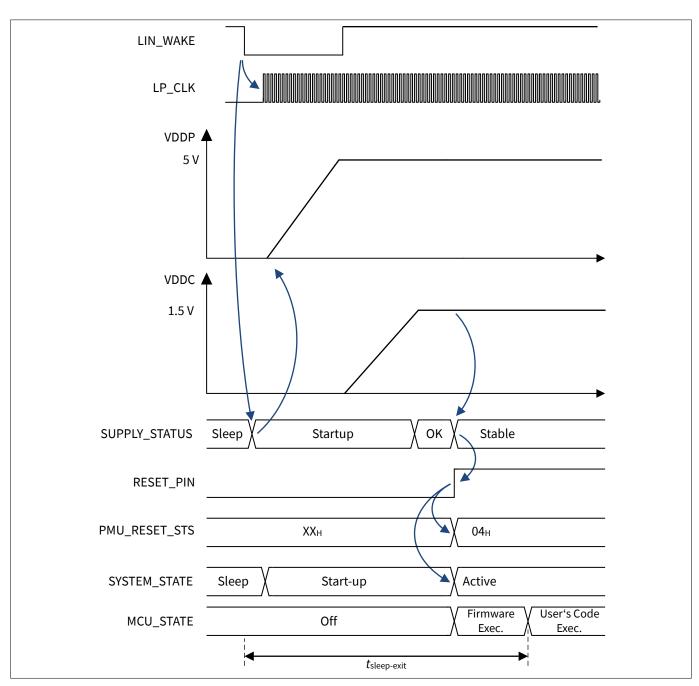

| 5.4.5     | Sleep mode                                                                       | 61 |

| 5.4.6     | Fail Sleep mode                                                                  | 63 |

| 5.4.6.1   | Fail safe scenarios                                                              | 64 |

| 5.4.6.1.1 | VDDP/VDDC supply error                                                           | 64 |

| 5.4.6.1.2 | Watchdog timer WDT1 error                                                        | 64 |

|           |                                                                                  |    |

# $\textbf{MOTIX}^{^{\text{TM}}}\textbf{TLE984xQX}$

## Microcontroller with LIN and power switches for automotive applications

| 5.4.6.1.3 | WDT1 and supply error counters                                                   | 64 |

|-----------|----------------------------------------------------------------------------------|----|

| 5.4.6.1.4 | VDDP/VDDC overcurrent                                                            | 65 |

| 5.4.6.1.5 | System overtemperature                                                           | 65 |

| 5.4.6.1.6 | LP_CLK clock watchdog                                                            | 65 |

| 5.4.7     | Power control unit registers                                                     | 66 |

| 5.4.7.1   | Register overview - Power Control Unit registers (ascending offset address)      | 66 |

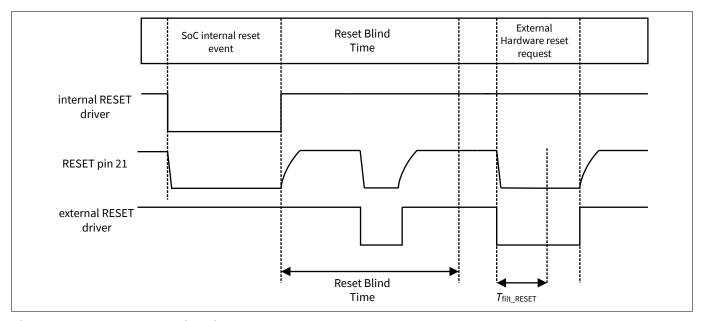

| 5.5       | Reset management unit (RMU)                                                      | 67 |

| 5.5.1     | Reset sources                                                                    | 68 |

| 5.5.1.1   | Power-on reset                                                                   | 68 |

| 5.5.1.2   | System fail                                                                      | 68 |

| 5.5.1.3   | Wake-up from Stop mode (with reset)                                              | 68 |

| 5.5.1.4   | Wake-up from Sleep mode                                                          | 68 |

| 5.5.1.5   | Low priority resets - software reset or lockup                                   | 68 |

| 5.5.1.6   | Clock watchdog                                                                   | 69 |

| 5.5.1.7   | Watchdog timer (WDT1)                                                            | 69 |

| 5.5.1.8   | Hardware reset (RESET pin)                                                       | 69 |

| 5.5.2     | RESET pin                                                                        | 70 |

| 5.5.3     | Reset management unit (RMU) registers                                            | 71 |

| 5.5.3.1   | Register overview - Reset Management Unit registers (ascending offset address)   | 71 |

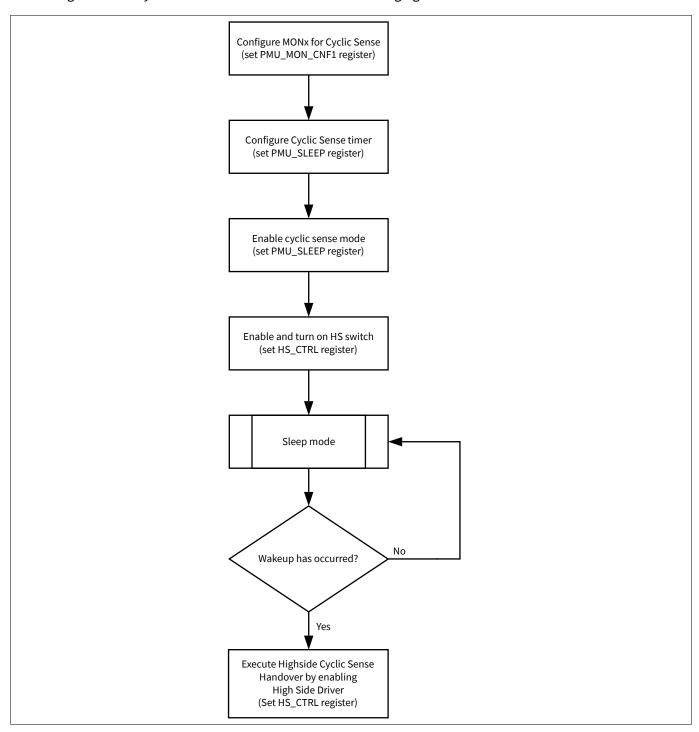

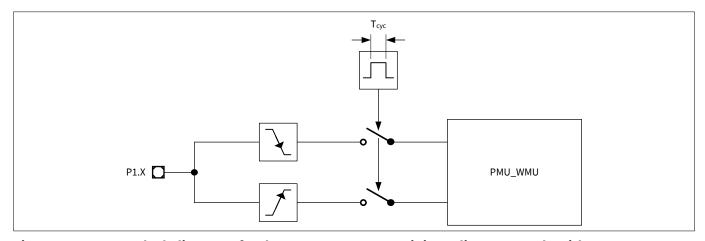

| 5.6       | Cyclic management unit (CMU)                                                     | 72 |

| 5.6.1     | Cyclic sense mode                                                                | 72 |

| 5.6.1.1   | Configuration of cyclic sense mode                                               | 73 |

| 5.6.2     | Cyclic wake mode                                                                 | 73 |

| 5.6.3     | Cyclic management unit (CMU) registers                                           | 74 |

| 5.6.3.1   | Register overview - Cyclic Management Unit registers (ascending offset address)  | 74 |

| 5.6.3.2   | Cyclic mode configuration registers (CYCMU)                                      | 74 |

| 5.7       | Wake-up management unit (WMU)                                                    | 75 |

| 5.7.1     | Wake-up management unit (WMU) registers                                          | 76 |

| 5.7.1.1   | Register overview - Wake-up Management Unit registers (ascending offset address) | 76 |

| 5.8       | PMU data storage area                                                            | 77 |

| 5.8.1     | PMU data storage registers                                                       | 77 |

| 5.8.1.1   | Register overview - PMU data storage area registers (ascending offset address)   | 77 |

| 5.9       | Power management unit (PMU) register definition                                  | 78 |

| 5.9.1     | Register address space - PMU                                                     | 78 |

| 5.9.2     | Register overview - PMU (ascending offset address)                               | 78 |

| 5.9.3     | Voltage reg status register                                                      | 79 |

| 5.9.4     | VDDEXT control register                                                          | 81 |

| 5.9.5     | High-side control register                                                       | 83 |

| 5.9.6     | WFS system fail register                                                         | 84 |

| 5.9.7     | Main wake status register                                                        | 86 |

| 5.9.8     | GPIO port wake status register                                                   | 89 |

| 5.9.9     | LIN wake enable register                                                         | 91 |

## Microcontroller with LIN and power switches for automotive applications

| 5.9.10  | PMU wake-up timing register                                                    | 92  |

|---------|--------------------------------------------------------------------------------|-----|

| 5.9.11  | Wake configuration GPIO port 1 register                                        | 93  |

| 5.9.12  | PMU sleep behavior register                                                    | 95  |

| 5.9.13  | Reset status register                                                          | 97  |

| 5.9.14  | Reset blind time register                                                      | 99  |

| 5.9.15  | General purpose user DATA0to3 register                                         | 100 |

| 5.9.16  | General purpose user DATA4to7 register                                         | 101 |

| 5.9.17  | General purpose user DATA8to11 register                                        | 102 |

| 5.9.18  | Settings monitor 1-4 register                                                  | 103 |

| 5.9.19  | Settings monitor 5 register                                                    | 107 |

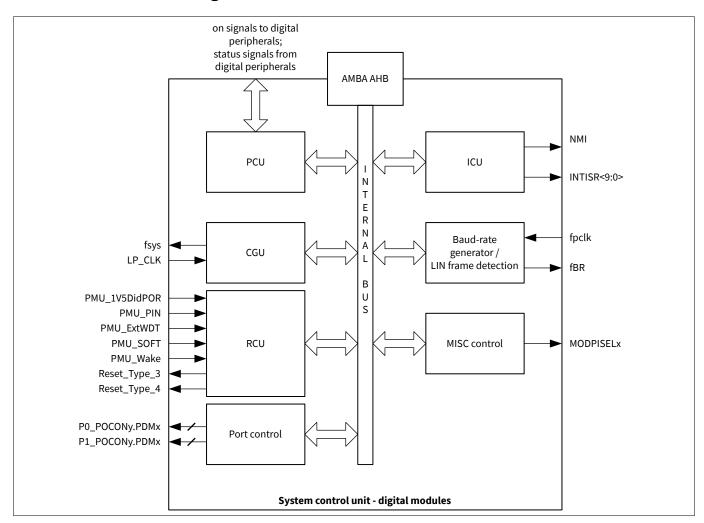

| 6       | System control unit - digital modules (SCU-DM)                                 | 109 |

| 6.1     | Features                                                                       | 109 |

| 6.2     | Introduction                                                                   | 109 |

| 6.2.1   | Block diagram                                                                  | 110 |

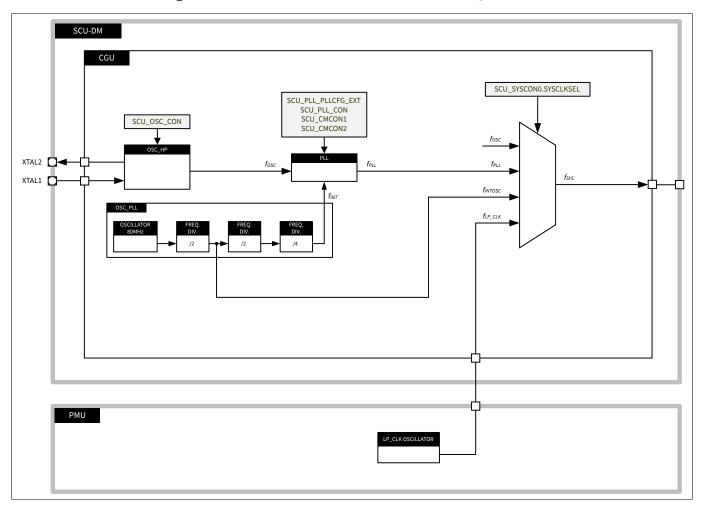

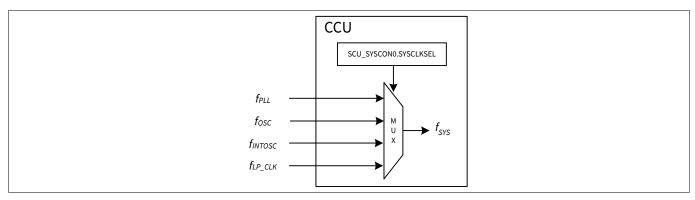

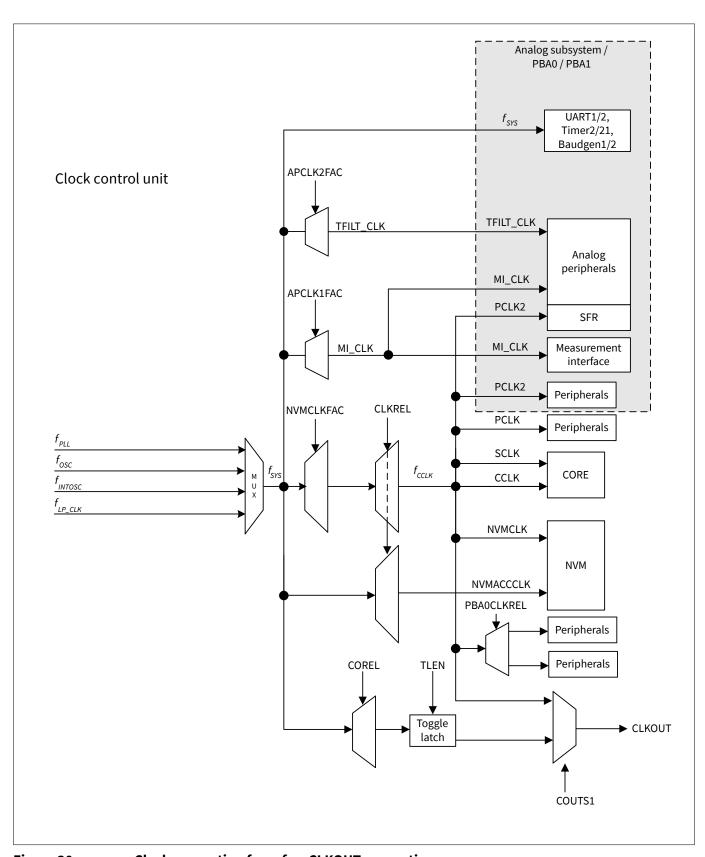

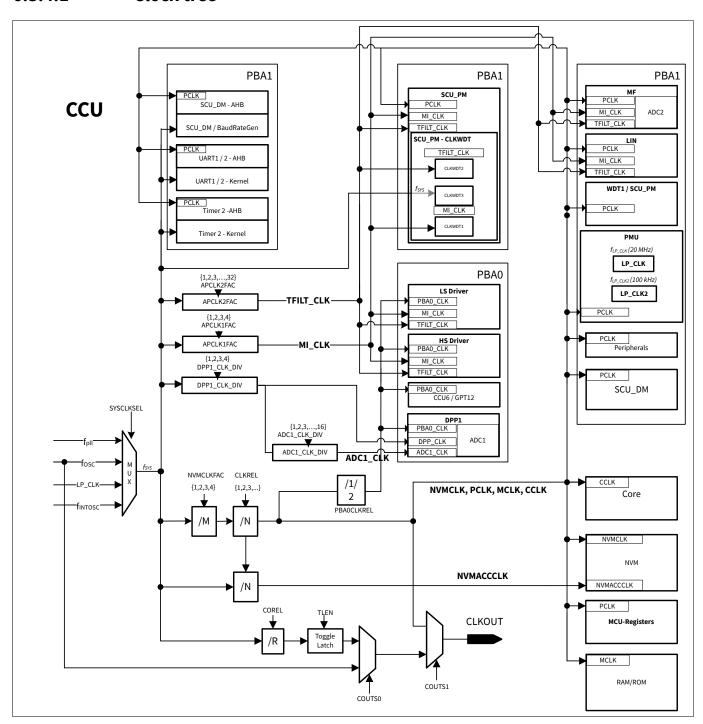

| 6.3     | Clock generation unit                                                          | 111 |

| 6.3.1   | Low precision clock                                                            | 112 |

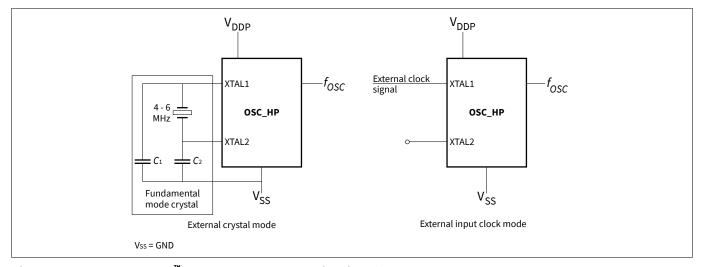

| 6.3.2   | High precision oscillator circuit (OSC_HP)                                     | 112 |

| 6.3.2.1 | External input clock mode                                                      | 112 |

| 6.3.2.2 | External crystal mode                                                          | 112 |

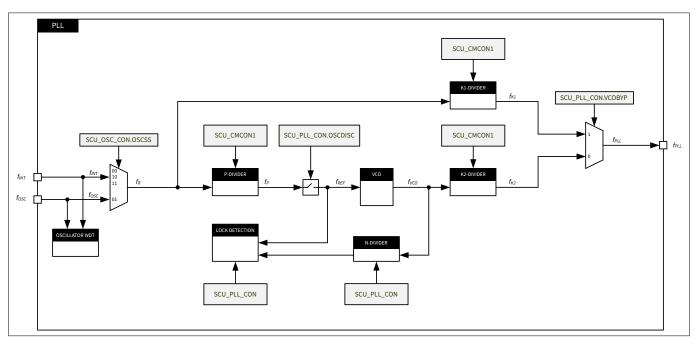

| 6.3.3   | Phase-locked loop (PLL) module                                                 | 113 |

| 6.3.3.1 | Features                                                                       | 113 |

| 6.3.3.2 | PLL functional description                                                     | 113 |

| 6.3.3.3 | Oscillator watchdog                                                            | 118 |

| 6.3.3.4 | PLL VCO lock detection                                                         | 118 |

| 6.3.3.5 | Internal oscillator (OSC_PLL)                                                  | 119 |

| 6.3.3.6 | Switching PLL parameters                                                       | 119 |

| 6.3.3.7 | Oscillator watchdog event or PLL loss of lock detection                        | 119 |

| 6.3.3.8 | Oscillator watchdog event or loss of lock recovery                             | 120 |

| 6.3.4   | Clock control unit                                                             | 121 |

| 6.3.4.1 | Clock tree                                                                     | 123 |

| 6.3.4.2 | Startup control for system clock                                               | 124 |

| 6.3.5   | External clock output                                                          | 124 |

| 6.3.6   | Clock generation unit (CGU) registers                                          | 125 |

| 6.3.6.1 | Register overview - Clock generation unit registers (ascending offset address) | 125 |

| 6.3.6.2 | PLL oscillator register                                                        | 125 |

| 6.3.6.3 | PLL registers                                                                  | 125 |

| 6.3.6.4 | System clock control registers                                                 | 125 |

| 6.3.6.5 | Analog peripherals clock control registers                                     | 126 |

| 6.3.6.6 | External clock control register                                                | 126 |

| 6.4     | Reset control                                                                  | 127 |

| 6.4.1   | Types of reset                                                                 | 127 |

## Microcontroller with LIN and power switches for automotive applications

| 6.4.2     | Overview                                                                              | 127 |

|-----------|---------------------------------------------------------------------------------------|-----|

| 6.4.3     | Module reset behavior                                                                 | 128 |

| 6.4.4     | Functional description of reset types                                                 | 129 |

| 6.4.4.1   | Power-on/brown-out reset                                                              | 129 |

| 6.4.4.2   | Wake-up reset                                                                         | 129 |

| 6.4.4.3   | Hardware reset                                                                        | 129 |

| 6.4.4.4   | WDT1 reset                                                                            | 129 |

| 6.4.4.5   | Soft reset                                                                            | 129 |

| 6.4.5     | Reset control registers                                                               | 130 |

| 6.4.5.1   | Register overview - Reset control registers (ascending offset address)                | 130 |

| 6.4.6     | Booting scheme                                                                        | 130 |

| 6.5       | Power management                                                                      | 131 |

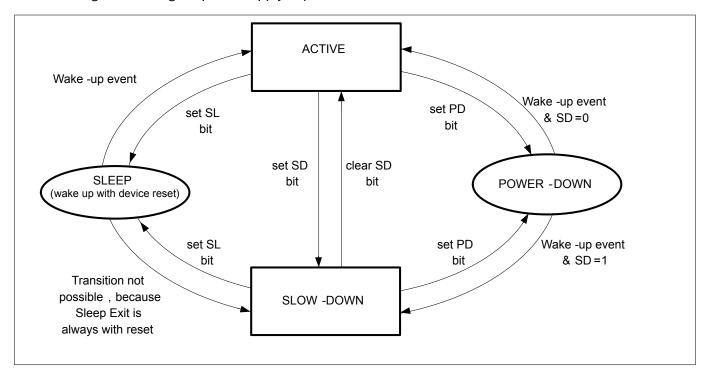

| 6.5.1     | Overview                                                                              | 131 |

| 6.5.2     | Functional description                                                                | 132 |

| 6.5.2.1   | Slow down mode                                                                        | 132 |

| 6.5.2.2   | Stop mode                                                                             | 132 |

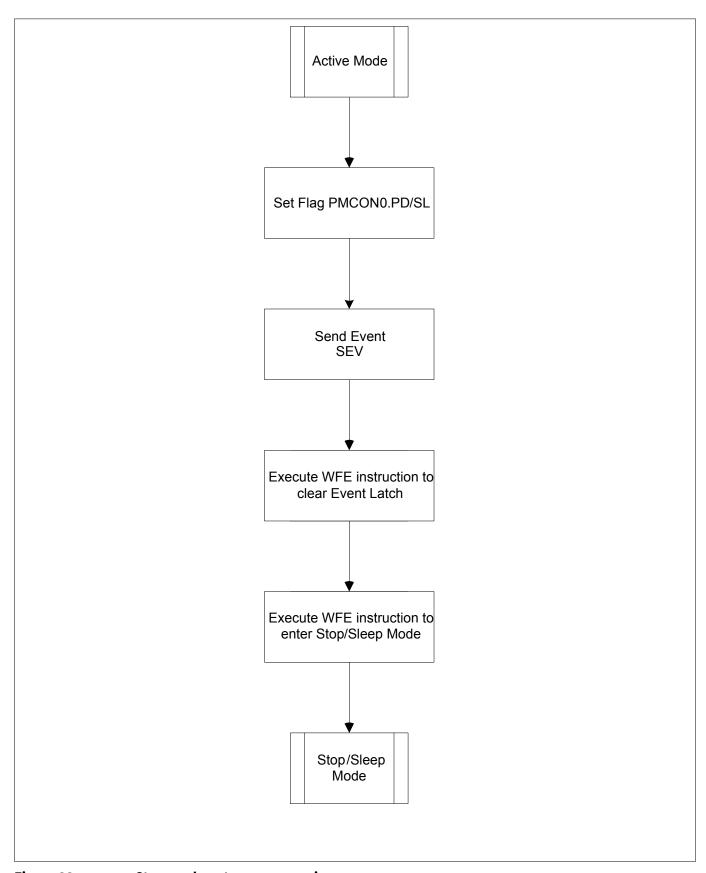

| 6.5.2.2.1 | Usage of Arm <sup>®</sup> core low power modes for stop and sleep mode                | 134 |

| 6.5.2.3   | Sleep mode                                                                            | 134 |

| 6.5.3     | Power management registers                                                            | 135 |

| 6.5.3.1   | Register overview - Power management registers (ascending offset address)             | 135 |

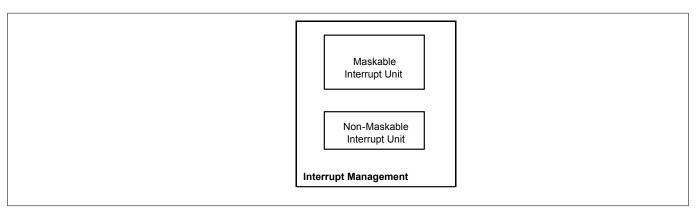

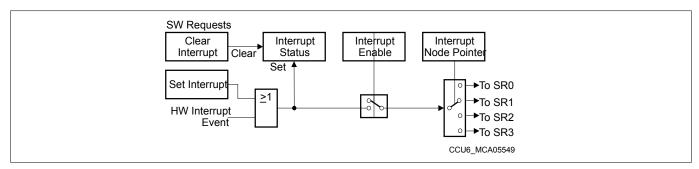

| 6.6       | Interrupt management                                                                  | 136 |

| 6.6.1     | Overview                                                                              | 136 |

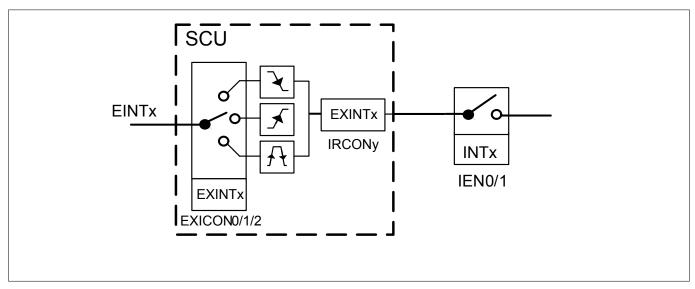

| 6.6.1.1   | External interrupts                                                                   | 136 |

| 6.6.1.2   | Extended interrupts                                                                   | 137 |

| 6.6.2     | Interrupt node assignment                                                             | 137 |

| 6.6.3     | Interrupt management registers                                                        | 139 |

| 6.6.3.1   | Register overview - Interrupt management registers (ascending offset address)         | 139 |

| 6.6.3.2   | Interrupt node enable registers                                                       | 140 |

| 6.6.3.3   | External interrupt control registers                                                  | 140 |

| 6.6.3.4   | Interrupt flag registers                                                              | 140 |

| 6.6.3.5   | Interrupt related registers                                                           | 140 |

| 6.6.4     | NMI event flags handling                                                              | 140 |

| 6.7       | General port control                                                                  | 141 |

| 6.7.1     | General port control registers                                                        | 141 |

| 6.7.1.1   | Register overview - General port control registers (ascending offset address)         | 141 |

| 6.7.1.2   | Input pin function selection registers                                                | 141 |

| 6.7.1.3   | Port output control registers                                                         | 141 |

| 6.7.1.4   | GPT12 T3IN/T4IN input pin function selection registers                                |     |

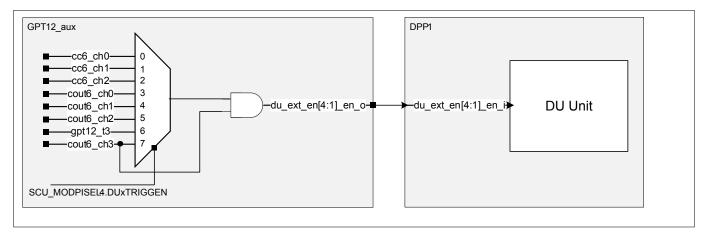

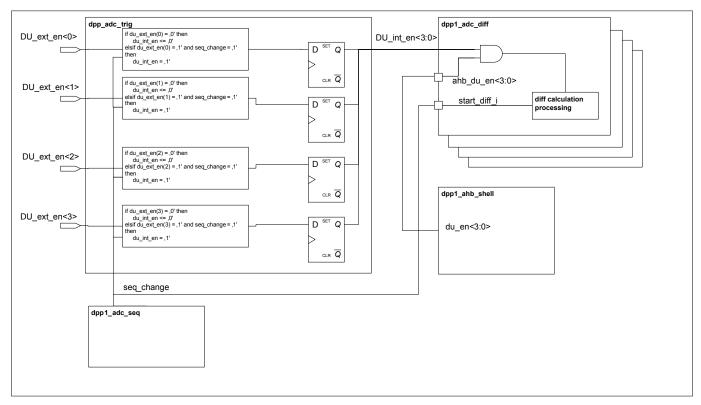

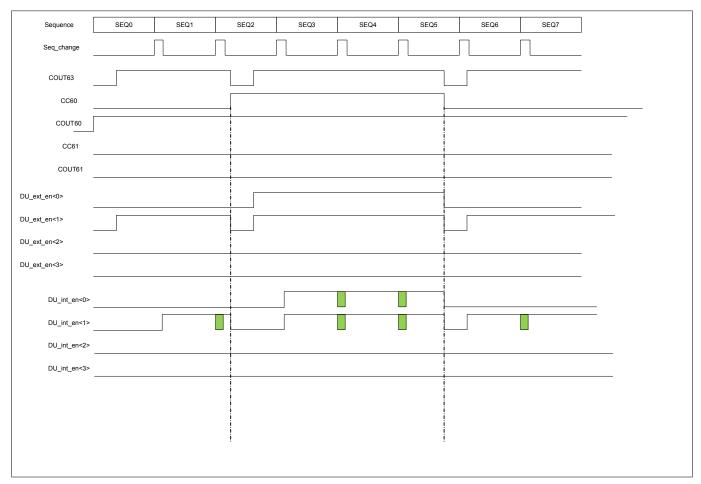

| 6.8       | Differential unit trigger enable (only TLE9845QX)                                     |     |

| 6.8.1     | Differential unit trigger register                                                    |     |

| 6.8.1.1   | Register overview - Differential unit trigger registers for TLE9845QX only (ascending |     |

|           | offset address)                                                                       | 142 |

## Microcontroller with LIN and power switches for automotive applications

### **Table of contents**

| 6.9      | Flexible peripheral management                                                       | 143      |

|----------|--------------------------------------------------------------------------------------|----------|

| 6.9.1    | Peripheral management registers                                                      | 143      |

| 6.9.1.1  | Register overview - Flexible peripheral management registers (ascending offset addre | ss) .143 |

| 6.10     | Module suspend control                                                               |          |

| 6.10.1   | Module suspend control registers                                                     | 144      |

| 6.10.1.1 | Register overview - Module suspend control registers (ascending offset address)      | 144      |

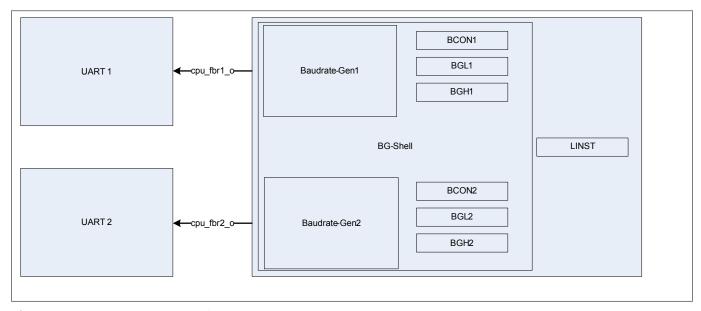

| 6.11     | Baud-rate generator                                                                  | 145      |

| 6.11.1   | Baud-rate generator registers                                                        | 145      |

| 6.11.1.1 | Register overview - Baud-rate generator registers (ascending offset address)         | 145      |

| 6.11.1.2 | Baud-rate generator control and status registers                                     | 145      |

| 6.11.1.3 | Baud-rate generator timer/reload registers                                           | 145      |

| 6.12     | LIN break and sync byte detection                                                    | 146      |

| 6.12.1   | LIN break and sync byte detection control registers                                  | 146      |

| 6.12.1.1 | Register overview - LIN break and sync byte registers (ascending offset address)     |          |

| 6.13     | Error detection and correction control for memories                                  |          |

| 6.13.1   | Error detection and correction control for memories registers                        |          |

| 6.13.1.1 | Register overview - Error detection and correction control for memories registers    |          |

|          | (ascending offset address)                                                           | 147      |

| 6.13.1.2 | Error detection and correction control register                                      |          |

| 6.13.1.3 | Error detection and correction status register                                       |          |

| 6.14     | Miscellaneous control                                                                |          |

| 6.14.1   | Miscellaneous control registers                                                      |          |

| 6.14.1.1 | Register overview - Miscellaneous control registers (ascending offset address)       |          |

| 6.14.1.2 | Bit protection register                                                              |          |

| 6.14.1.3 | System control and status registers                                                  |          |

| 6.15     | System control unit - digital modules (SCU) register definition                      |          |

| 6.15.1   | Register address space - SCUDM                                                       |          |

| 6.15.2   | Register overview - SCUDM (ascending offset address)                                 |          |

| 6.15.3   | Register overview - UART1/2 control/status registers                                 |          |

| 6.15.4   | PLL control register                                                                 |          |

| 6.15.5   | Clock control 1 register                                                             |          |

| 6.15.6   | Clock control 2 register                                                             |          |

| 6.15.7   | Analog peripheral clock control register                                             |          |

| 6.15.8   | Analog peripheral clock register                                                     |          |

| 6.15.9   | Analog peripheral clock status register                                              |          |

| 6.15.10  | Analog peripheral clock status clear register                                        |          |

| 6.15.11  | ADC1 peripheral clock register                                                       |          |

| 6.15.12  | System control 0 register                                                            |          |

| 6.15.13  | OSC control register                                                                 |          |

| 6.15.14  | Clock output control register                                                        |          |

| 6.15.15  | Reset control register                                                               |          |

| 6.15.16  | Power mode control 0 register                                                        |          |

|          | ♥                                                                                    |          |

6

# $\textbf{MOTIX}^{^{\text{TM}}}\textbf{TLE984xQX}$

## Microcontroller with LIN and power switches for automotive applications

| 6.15.17 | NMI status clear register                          | 173 |

|---------|----------------------------------------------------|-----|

| 6.15.18 | Interrupt request 0 register                       | 175 |

| 6.15.19 | Interrupt request 1 register                       | 176 |

| 6.15.20 | Interrupt request 2 register                       | 178 |

| 6.15.21 | Interrupt request 3 register                       | 179 |

| 6.15.22 | Interrupt request 4 register                       | 180 |

| 6.15.23 | NMI status register                                | 181 |

| 6.15.24 | Interrupt enable 0 register                        | 183 |

| 6.15.25 | Vector table reallocation register                 | 184 |

| 6.15.26 | NMI control register                               | 185 |

| 6.15.27 | External interrupt control 0 register              | 186 |

| 6.15.28 | External interrupt control 1 register              |     |

| 6.15.29 | Peripheral interrupt enable 1 register             | 188 |

| 6.15.30 | Peripheral interrupt enable 2 register             | 189 |

| 6.15.31 | Peripheral interrupt enable 3 register             | 190 |

| 6.15.32 | Peripheral interrupt enable 4 register             | 191 |

| 6.15.33 | Wake-up interrupt control register                 |     |

| 6.15.34 | Interrupt request 5 register                       | 193 |

| 6.15.35 | General purpose timer 12 interrupt enable register |     |

| 6.15.36 | Timer and counter control/status register          | 195 |

| 6.15.37 | Interrupt request 0 clear register                 | 196 |

| 6.15.38 | Interrupt request 1 clear register                 | 197 |

| 6.15.39 | Timer and counter control/status clear register    | 199 |

| 6.15.40 | Monitoring input interrupt enable register         | 200 |

| 6.15.41 | Interrupt request 2 clear register                 | 201 |

| 6.15.42 | Interrupt request 3 clear register                 | 202 |

| 6.15.43 | Interrupt request 4 clear register                 | 203 |

| 6.15.44 | Interrupt request 5 clear register                 | 204 |

| 6.15.45 | Peripheral input select register                   | 205 |

| 6.15.46 | Peripheral input select 1 register                 | 207 |

| 6.15.47 | Peripheral input select 2 register                 | 208 |

| 6.15.48 | Peripheral input select 3 register                 | 209 |

| 6.15.49 | GPT12 peripheral input select register             | 210 |

| 6.15.50 | Port output control register                       | 211 |

| 6.15.51 | Temperature compensation control register          | 213 |

| 6.15.52 | Port output control register                       | 214 |

| 6.15.53 | Peripheral input select 4 register                 | 216 |

| 6.15.54 | Peripheral management control register             | 218 |

| 6.15.55 | Module suspend control register                    |     |

| 6.15.56 | Baud-rate control 1 register                       |     |

| 6.15.57 | Baud-rate timer/reload, low byte 1 register        |     |

| 6.15.58 | Baud-rate timer/reload 1 register                  |     |

## Microcontroller with LIN and power switches for automotive applications

| 6.15.59 | Baud-rate control 2 register                                                         | 224 |

|---------|--------------------------------------------------------------------------------------|-----|

| 6.15.60 | Baud-rate timer/reload, low byte 2 register                                          | 225 |

| 6.15.61 | Baud-rate timer/reload 2 register                                                    | 226 |

| 6.15.62 | LIN status register                                                                  | 227 |

| 6.15.63 | LIN status clear register                                                            | 228 |

| 6.15.64 | Error detection and correction control register                                      | 229 |

| 6.15.65 | Error detection and correction status register                                       | 230 |

| 6.15.66 | Error detection and correction status clear register                                 | 231 |

| 6.15.67 | System startup status register                                                       | 232 |

| 6.15.68 | Identity register                                                                    | 234 |

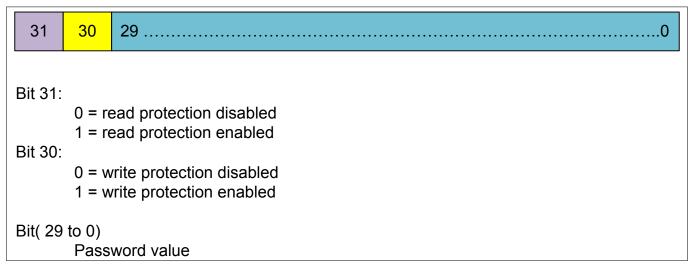

| 6.15.69 | Password register                                                                    | 235 |

| 6.15.70 | Emergency and program operation status register                                      | 236 |

| 6.15.71 | Memory status register                                                               | 237 |

| 6.15.72 | NVM protection status register                                                       | 238 |

| 6.15.73 | Memory access status register                                                        | 240 |

| 6.15.74 | UART1 control/status register                                                        | 241 |

| 6.15.75 | UART2 control/status register                                                        | 242 |

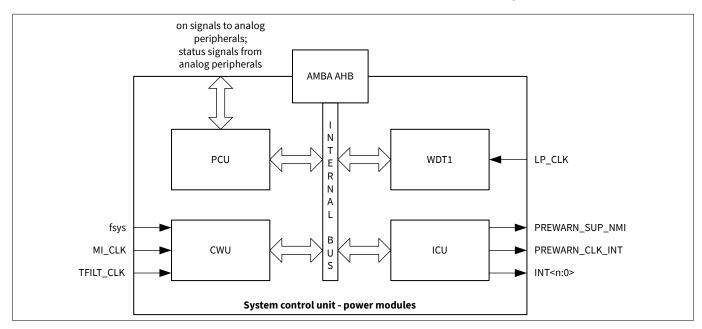

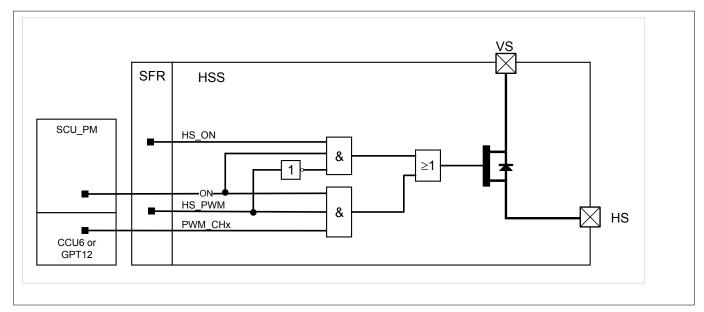

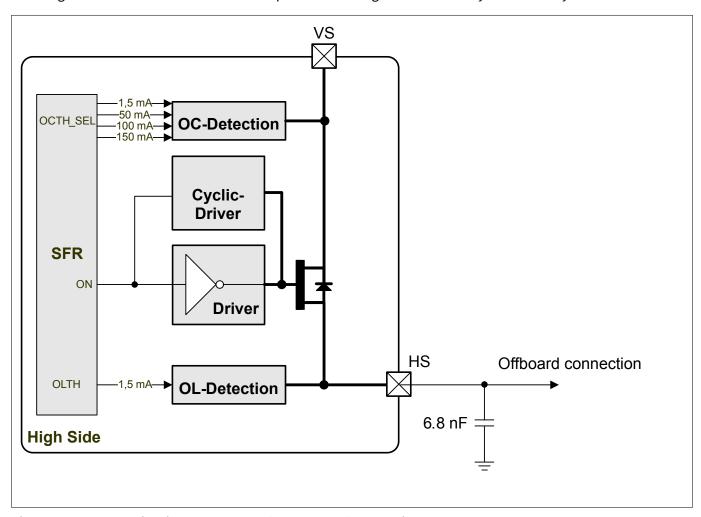

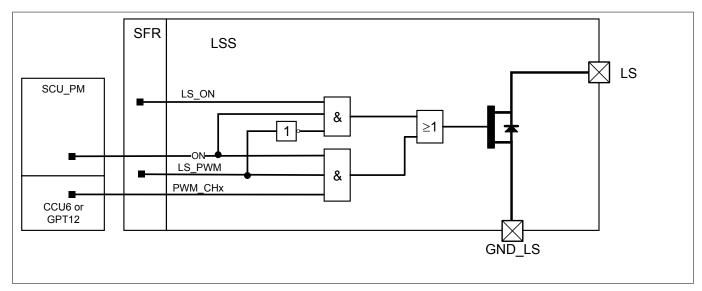

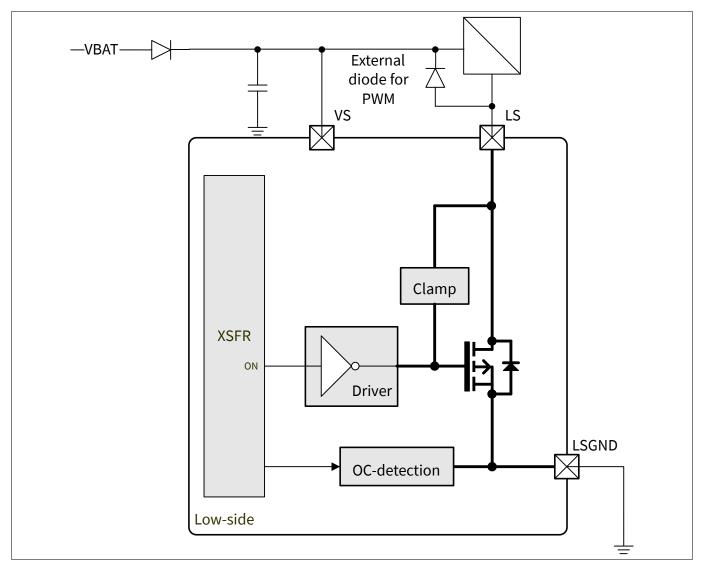

| 7       | System control unit - power modules (SCU-PM)                                         | 243 |

| 7.1     | Description of the power modules system control unit                                 | 243 |

| 7.2     | Introduction                                                                         | 243 |

| 7.2.1   | Block diagram                                                                        | 243 |

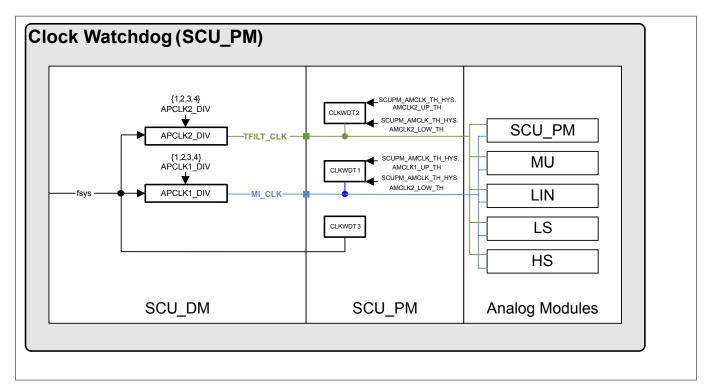

| 7.3     | Clock watchdog unit (CWU)                                                            | 244 |

| 7.3.1   | Fail safe functionality of clock generation unit (clock watchdog)                    | 244 |

| 7.3.1.1 | Functional description of clock watchdog module                                      | 245 |

| 7.3.2   | Clock generation unit registers                                                      | 245 |

| 7.3.2.1 | Register overview - Clock Watchdog Unit registers (ascending offset address)         | 245 |

| 7.4     | Interrupt control unit (ICU)                                                         | 246 |

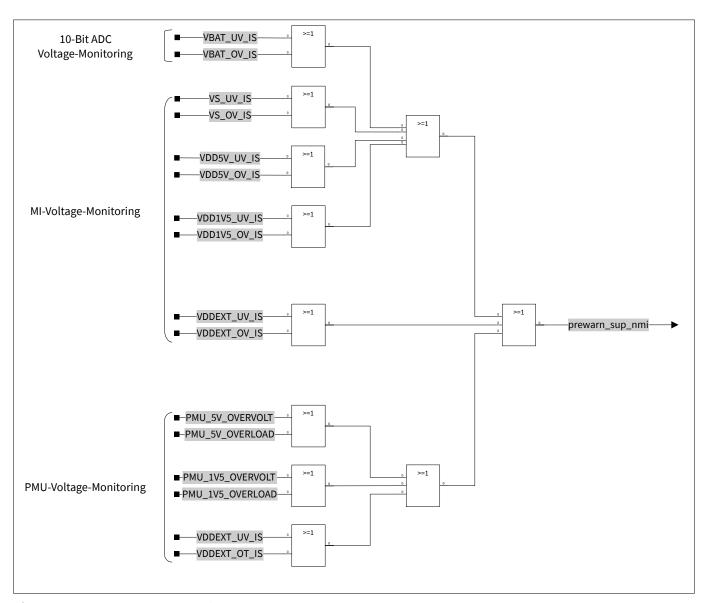

| 7.4.1   | Structure of PREWARN_SUP_NMI                                                         | 246 |

| 7.4.2   | Interrupt control unit status registers                                              | 248 |

| 7.4.2.1 | Register overview - Interrupt Control Unit registers (ascending offset address)      | 248 |

| 7.4.2.2 | Interrupt control unit status overview registers                                     | 248 |

| 7.4.2.3 | Interrupt control unit - interrupt clear registers                                   | 248 |

| 7.4.2.4 | Interrupt control unit - interrupt enable registers                                  | 248 |

| 7.5     | Power control unit for power modules (PCU_PM)                                        | 249 |

| 7.5.1   | Overtemperature system shutdown                                                      |     |

| 7.5.2   | Power control unit registers                                                         | 251 |

| 7.5.2.1 | Register overview - Power Control Unit for Power Modules registers (ascending offset |     |

|         | address)                                                                             | 251 |

| 7.6     | System control unit - power modules (SCUPM) register definition                      | 252 |

| 7.6.1   | Register address space - SCUPM                                                       | 252 |

| 7.6.2   | Register overview - SCUPM (ascending offset address)                                 | 252 |

## Microcontroller with LIN and power switches for automotive applications

| 7.6.3    | Analog module clock frequency status register      | 253 |

|----------|----------------------------------------------------|-----|

| 7.6.4    | Analog module clock control register               | 254 |

| 7.6.5    | Analog module clock limit register                 | 255 |

| 7.6.6    | System tick calibration register                   | 256 |

| 7.6.7    | System interrupt status clear register             | 257 |

| 7.6.8    | System interrupt status register                   | 258 |

| 7.6.9    | System supply interrupt status register            | 261 |

| 7.6.10   | System supply interrupt control register           | 263 |

| 7.6.11   | System supply interrupt status clear register      | 265 |

| 7.6.12   | System interrupt control register                  | 267 |

| 7.6.13   | Power control unit control status register         | 268 |

| 7.6.14   | WDT1 watchdog control register                     | 269 |

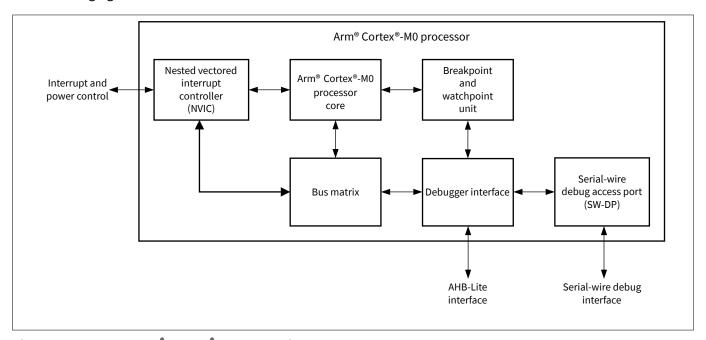

| 8        | Arm <sup>®</sup> Cortex <sup>®</sup> -M0 core      | 270 |

| 3.1      | Features                                           |     |

| 3.2      | Introduction                                       | 271 |

| 3.2.1    | Block diagram                                      | 271 |

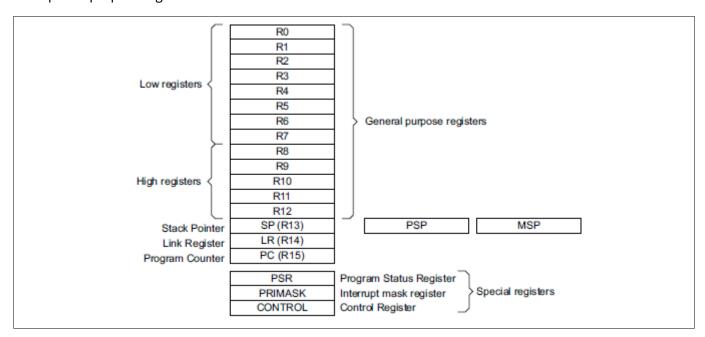

| 3.3      | Functional description                             | 272 |

| 3.3.1    | Processor registers                                |     |

| 3.3.1.1  | General-purpose registers                          |     |

| 3.3.1.2  | Special-purpose registers                          |     |

| 3.3.2    | Processor (CPU) register definition                |     |

| 3.3.2.1  | Register address space - CPU                       | 274 |

| 3.3.2.2  | Register overview - CPU (ascending offset address) | 274 |

| 3.3.2.3  | SysTick control and status register                |     |

| 3.3.2.4  | SysTick reload value register                      | 276 |

| 3.3.2.5  | SysTick current value register                     | 277 |

| 8.3.2.6  | SysTick calibration value register                 | 278 |

| 8.3.2.7  | Interrupt set-enable register                      | 279 |

| 3.3.2.8  | Interrupt clear-enable register                    | 282 |

| 3.3.2.9  | Interrupt set-pending register                     | 285 |

| 3.3.2.10 | Interrupt clear-pending register                   | 288 |

| 3.3.2.11 | Interrupt priority 0 register                      | 291 |

| 3.3.2.12 | Interrupt priority 1 register                      | 292 |

| 8.3.2.13 | Interrupt priority 2 register                      | 293 |

| 3.3.2.14 | Interrupt priority 3 register                      | 294 |

| 8.3.2.15 | Interrupt priority 4 register                      | 295 |

| 3.3.2.16 | Interrupt priority 5 register                      | 296 |

| 8.3.2.17 | CPU ID base register                               | 297 |

| 3.3.2.18 | Interrupt control and state register               | 298 |

| 3.3.2.19 | Application interrupt/reset control register       | 300 |

| 3.3.2.20 | System control register                            | 301 |

## Microcontroller with LIN and power switches for automotive applications

| 3.3.2.21   | Configuration control register      | 302 |

|------------|-------------------------------------|-----|

| 3.3.2.22   | System handler priority 2 register  | 303 |

| 3.3.2.23   | System handler priority 3 register  | 304 |

| 3.4        | Instruction set summary             | 305 |

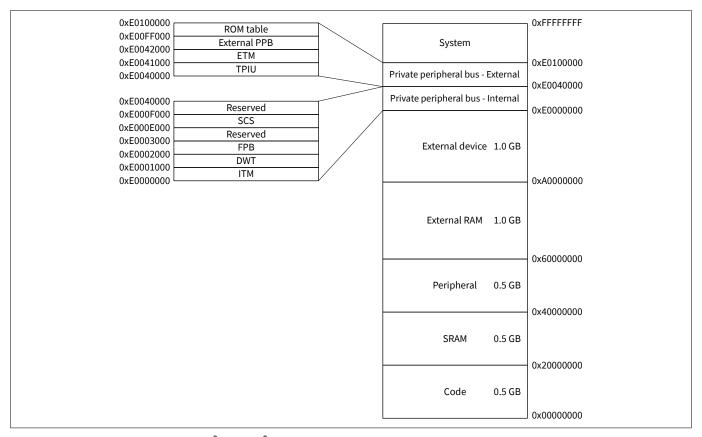

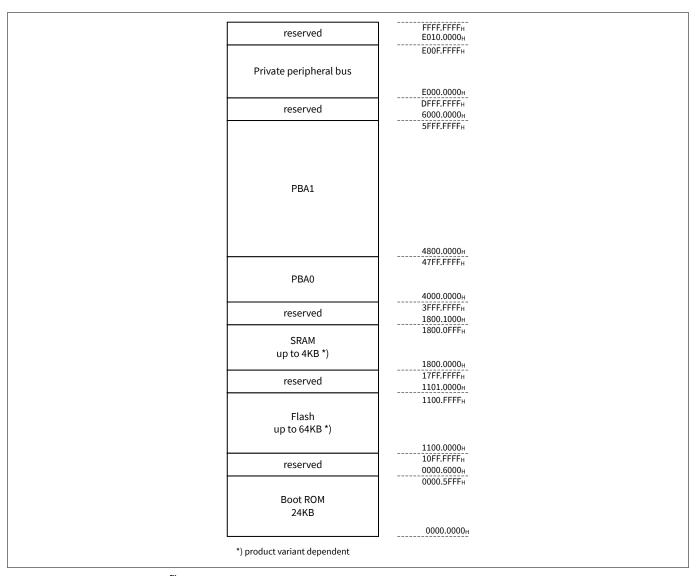

| 9          | Address space organization          | 308 |

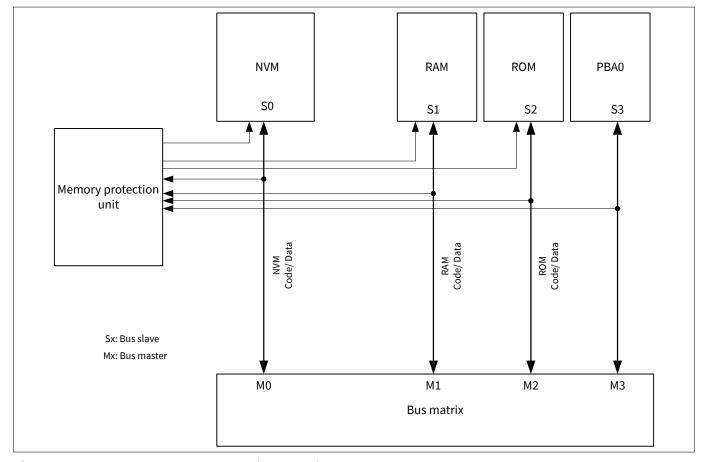

| 10         | Memory control unit                 | 312 |

| 10.1       | Features                            | 312 |

| 10.2       | Introduction                        | 312 |

| 10.2.1     | Block diagram                       | 312 |

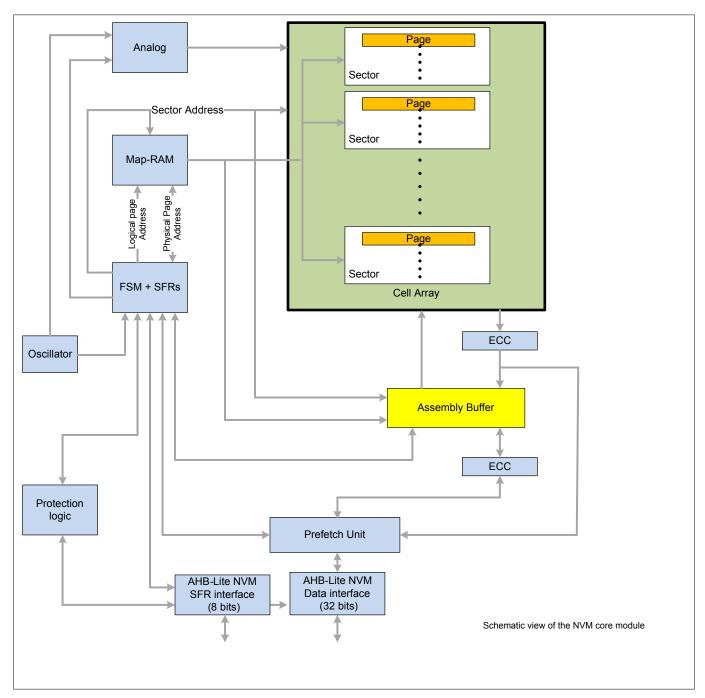

| 10.3       | NVM module (flash memory)           | 314 |

| 10.4       | BootROM module                      | 314 |

| 10.4.1     | BootROM addressing                  | 314 |

| 10.4.2     | BootROM firmware program structure  | 314 |

| 10.5       | RAM module                          | 315 |

| 10.5.1     | RAM addressing                      | 315 |

| 10.6       | Memory protection unit (MPU)        | 316 |

| 10.6.1     | Memory protection regions           | 316 |

| 10.6.2     | Hardware protection mode            | 317 |

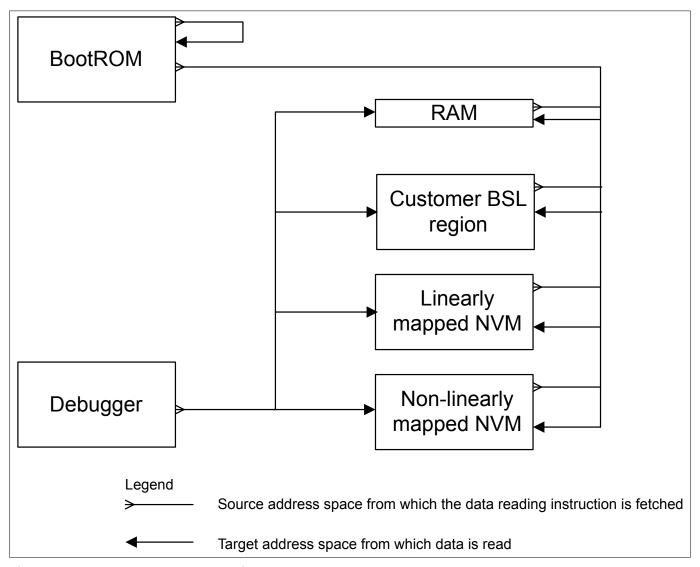

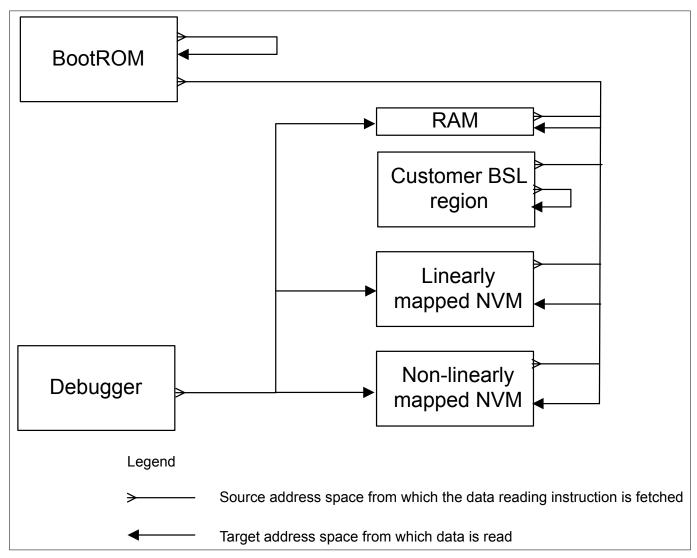

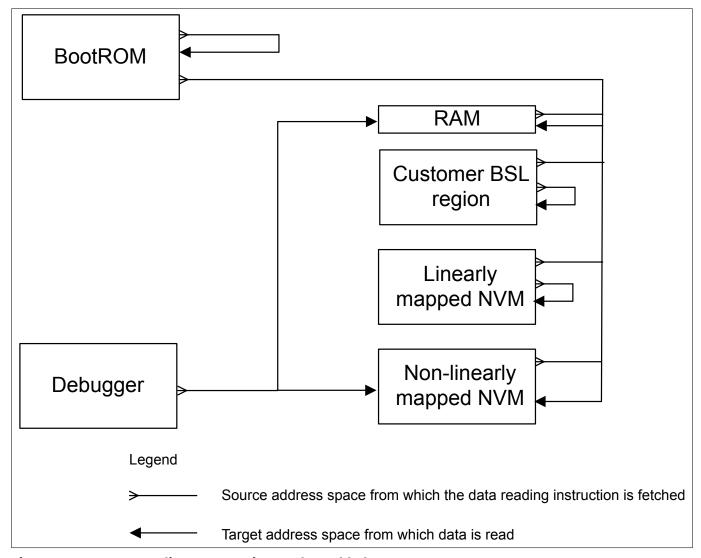

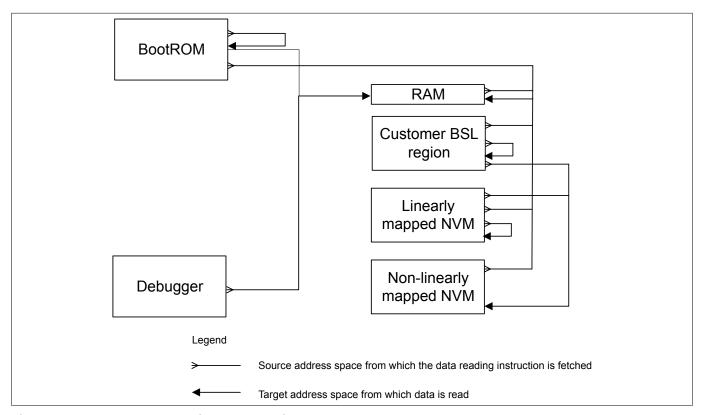

| 10.6.2.1   | BootROM protection mode             | 317 |

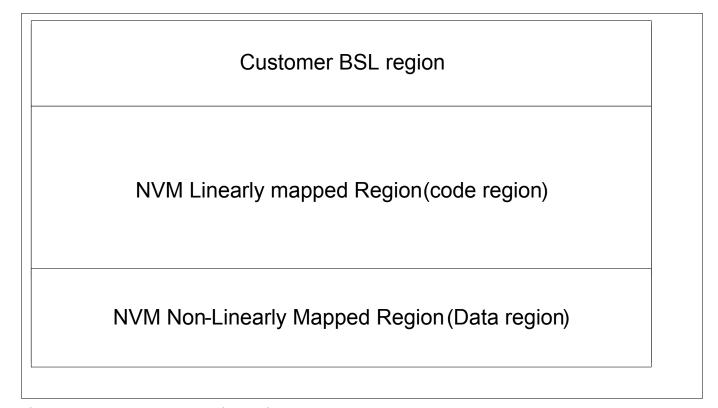

| 10.6.2.2   | NVM protection modes                | 318 |

| 10.6.2.2.1 | Customer BSL region protection mode | 319 |

| 10.6.2.2.2 | NVM linear protection mode          | 320 |

| 10.6.2.2.3 | NVM non-linear protection mode      | 322 |

| 10.6.2.2.4 | NVM protection mode control         | 323 |

| 10.6.3     | Firmware protection mode            | 324 |

| 10.7       | Core protection mode                | 325 |

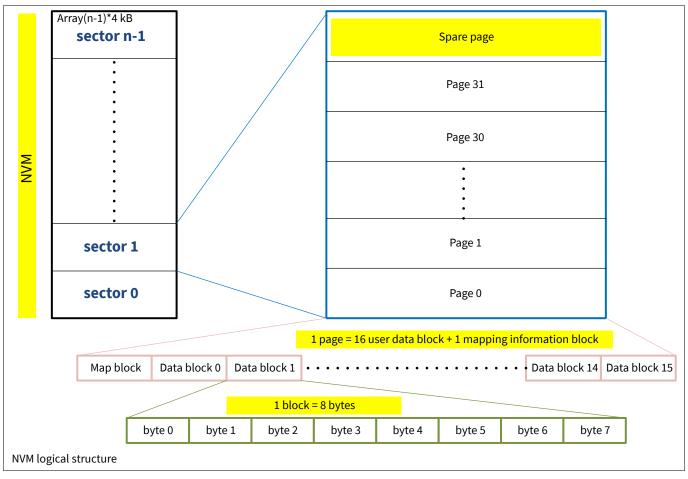

| 11         | NVM module (flash memory)           | 326 |

| 11.1       | Definitions                         | 327 |

| 11.1.1     | General definitions                 | 327 |

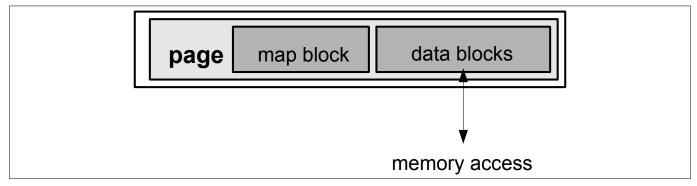

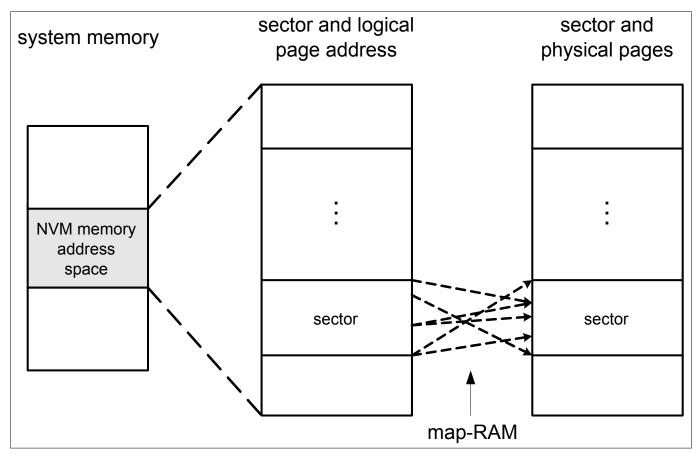

| 11.2       | Functional description              | 329 |

| 11.2.1     | Basic block functions               | 329 |

| 11.2.2     | Memory cell array                   | 330 |

| 11.2.3     | SFR accesses                        | 331 |

| 11.2.4     | Memory read                         | 331 |

| 11.2.5     | Memory write                        | 332 |

| 11.2.6     | Timing                              | 332 |

| 11.2.7     | Verify                              | 332 |

| 11.2.8     | Tearing-safe programming            | 332 |

| 11.2.9     | Dynamic address scrambling          | 333 |

| 11.2.10    | Linearly mapped sectors             | 333 |

| 11.2.11    | Disturb handling                    |     |

## Microcontroller with LIN and power switches for automotive applications

| 11.2.12   | Hot spot distribution                                                         | 334 |

|-----------|-------------------------------------------------------------------------------|-----|

| 11.2.13   | Properties of error correcting code (ECC)                                     | 334 |

| 11.2.14   | Resume from disturbed program/erase operation                                 | 334 |

| 11.2.15   | Code and data access through the AHB-Lite interface                           | 335 |

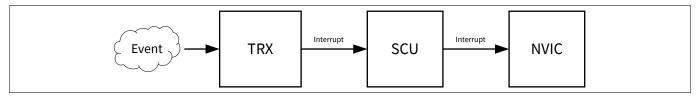

| 12        | Interrupt system                                                              | 336 |

| 12.1      | Features                                                                      | 336 |

| 12.2      | Introduction                                                                  | 336 |

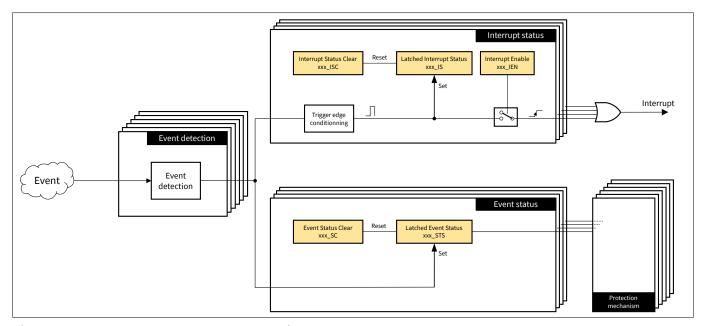

| 12.2.1    | Overview                                                                      | 336 |

| 12.3      | Functional description                                                        | 338 |

| 12.3.1    | Interrupt node assignment                                                     | 338 |

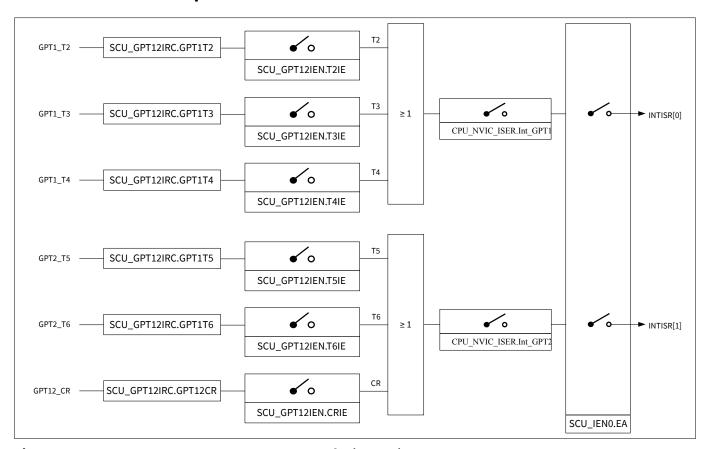

| 12.3.1.1  | Interrupt node 0 and 1 – GPT12 timer module                                   | 338 |

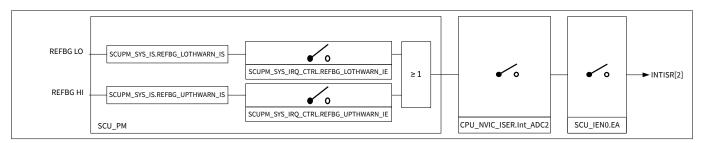

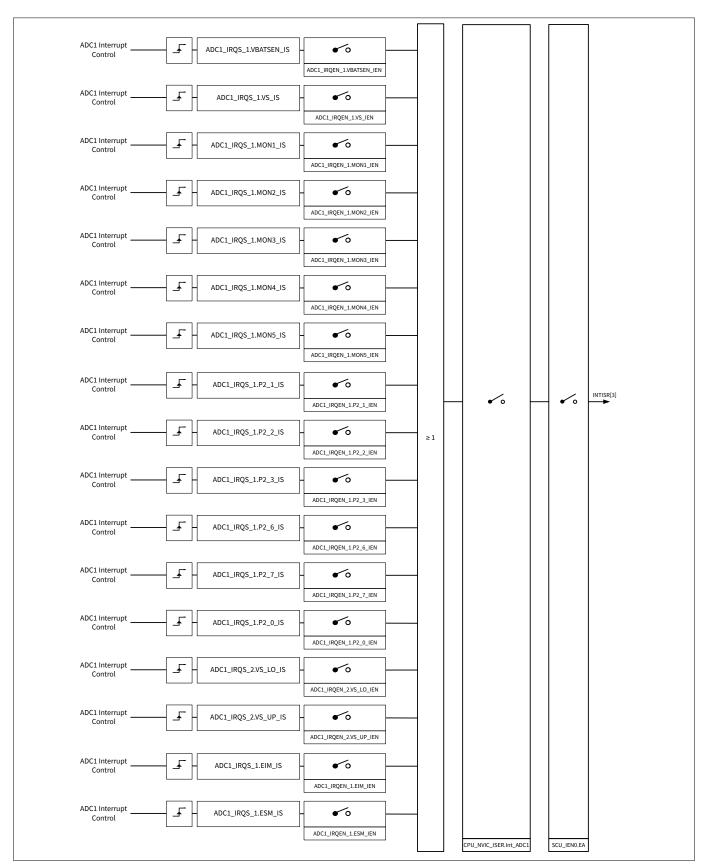

| 12.3.1.2  | Interrupt node 2 – measurement unit                                           | 339 |

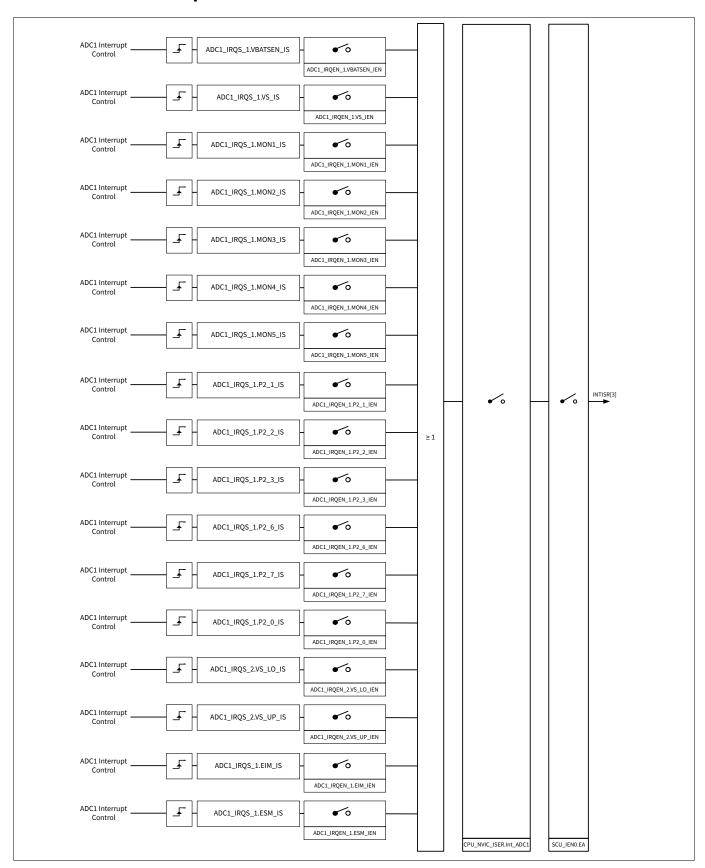

| 12.3.1.3  | Interrupt node 3 – ADC10                                                      | 340 |

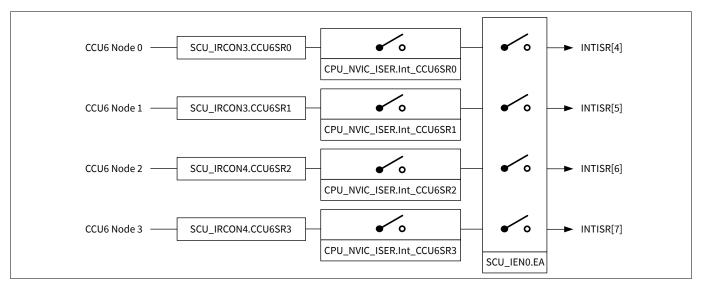

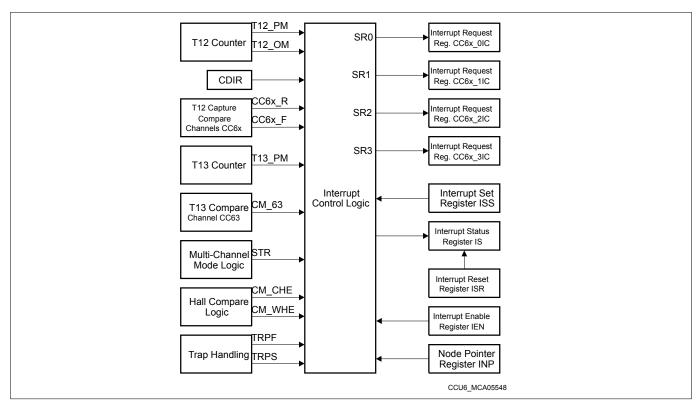

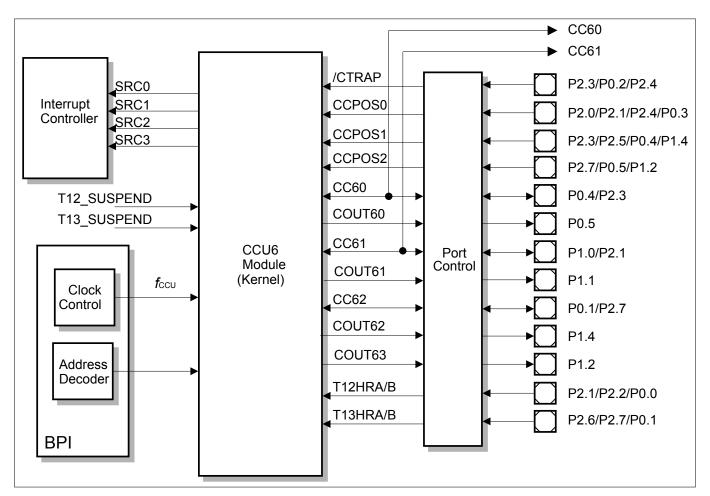

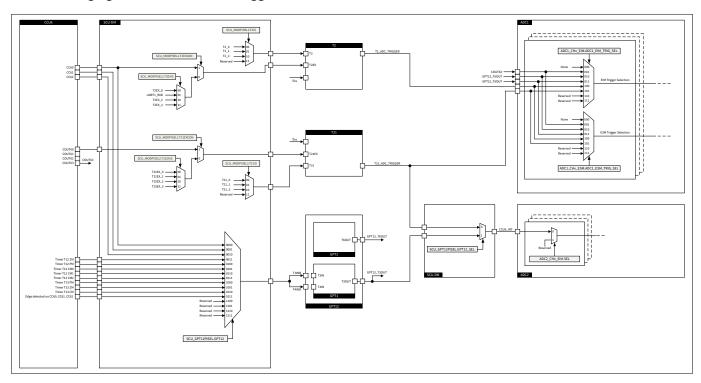

| 12.3.1.4  | Interrupt node 4, 5, 6, 7 – CCU6                                              | 341 |

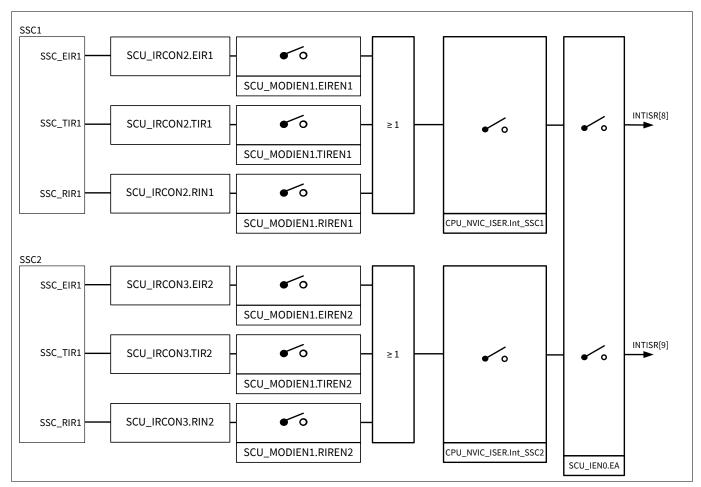

| 12.3.1.5  | Interrupt node 8 and 9 – SSC                                                  | 342 |

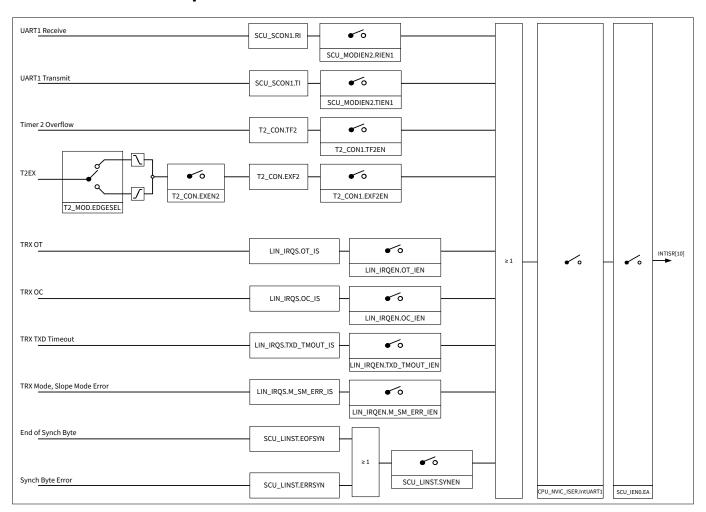

| 12.3.1.6  | Interrupt node 10 – UART1                                                     | 343 |

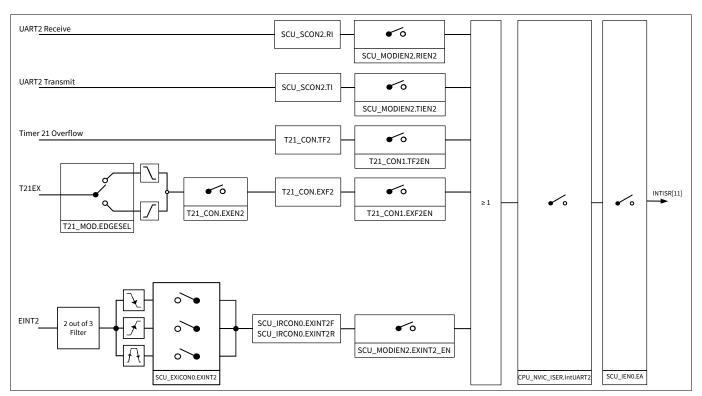

| 12.3.1.7  | Interrupt node 11 – UART2                                                     | 344 |

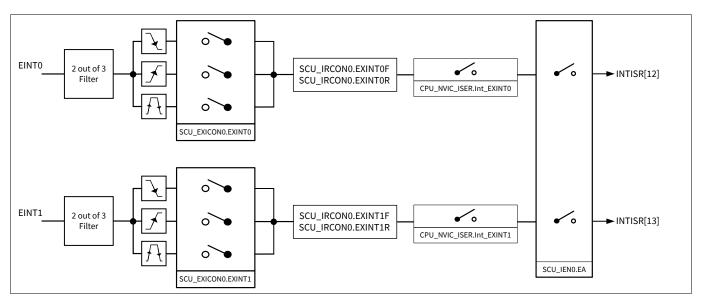

| 12.3.1.8  | Interrupt node 12 and 13 – interrupt                                          | 345 |

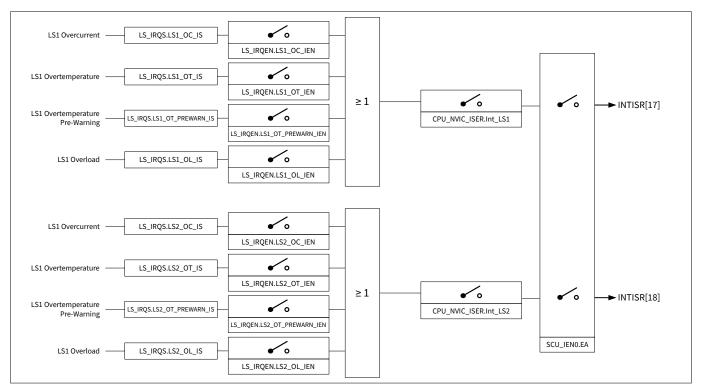

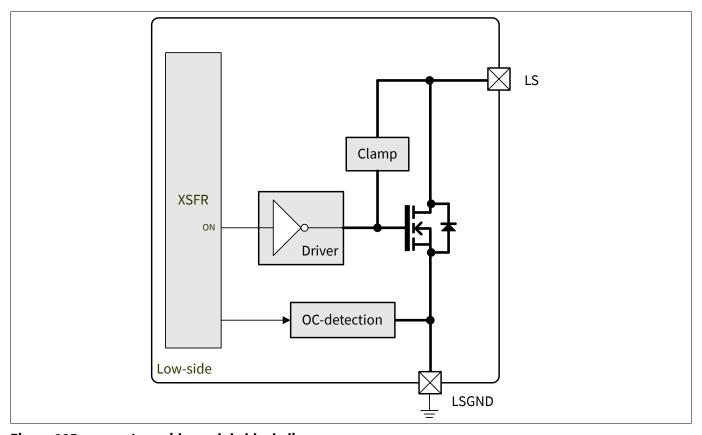

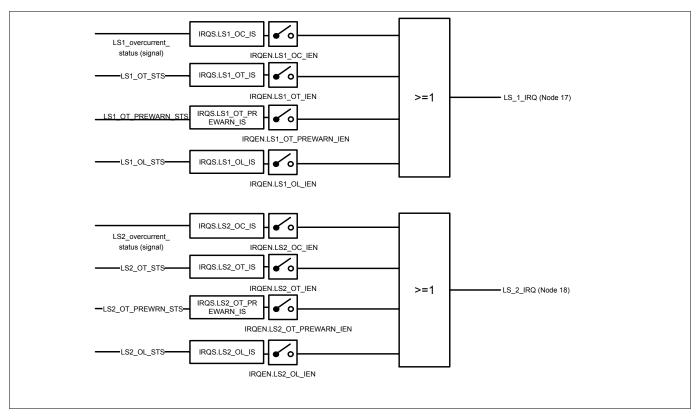

| 12.3.1.9  | Interrupt node 17 and 18 – LS1, LS2                                           | 346 |

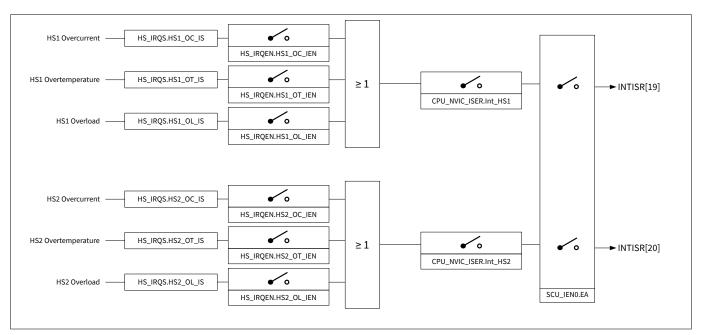

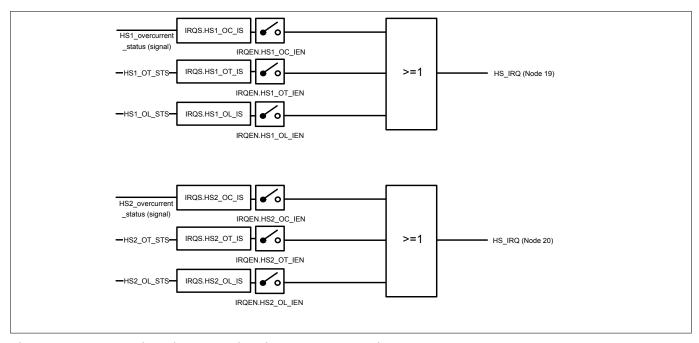

| 12.3.1.10 | Interrupt node 19 and 20 – HS1, HS2                                           | 347 |

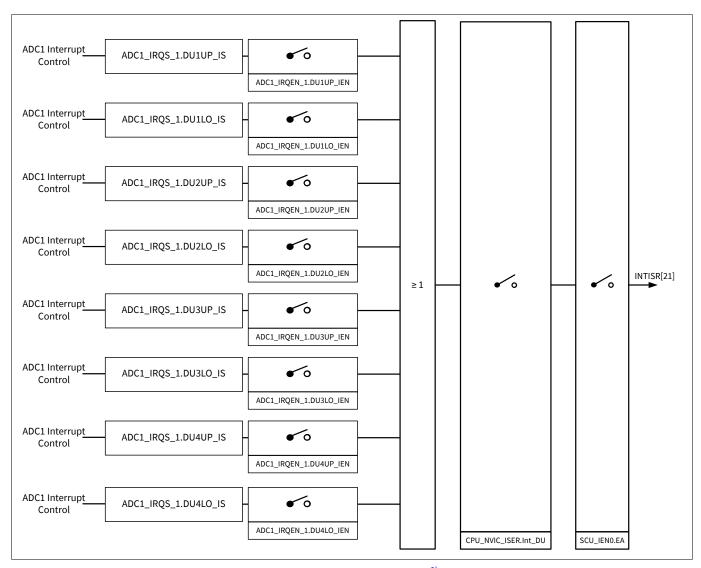

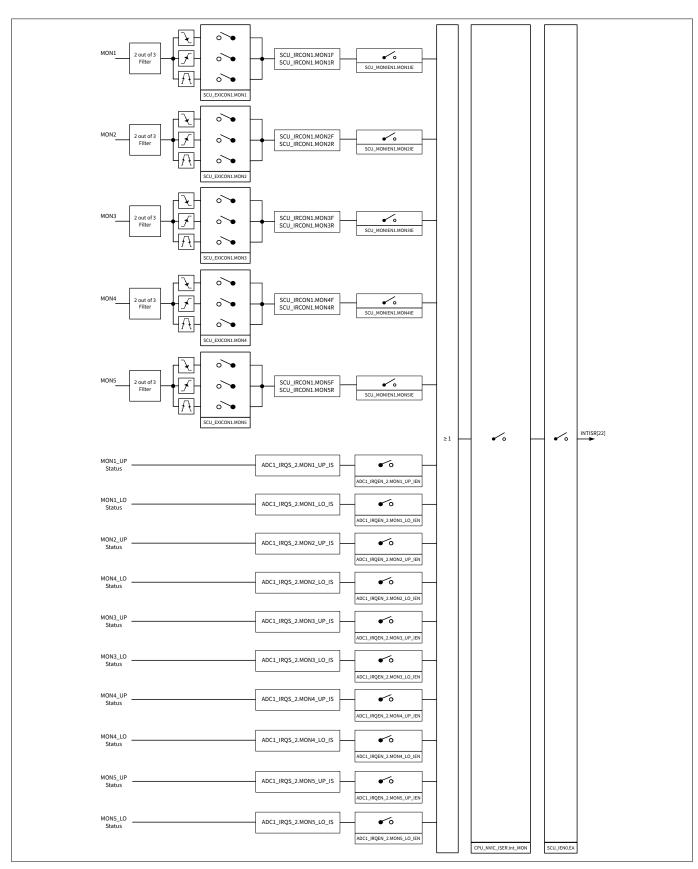

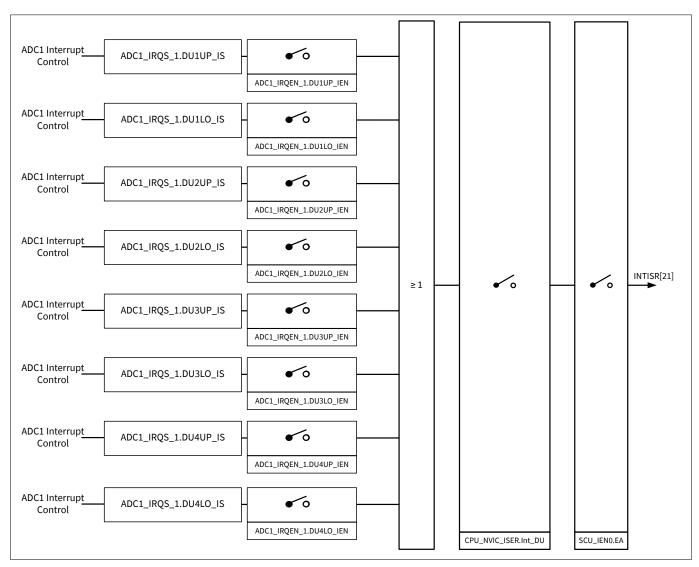

| 12.3.1.11 | Interrupt node 21 – DPP1                                                      | 348 |

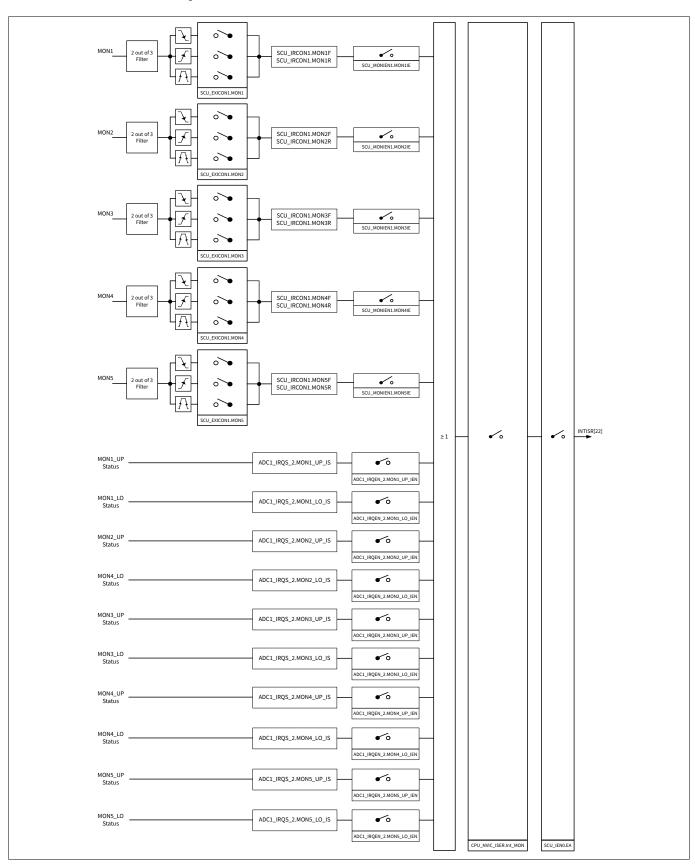

| 12.3.1.12 | Interrupt node 22 – MON15                                                     | 349 |

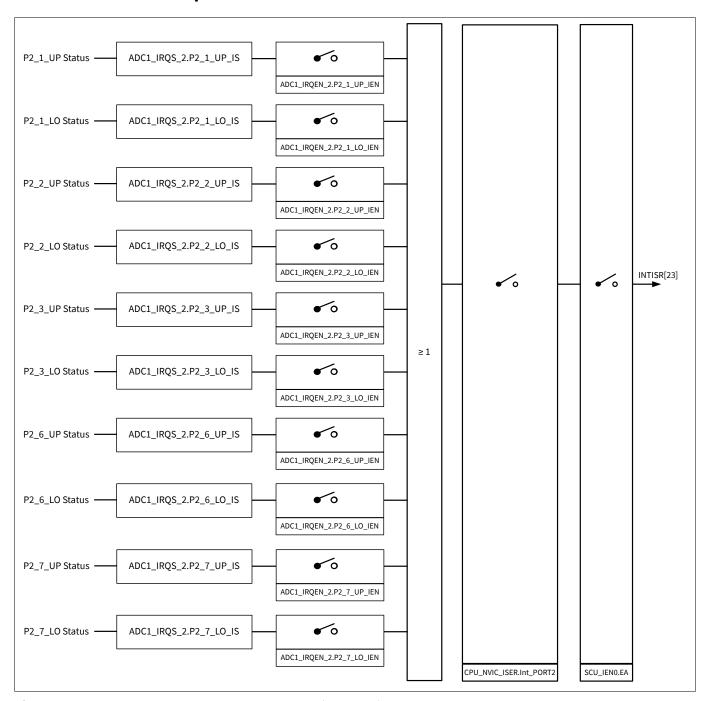

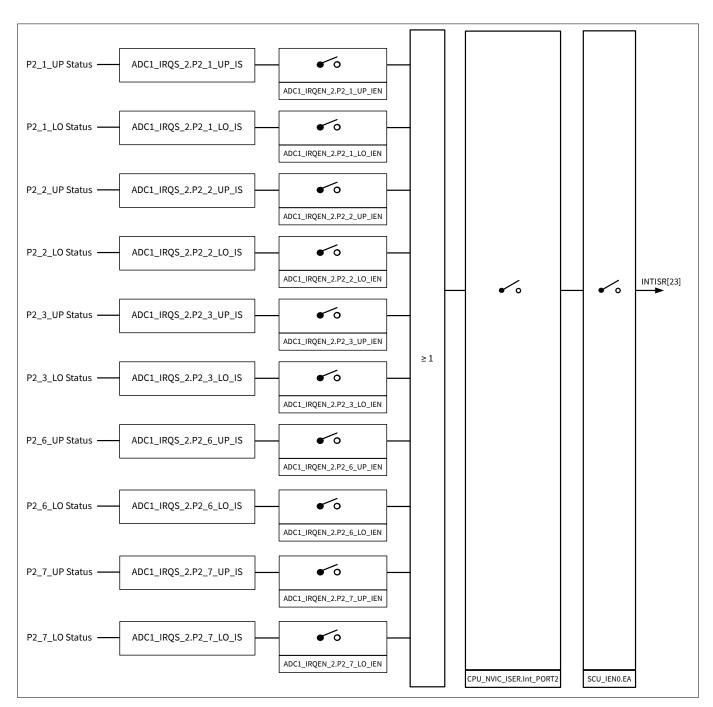

| 12.3.1.13 | Interrupt node 23 – Port2.x                                                   | 350 |

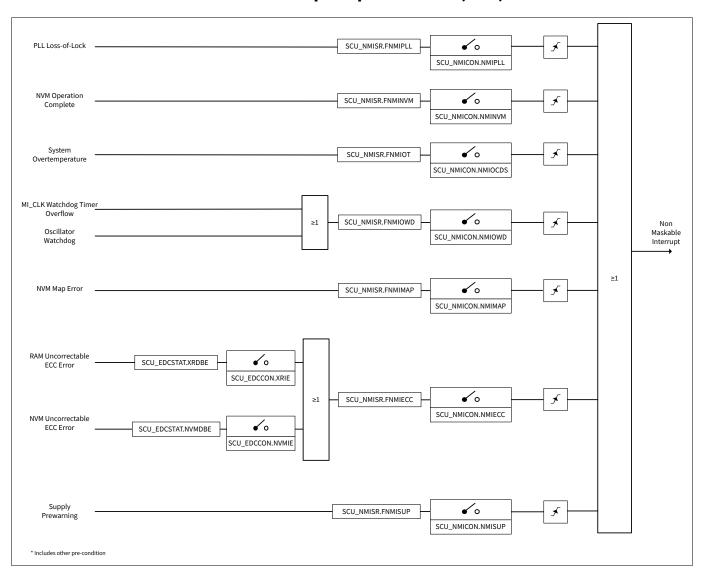

| 12.3.1.14 | Non-maskable interrupt request source (NMI)                                   | 351 |

| 12.3.1.15 | Interrupt flags overview                                                      | 352 |

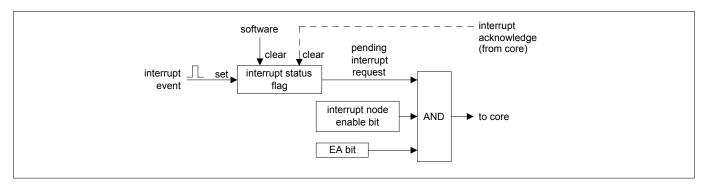

| 12.4      | Interrupt structure                                                           | 360 |

| 12.4.1    | Interrupt structure 1                                                         | 360 |

| 12.5      | Interrupt source and vector                                                   | 361 |

| 12.6      | Interrupt priority                                                            | 362 |

| 12.6.1    | Interrupt priority registers                                                  | 363 |

| 12.7      | Interrupt handling                                                            | 363 |

| 12.8      | Interrupt (SCU) registers                                                     | 364 |

| 12.8.1    | Register overview - Interrupt management registers (ascending offset address) | 364 |

| 12.8.2    | Interrupt node enable registers                                               | 365 |

| 12.8.3    | External interrupt control registers                                          | 365 |

| 12.8.4    | Interrupt flag registers                                                      | 365 |

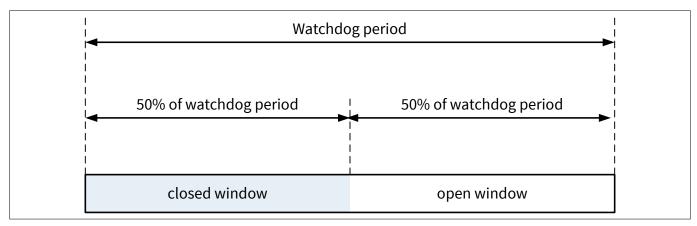

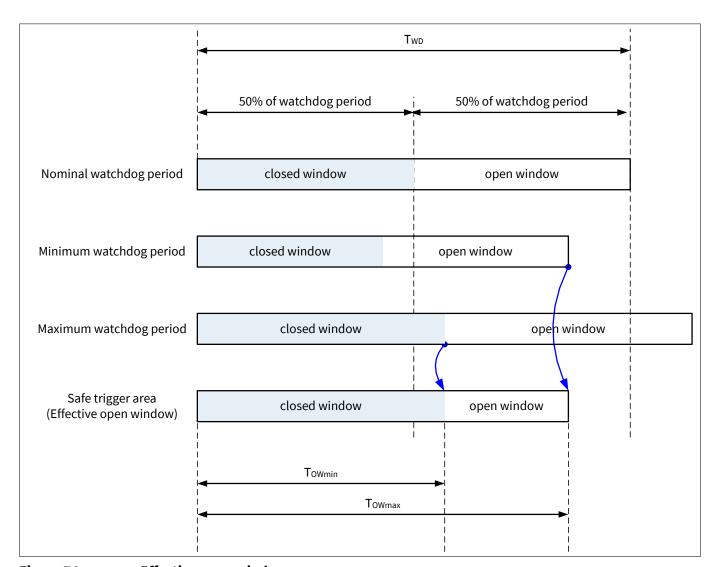

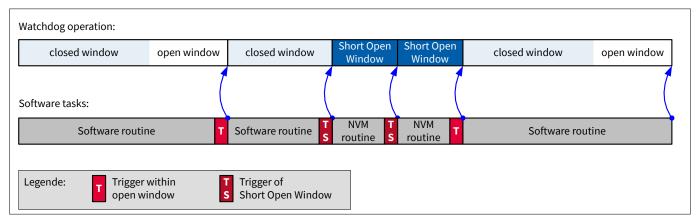

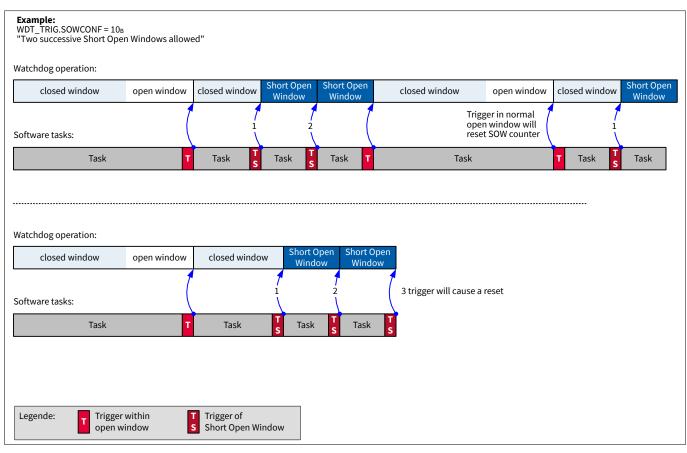

| 13        | Watchdog timer (WDT1)                                                         | 366 |

| 13.1      | Features                                                                      | 366 |

| 13.2      | Introduction                                                                  | 367 |

| 13.3      | Functional description                                                        | 368 |

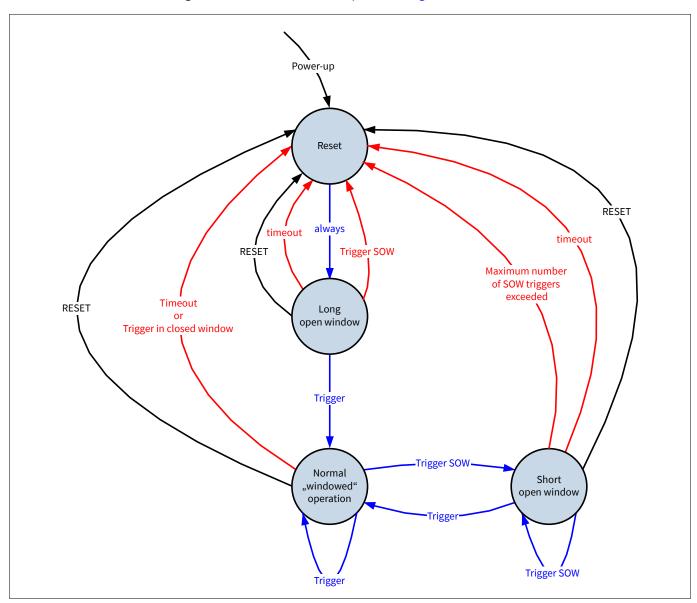

| 13.3.1    | Modes of operation                                                            | 368 |

## Microcontroller with LIN and power switches for automotive applications

| 13.3.2     | Normal operation                                                           | 369 |

|------------|----------------------------------------------------------------------------|-----|

| 13.3.3     | Watchdog register                                                          | 371 |

| 13.3.3.1   | Register overview - External Watchdog registers (ascending offset address) | 372 |

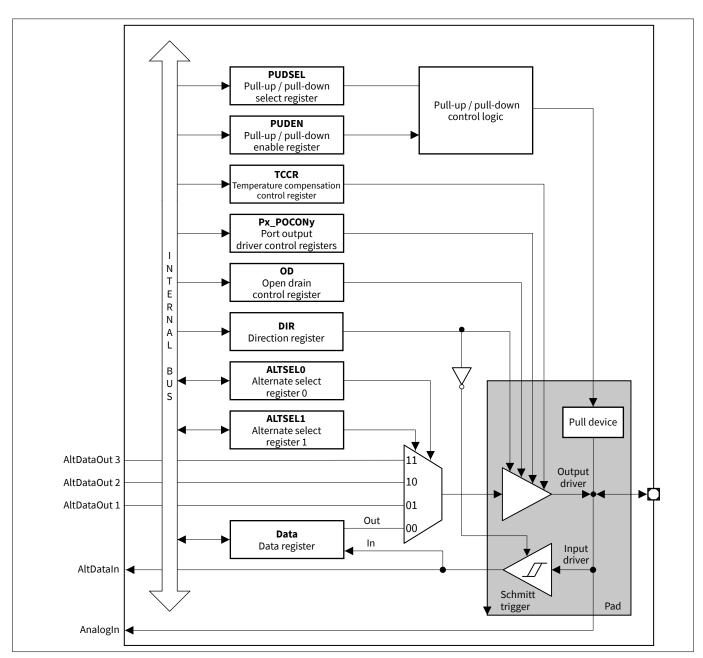

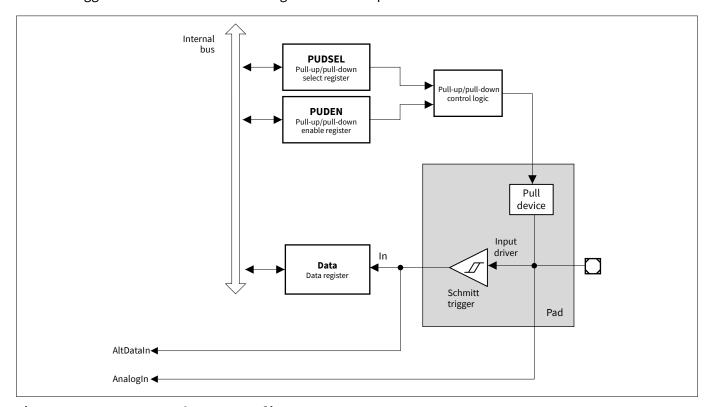

| 14         | GPIO ports and peripheral I/O                                              | 373 |

| 14.1       | Features                                                                   | 373 |

| 14.2       | Introduction                                                               | 374 |

| 14.2.1     | Port 0 and port 1                                                          | 374 |

| 14.2.2     | Port 2                                                                     | 376 |

| 14.3       | Port implementation details                                                | 377 |

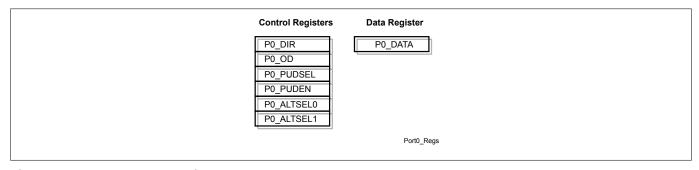

| 14.3.1     | Port 0                                                                     | 377 |

| 14.3.1.1   | Port 0 functions                                                           | 377 |

| 14.3.1.2   | Overview - Port 0 registers                                                | 379 |

| 14.3.1.2.1 | Register overview - Port 0 registers (ascending offset address)            | 379 |

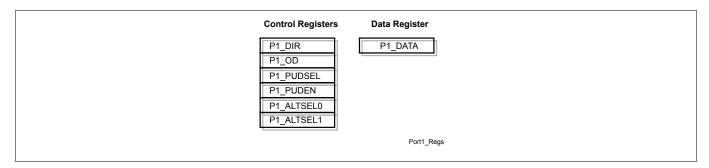

| 14.3.2     | Port 1                                                                     | 380 |

| 14.3.2.1   | Port 1 functions                                                           | 380 |

| 14.3.2.2   | Overview - Port 1 registers                                                | 381 |

| 14.3.2.2.1 | Register overview - Port 1 registers (ascending offset address)            | 381 |

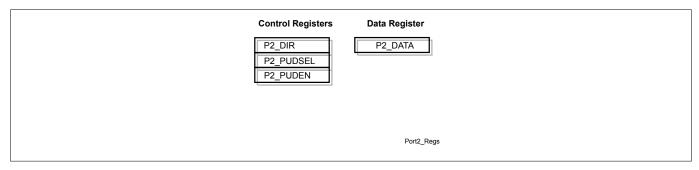

| 14.3.3     | Port 2                                                                     | 382 |

| 14.3.3.1   | Port 2 functions                                                           | 382 |

| 14.3.3.2   | Overview - Port 2 registers                                                | 383 |

| 14.3.3.2.1 | Register overview - Port 2 registers (ascending offset address)            | 384 |

| 14.3.4     | GPIO ports and peripheral I/O (PORT) register definition                   | 385 |

| 14.3.4.1   | Register address space - PORT                                              | 385 |

| 14.3.4.2   | Register overview - PORT (ascending offset address)                        | 385 |

| 14.3.4.3   | Port 0 data register                                                       | 386 |

| 14.3.4.4   | Port 0 direction register                                                  | 388 |

| 14.3.4.5   | Port 0 open drain control register                                         | 390 |

| 14.3.4.6   | Port 0 pull-up/pull-down select register                                   | 391 |

| 14.3.4.7   | Port 0 pull-up/pull-down enable register                                   | 392 |

| 14.3.4.8   | Port 0 alternate select 0 register                                         | 393 |

| 14.3.4.9   | Port 0 alternate select 1 register                                         | 395 |

| 14.3.4.10  | Port 1 data register                                                       | 397 |

| 14.3.4.11  | Port 1 direction register                                                  | 399 |

| 14.3.4.12  | Port 1 open drain control register                                         | 401 |

| 14.3.4.13  | Port 1 pull-up/pull-down select register                                   | 402 |

| 14.3.4.14  | Port 1 pull-up/pull-down enable register                                   | 403 |

| 14.3.4.15  | Port 1 alternate select 0 register                                         |     |

| 14.3.4.16  | Port 1 alternate select 1 register                                         | 405 |

| 14.3.4.17  | Port 2 data register                                                       | 406 |

| 14.3.4.18  | Port 2 direction register                                                  | 407 |

| 14.3.4.19  | Port 2 pull-up/pull-down select register                                   | 408 |

## Microcontroller with LIN and power switches for automotive applications

| 14.3.4.20  | Port 2 pull-up/pull-down enable register                                   | 409 |

|------------|----------------------------------------------------------------------------|-----|

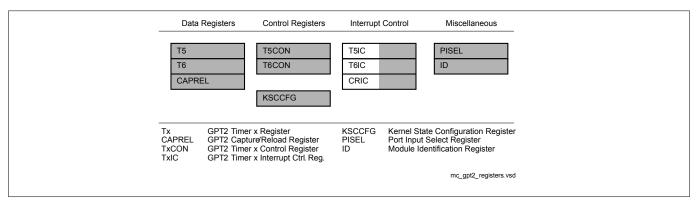

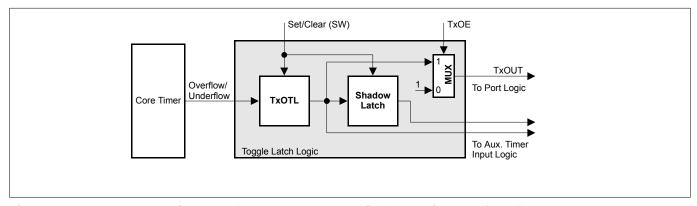

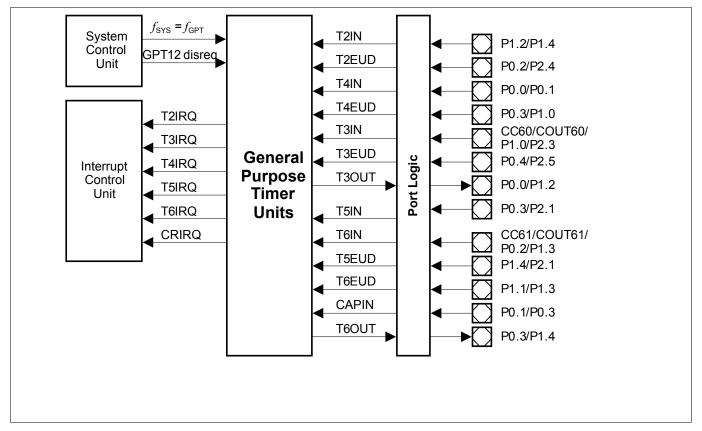

| 15         | General purpose timer units (GPT12)                                        | 410 |

| 15.1       | Features                                                                   | 410 |

| 15.1.1     | Features block GPT1                                                        | 410 |

| 15.1.2     | Features block GPT2                                                        | 410 |

| 15.2       | Introduction                                                               | 410 |

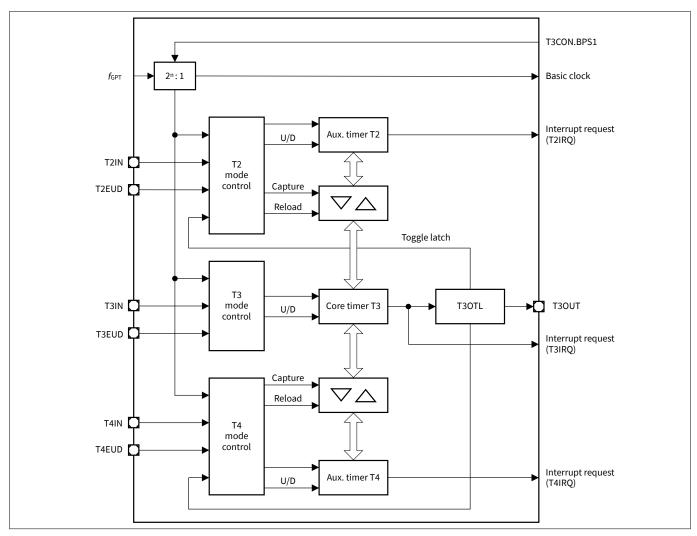

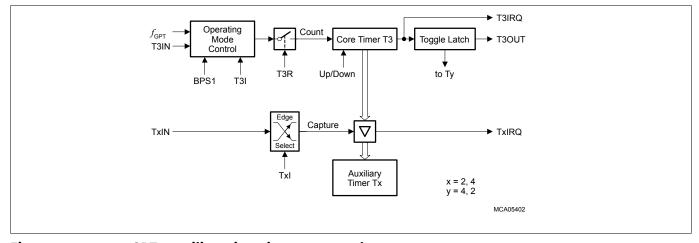

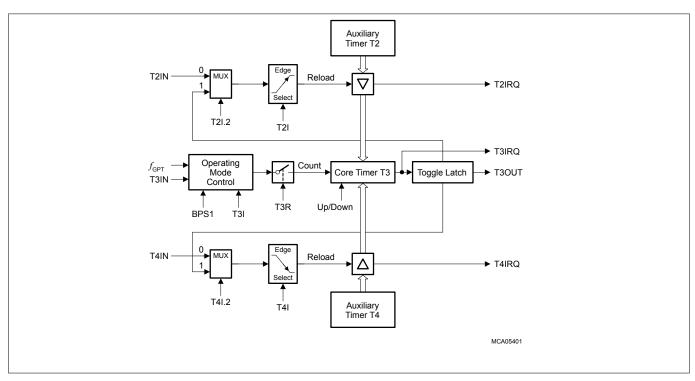

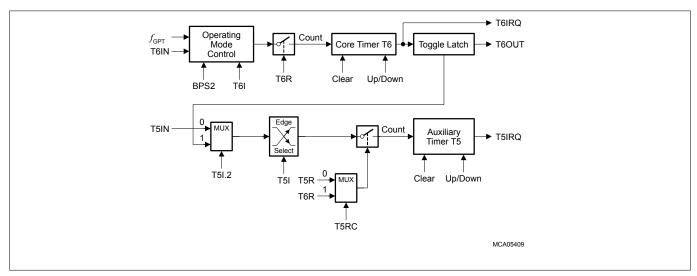

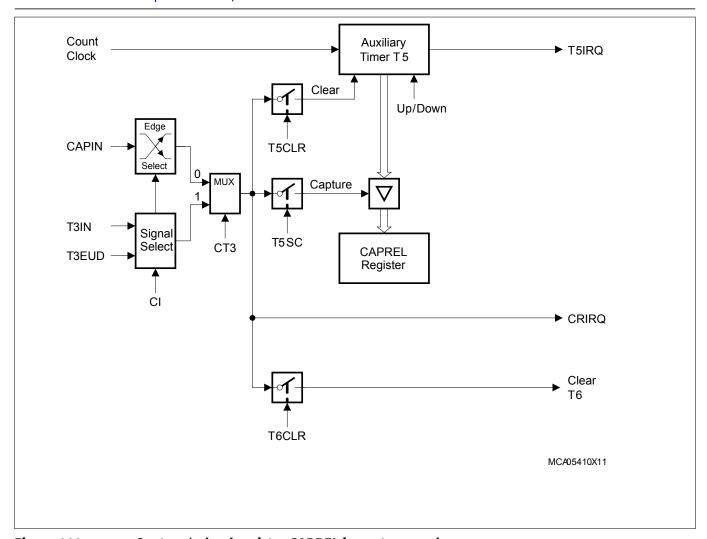

| 15.2.1     | Block diagram GPT1                                                         | 411 |

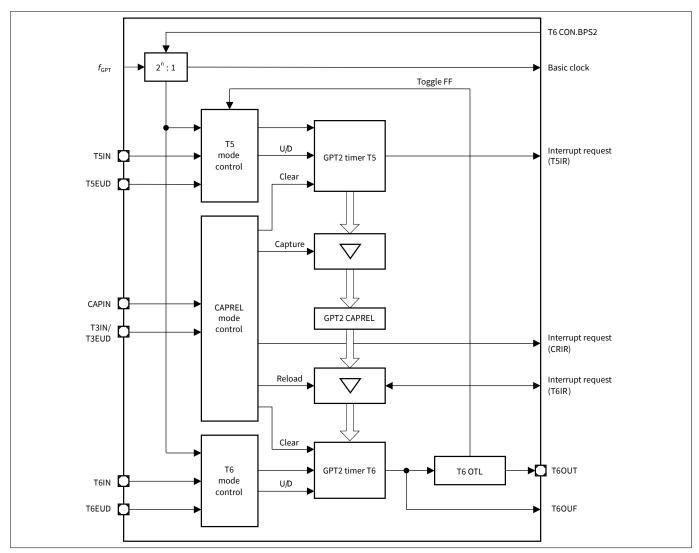

| 15.2.2     | Block diagram GPT2                                                         | 412 |

| 15.3       | Timer block GPT1                                                           | 413 |

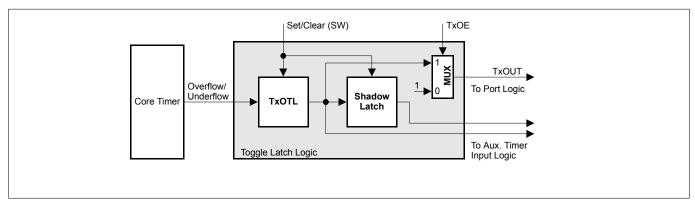

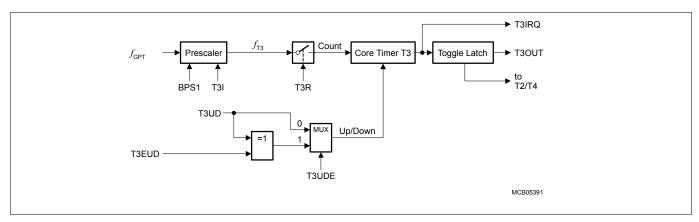

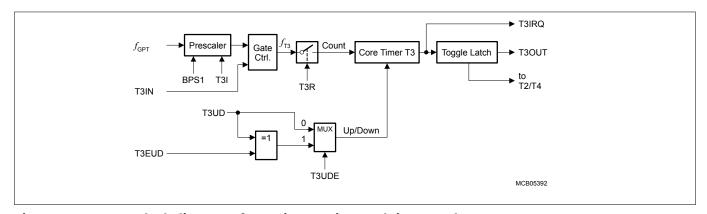

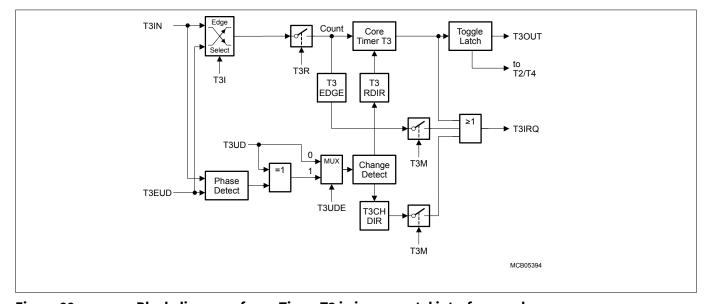

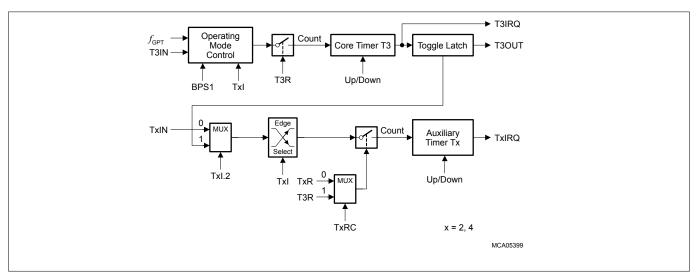

| 15.3.1     | GPT1 core timer T3 control                                                 | 413 |

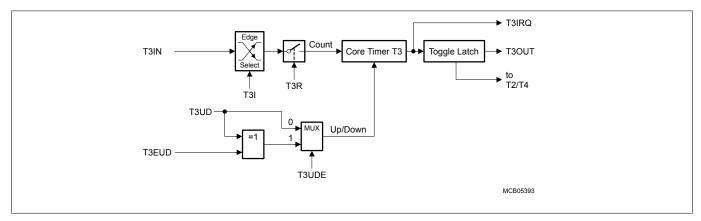

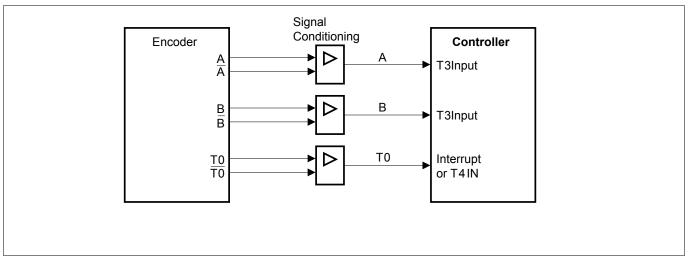

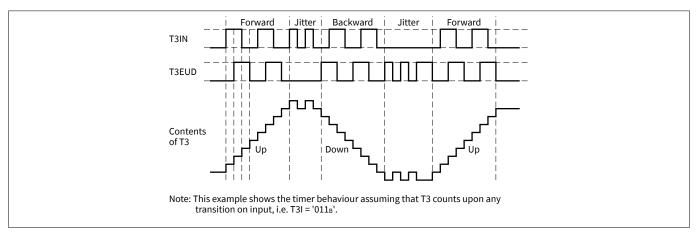

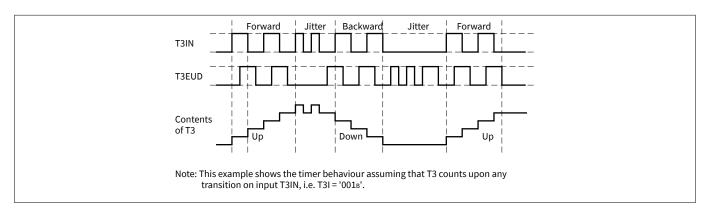

| 15.3.2     | GPT1 core timer T3 operating modes                                         | 415 |

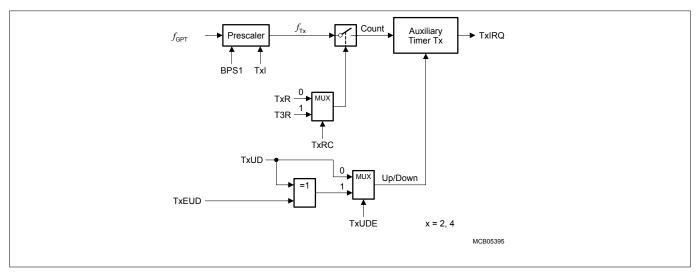

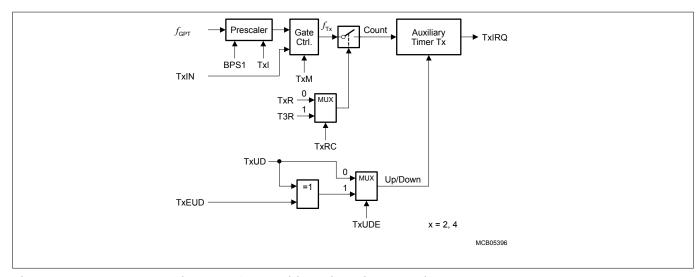

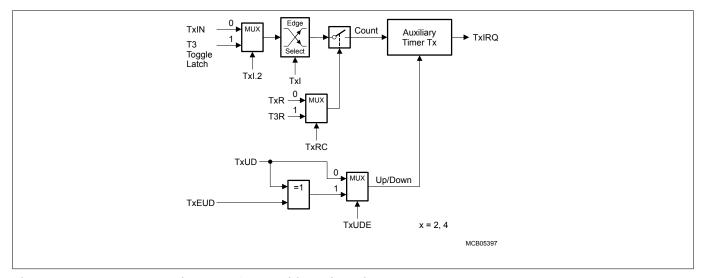

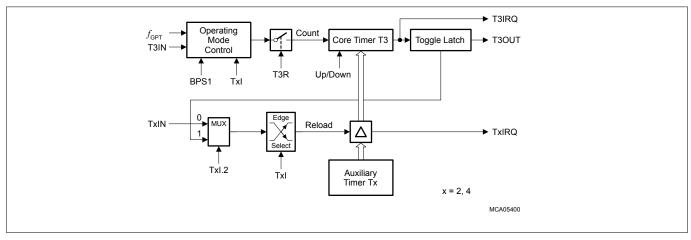

| 15.3.3     | GPT1 auxiliary timers T2/T4 control                                        | 419 |

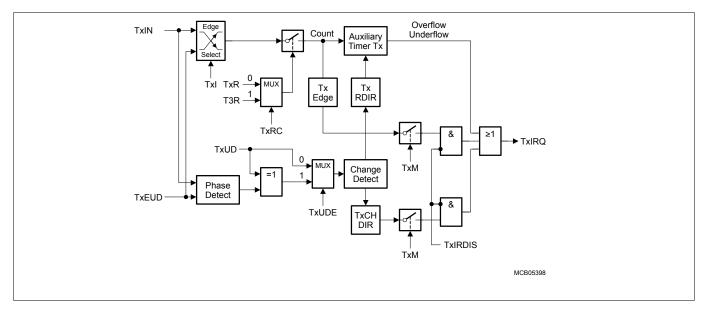

| 15.3.4     | GPT1 auxiliary timers T2/T4 operating modes                                | 420 |

| 15.3.5     | GPT1 clock signal control                                                  | 425 |

| 15.3.6     | Interrupt control for GPT1 timers                                          | 427 |

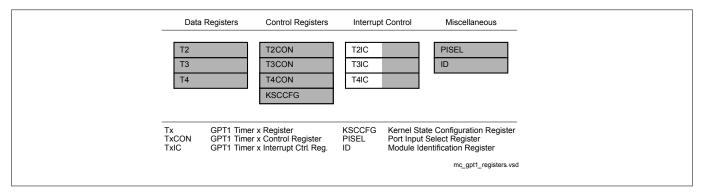

| 15.3.7     | GPT1 registers                                                             | 428 |

| 15.3.7.1   | Register overview - GPT1 registers (ascending offset address)              | 428 |

| 15.3.7.2   | GPT1 timer interrupt control registers                                     | 428 |

| 15.3.7.3   | GPT1 encoding                                                              | 428 |

| 15.3.7.3.1 | Encoding of GPT1 timer count direction control                             | 428 |

| 15.3.7.3.2 | Timer mode and gated timer mode: Encoding of GPT1 overall prescaler factor | 428 |

| 15.3.7.3.3 | Counter mode: Encoding of GPT1 input edge selection                        | 429 |

| 15.3.7.3.4 | Incremental interface mode: Encoding of input edge selection               | 430 |

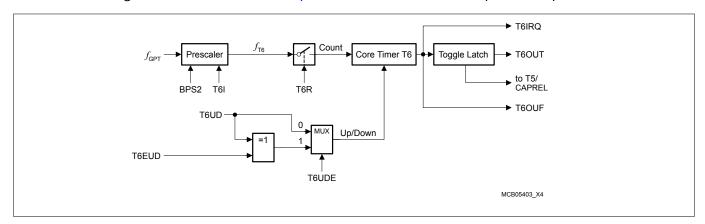

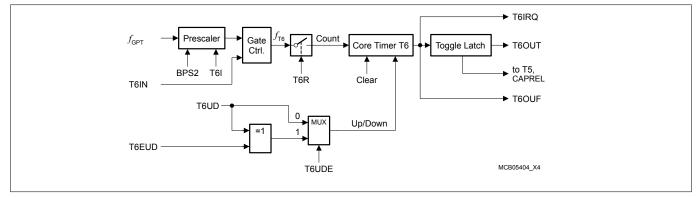

| 15.4       | Timer block GPT2                                                           | 431 |

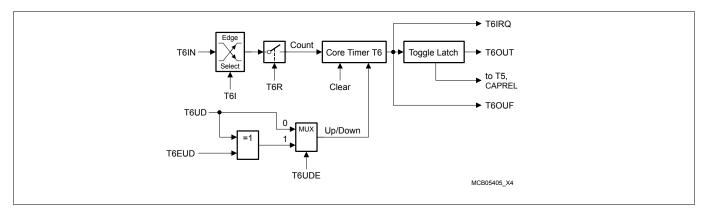

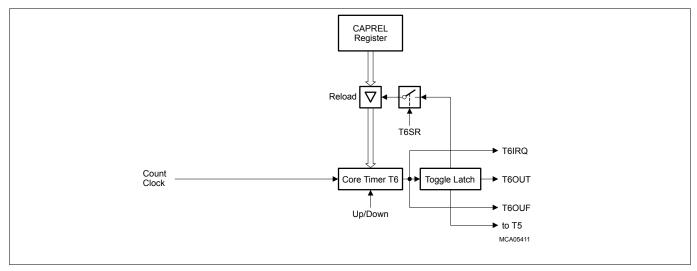

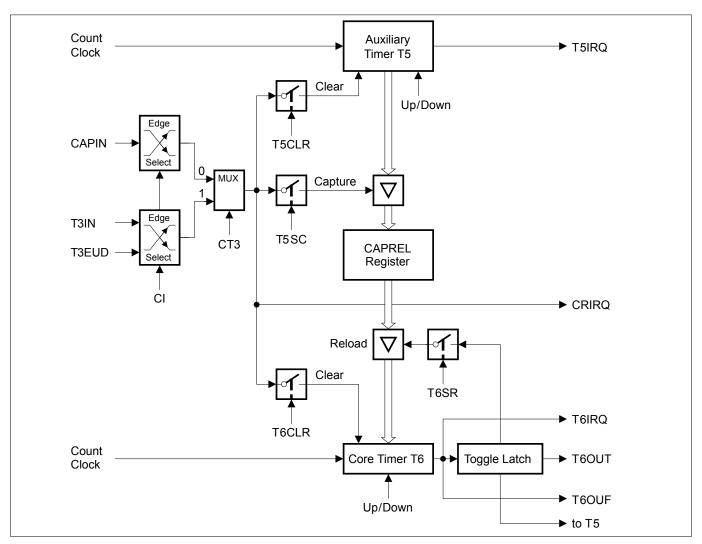

| 15.4.1     | GPT2 core timer T6 control                                                 | 431 |

| 15.4.2     | GPT2 core timer T6 operating modes                                         | 433 |

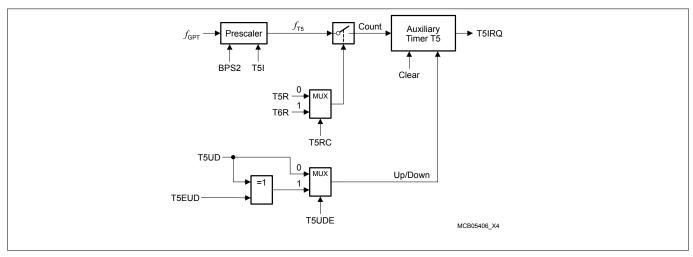

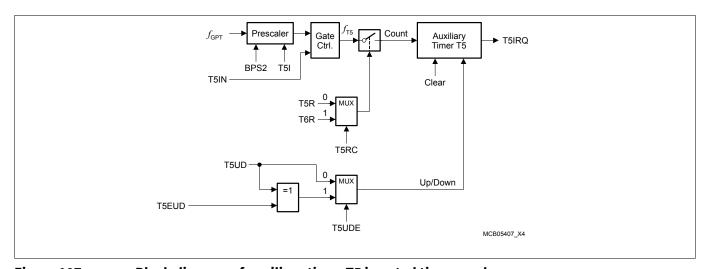

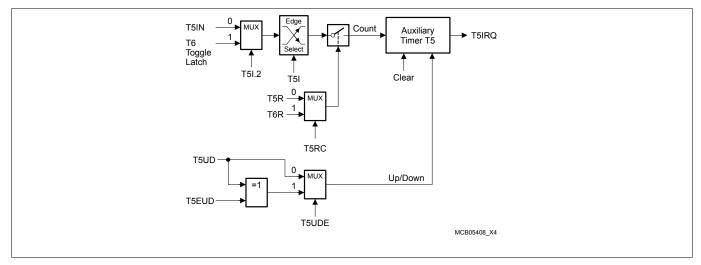

| 15.4.3     | GPT2 auxiliary timer T5 control                                            | 435 |

| 15.4.4     | GPT2 auxiliary timer T5 operating modes                                    | 436 |

| 15.4.5     | GPT2 register CAPREL operating modes                                       | 438 |

| 15.4.6     | GPT2 clock signal control                                                  | 443 |

| 15.4.7     | Interrupt control for GPT2 timers and CAPREL                               | 444 |

| 15.4.8     | GPT2 registers                                                             | 445 |

| 15.4.8.1   | Register overview - GPT2 registers (ascending offset address)              | 445 |

| 15.4.8.2   | GPT2 timer and CAPREL interrupt control registers                          | 445 |

| 15.4.8.3   | GPT2 encoding                                                              | 445 |

| 15.4.8.3.1 | Encoding of timer count direction control                                  | 445 |

| 15.4.8.3.2 | Timer mode and gated timer mode: encoding of overall prescaler Factor      | 446 |

| 15.4.8.3.3 | Counter mode: encoding of input edge selection                             | 446 |

| 15.5       | Miscellaneous GPT12 registers                                              | 447 |

| 15.5.1     | Register overview - GPT12 registers (ascending offset address)             | 447 |

| 15.6       | Implementation of the GPT12 module                                         | 448 |

## Microcontroller with LIN and power switches for automotive applications

| 15.6.1   | Module connections                                       | 448 |

|----------|----------------------------------------------------------|-----|

| 15.7     | General purpose timer units (GPT12E) register definition | 451 |

| 15.7.1   | Register address space - GPT12E                          | 451 |

| 15.7.2   | Register overview - GPT12E (ascending offset address)    | 451 |

| 15.7.3   | Module identification register                           | 452 |

| 15.7.4   | Port input select register                               | 453 |

| 15.7.5   | Timer T2 control register                                | 455 |

| 15.7.6   | Timer T3 control register                                | 457 |

| 15.7.7   | Timer T4 control register                                | 459 |

| 15.7.8   | Timer T2 count register                                  | 461 |

| 15.7.9   | Timer T3 count register                                  | 462 |

| 15.7.10  | Timer T4 count register                                  | 463 |

| 15.7.11  | Timer T5 control register                                | 464 |

| 15.7.12  | Timer T6 control register                                | 466 |

| 15.7.13  | Capture/reload register                                  | 468 |

| 15.7.14  | Timer 5 count register                                   | 469 |

| 15.7.15  | Timer 6 count register                                   | 470 |

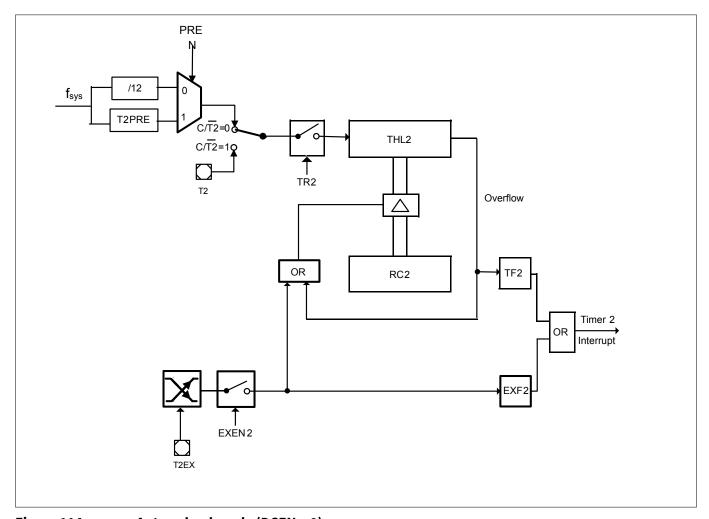

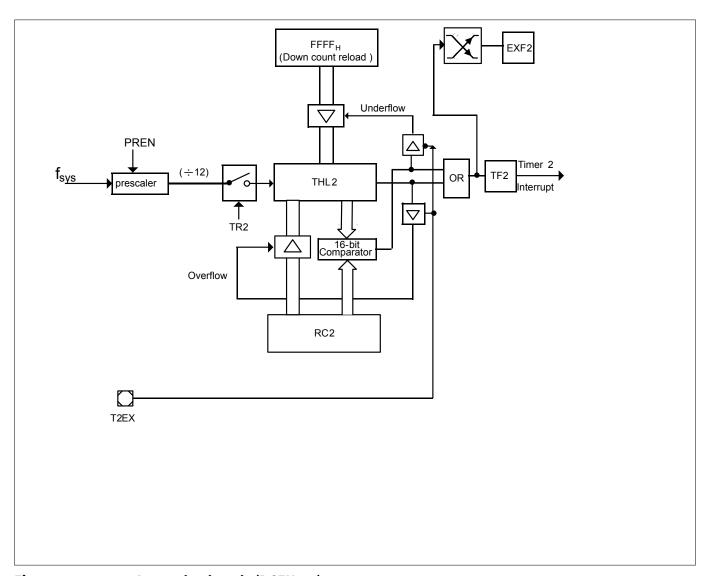

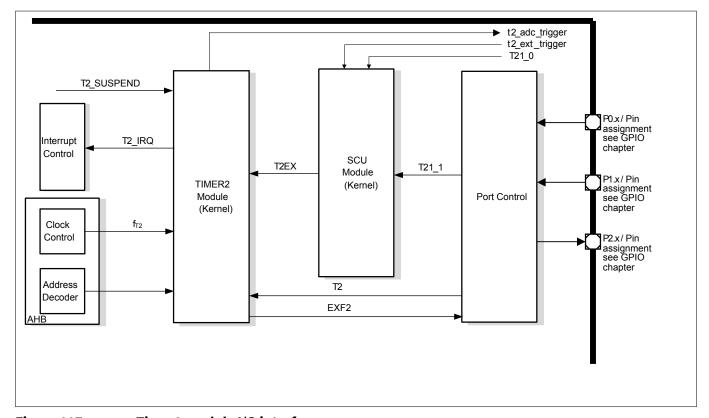

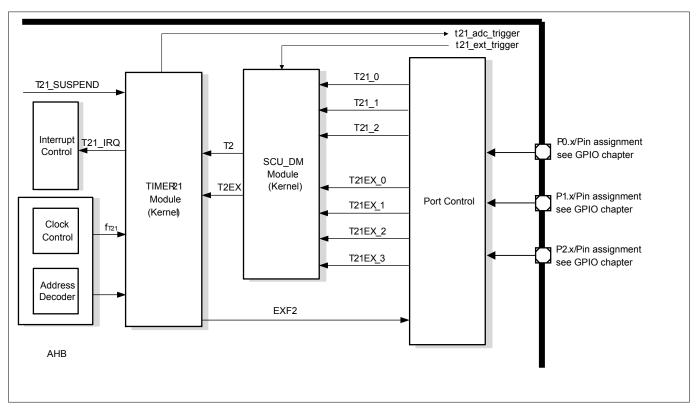

| 16       | Timer2 and Timer21                                       | 471 |

| 16.1     | Features                                                 | 471 |

| 16.2     | Introduction                                             | 471 |

| 16.2.1   | Timer2 and Timer21 modes overview                        | 471 |

| 16.3     | Functional description                                   | 473 |

| 16.3.1   | Auto-reload mode                                         | 473 |

| 16.3.1.1 | Up/down count disabled                                   | 473 |

| 16.3.1.2 | Up/down count enabled                                    | 474 |

| 16.3.2   | Capture mode                                             | 476 |

| 16.3.3   | Count clock                                              | 476 |

| 16.3.4   | Interrupt generation                                     | 477 |

| 16.4     | Timer2 registers                                         | 478 |

| 16.4.1   | Timer2 and Timer21 (TIMER) register definition           | 479 |

| 16.4.1.1 | Register address space - TIMER                           | 479 |

| 16.4.1.2 | Register overview - TIMER (ascending offset address)     | 479 |

| 16.4.1.3 | Timer2 mode register                                     | 480 |

| 16.4.1.4 | Timer2 control register                                  | 482 |

| 16.4.1.5 | Timer2 interrupt clear register                          | 483 |

| 16.4.1.6 | Timer2 control 1 register                                | 484 |

| 16.4.1.7 | Timer2 reload/capture register                           | 485 |

| 16.4.1.8 | Timer2 count register                                    | 486 |

| 16.5     | Timer2 and Timer21 implementation details                | 487 |

| 16.5.1   | Interfaces of the Timer2 and Timer21                     | 487 |

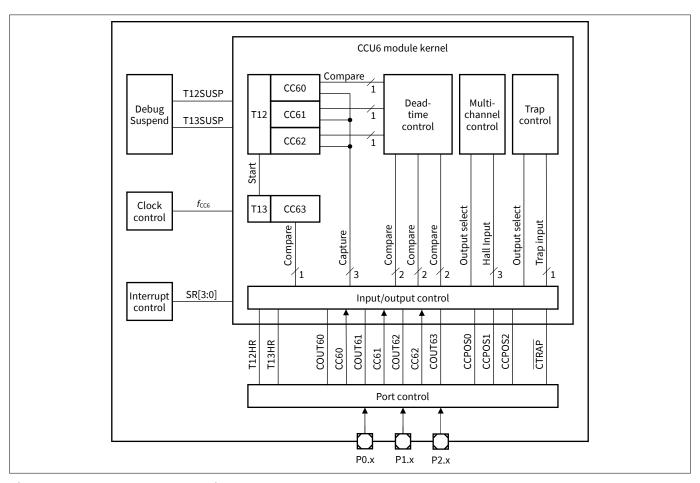

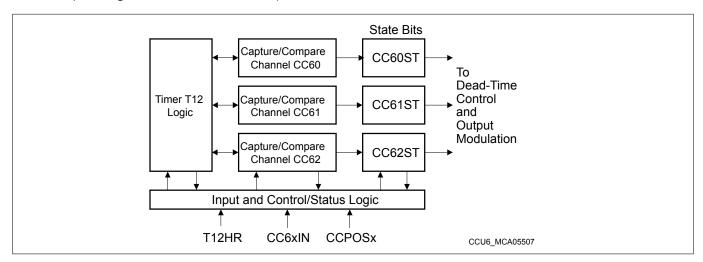

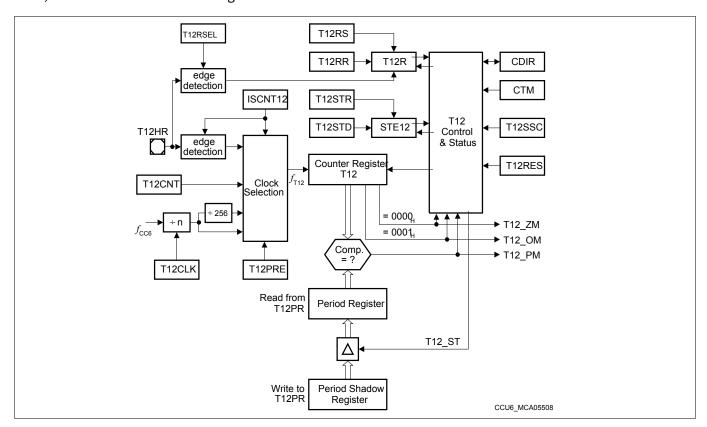

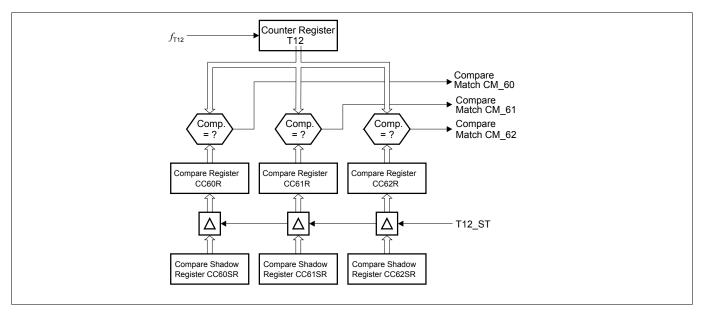

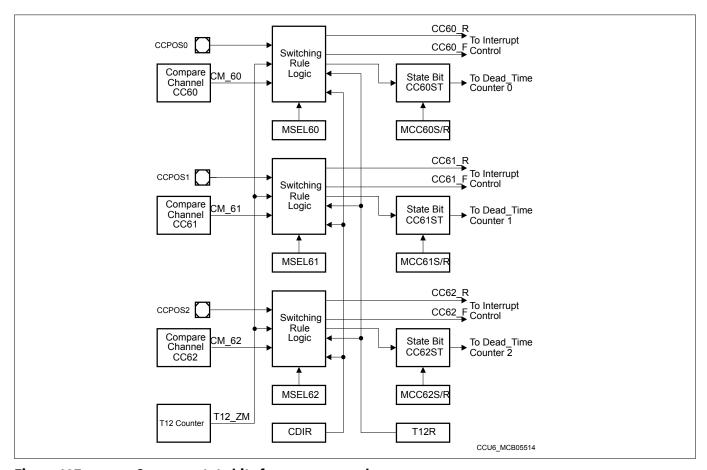

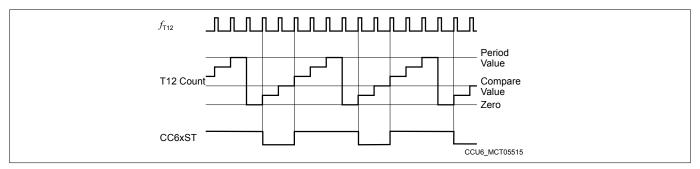

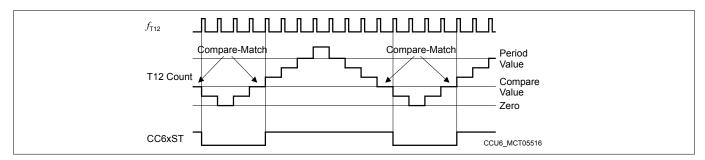

| 17       | Capture/compare unit 6 (CCU6)                            | 489 |

## Microcontroller with LIN and power switches for automotive applications

### **Table of contents**

| 490 |

|-----|

|     |

| 490 |

| 492 |

| 493 |

| 495 |

| 495 |

| 496 |

| 498 |

| 499 |

| 499 |

| 499 |

| 503 |

| 504 |

| 504 |

| 506 |

| 507 |

| 509 |

| 512 |

| 513 |

| 514 |

| 514 |

| 516 |

| 516 |

| 517 |

| 517 |

| 518 |

| 519 |

| 520 |

| 521 |

| 522 |

| 524 |

| 526 |

| 527 |

| 528 |

| 529 |

| 530 |

| 532 |

| 532 |

| 533 |

| 533 |

|     |

|     |

15

## Microcontroller with LIN and power switches for automotive applications

| 17.10.1    | System registers                                                                                                         | 534 |

|------------|--------------------------------------------------------------------------------------------------------------------------|-----|

| 17.10.1.1  | Register overview - System registers (ascending offset address)                                                          | 534 |

| 17.10.2    | Timer 12 related registers                                                                                               | 534 |

| 17.10.2.1  | Register overview - Timer 12 related registers (ascending offset address)                                                | 535 |

| 17.10.3    | Timer 13 related registers                                                                                               | 536 |

| 17.10.3.1  | Register overview - Timer 13 related registers (ascending offset address)                                                | 536 |

| 17.10.4    | Capture/compare control registers                                                                                        | 537 |

| 17.10.4.1  | $\label{lem:Register} \textbf{Register overview - Capture and compare control registers (ascending offset address)} \;.$ | 537 |

| 17.10.5    | Global modulation control registers                                                                                      | 538 |

| 17.10.5.1  | Register overview - Global modulation control registers (ascending offset address) $\dots$                               | 538 |

| 17.10.6    | Multi-channel modulation control registers                                                                               | 538 |

| 17.10.6.1  | Register overview - Multi-channel modulation control registers (ascending offset                                         |     |

|            | address)                                                                                                                 | 538 |

| 17.10.7    | Interrupt control registers                                                                                              | 539 |

| 17.10.7.1  | Register overview - Interrupt control registers (ascending offset address)                                               | 539 |

| 17.10.8    | Capture/compare unit 6 (CCU6) register definition                                                                        | 540 |

| 17.10.8.1  | Register address space - CCU6                                                                                            | 540 |

| 17.10.8.2  | Register overview - CCU6 (ascending offset address)                                                                      | 540 |

| 17.10.8.3  | Port input select 0 register                                                                                             | 542 |

| 17.10.8.4  | Port input select 2 register                                                                                             | 544 |

| 17.10.8.5  | Capture/compare shadow register for channel CC60 register                                                                | 546 |

| 17.10.8.6  | Capture/compare shadow register for channel CC61 register                                                                | 547 |

| 17.10.8.7  | Capture/compare shadow register for channel CC62 register                                                                | 548 |

| 17.10.8.8  | Timer T12 period register                                                                                                | 549 |

| 17.10.8.9  | Dead-time control register for timer T12 low register                                                                    | 550 |

| 17.10.8.10 | Capture/compare register for channel CC60 register                                                                       | 552 |

| 17.10.8.11 | Capture/compare register for channel CC61 register                                                                       | 553 |

| 17.10.8.12 | Capture/compare register for channel CC62 register                                                                       | 554 |

| 17.10.8.13 | T12 capture/compare mode select register                                                                                 | 555 |

| 17.10.8.14 | Timer T12 counter register                                                                                               | 558 |

| 17.10.8.15 | Capture/compare for channel CC63 register                                                                                | 559 |

| 17.10.8.16 | Capture/compare shadow for channel CC63 register                                                                         | 560 |

| 17.10.8.17 | Timer T13 period register                                                                                                | 561 |

| 17.10.8.18 | Timer T13 counter register                                                                                               | 562 |

| 17.10.8.19 | Timer control 4 register                                                                                                 | 563 |

| 17.10.8.20 | Compare state modification register                                                                                      | 565 |

| 17.10.8.21 | Timer control 0 register                                                                                                 | 567 |

| 17.10.8.22 | Timer control 2 register                                                                                                 | 570 |

| 17.10.8.23 | Compare state register                                                                                                   | 572 |

| 17.10.8.24 | Passive state level register                                                                                             | 576 |

| 17.10.8.25 | Multi-channel mode control register                                                                                      | 577 |

| 17.10.8.26 | Trap control register                                                                                                    | 579 |

|            |                                                                                                                          |     |

# $\textbf{MOTIX}^{^{\text{TM}}}\textbf{TLE984xQX}$

## Microcontroller with LIN and power switches for automotive applications

| 17.10.8.27 | Multi-channel mode output shadow register                  | 581 |

|------------|------------------------------------------------------------|-----|

| 17.10.8.28 | Modulation control register                                | 583 |

| 17.10.8.29 | Multi-channel mode output register                         | 585 |

| 17.10.8.30 | Capture/compare interrupt status reset register            | 587 |

| 17.10.8.31 | Capture/compare interrupt enable register                  | 589 |

| 17.10.8.32 | Capture/compare interrupt node pointer register            | 592 |

| 17.10.8.33 | Capture/compare interrupt status set register              | 594 |

| 17.10.8.34 | Capture/compare interrupt status register                  | 596 |

| 17.11      | MOTIX <sup>™</sup> TLE984xQX module implementation details | 599 |

| 17.11.1    | Interfaces of the CCU6 module                              | 599 |

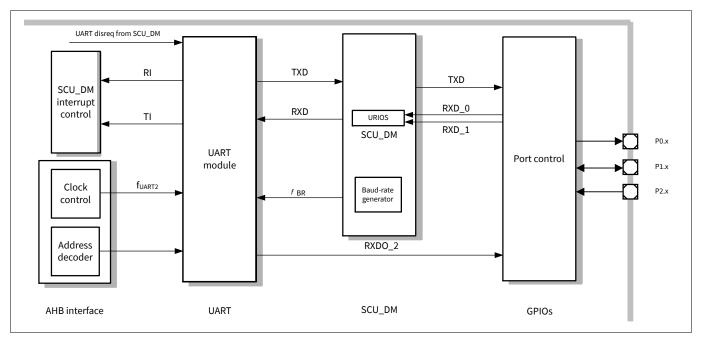

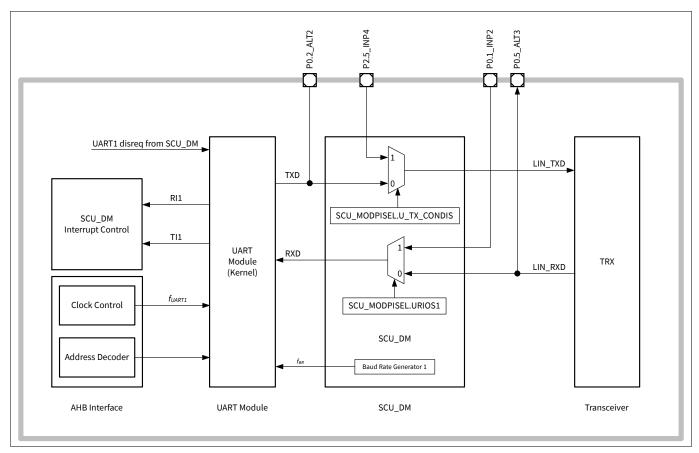

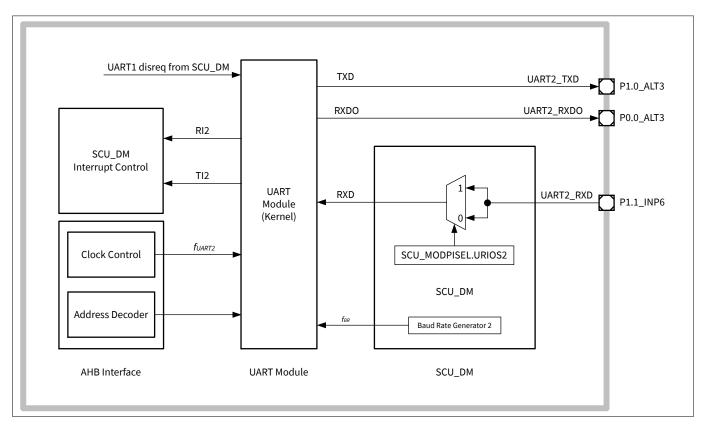

| 18         | UART1/UART2                                                | 601 |

| 18.1       | Features                                                   | 601 |

| 18.2       | Introduction                                               | 601 |

| 18.2.1     | Block diagram                                              | 602 |

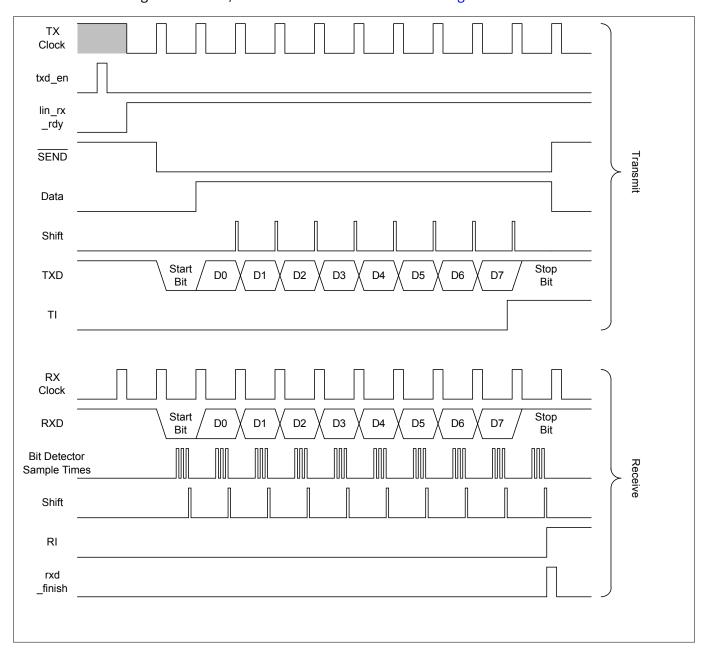

| 18.3       | UART modes                                                 | 603 |

| 18.3.1     | Mode 0, 8-bit shift register, fixed baud-rate              | 603 |

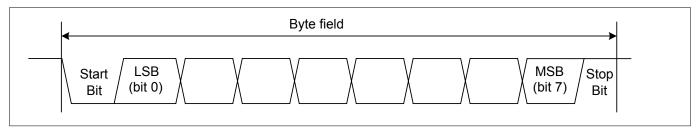

| 18.3.2     | Mode 1, 8-bit UART, variable baud-rate                     | 603 |

| 18.3.3     | Mode 2, 9-bit UART, fixed baud-rate                        | 605 |

| 18.3.4     | Mode 3, 9-bit UART, variable baud-rate                     | 605 |

| 18.4       | Multiprocessor communication                               | 607 |

| 18.5       | Interrupts                                                 | 607 |

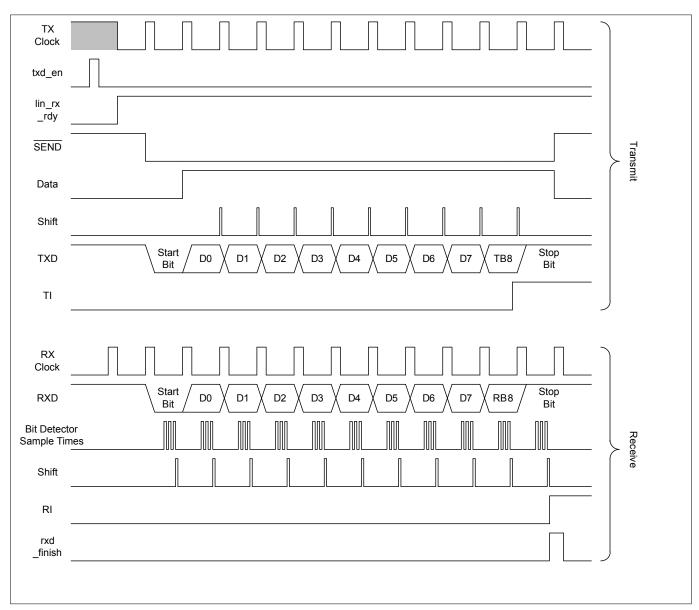

| 18.6       | Baud-rate generation                                       | 608 |

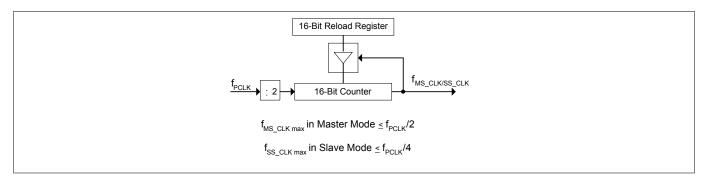

| 18.6.1     | Baud-rate generator                                        | 608 |

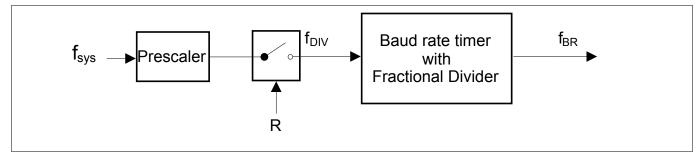

| 18.7       | LIN support in UART                                        | 610 |

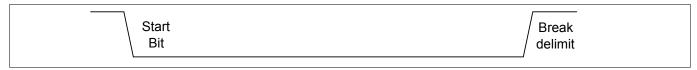

| 18.7.1     | LIN protocol                                               | 610 |

| 18.7.2     | LIN header transmission                                    | 611 |

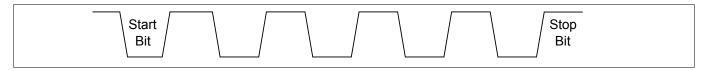

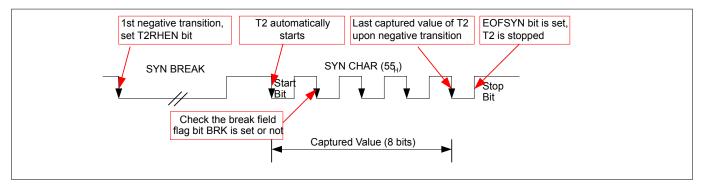

| 18.7.3     | Automatic synchronization to the host                      | 611 |

| 18.7.4     | Initialization of break/sync field detection logic         | 612 |

| 18.7.5     | Baud-rate range selection                                  | 612 |

| 18.7.6     | LIN baud-rate detection                                    | 614 |

| 18.8       | UART1/UART2 (UART) register definition                     | 615 |

| 18.8.1     | Register address space - UART                              | 615 |

| 18.8.2     | Register overview - UART (ascending offset address)        | 615 |

| 18.8.3     | Serial channel control register                            | 616 |

| 18.8.4     | Serial data buffer register                                | 618 |

| 18.8.5     | Serial channel control clear register                      | 619 |

| 18.8.6     | Baud-rate generator control and status registers           | 620 |

| 18.9       | Interfaces of the UART module                              | 621 |

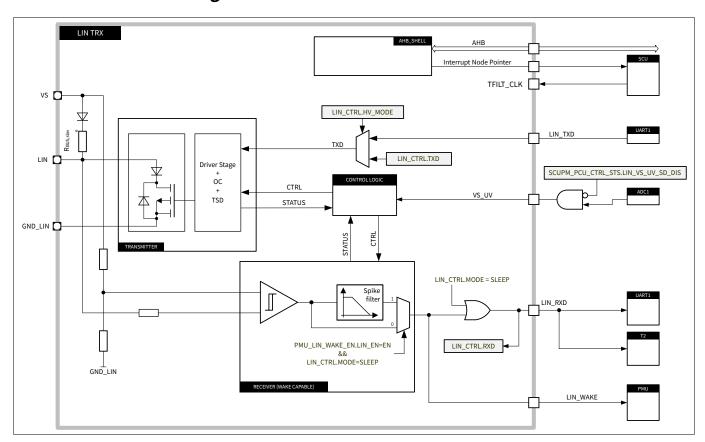

| 19         | LIN transceiver                                            | 623 |

| 19.1       | Features                                                   | 623 |

| 19.1.1     | General functional features                                | 623 |

| 19.1.2   | Mode of operation                                     | 3 |

|----------|-------------------------------------------------------|---|

| 19.1.3   | Special features                                      | 3 |

| 19.1.4   | Slope mode features                                   | 3 |

| 19.1.5   | Wake-up features                                      | 3 |

| 19.2     | Introduction                                          | 4 |

| 19.2.1   | Block diagram                                         | 5 |

| 19.3     | Functional description                                | 6 |

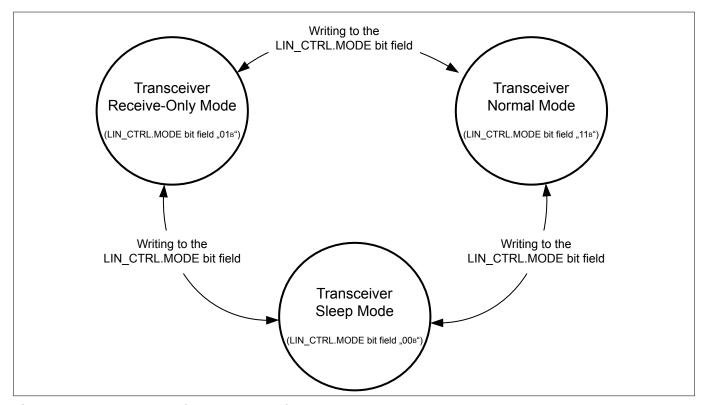

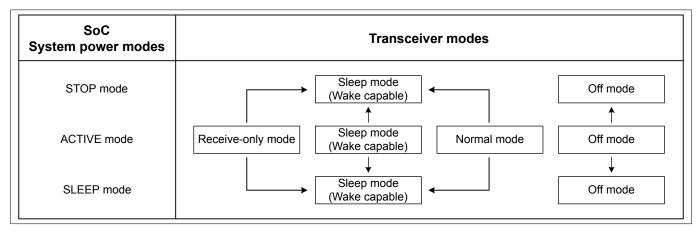

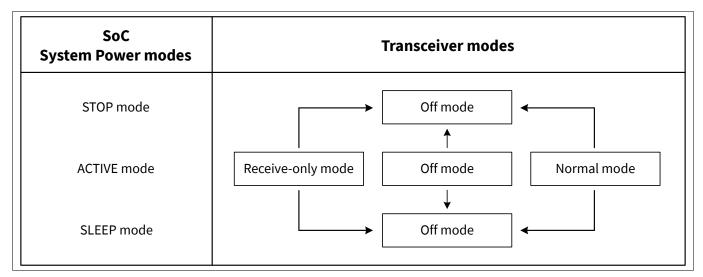

| 19.3.1   | Modes of operation                                    | 7 |

| 19.3.1.1 | Normal mode                                           | 7 |

| 19.3.1.2 | Receive-Only mode                                     | 8 |

| 19.3.1.3 | Sleep (wake-capable) mode                             | 8 |

| 19.3.1.4 | High voltage input/output (LHVIO)                     | 9 |

| 19.3.1.5 | Wake-up from network                                  | 9 |

| 19.3.2   | Fail-safe functions                                   | 0 |

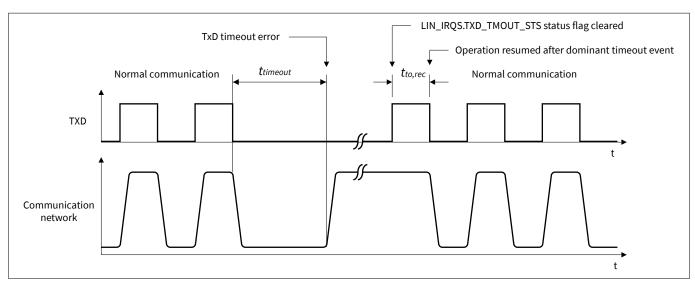

| 19.3.2.1 | TXD dominant timeout                                  | 0 |

| 19.3.2.2 | Overcurrent protection                                | 0 |

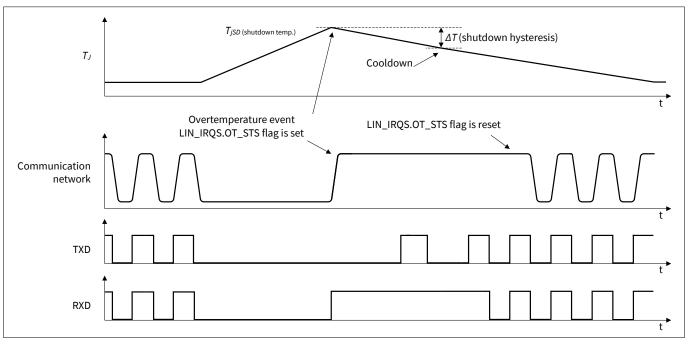

| 19.3.2.3 | Overtemperature protection                            | 0 |

| 19.3.3   | Transceiver slope modes                               | 1 |

| 19.3.4   | Transceiver error handling                            | 2 |

| 19.3.5   | Interrupts                                            | 2 |

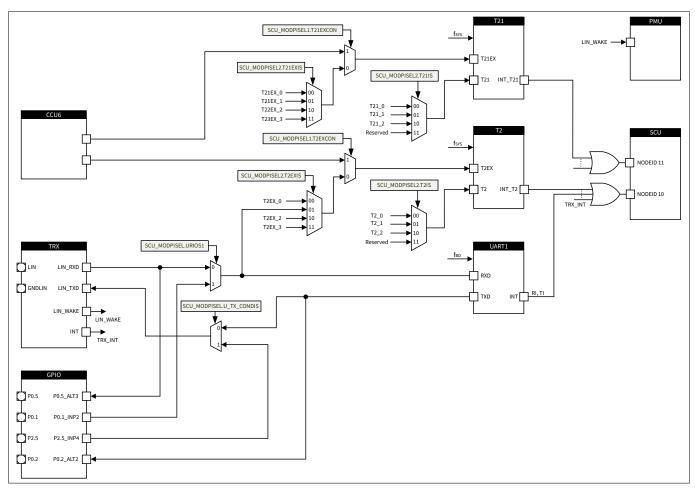

| 19.3.6   | Interconnect TRX, UART1, TIMER2, GPIO, CCU6, SCU, PMU | 4 |

| 19.4     | LIN transceiver (TRX) register definition             | 5 |

| 19.4.1   | Register address space - TRX63.                       | 5 |

| 19.4.2   | Register overview - TRX (ascending offset address)    | 5 |

| 19.4.3   | Transceiver control register                          | 6 |

| 19.4.4   | Transceiver interrupt status register                 | 8 |

| 19.4.5   | Transceiver interrupt status rclear register          | 9 |

| 19.4.6   | Transceiver interrupt enable register                 | 0 |

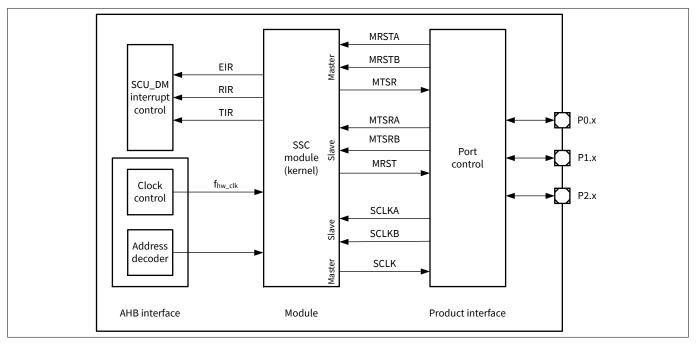

| 20       | High-speed synchronous serial interface SSC1/SSC2     | 1 |

| 20.1     | Features64                                            | 1 |

| 20.2     | Introduction                                          | 1 |

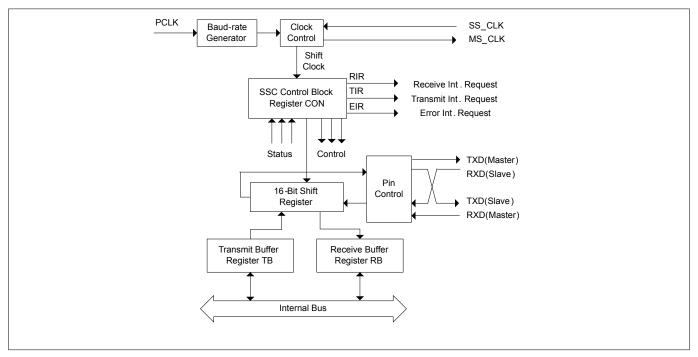

| 20.2.1   | Block diagram                                         | 2 |

| 20.3     | Functional description                                | 2 |

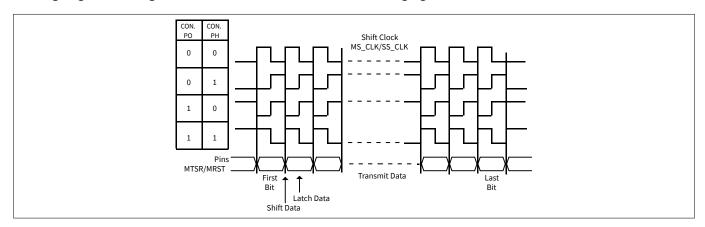

| 20.3.1   | SSC1 and SSC2 mode overview                           | 2 |

| 20.3.2   | Operating mode selection                              | 3 |

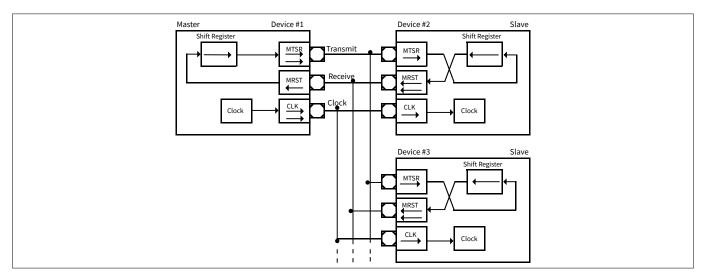

| 20.3.3   | Full-duplex operation                                 | 4 |

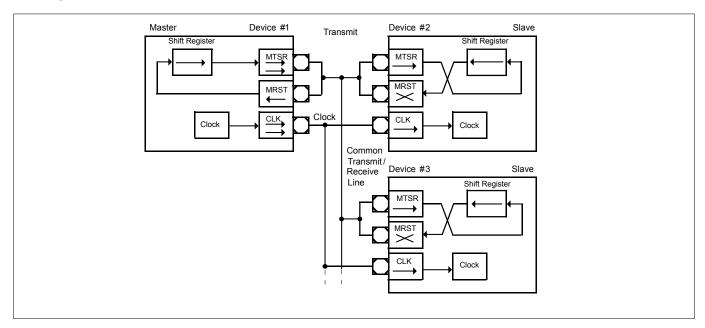

| 20.3.4   | Half-duplex operation                                 | 7 |

| 20.3.5   | Continuous transfers                                  | 7 |

| 20.3.5.1 | Port control64                                        | 8 |

| 20.3.6   | Baud-rate generation                                  | 9 |

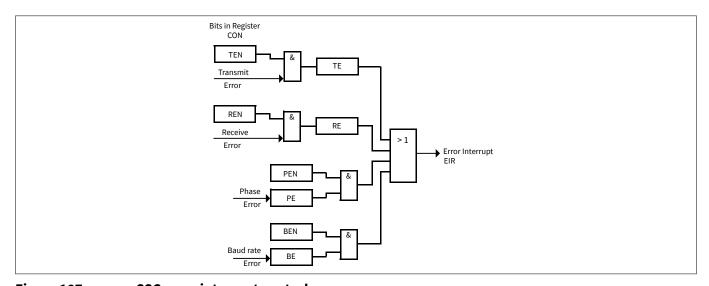

| 20.3.7   | Error detection mechanisms                            | 0 |

## Microcontroller with LIN and power switches for automotive applications

| 20.4     | Interrupts                                                                                     | 352          |

|----------|------------------------------------------------------------------------------------------------|--------------|

| 20.5     | SSC kernel registers                                                                           | 353          |

| 20.5.1   | High-speed synchronous serial interface (SSC) register definition                              | 354          |

| 20.5.1.1 | Register address space - SSC                                                                   | 354          |

| 20.5.1.2 | Register overview - SSC (ascending offset address)                                             | 354          |

| 20.5.1.3 | Port input select register                                                                     | 355          |

| 20.5.1.4 | Control register                                                                               | 356          |

| 20.5.1.5 | Interrupt status register clear                                                                | 359          |

| 20.5.1.6 | Baud-rate timer reload register                                                                | 360          |

| 20.5.1.7 | Transmitter buffer register                                                                    | 361          |

| 20.5.1.8 | Receiver buffer register                                                                       | 362          |

| 20.6     | Output multiplexing                                                                            | 362          |

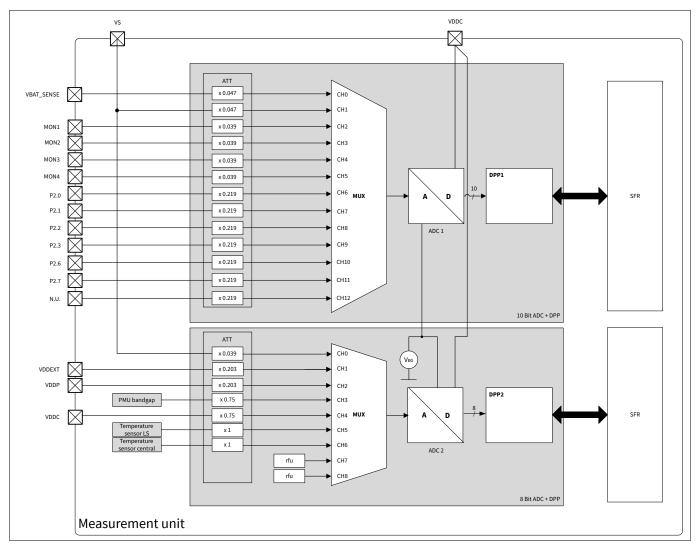

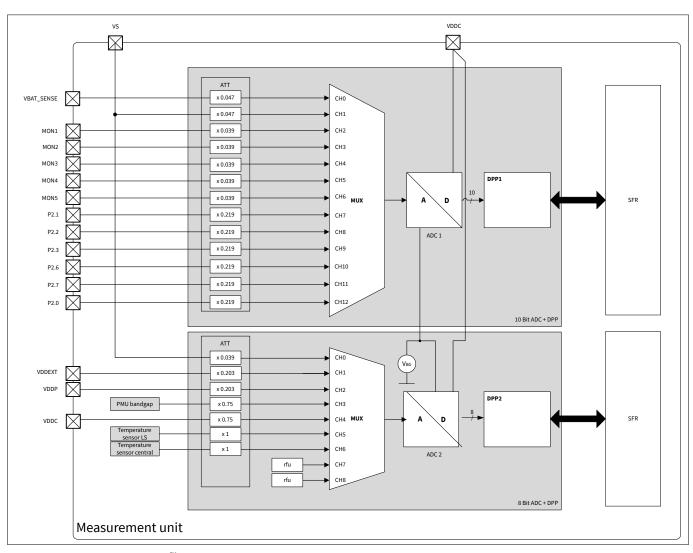

| 21       | Measurement unit                                                                               | 363          |

| 21.1     | Features                                                                                       | 363          |

| 21.2     | Introduction                                                                                   | 363          |

| 21.2.1   | Block diagram                                                                                  | 364          |

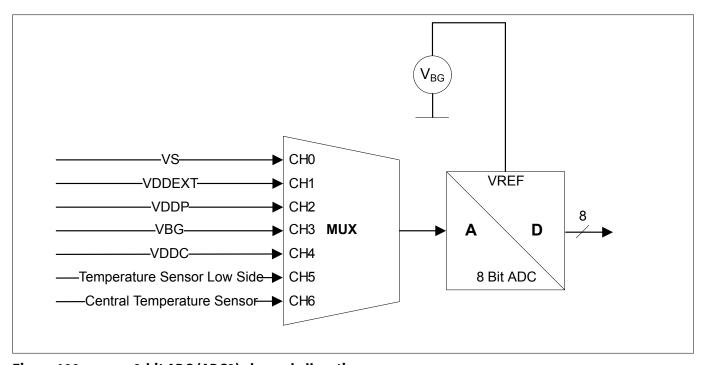

| 21.3     | 8-bit 10 channel ADC core                                                                      | 366          |

| 21.3.1   | 8-bit ADC channel allocation                                                                   | 366          |

| 21.3.2   | Transfer characteristics of ADC2                                                               | 367          |

| 21.3.3   | Detailed ADC2 measurement channel description                                                  | 367          |

| 21.3.4   | 8-bit 10 channel control register                                                              | 367          |

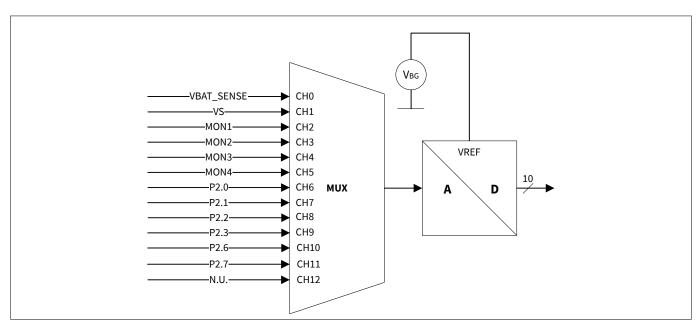

| 21.4     | 10-bit channel ADC core                                                                        | 368          |

| 21.4.1   | 10-bit ADC channel allocation                                                                  | 368          |

| 21.5     | Central and PMU regulator temperature sensor                                                   | 570          |

| 21.5.1   | Temperature sensor control register                                                            | 570          |

| 21.5.1.1 | Register overview - Temperature sensor control registers (ascending offset address) 6          | 570          |

| 21.6     | Supplement modules                                                                             | 571          |

| 21.6.1   | Functional safety concept                                                                      | 571          |

| 21.6.2   | Supplement modules control and status register                                                 | 572          |

| 21.6.2.1 | Register overview - Supplement modules control and status registers (ascending offset address) | 3 <b>7</b> 2 |

| 21.7     | Measurement unit (MF) register definition                                                      |              |

| 21.7.1   | Register address space - MF                                                                    |              |

| 21.7.2   | Register overview - MF (ascending offset address)                                              |              |

| 21.7.3   | Temperature sensor control register                                                            |              |

| 21.7.4   | Reference 1 status register                                                                    |              |

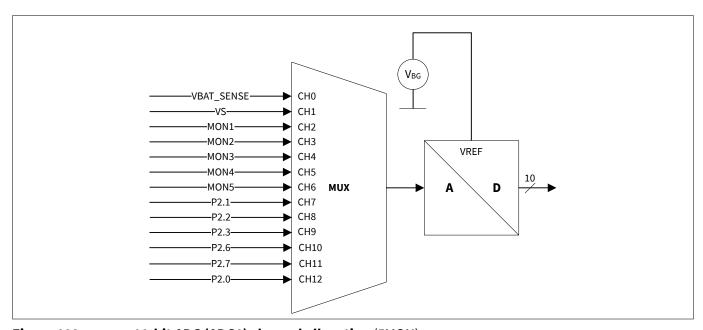

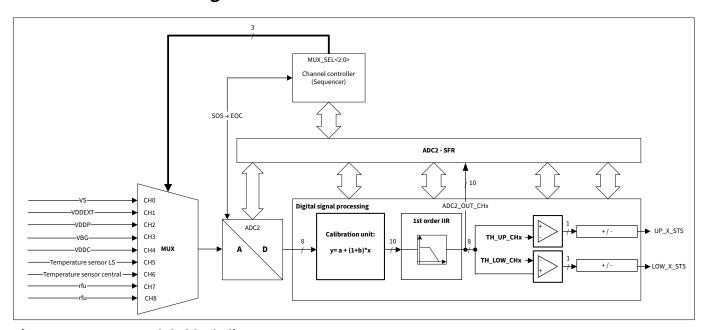

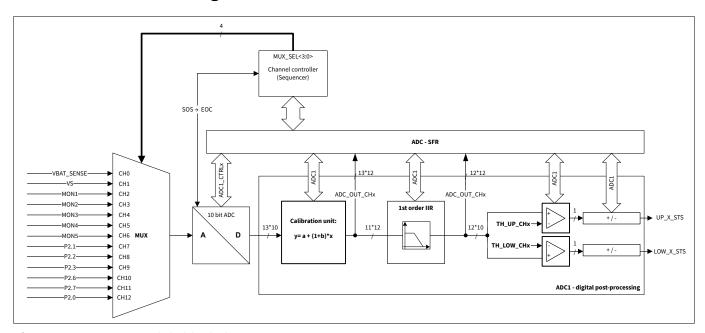

| 22       | Measurement core module (incl. ADC2)                                                           | 376          |

| 22.1     | Features                                                                                       |              |

| 22.2     | Introduction                                                                                   |              |

| 22.2.1   | Block diagram                                                                                  |              |

| 22.2.2   | Measurement core module modes overview                                                         |              |

|          |                                                                                                |              |

## Microcontroller with LIN and power switches for automotive applications

| 22.3     | ADC2 - Core (8-bit ADC)                                                             | 678 |

|----------|-------------------------------------------------------------------------------------|-----|

| 22.3.1   | Functional description                                                              | 678 |

| 22.3.2   | ADC2 control registers                                                              | 678 |

| 22.3.2.1 | Register overview - ADC2 control registers (ascending offset address)               | 679 |

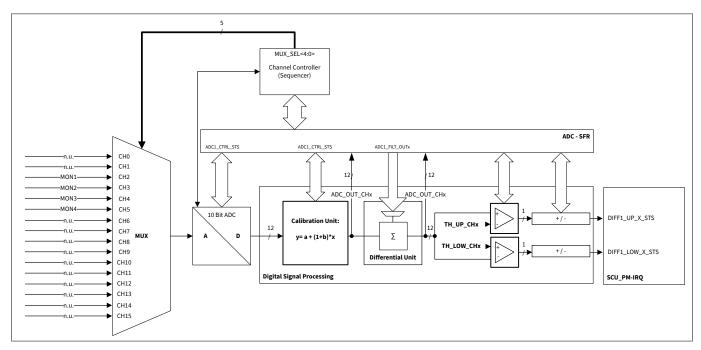

| 22.4     | Channel controller                                                                  | 680 |

| 22.4.1   | Functional description                                                              | 680 |

| 22.4.2   | Channel controller control registers                                                | 682 |

| 22.4.2.1 | Register overview - Channel controller control registers (ascending offset address) | 682 |

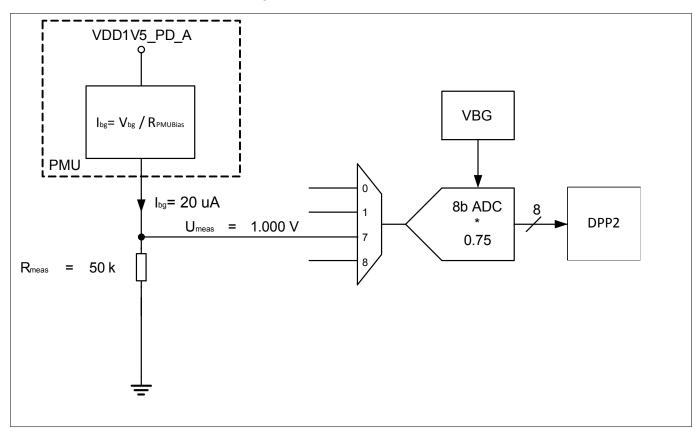

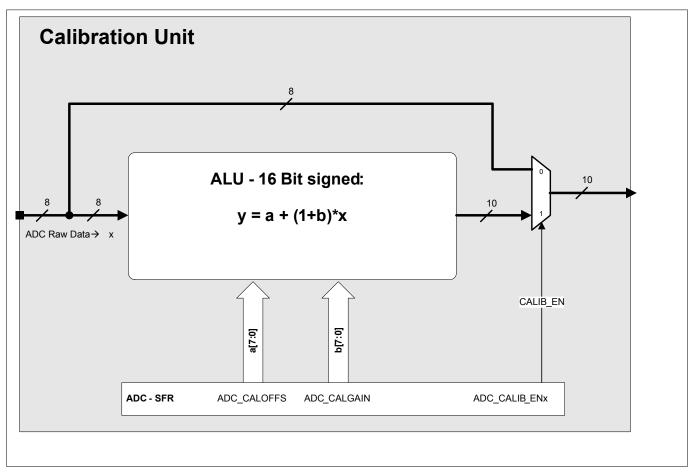

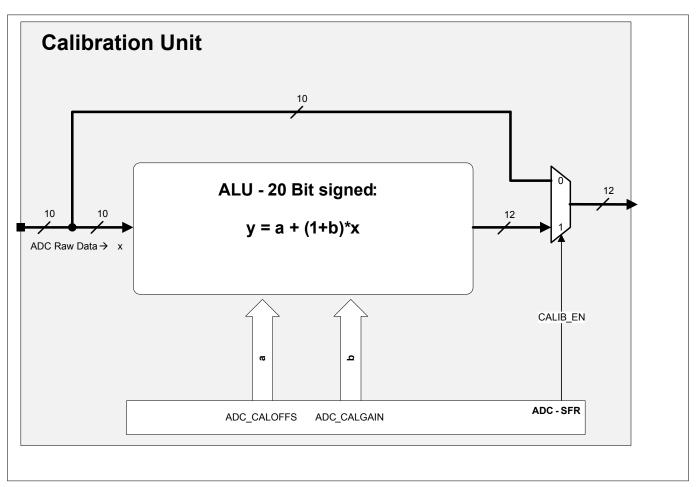

| 22.5     | Calibration unit                                                                    | 683 |

| 22.5.1   | Functional description                                                              | 683 |

| 22.5.1.1 | Method for determining the calibration parameters                                   | 683 |

| 22.5.1.2 | Setup of calibration unit                                                           | 683 |

| 22.5.2   | Calibration unit control registers                                                  | 685 |

| 22.5.2.1 | Register overview - Calibration unit control registers (ascending offset address)   | 685 |

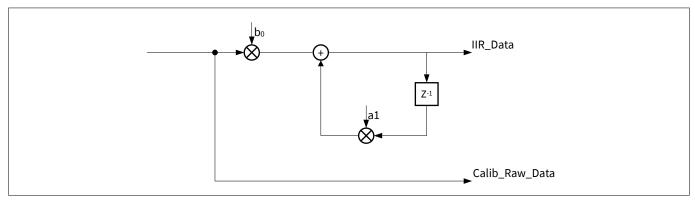

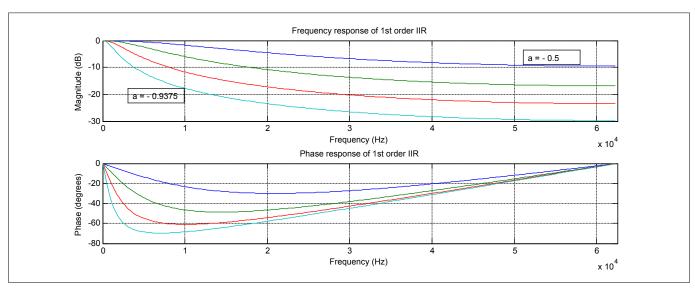

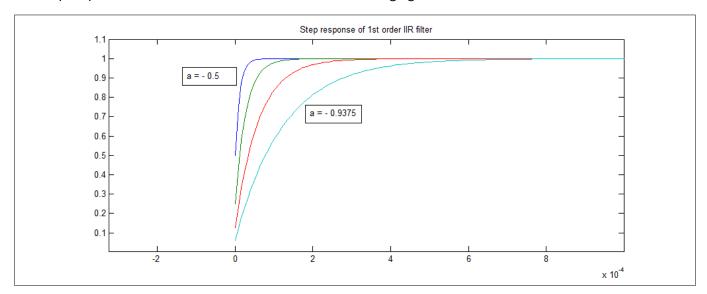

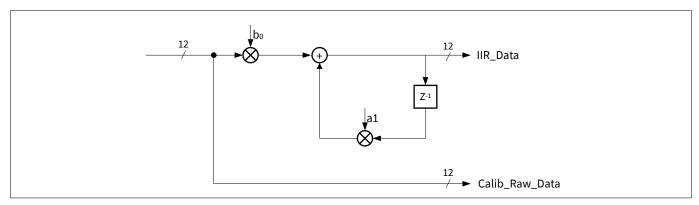

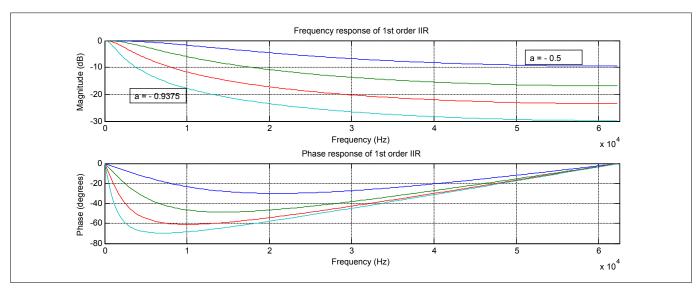

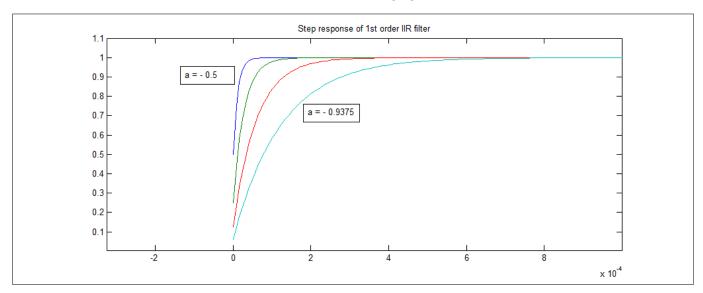

| 22.6     | IIR-filter                                                                          | 686 |

| 22.6.1   | Functional description                                                              | 686 |

| 22.6.1.1 | Step response                                                                       | 687 |

| 22.6.2   | IIR filter control registers                                                        | 688 |

| 22.6.2.1 | Register overview - IIR filter control registers (ascending offset address)         | 688 |

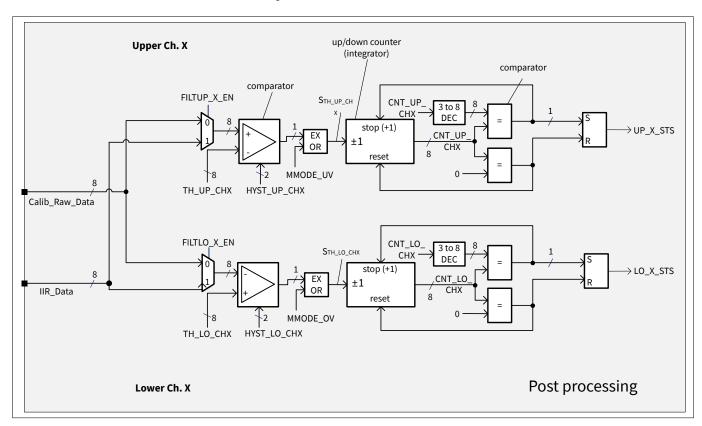

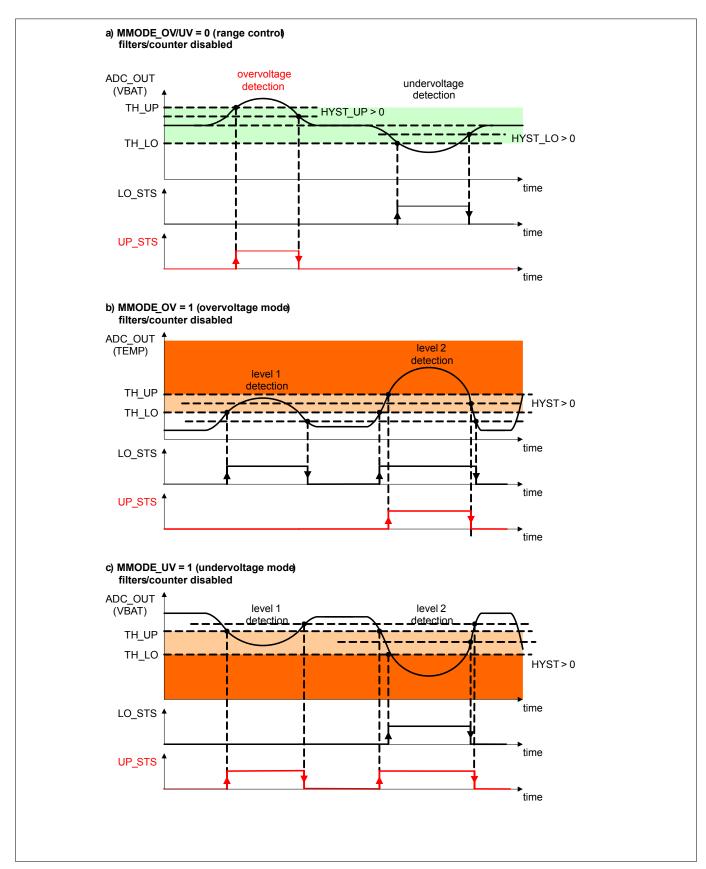

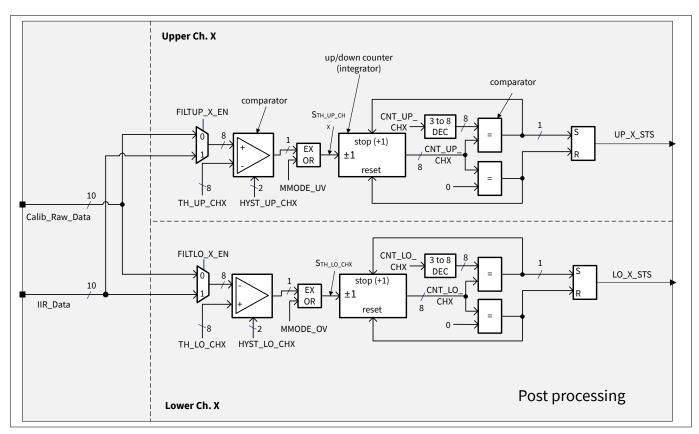

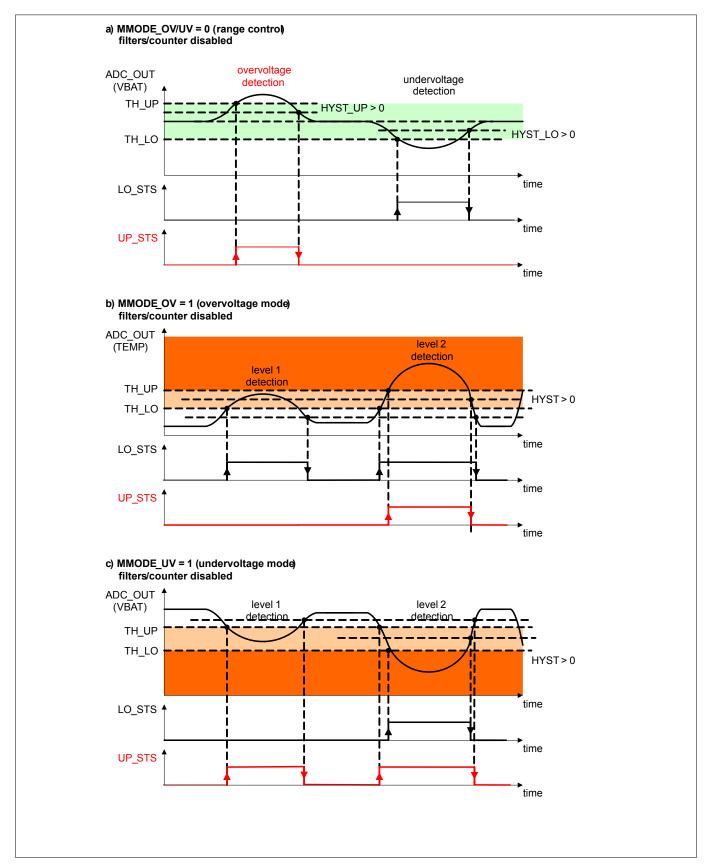

| 22.7     | Signal processing                                                                   |     |

| 22.7.1   | Functional description                                                              |     |

| 22.7.2   | Postprocessing control registers                                                    |     |

| 22.7.2.1 | Register overview - Postprocessing control registers (ascending offset address)     |     |

| 22.8     | Start-up behavior after reset                                                       |     |

| 22.9     | Post processing default values                                                      |     |

| 22.10    | Measurement core module (incl. ADC2) register definition                            |     |

| 22.10.1  | Register address space - ADC2                                                       |     |

| 22.10.2  | Registers overview - ADC2 (sorted by name)                                          |     |

| 22.10.3  | ADC2 control and status register                                                    |     |

| 22.10.4  | ADC2 HV status register                                                             |     |

| 22.10.5  | Sequencer feedback register                                                         |     |

| 22.10.6  | Channel settings bits for exceptional interrupt measurement register                |     |