Document Number:AN4850 Rev 1, Mar 2014

# Getting Started with Qorivva Fast Start Kit for TRK-MPC5606B

by: Sudhakar Srinivasa

# **1** Introduction

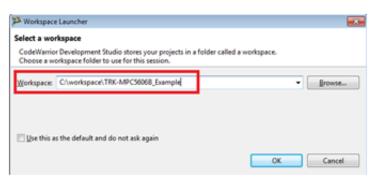

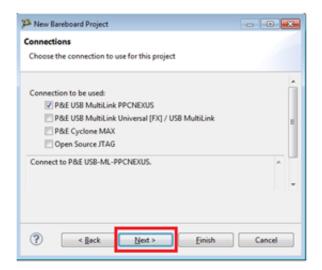

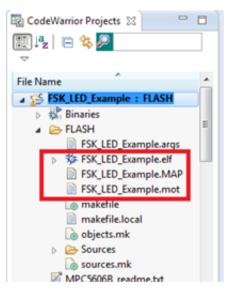

This application note provides an overview of software tools provided with the Fast Start Kit for the <u>TRK-MPC5606B</u>. The application note also provides an example to use the software tools included in the Fast Start Kit. The example software application uses:

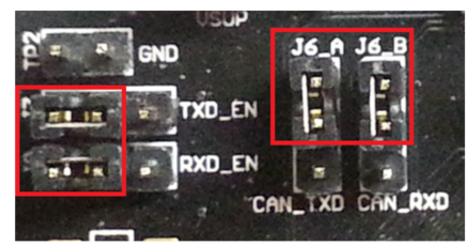

- RAppID init tool for configuring microcontroller and for auto generation of the initialization code

- CodeWarrior Development Studio for Microcontrollers v10.5 for building the project

- RAppID Boot loader for programming the code on to the target

- FreeMASTER utility for monitor and debug purposes

### 2 Overview of Qorivva Fast Start Kit for TRK-MPC5606B

The Fast Start Kit for TRK-MPC5606B contains TRK-MPC5606B evaluation board and many Freescale's software tools to help you get started with your application development. The software tools consist of:

- RAppID initialization tool,

- CodeWarrior Development Studio v10.5 (Special Edition),

- RAppID Boot loader utility,

- FreeMASTER utility,

© 2014 Freescale Semiconductor, Inc.

#### Contents

| 2 Overview of Qorivva Fast Start Kit for TRK-                  |    |

|----------------------------------------------------------------|----|

| MPC5606B                                                       | 1  |

| 3 Using RAppID tool to configure<br>MPC5606B and generate code | 3  |

| 4 Build code using CodeWarrior                                 | 28 |

| 5 Flash code                                                   | 37 |

| 6 Test code                                                    | 41 |

| 7 Conclusion                                                   | 45 |

#### overview of Qorivva Fast Start Kit for TRK-MPC5606B

- CodeWarrior Project Maker utility to add RAppID generated source code to an empty CodeWarrior project,

- Driver code for the MPC5606B,

- Example projects to help you to get started with the Fast Start Kit.

An overview of some of the software tools provided with Fast Start Kit is described below.

# 2.1 RAppID Init overview

RAppID Init is a family of graphical development tools for Freescale's MPC56xx Qorivva microcontrollers that enable the user to quickly and easily configure the microcontroller and generate complete initialization code and documentation. It is also a learning tool that can help gain understanding of the microcontroller and its peripherals. Some of the product highlights include:

- Intuitive, easy-to-use graphical user interface (GUI)

- Comprehensive initialization of the CPU, memory and peripherals

- · Automatic DMA register setting from peripherals for basic modes

- · Built-in consistency checks to minimize incorrect settings

- Automatic report generation of settings

- Efficient C and assembly code generation for compilers from companies such as Wind River<sup>®</sup>, Green Hills<sup>®</sup> and CodeWarrior

- Online documentation and built-in tool tips

- Installation comes with many example projects

- · Generates complete infrastructure code for MCU startup

- Provisions for revision management

- Automatic date and time stamps on generated code and reports

- Modular code generation generate code for any or all peripherals

- Option to generate code for RAM or Flash

- Flexible Initialization sequence

- · Project import/export capability for distributed development teams

- Wizards for eMIOS initialization and function settings

# 2.2 RAppID Boot Loader utility

The RAppID Boot Loader tool is developed by Freescale and helps you develop software for Freescale microcontrollers by providing a method to update software of these microcontrollers through a serial link. The RAppID Boot Loader works with the built-in Boot Assist Module (BAM) included in the Freescale's Qorivva family of parts. The Boot Loader provides a streamlined method for programming code into FLASH or RAM on either target EVBs or custom boards. The Boot Loader has two modes of operation; for use as a stand-alone PC desktop GUI utility, or for integration with different user required tools chains through a command line interface (i.e. Eclipse Plug-in, MatLab/SimuLink etc.).

# 2.3 FreeMASTER utility

FreeMASTER is a user-friendly real-time debug monitor and data visualization tool for application development and information management. FreeMASTER supports completely non-intrusive monitoring of variables on a running system. You can display multiple variables changing over time on an oscilloscope-like display, or view the data in text form.

### 2.4 Low-level and high-level drivers

The Fast Start Kit for TRK-MPC5606B includes low-level and high-level drivers to help make the application development easier. The included drivers are for peripherals ADC, GPIO, UART, and CAN. The high level drivers included are for the Potentiometer, Photo Sensor, and System Basis Chip (SBC) that are on the TRK-MPC5606B board.

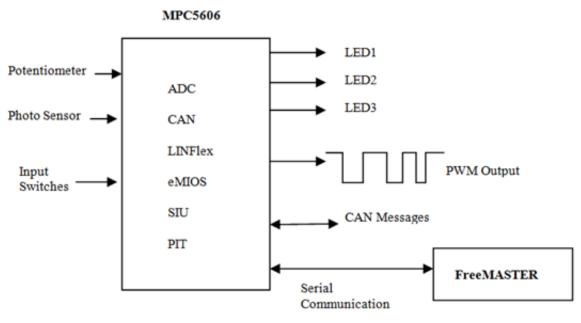

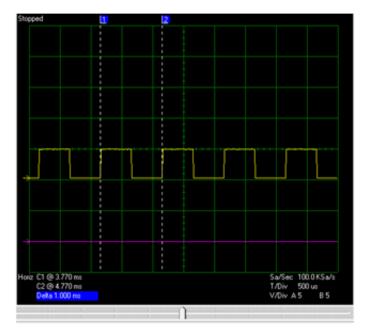

# 2.5 Overview of example application

The example provided in this application note demonstrates the software tools provided with the Fast Start Kit and makes use of the input buttons, LEDs, and analog inputs provided in the TRK-MPC5606B evaluation board. This example uses multiple peripherals on the MPC5606B microcontroller like ADC, SIU, PIT, eMIOS, LINFlex (UART), and CAN. The example project turns on/off the LEDs based on different input commands:

- LED1 is turned on/off based on Potentiometer input value

- · LED2 is turned on/off based on Photo sensor input value

- LED3 is turned on/off based on CAN command

- LED4 is driven by PWM signal where the duty cycle of PWM output can be increased by input pressing button S3 and decreased by pressing input button S4.

The application communicates with FreeMASTER utility via UART and monitor variables used in the example project.

The next few sections in this application note describe the steps to configure microcontroller, generate code, and build and run a simple project on TRK-MPC5606B target. The figure below depicts the example software in a block diagram.

Figure 1. Block diagram of example application

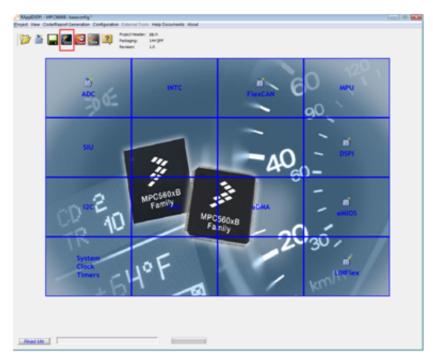

# 3 Using RAppID tool to configure MPC5606B and generate code

This section describes the steps to configure MPC5606B microcontroller and generate initialization code for the example project using the RAppID tool.

# 3.1 Pin configuration

The table below shows TRK-MPC5606B board pin connections for the features used in the example project

### Table 1. TRK-MPC5606B Pin connections used in example project

| Feature       | Pin  | Comments                                           |

|---------------|------|----------------------------------------------------|

| Potentiometer | PB4  | ADC input - ANP0                                   |

| Photo Sensor  | PB5  | ADC input ANP1                                     |

| UART Tx       | PB2  | Connected to virtual serial port Tx                |

| UART Rx       | PB3  | Connected to virtual serial port Rx                |

| Switch S1     | PE0  | Not used in this example                           |

| Switch S2     | PE1  | Not used in this example                           |

| Switch S3     | PE2  | Used to increment duty cycle of LED4<br>PWM signal |

| Switch S4     | PE3  | Used to decrement duty cycle of LED4<br>PWM signal |

| LED 1         | PE4  | Turns on/off based on Potentiometer input value    |

| LED 2         | PE5  | Turns on/off based on Photo sensor input value     |

| LED 3         | PE6  | Turns on/off based on CAN message                  |

| LED 4         | PE7  | Output driven by PWM signal                        |

| CAN Tx        | PC10 | Connected to CAN1 Tx via SBC                       |

| CAN Rx        | PC11 | Connected to CAN1 Rx via SBC                       |

The Pin configuration table above shows the relevant pin connection for the functions you will use in this project. You will use the RAppID tool to configure the pins and peripherals for this project.

To create, configure, and generate code for the project using RAppID Init:

1. Double-click the RAppID desktop icon to launch the RAppID application.

Figure 2. RAppID desktop icon

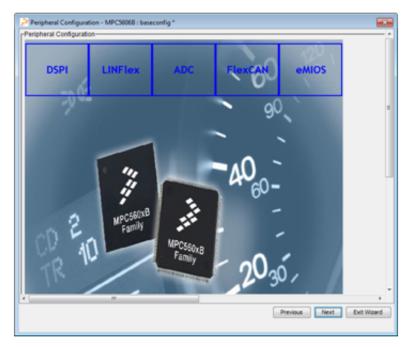

The RAppID window appears.

Using RAppID tool to configure MPC5606B and generate code

Figure 3. RAppID main window

2. Click the new project wizard button to start a new project.

### 3.2 Select part and package

1. Select *MPC5606B* and click the **Start Wizard** button.

| art Selection-    |      |                  |            |          |  |

|-------------------|------|------------------|------------|----------|--|

| Part              | Core | Max. Speed (MHz) | Flash (KB) | RAM (KB) |  |

| MPC5601D          | z0   | 48               | 128        | 12       |  |

| MPC5602D          | 20   | 48               | 256        | 16       |  |

| MPC56058          | z0h  | 64               | 768        | 64       |  |

| @ MPC56068        | z0h  | 64               | 1024       | 80       |  |

| MPC56078          | z0h  | 64               | 1536       | 96       |  |

|                   |      |                  |            |          |  |

|                   |      |                  |            |          |  |

|                   |      |                  |            |          |  |

|                   |      |                  |            |          |  |

| Load existing pro | ject |                  |            |          |  |

|                   |      |                  | 1          |          |  |

### Figure 4. Part selection

2. Select the *144 QFP* package and click the **Next** button.

using RAppID tool to configure MPC5606B and generate code

| Package Selection - MPC5606B : baseconfig *                                                                                                                                                                                                                                                                                                                      |                           | × |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---|

| Package Selection<br>208 BGA *<br>176 QFP<br>100 QFP<br>64 QFP<br>*Because of an order from the United States International Trade Commission, BGA-packaged product lines and part numbers indicated here currently are not available from Freescale for import or sale in the United States prior to September 2010: MPC560x8/C products in 208 MAPBGA packages. |                           |   |

| [                                                                                                                                                                                                                                                                                                                                                                | Previous Next Exit Wizard | כ |

Figure 5. Package selection

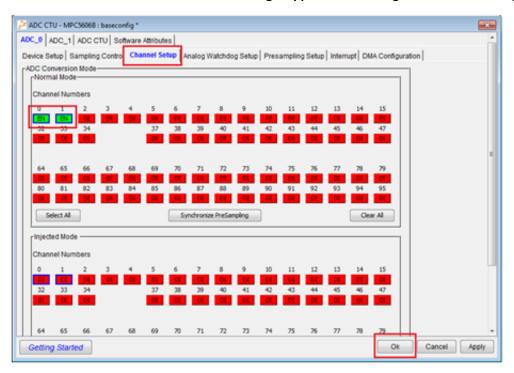

# 3.3 Configure ADC pins

In TRK-MPC5606B, the potentiometer is connected to input ANPO (PB4) and the photo sensor is connected to ANP1 (PB5).

To configure ADC inputs:

- 1. Select the ADC tab in the Pin Allocation window.

- 2. Select PB4 and PB5 as inputs and enter the user signal names as shown below.

| Pin Allocation - MPC56068 : baseco | nlig* |        |                                                                                                                                                                                                                                                                                                  |     |

|------------------------------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Pin Allocation Wzard-              |       |        |                                                                                                                                                                                                                                                                                                  |     |

|                                    |       |        | TOX PAD IHIB Allocated as Input<br>THIS RAU THIB Allocated as Input<br>TOX PAD CR Allocated as Drut<br>TOX PAD CR Allocated as Drut<br>PAS PAD PAB Allocated as Drut<br>PAS PAD PAB Allocated as Drut<br>ALC0_CC_1 MP 1 PAD PBS Allocated as Drut<br>ADC_0_RAUC_1 MP 1 PAD PBS Allocated as Drut |     |

| Functions                          | Input | Output | User Assigned Signal Name                                                                                                                                                                                                                                                                        |     |

| ADC_0_ADC_1 ANP 0                  | 2.704 |        | AVPO_Potentiometer_input                                                                                                                                                                                                                                                                         |     |

| ADC_0_ADC_1 ANP 1                  | 2 P65 |        | AVP1_PhotoSensor_input                                                                                                                                                                                                                                                                           |     |

| ADC_0_ADC_1 ANP 2                  | 766   |        | WY LOTIONOPHIC INPUT                                                                                                                                                                                                                                                                             |     |

| ADC_0_ADC_1 ANP 3                  | E #67 |        |                                                                                                                                                                                                                                                                                                  |     |

| ADC 0 ADC 1ANP 4                   | P P00 |        |                                                                                                                                                                                                                                                                                                  |     |

| 1                                  | =     |        |                                                                                                                                                                                                                                                                                                  |     |

|                                    |       |        | Previous Next Exit Waard                                                                                                                                                                                                                                                                         | Ven |

### Figure 6. Configure ADC pins

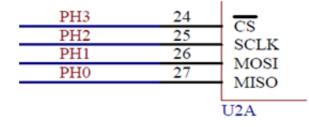

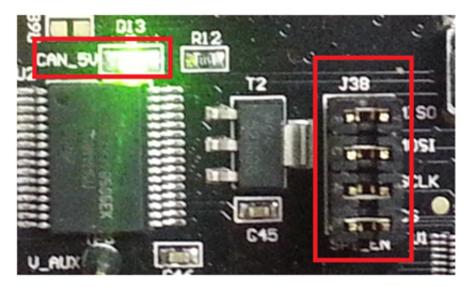

### 3.4 Configure DSPI pins

TRK-MPC5606B contains MCZ3390S5EK system basis chip (SBC) with integrated CAN transceiver and LIN 2.0 interface. Since DSPI 1 of the MPC5606B is connected to SBC, you can use the DSPI 1 peripheral to configure the SBC and enable CAN communication by sending appropriate commands via DSPI 1.

The figure below shows the connections between the SBC and DSPI 1 peripheral.

### Figure 7. Connection between SBC and DSPI 1

Configure DSPI 1 pins PH3, PH2, PH1, and PH0 using RAppID as shown below.

| N817050216                                                                                    | <u></u>                         |                                                 | 94 000000000000000000000000000000000000 |             |

|-----------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------|-----------------------------------------|-------------|

| 2 2 2 2 2 2 2 2                                                                               | END COLUMPER MISC CANOS         |                                                 |                                         | formal Name |

| ADC 0591 FlexC4V CORD                                                                         | Input                           | Output                                          | User Assigned                           |             |

|                                                                                               | Input<br>E PA6                  | 04put                                           | User Assigned                           |             |

| Functions                                                                                     |                                 | E PA6 E PO14 E PF6                              | User Assgred                            |             |

| Punctions<br>SPI_1 Chip Select 1<br>SPI_1 Chip Select 0                                       | E PAS                           | E PA6 E PO14 E PF6                              |                                         | put         |

| Functions<br>SEPI_1 Chip Select 1                                                             | PA6<br>PA4 EPC3 EPE5 EP013 EPH3 | PA6 P014 PF6                                    | 2 PH3_DSPI1_CS0_Outp                    | put put     |

| Punctions<br>SPI_1 Chip Select 1<br>SPI_1 Chip Select 0<br>SPI_1 Chip Select 0<br>SPI_1 Chick | PA6<br>PA4 EPC3 EPE5 EP013 EPH3 | PA6 P034 PP6<br>PA4 PC3 PE5 P013<br>PE4 PC2 PE2 | PH3_DSP11_CS0_OVp<br>PH2_DSP11_CLK_OVp  | put put put |

Figure 8. Configure DSPI 1 pins

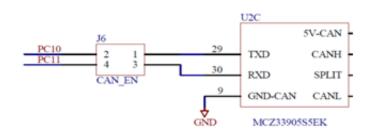

### 3.5 Configure FlexCAN pins

The CAN TX and CAN RX pins of the SBC are connected to the pins PC10 and PC11 of CAN 1 peripheral of the microcontroller as shown in the figure below.

### Figure 9. CAN TX and CAN RX pins of SBC connected to pins PC10 and PC11

Configure FlexCAN 1 pins PC10 and PC11 using RAppID as shown below.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ordig " |       | TCCFAD PH9 Allocated as Input<br>TCCFAD PH9 Allocated as Input<br>TCF PAD PC0 Allocated as Input<br>TCF PAD PC0 Allocated as Input<br>PAD PAD PAB Allocated as Input<br>PAD PAD PAB Allocated as Input<br>ACC_0_ACC_1 APP 0 PAD PH4 Allocated as Input<br>ACC_0_ACC_1 APP 0 PAD PH4 Allocated as Input<br>DSPL 1 Obj Select 0 PAD PH4 Allocated as Input<br>DSPL 1, 1 Obj Select 0 PAD PH4 Allocated as Output<br>DSPL 1, 1 Obj Select 0 PAD PH4 Allocated as Output<br>DSPL 1, 1 Obj Select 0 PAD PH4 Allocated as Output<br>DSPL 1, 1 Obj Select 0 PAD PH4 Allocated as Input<br>OSPL 1, 1 Obj Select 0 PAD PH4 Allocated as Input<br>OSPL 1, 1 Obj Select 0 PAD PH4 Allocated as Input<br>CAN_1 The PAD PH2 Allocated as Input<br>CAN_1 The PAD PC11 Allocated as Input |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| NOC DSP FlexCAN Case 12<br>Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Input   |       | User Assigned Signal Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| RUE DEPENDENT CAN CONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | Ovput |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 | Input   |       | PC10_CAN1_Tx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| RUE DEPENDENT CAN CONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Input   | Ovput | PC10_CAN1_Tr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

Figure 10. Configure FlexCAN pins

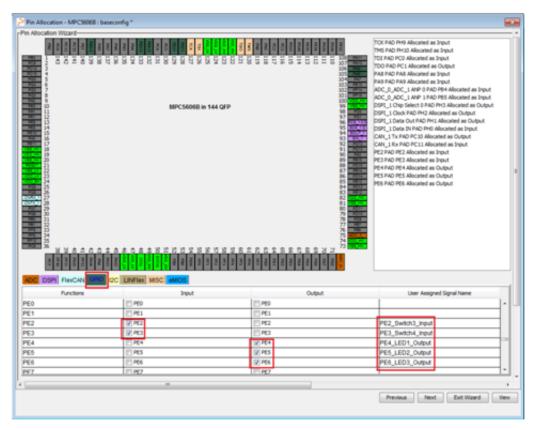

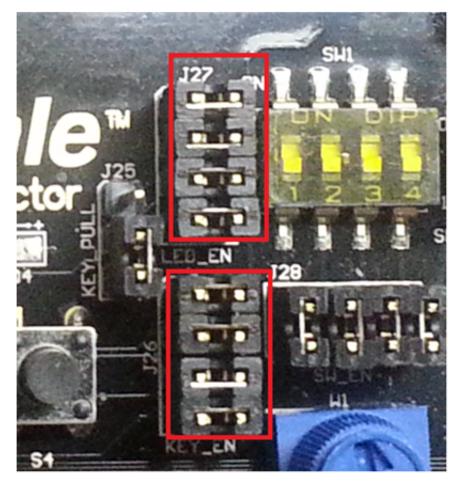

# 3.6 Configure GPIO pins

In this example, you use Switch S3 and S4 as inputs and LED1, LED2, and LED3 as general purpose outputs. The switches S3 and S4 are connected to PE2 and PE3 pins of the microcontroller and LED1, LED2, and LED3 are connected to PE4, PE5, and PE6 pins of microcontroller. Configure GPIO pins using RAppID as shown below.

Figure 11. Configure GPIO pins

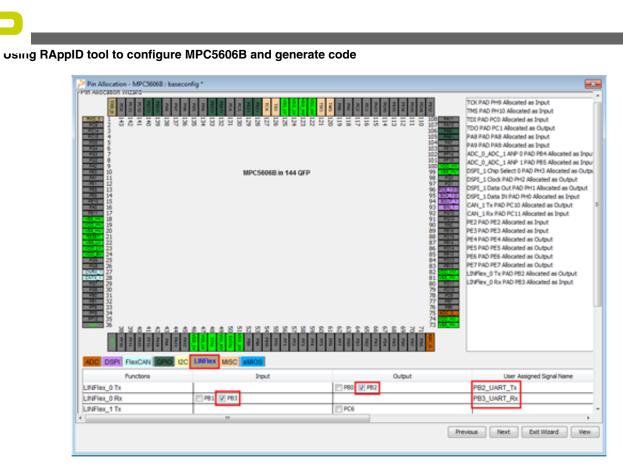

# 3.7 Configure LINFlex (UART) pins

In this example, use the virtual serial port of TRK-MPC5606B board for serial communication. The PB2 and PB3 pins of microcontroller in TRK-MPC5606B board are connected to TX and RX pins of virtual serial port. Configure LINFlex 0 pins using RAppID as shown below.

Figure 12. Configure LINFlex (UART) pins

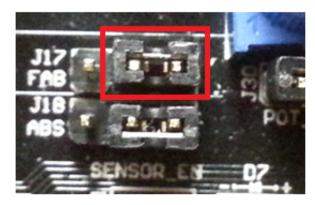

# 3.8 Configure eMIOS pins

Use LED4 as PWM output in this example. LED4 is connected to PE7 pin of the microcontroller. Configure eMIOS function and pin using RAppID as shown below.

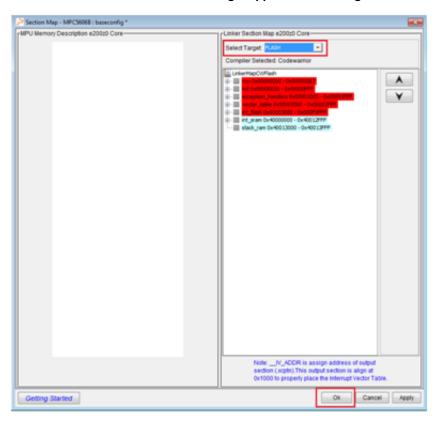

Using RAppID tool to configure MPC5606B and generate code

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 8 9 1 1 2 1 1 2 1 1 2 1 1 2 1 1 2 1 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 1 2 1 1 | 200<br>200<br>200<br>200<br>200<br>200<br>200<br>200<br>200<br>200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TO THO PC3 MICRIME as Curput<br>PAI PIAD PIAB Allocated as Tipust<br>PAI PIAD PIAB Allocated as Tipust<br>ACC_B_ADCL_1 ANP 9 TAID PIB4 Allocated as Tipust<br>ACC_B_ADCL_1 ANP 9 TAID PIB4 Allocated as Tipust<br>DSPL_1 Disk Delete 1PAD PIB4 Allocated as Curput<br>DSPL_1 Disk DVAD PI12 Allocated as Curput<br>DSPL_1 Disk DVAD PI12 Allocated as Curput<br>CAL_1 TI: PIAD PC23 Allocated as Curput<br>CAL_1 TI: PIAD PC23 Allocated as Tipust<br>PC3 PIAD PI22 Allocated as Tipust<br>PC3 PIAD PI22 Allocated as Tipust<br>PC3 PIAD PI22 Allocated as Tipust<br>PC3 PIAD PC3 Allocated as Tipust<br>PC3 PIAD PC4 Allocated as Topust<br>PC3 PIAD PC4 Allocated as Topust<br>PC4 PIAD PC4 Allocated as Topust<br>PC4 PIAD PC4 Allocated as Topust<br>PC5 PIAD PC5 Allocated as Topust<br>PC5 PIAD PC6 Allocated as Topust |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| AL NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| OC DSPI Flex<br>Oarnel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5 |

| Cite Control C | Punctions<br>Default Mode<br>Default Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Output User Assigned Signal Riame PES PEB PEB PFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| CC DSPI Flax<br>Channel<br>MIDS_0 C+C21<br>MIDS_0 C+C22<br>MIDS_0 C+C22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Punctions<br>Default Mode<br>Default Mode<br>Output Pulse Width and Prequency Modulation Buffered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pps PPS - | Output         User Assigned Signal Name           PDS         PDS           PDS         PDS           PDS         PDS           PDS         PDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |