# Tsi721<sup>™</sup> Datasheet

April 4, 2016

## **Table of Contents**

|    | Abo  | out this Document                   | 6 |  |  |  |  |

|----|------|-------------------------------------|---|--|--|--|--|

|    |      | Overview                            |   |  |  |  |  |

|    |      | Document Conventions                |   |  |  |  |  |

|    |      | Revision History                    | 7 |  |  |  |  |

| 1. | Dev  | vice Overview                       |   |  |  |  |  |

|    | 1.1  | Overview                            |   |  |  |  |  |

|    | 1.2  | Features                            |   |  |  |  |  |

|    |      | 1.2.1 PCIe Features                 |   |  |  |  |  |

|    |      | 1.2.2 S-RIO Features                |   |  |  |  |  |

|    |      | 1.2.3 Bridging Features             |   |  |  |  |  |

|    |      | 1.2.4 Messaging Features            |   |  |  |  |  |

|    |      | 1.2.5 Block DMA Engine Features     |   |  |  |  |  |

|    |      | 1.2.6 Miscellaneous Features        |   |  |  |  |  |

|    | 1.3  | Block Diagram                       |   |  |  |  |  |

|    |      | 1.3.1 PCIe Interface                |   |  |  |  |  |

|    |      | 1.3.2 S-RIO Interface               |   |  |  |  |  |

|    |      | 1.3.3 Messaging Engine              |   |  |  |  |  |

|    |      | 1.3.4 Mapping Engine                |   |  |  |  |  |

|    |      | 1.3.5 Block DMA Engine              |   |  |  |  |  |

|    | 1.4  | Typical Applications                |   |  |  |  |  |

|    |      | 1.4.1 Defense/Aerospace Application |   |  |  |  |  |

|    |      | 1.4.2 Video and Imaging Application |   |  |  |  |  |

|    |      | 1.4.3 Wireless Application          |   |  |  |  |  |

| 2. | Sigr | nals                                |   |  |  |  |  |

|    | 2.1  | Overview                            |   |  |  |  |  |

|    | 2.2  | Ballmap                             |   |  |  |  |  |

|    | 2.3  | Pinlist                             |   |  |  |  |  |

|    | 2.4  | PCIe Signals                        |   |  |  |  |  |

|    | 2.5  | S-RIO Signals                       |   |  |  |  |  |

|    | 2.6  | General Signals                     |   |  |  |  |  |

|    | 2.7  | I2C Signals                         |   |  |  |  |  |

|    | 2.8  | JTAG and Test Interface Signals     |   |  |  |  |  |

|    | 2.9  | GPIO Signals                        |   |  |  |  |  |

|    | 2.10 | Power-up Signals                    |   |  |  |  |  |

|    | 2.11 |                                     |   |  |  |  |  |

| 3. | Flee | ectrical Characteristics            |   |  |  |  |  |

| 5. | 3.1  | Absolute Maximum Ratings            |   |  |  |  |  |

|    | 3.2  | Recommended Operating Conditions    |   |  |  |  |  |

|    | 3.3  | Power Consumption                   |   |  |  |  |  |

|    | 0.0  | i oner consumption                  |   |  |  |  |  |

|    | 3.4 | Power  | Supply Sequencing                            |    |

|----|-----|--------|----------------------------------------------|----|

|    |     | 3.4.1  | Power-Up Sequencing                          |    |

|    |     | 3.4.2  | Power-Down Sequencing                        |    |

|    | 3.5 | DC Op  | erating Characteristics                      |    |

|    | 3.6 | Decou  | oling Recommendation                         |    |

|    | 3.7 | AC Tim | ning Specifications                          |    |

|    |     | 3.7.1  | PCIe Differential Receiver Specifications    |    |

|    |     | 3.7.2  | PCIe Differential Transmitter Specifications |    |

|    |     | 3.7.3  | RapidIO SerDes Characteristics               |    |

|    |     | 3.7.4  | Level I Long Run Transmitter Specifications  |    |

|    |     | 3.7.5  | Reference Clocks – PCCLKP/N and REFCLKP/N    |    |

|    |     | 3.7.6  | JTAG and Test Interface Signal Timings       |    |

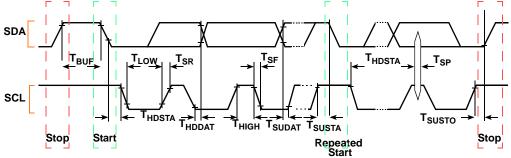

|    |     | 3.7.7  | I2C Interface Signal Timings                 |    |

|    |     | 3.7.8  | GPIO Interface Signal Timings                |    |

|    |     | 3.7.9  | RSTn Signal Timings                          |    |

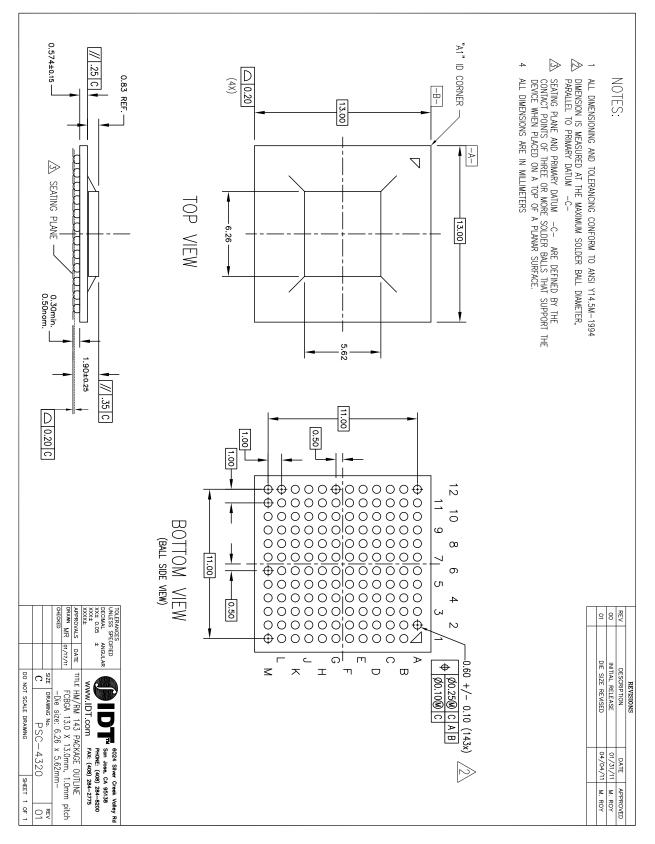

| 4. | Pac | kage S | Specifications                               | 62 |

|    | 4.1 |        | je Dimensions                                |    |

|    | 4.2 | Packad | je Diagrams                                  |    |

|    | 4.3 |        | al Characteristics                           |    |

|    | 4.4 |        | re Sensitivity                               |    |

| 5. | Ord | ering  | Information                                  | 65 |

## **List of Figures**

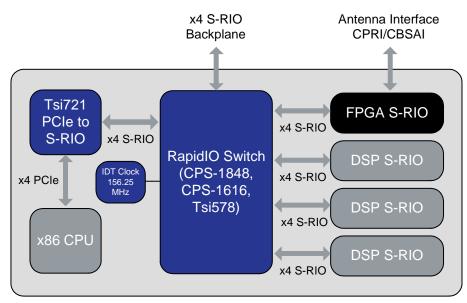

| Figure 1:  | Block Diagram                                       | . 12 |

|------------|-----------------------------------------------------|------|

| Figure 2:  | Defense/Aerospace Application                       | . 14 |

| Figure 3:  | Video and Imaging Application                       | . 15 |

| Figure 4:  | Wireless Application                                | . 16 |

| Figure 5:  | Ballmap                                             | . 18 |

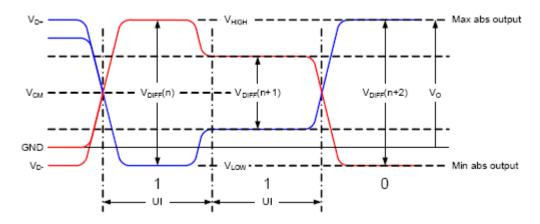

| Figure 6:  | S-RIO Definition of Transmitter Amplitude and Swing |      |

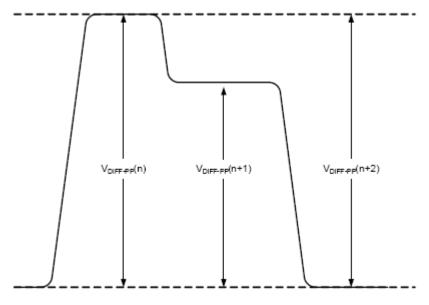

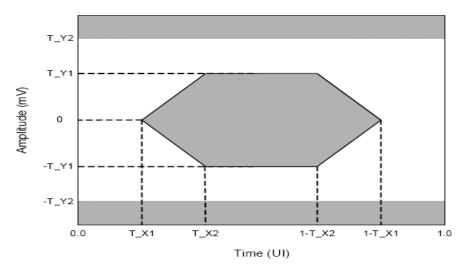

| Figure 7:  | S-RIQ Transition Symbol Transmit Eve Mask           | . 44 |

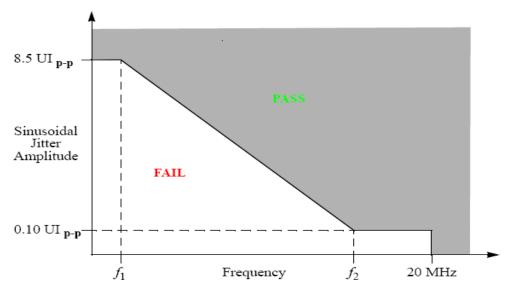

| Figure 8:  | S-RIO Single Frequency Sinusoidal Jitter Limits     | . 46 |

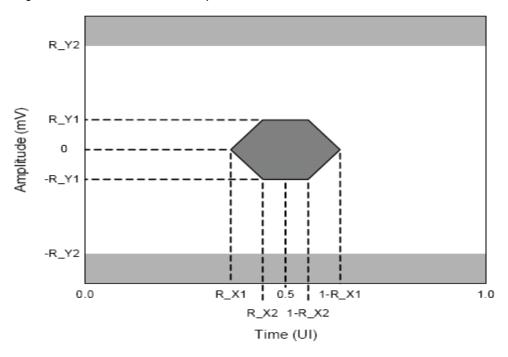

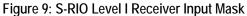

| Figure 9:  | S-RIO Level I Receiver Input Mask                   | . 47 |

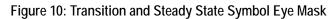

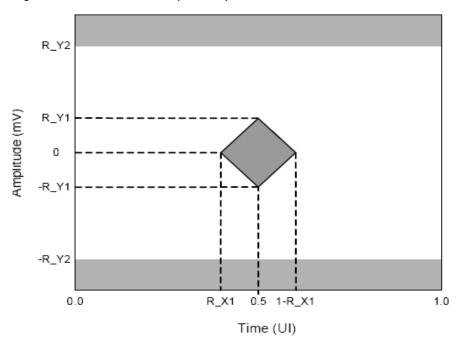

| Figure 10: | Transition and Steady State Symbol Eye Mask         |      |

| Figure 11: | Level II Receiver Input Compliance Mask             | . 56 |

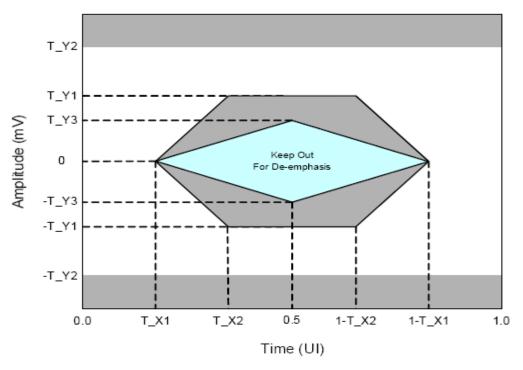

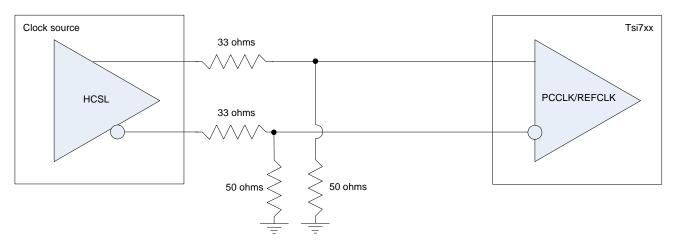

|            | HCSL to REFCLKP/N / PCCLKP/N                        |      |

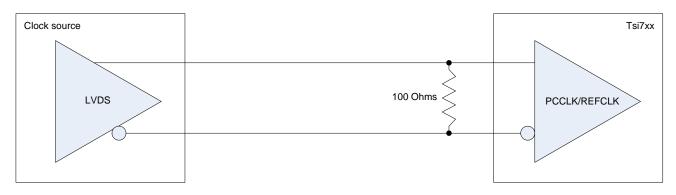

| Figure 13: | LVDS to REFCLKP/N / PCCLKP/N                        | . 58 |

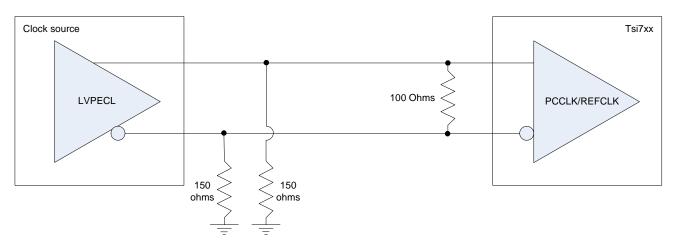

| Figure 14: | LVPECL to REFCLKP/N / PCCLKP/N                      | . 58 |

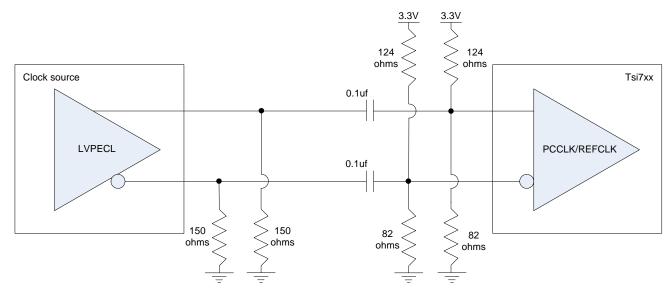

|            | LVPECL to REFCLKP/N / PCCLKP/N                      |      |

| Figure 16: | I2C Interface Signal Timings                        | . 60 |

| Figure 17: | Package Diagrams                                    | . 63 |

## **List of Tables**

| Table 1:  | Signal Types                                                                       |  |

|-----------|------------------------------------------------------------------------------------|--|

| Table 2:  | PCIe Signals                                                                       |  |

| Table 3:  | S-RIO Signals                                                                      |  |

| Table 4:  | General Signals                                                                    |  |

| Table 5:  | I2C Signals                                                                        |  |

| Table 6:  | JTAG Interface Signals                                                             |  |

| Table 7:  | GPIO Signals                                                                       |  |

| Table 8:  | GPIO Mapping to Power-up Signals                                                   |  |

| Table 9:  | Power-Up Signals                                                                   |  |

| Table 10: | Power Supply Signals                                                               |  |

| Table 11: | Absolute Maximum Ratings                                                           |  |

| Table 12: | Recommended Operating Conditions                                                   |  |

| Table 13: | Power Consumption                                                                  |  |

| Table 14: | Power Supply Sequencing Ramp Times                                                 |  |

| Table 15: | 3.3V LVTTL DC Operating Characteristics at Recommended Operating Condition of 3.3V |  |

| Table 16: | 2.5V LVTTL DC Operating Characteristics at Recommended Operating Condition of 2.5V |  |

| Table 17: | Decoupling Recommendation                                                          |  |

| Table 18: | PCIe Differential Receiver Specifications                                          |  |

| Table 19: | PCIe Differential Transmitter Specifications                                       |  |

| Table 20: | Level I Short Run Transmitter AC Timing Specifications                             |  |

| Table 21: | Level I Long Run Transmitter AC Timing Specifications                              |  |

| Table 22: | Level I Near-End (Tx) Template Intervals                                           |  |

| Table 23: | Level I Receiver Electrical Input Specifications                                   |  |

| Table 24: | Level I Receiver Input Jitter Tolerance Specifications                             |  |

| Table 25: | Level I Far-End (Rx) Template Intervals                                            |  |

| Table 26: | Level II Short Run Transmitter Output Electrical Specifications                    |  |

| Table 27: | Level II Medium Run Transmitter Output Electrical Specifications                   |  |

| Table 28: | Level II Medium Run Near-End (Tx) Template Intervals                               |  |

| Table 29: | Level II Short Run Receiver Electrical Input Specifications                        |  |

| Table 30: | Level II MR Receiver Electrical Input Specifications                               |  |

| Table 31: | Level II Far-End (Rx) Template Intervals                                           |  |

| Table 32: | PCCLKP/N and REFCLKP/NClock Electrical Characteristics                             |  |

| Table 33: | JTAG and Test Interface AC Specifications                                          |  |

| Table 34: | I2C Interface AC Specifications                                                    |  |

| Table 35: | GPIO Interface AC Specifications                                                   |  |

| Table 36: | RSTn Signal AC Specifications                                                      |  |

| Table 37: | Package Dimensions                                                                 |  |

| Table 38: | Junction to Ambient Characteristics – Theta JB/JC                                  |  |

| Table 39: | Junction to Ambient Characteristics – Theta JA                                     |  |

## About this Document

Topics discussed include the following:

- Overview

- Document Conventions

- Revision History

### Overview

The *Tsi721 Datasheet* provides signal, electrical, and packaging information about the Tsi721. It is intended for hardware engineers who are designing system interconnect applications with the device.

### **Document Conventions**

This document uses the following conventions.

#### **Non-differential Signal Notation**

Non-differential signals are either active-low or active-high. An active-low signal has an active state of logic 0 (or the lower voltage level), and is denoted by a lowercase "n". An active-high signal has an active state of logic 1 (or the higher voltage level), and is not denoted by a special character. The following table illustrates the non-differential signal naming convention.

| State       | Single-line signal | Multi-line signal |  |  |

|-------------|--------------------|-------------------|--|--|

| Active low  | NAMEn              | NAMEn[3]          |  |  |

| Active high | NAME               | NAME[3]           |  |  |

#### **Differential Signal Notation**

Differential signals consist of pairs of complement positive and negative signals that are measured at the same time to determine a signal's active or inactive state (they are denoted by "\_p" and "\_n", respectively). The following table illustrates the differential signal naming convention.

| State    | Single-line signal       | Multi-line signal                |

|----------|--------------------------|----------------------------------|

| Inactive | NAME_p = 0<br>NAME_n = 1 | NAME_p[3] = 0<br>NAME_n[3] = 1   |

| Active   | NAME_p = 1<br>NAME_n = 0 | NAME_p[3] is 1<br>NAME_n[3] is 0 |

### **Object Size Notation**

- A byte is an 8-bit object.

- A PCIe word is a 16-bit object.

- A PCIe doubleword (DW) is a 32-bit object.

- · An S-RIO word is a 32-bit object.

- An S-RIO doubleword (Dword) is a 64-bit object.

#### **Numeric Notation**

- Hexadecimal numbers are denoted by the prefix Ox (for example, 0x04).

- Binary numbers are denoted by the prefix *Ob* (for example, 0b010).

- Registers that have multiple iterations are denoted by {x..y} in their names; where x is first register and address, and y is the last register and address. For example, REG{0..1} indicates there are two versions of the register at different addresses: REG0 and REG1.

#### Symbols

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or damage to the device.

### **Revision History**

### April 4, 2016

• Added GCLV, GILH, and GILV part numbers to Ordering Information

#### May 5, 2014

Updated the description of the V<sub>IN DIFF</sub> parameter in Table 32

#### December 3, 2012

Updated Ordering Information with production ordering numbers

#### February 28, 2012

- Added a footnote to Absolute Maximum Ratings, and removed the minimum rating for T<sub>JN</sub> from the same section

- Added T<sub>JN</sub> and a footnote to Recommended Operating Conditions

### December 16, 2011

- · Updated the minimum and maximum values for AVDD10 in Recommended Operating Conditions

- Added Power Consumption data

- · Changed the Moisture Sensitivity Level to 4

## 1. Device Overview

Topics discussed include the following:

- Overview

- Features

- Block Diagram

- Typical Applications

### 1.1 Overview

IDT is the leading supplier of RapidIO<sup>®</sup> and PCI Express Interconnect solutions, providing a broad portfolio of switches, bridges, IP, and development platforms for defense aerospace, video, imaging, and wireless markets. The Tsi721 is IDT's solution for hardware-based PCIe Gen2 to RapidIO Gen2 protocol conversion in a bridging device.

The Tsi721 converts transactions from PCIe to RapidIO, and vice versa, and provides full line rate bridging at 20 Gbaud. Using the Tsi721, designers can develop heterogeneous systems that leverage the peer-to-peer networking performance of RapidIO while using multiprocessor clusters that may be only PCIe enabled. In addition, applications that require large amounts of data transferred efficiently without processor involvement can be executed using the full line rate of the Tsi721's Block DMA Engine and Messaging Engine.

Key to the Tsi721 is the hardware bridging functionality that converts PCIe transactions to RapidIO, and vice versa. The Tsi721 supports PCIe non-transparent bridging for transaction mapping. The device has both RapidIO and PCIe endpoints embedded in the bridge, and each of its Block DMA/Messaging DMA channels can buffer up to 8 KB of data on the PCIe side.

### 1.2 Features

The Tsi721 supports the following features.

#### 1.2.1 PCIe Features

- PCle 2.1 standard compliant

- 5/2.5 Gbaud link speed

- x4/x2/x1 link width

- 128- and 256-byte maximum payload

- Advanced error reporting

- · Internal error reporting

- Lane reversal

- Automatic polarity inversion

- · Dynamic port width: x4 drops to x1

- ECRC support

- INTx, MSI, and MSI-X support

- Single virtual channel, VC0

- Single traffic class, TC0

- Generates only PCIe posted/non-posted TLPs with TC0

- Generates only PCIe Cpl/CpID TLPs with TC matching their requests

- Accepts PCIe TLPs with any TC

- Four BARs

- Prefetchable BAR with 32- or 64-bit addressing for PCIe-to-S-RIO bridging

- Non-prefetchable BAR with 32- or 64-bit addressing for PCIe-to-S-RIO bridging

- Non-prefetchable BAR with 32-bit addressing for PCIe MWr to S-RIO doorbell bridging

- Non-prefetchable BAR with 32-bit addressing for Tsi721 internal register access

- Initial credit advertisement programmable through EEPROM

- · Dynamic control of credits through registers

- Starvation prevention based on flow control credit updates

- Large buffers

- 12 KB/2 KB/12 KB input buffers for up to 127 posted/non-posted/completion TLPs

- 12 KB/2 KB/12 KB output buffers for up to 128 posted/non-posted/completion TLPs

- Debug features

- Slave analog loopback through a control register

- Slave loopback using TS1/TS2 ordered sets

- Master loopback

- Internal error reporting

- ECC protection on internal memories

### 1.2.2 S-RIO Features

- S-RIO 2.1 standard compliant

- 5/3.125/2.5/1.25 Gbaud link speed

- x4/x2/x1 link width

- 34-, 50-, and 66-bit addressing

- 16 destID filters

- 8 S-RIO flows

- 9-KB ingress buffer (32 x 288)

- 9-KB egress buffer (32 x 288)

- Lane reversal

- Lane polarity inversion

### 1.2.3 Bridging Features

- Store and forward from PCIe to S-RIO

- Store and forward from S-RIO to PCIe

- Line rate support for 64 byte and larger packets

- 32 outstanding PCIe requests to root complex

- 32 outstanding S-RIO NREAD/maintenance read requests to S-RIO network

- 32 outstanding S-RIO NWRITE\_R/maintenance write/doorbell requests to S-RIO network

- 12-KB completion reassembly buffer

- 8 windows from PCIe to S-RIO with 8 zones (sub windows) per window

- 8 windows from S-RIO to PCIe

- Initiates and receives the following S-RIO transactions:

- NREAD

- SWRITE/NWRITE/NWRITE\_R

- Maintenance read and write

- Port-write

- Doorbell

- Type 8 response

- Type 13 response

- Initiates and receives the following PCIe transactions:

- MWr

- MRd

- Cpl

- CpID

- Round-robin scheduling between Mapping Engine, Block DMA Engine, and Messaging traffic to the S-RIO link

- Round-robin scheduling between Mapping Engine, Block DMA Engine, and Messaging traffic to the PCIe link

- Forward bridge

- Connects PCIe root complex to S-RIO network

- PCIe Type 0 configuration header

#### 1.2.4 Messaging Features

- 8 Tx queues with one dedicated messaging DMA engine per Tx queue

- · 8 Rx queues with one dedicated messaging DMA engine per Rx queue

- Descriptor prefetch per Tx queue

- 32 outstanding PCIe requests to root complex

- 8-KB message segment reassembly buffer per Tx queue

- Round-robin scheduling among Tx queues

- One outstanding message per Tx queue

- 16 receive contexts per Rx queue

#### 1.2.5 Block DMA Engine Features

- 8 DMA channels

- Each DMA channel can perform DMA writes from root complex to S-RIO network, or DMA reads from S-RIO network to root complex

- DMA from PCIe port to PCIe port is not supported

- DMA from S-RIO port to S-RIO port is not supported

Integrated Device Technology

- · Round-robin scheduling among DMA channels

- DMA descriptors for all channels reside on PCIe side

- · Scatter-and-gather with descriptor list

- Supports DMA strides

- · Supports up to 64 MB data for a single descriptor

- · Supports both read and write descriptors per DMA channel

- Dynamic descriptor chaining

- Flexible addressing modes

- Linear addressing

- Constant addressing

- Descriptor prefetch

- 32 outstanding PCIe requests to root complex

- 64 outstanding S-RIO NREAD/maintenance read requests to S-RIO network

- 64 outstanding S-RIO NWRITE\_R/maintenance write requests to S-RIO network

- Supports the following S-RIO transactions:

- NREAD

- NWRITE

- SWRITE

- NWRITE\_R

- Maintenance read

- Maintenance write

#### 1.2.6 Miscellaneous Features

- I<sup>2</sup>C interface supports the following:

- As a slave, being read/written by an external master during normal operations

- As a master, reading external EEPROM during boot load

- As a master, reading/writing other external devices during normal operations

- JTAG 1149.1, 1149.6 (AC JTAG)

- 16 GPIO pins

### 1.3 Block Diagram

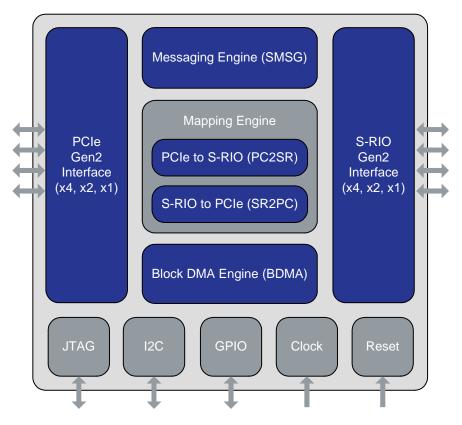

The Tsi721 block diagram is displayed in the following figure. The five main functions of the device are briefly described below.

### Figure 1: Block Diagram

#### 1.3.1 PCIe Interface

The PCIe Interface performs all the physical, data link, and transport layer protocols associated with PCIe.

#### 1.3.2 S-RIO Interface

The S-RIO Interface performs all the physical and transport layer protocols associated with S-RIO.

#### 1.3.3 Messaging Engine

The Messaging Engine uses S-RIO messaging logical layer functions with dedicated messaging DMA channels per Tx queue and per Rx queue.

#### 1.3.4 Mapping Engine

The Mapping Engine maps between PCIe and S-RIO transactions, including segmentation and reassembly as required.

#### 1.3.5 Block DMA Engine

The Block DMA Engine uses 8 DMA channels, where descriptors of each DMA channel can perform read or write.

### 1.4 Typical Applications

The Tsi721 supports the following typical applications:

- Defense and aerospace

- Radar

- Sonar

- Navigations systems

- Medical imaging

- CT scanners

- MRIs

- Video

•

- Teleconferencing

- Head end

- Wireless

- Baseband cards with x86

Three of Tsi721's typical applications – defense/aerospace, video/imaging, and wireless – are discussed in the following sections.

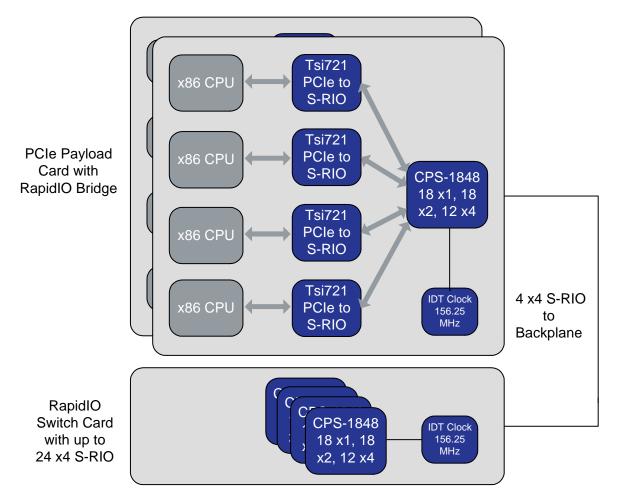

#### 1.4.1 Defense/Aerospace Application

In defense applications, the Tsi721 supports the use of PCIe enabled x86 processors to RapidIO backplanes. This provides system designers with the best of both worlds: the floating point and MIPs horsepower of the latest generation of x86 solutions, with the superior peer-to-peer networking performance of RapidIO architectures.

By using the Tsi721 combined with IDT's RapidIO Gen2 switches, payload processor cards with x86 processors can be used with existing RapidIO 1.3 backplanes operating at up to 3.125 Gbaud, or the same card can be used with RapidIO Gen2 compatible backplanes operating at 5 Gbaud.

RENESAS

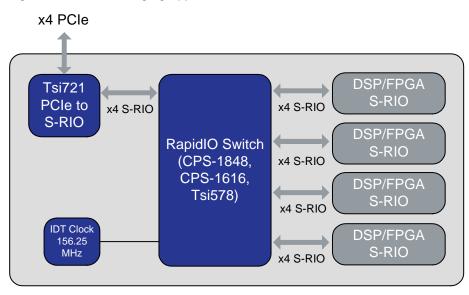

### 1.4.2 Video and Imaging Application

In video and imaging applications, system designers need to cluster large numbers of DSPs or FPGAs to perform encoding/decoding/trans coding, or do FFTs (Fast Fourier Transform) on large arrays of data. The RapidIO protocol is optimal for this DSP/FPGA cluster requirement. However, the analog front-end to the system is usually a sensor with streaming data terminated in an FPGA (for example, a camera subsystem). This is usually in an PCIe network, often with a PC back-end. In these applications the designer needs to bridge between a PCIe network and the RapidIO DSP/FPGA cluster. The Tsi721 is ideal for this application.

#### Figure 3: Video and Imaging Application

#### 1.4.3 Wireless Application

In wireless base stations, the incumbent interconnect technology in the baseband processing cards – LTE, WiMAX, WCDMA, and TD-SCDMA – is RapidIO. RapidIO connects a cluster of DSPs, processor, and FPGA, locally on the baseband processor for MAC and PHY layer processing. However, the LTE standard pushes the performance available in existing RapidIO enabled microprocessors.

The Tsi721 provides wireless OEMs with an additional option to use an x86 processor with superior MIPs in a baseband card that is predominantly RapidIO. In these card designs, RapidIO is the interconnect between devices and functions as the backplane interconnect. x86 processors can now be used with other RapidIO devices on the baseband card and leverage the messaging performance of RapidIO for this peer-to-peer multiprocessor network.

### RENESAS

## 2. Signals

Topics discussed include the following:

- Overview

- Ballmap

- Pinlist

- PCIe Signals

- S-RIO Signals

- General Signals

- I2C Signals

- JTAG and Test Interface Signals

- GPIO Signals

- Power-up Signals

- Power Supply Signals

### 2.1 Overview

The following conventions are used in this chapter:

- Signals with the suffix "P" are the positive half of a differential pair.

- Signals with the suffix "N" are the negative half of a differential pair.

- Signals with the suffix "n" are active low.

Signals are classified according to the types defined in the following table.

### Table 1: Signal Types

| Pin Type | Definition                              |

|----------|-----------------------------------------|

| 1        | 3.3/2.5V LVTTL Input                    |

| 0        | 3.3/2.5V LVTTL Output                   |

| 10       | 3.3/2.5V LVTTL Bidirectional            |

| IO-OD    | 3.3/2.5V LVTTL Bidirectional Open Drain |

| OD       | 3.3/2.5V LVTTL Open Drain               |

| I-PU     | 3.3/2.5V LVTTL Input with Pull-up       |

| I-PD     | 3.3/2.5V LVTTL Input with Pull-down     |

### Table 1: Signal Types (Continued)

| Pin Type | Definition                                  |

|----------|---------------------------------------------|

| IO-PD    | 3.3/2.5V LVTTL Bidirectional with Pull-down |

| IO-PU    | 3.3/2.5V LVTTL Bidirectional with Pull-up   |

| PCIE_O   | Differential CML PCIe output                |

| PCIE_I   | Differential CML PCIe input                 |

| SRIO_O   | Differential CML S-RIO output               |

| SRIO_I   | Differential CML S-RIO input                |

| DIFF_I   | Differential CML input                      |

| PWR      | Power                                       |

| GND      | Ground                                      |

### 2.2 Ballmap

### Figure 5: Ballmap

|   | 1       | 2             | 3       | 4       | 5       | 6       | 7       | 8       | 9       | 10      | 11      | 12                 |

|---|---------|---------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|--------------------|

| A | NO_BALL | GPIO[9]       | VSS     | PCRP[0] | PCTP[0] | PCTP[1] | PCRP[1] | PCRP[2] | PCTP[2] | PCTP[3] | PCRP[3] | PCCLKP             |

| В | GPIO[0] | GPIO[10]      | VSS     | PCRN[0] | PCTN[0] | PCTN[1] | PCRN[1] | PCRN[2] | PCTN[2] | PCTN[3] | PCRN[3] | PCCLKN             |

| С | GPIO[1] | GPI0[11]      | VSS     | VSS     | AVDD25  | AVDD25  | AVDD25  | AVDD25  | VSS     | VSS     | VSS     | PCBIAS             |

| D | GPIO[2] | GPI0[12]      | VDDIO   | AVTT    | AVTT    | VSS     | VSS     | AVDD10  | AVDD10  | VSS     | TDO     | PCRSTOn            |

| E | GPIO[3] | GPIO[13]      | VDDIO   | AVTT    | VDD     | VSS     | VSS     | VDD     | AVDD10  | VDDIO   | тск     | TEST_BCE           |

| F | GPIO[4] | GPIO[14]      | VDDIO   | AVTT    | VSS     | VDD     | VDD     | VSS     | AVDD10  | VDDIO   | TDI     | TEST_ON            |

| G | GPIO[5] | GPIO[15]      | VDDIO   | AVTT    | VSS     | VDD     | VDD     | VSS     | AVDD10  | VDDIO   | VSS     | TEST_BIDIR_CT<br>L |

| Н | GPIO[6] | STRAP_RATE[0] | VDDIO   | AVTT    | VDD     | VSS     | VSS     | VDD     | AVDD10  | VDDIO   | TMS     | RSTn               |

| J | GPIO[7] | STRAP_RATE[1] | VDDIO   | AVTT    | AVTT    | VSS     | VSS     | AVDD10  | AVDD10  | VSS     | TRSTn   | SRRSTOn            |

| к | GPIO[8] | STRAP_RATE[2] | VSS     | VSS     | AVDD25  | AVDD25  | AVDD25  | AVDD25  | VSS     | VSS     | VSS     | SRBIAS             |

| L | I2C_SCL | CLKMOD        | VSS     | SRRN[0] | SRTN[0] | SRTN[1] | SRRN[1] | SRRN[2] | SRTN[2] | SRTN[3] | SRRN[3] | REFCLKN            |

| М | I2C_SDA | MECS          | SR_BOOT | SRRP[0] | SRTP[0] | SRTP[1] | SRRP[1] | SRRP[2] | SRTP[2] | SRTP[3] | SRRP[3] | REFCLKP            |

Tsi721 Datasheet

18

© 2019 Renesas Electronics Corporation

RENESAS

### 2.3 Pinlist

For a list-based version of Tsi721's pin to signal mapping, see the Tsi721 Ballmap and Pinlist.

### 2.4 PCIe Signals

### Table 2: PCIe Signals

| Name                   | Pin Type | Description                                                                                                                                                                                                                                                             |

|------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCTP[3:0]<br>PCTN[3:0] | PCIE_O   | Differential transmit data for the PCIe port.                                                                                                                                                                                                                           |

| PCRP[3:0]<br>PCRN[3:0] | PCIE_I   | Differential receive data for the PCIe port.                                                                                                                                                                                                                            |

| PCCLKP                 | DIFF_I   | PCIe reference clock input.                                                                                                                                                                                                                                             |

| PCCLKN                 |          | When in PCIe common clock mode (CLKMOD pin is high, see the "Clocking" chapter in the Tsi721 User Manual), PCCLKP/N requires a clock frequency of 100 MHz.                                                                                                              |

|                        |          | When in PCIe non-common clock mode (CLKMOD pin is low), PCCLKP/N requires a clock frequency as selected by CLKSEL[1:0], and must have the same clock frequency as REFCLKP/N.                                                                                            |

| PCRSTOn                | 10       | <ul> <li>It is an output for normal operation and an input during scan test mode.</li> <li>As an asynchronous active-low reset output, this pin is low when the following occurs:</li> <li>The PCIe port detects hot reset</li> <li>The PCIe port is DL_DOWN</li> </ul> |

### 2.5 S-RIO Signals

Table 3: S-RIO Signals

| Name                   | Pin Type | Description <sup>a</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRTP[3:0]<br>SRTN[3:0] | SRIO_O   | Differential transmit data for the S-RIO port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SRRP[3:0]<br>SRRN[3:0] | SRIO_I   | Differential receive data for the S-RIO port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SRRSTOn                | IO       | It is an output for normal operation and an input during scan test mode.<br>As an asynchronous active-low reset output, this pin is low when four<br>consecutive S-RIO reset symbols are received, and SELF_RST is set to 1 in the<br>RapidIO PLM Port Implementation Specific Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MECS                   | IO-PD    | Asynchronous S-RIO Multicast Event Control Symbol (MECS). Its direction is<br>controlled by the MECS_O bit in the Device Control Register.<br>As an <i>input</i> , a rising or falling edge triggers an S-RIO MECS to be sent on the<br>S-RIO link. Use the RIO_PLM_SPO_MECS_FWD.SUBSCRIPTION/MULT_CS<br>and RIO_EM_MECS_TRIG_EN.CMD_EN to select the CMD field that should be<br>set with the MECS. Multiple MECSs with different CMD fields can be generated<br>by setting these fields appropriately.<br>As an <i>output</i> , this signal is toggled when an S-RIO MECS is received. Only a<br>single MECS CMD value should be selected to toggle the MECS input. Set the<br>RIO_EM_MECS_CAP_EN.CMD_EN to select the CMD value to be propagated<br>to the MECS pin. Note: Only 1 bit should be enabled in CMD_EN. |

a. For information on S-RIO signals that are used for power-up purposes only, see Power-up Signals.

### 2.6 General Signals

Table 4: General Signals

| Name               | Pin Type | Description                                                                                    |

|--------------------|----------|------------------------------------------------------------------------------------------------|

| RSTn               | I-PU     | Fundamental reset (device reset). Assertion of this signal resets all logic inside the Tsi721. |

| REFCLKP<br>REFCLKN | DIFF_I   | S-RIO reference clock input. REFCLK requires a clock frequency as selected by CLKSEL[1:0].     |

### 2.7 I2C Signals

The I2C Interface is used for the following:

- As a master, downloading configuration from EEPROM

- As a master, allowing the PCIe root complex or the S-RIO host to configure other I2C expansion devices

- As a slave, exposing internal register space to an I2C master (Note: To be used for lab debug or another master-driven initialization).

### Table 5: I<sup>2</sup>C Signals

| Name    | Pin Type | Description <sup>a</sup>                                                |

|---------|----------|-------------------------------------------------------------------------|

| I2C_SCL | IO-OD    | Serial clock for the I2C Interface with a maximum frequency of 100 kHz. |

| I2C_SDA | IO-OD    | Serial data for the I2C Interface.                                      |

a. For information on I2C signals that are used for power-up purposes only, see Power-up Signals.

### 2.8 JTAG and Test Interface Signals

### Table 6: JTAG Interface Signals

| Name           | Pin Type | Description                                                                                                                                                                             |  |  |  |  |  |

|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ТСК            | I-PD     | IEEE 1149.1/1149.6 test access port. Clock input.                                                                                                                                       |  |  |  |  |  |

| TDI            | I-PU     | EEE 1149.1/1149.6 test access port. Serial data input                                                                                                                                   |  |  |  |  |  |

| TDO            | 0        | IEEE 1149.1/1149.6 test access port. Serial data output                                                                                                                                 |  |  |  |  |  |

| TMS            | I-PU     | IEEE 1149.1/1149.6 test access port. Test mode select                                                                                                                                   |  |  |  |  |  |

| TRSTn          | I-PU     | IEEE 1149.1/1149.6 test access port. Reset input.<br>This input must be asserted during the assertion of RSTn. Thereafter, it can be<br>left in either state.                           |  |  |  |  |  |

| TEST_ON        | I-PD     | Test mode pin. Tie low or NC for normal operation.                                                                                                                                      |  |  |  |  |  |

| TEST_BCE       | I-PU     | Boundary scan compatibility enabled pin. This input aids 1149.6 testing. It must be tied to VDDIO (or NC as there is internal pull up in pad) during normal operation of the device.    |  |  |  |  |  |

|                |          | 0 = JTAG chain includes SerDes registers. SerDes registers are accessible to external JTAG pins. Used during ATE and lab debug of SerDes registers through an external JTAG Controller. |  |  |  |  |  |

|                |          | 1 = JTAG chain does not include SerDes registers. SerDes register are accessible through the internal register bus for BAR 0 access.                                                    |  |  |  |  |  |

| TEST_BIDIR_CTL | I-PU     | Test mode pin. Tie high or NC for normal operation.                                                                                                                                     |  |  |  |  |  |

### 2.9 GPIO Signals

Table 7: GPIO Signals

| Name       | Pin Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO[15:0] | IO       | <ul> <li>Asynchronous general purpose I/O.</li> <li>Each GPIO pin can be configured as a general purpose I/O pin.</li> <li>Each pin can be configured as either an input or an output</li> <li>When configured as an output, GPIO[0] is asserted high when<br/>BDMA/SMSG/PC2SR/SR2PC has an uncorrectable ECC error or S-RIO MAC<br/>has a non-data memory uncorrectable ECC error</li> <li>When configured as an output, GPIO[1] is asserted high when Tsi721 PCIe<br/>port is not in the data link active state</li> <li>When configured as an output, GPIO[2] is asserted high when Tsi721 has an<br/>active interrupt (for more information, see Figure 18 and Figure 19)</li> <li>When configured as an output, GPIO[15:3] can be programmed through<br/>software</li> <li>GPIO[12:0] are used as power-up pins as displayed in Table 8. These signals<br/>must remain stable for 4000 REFCLKP/REFCLKN cycles after RSTn is<br/>de-asserted. They are ignored after reset.</li> </ul> |

### Table 8: GPIO Mapping to Power-up Signals

| GPIO Pin Name<br>(Primary Function) | Power-up Pin Name <sup>a</sup><br>(Secondary Function) |  |  |  |  |

|-------------------------------------|--------------------------------------------------------|--|--|--|--|

| GPIO[3:0]                           | I2C_SA[3:0]                                            |  |  |  |  |

| GPIO[4]                             | I2C_DISABLE                                            |  |  |  |  |

| GPIO[5]                             | I2C_SEL                                                |  |  |  |  |

| GPIO[6]                             | I2C_MA                                                 |  |  |  |  |

| GPIO[7]                             | SP_SWAP_RX                                             |  |  |  |  |

| GPIO[8]                             | SP_SWAP_TX                                             |  |  |  |  |

| GPIO[9]                             | SP_HOST                                                |  |  |  |  |

| GPIO[10]                            | SP_DEVID                                               |  |  |  |  |

| GPIO[12:11]                         | CLKSEL[1:0]                                            |  |  |  |  |

a. For more information about these signals, see Power-up Signals.

### 2.10 Power-up Signals

Table 9: Power-Up Signals

| Name        | Pin Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKMOD      | I-PU     | Clock mode. When high, Tsi721 uses "PCIe common clocked mode." When low, it uses "PCIe non-common clocked mode." It is a static signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CLKSEL[1:0] | IO       | <ul> <li>REFCLKP/REFCLKN clock frequency select; PCCLKP/PCCLKN clock frequency select when in PCIe non-common clock mode.</li> <li>0b11 = 125 MHz</li> <li>0b10 = 100 MHz</li> <li>0b01 = 156.25 MHz</li> <li>Others = Reserved</li> <li>When a 100-MHz clock is used, S-RIO SerDes rates of 1.25/2.5/5 Gbaud are supported.</li> <li>When a 125/156.25-MHz clock is used, S-RIO SerDes rates of 1.25/2.5/3.125/5 Gbaud are supported.</li> <li>When either a 100/125/156.25-MHz clock is used, PCIe SerDes rates of 2.5/5 Gbaud are supported.</li> <li>These power-up signals are multiplexed with GPIO[12:11]. It is a static signal.</li> </ul> |

| I2C_DISABLE | IO       | Disable I <sup>2</sup> C register loading after reset. When asserted, Tsi721 does not attempt to load register values from an EEPROM over the I <sup>2</sup> C bus.<br>0 = Enable boot load from EEPROM<br>1 = Disable boot load from EEPROM<br>This power-up signal is multiplexed with GPIO[4]. It is a static signal.                                                                                                                                                                                                                                                                                                                            |

| I2C_MA      | IO       | <ul> <li>I<sup>2</sup>C multi-byte address mode. If I2C_DISABLE == 0 (that is, download registers from EEPROM) then:</li> <li>0 = Tsi721 uses 1-byte addressing for EEPROM</li> <li>1 = Tsi721 uses 2-byte addressing for EEPROM</li> <li>Else I2C_DISABLE == 1 (do not download from EEPROM)</li> <li>0 = Tsi721 is boot loaded by the PCIe root complex after reset</li> <li>1 = Tsi721 is boot loaded by an external I2C master after reset</li> <li>This power-up signal is multiplexed with GPIO[6]. It is a static signal.</li> </ul>                                                                                                         |

| I2C_SA[3:0] | IO       | I2C slave address. The values on these pins represent the values for the 7-bit address of the Tsi721 when acting as an I <sup>2</sup> C slave.<br>These signals, in combination with the I2C_SEL signal, determine the address of the EEPROM to boot from (see I2C_SEL pin description).<br>The values on these pins can be overridden after a reset by writing to the I2C Slave Configuration Register.<br>These power-up signals are multiplexed with GPIO[3:0]. It is a static signal.                                                                                                                                                           |

### Table 9: Power-Up Signals (Continued)

| Name       | Pin Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2C_SEL    | 10       | $I^2$ C pin select. Combined with the I2C_SA[1,0] pins, Tsi721 will determine the<br>lower 2 bits of the 7-bit address of the EEPROM address it boots from.<br>When asserted, the I2C_SA[1:0] pins represent the two LSBs of the 7-bit<br>EEPROM slave address when Tsi721 acts as a I <sup>2</sup> C master downloading from an<br>EEPROM. The EEPROM slave address is as follows:<br>A6 = 1<br>A5 = 0<br>A4 = 1<br>A3 = 0<br>A2 = 0<br>A1 = I2C_SA[1]<br>A0 = I2C_SA[1]<br>A0 = I2C_SA[0]<br>When de-asserted, the I2C_SA[1:0] pins are ignored and the lower two bits of<br>the EEPROM address default to 00. The values of the EEPROM address can be<br>overridden by software after initialization.<br>This power-up signal is multiplexed with GPI0[5]. It is a static signal.                                                                                                                                                |

| SP_DEVID   | IO       | S-RIO base deviceID control<br>When the SP_HOST pin is high, it configures the reset value of the RapidIO<br>Base deviceID CSR: the LSB of the CSR's BASE_ID and LAR_BASE_ID fields<br>are set to SP_DEVID, while other bits of these fields are set to 0.<br>When the SP_HOST pin is low and SP_DEVID is high, it configures the reset<br>value of the RapidIO Base deviceID CSR: the CSR's BASE_ID and<br>LAR_BASE_ID fields are set to all ones.<br>When the SP_HOST pin is low and SP_DEVID is low, it configures the reset<br>value of the RapidIO Base deviceID CSR: the CSR's BASE_ID and<br>LAR_BASE_ID fields are set to all ones.<br>When the SP_HOST pin is low and SP_DEVID is low, it configures the reset<br>value of the RapidIO Base deviceID CSR: the CSR's BASE_ID field is set to<br>0xFE and the CSR's LAR_BASE_ID field are set to 0x00FE.<br>This signal is multiplexed with GPIO[10]. It is a static signal. |

| SP_HOST    | IO       | S-RIO host / slave control. This signal sets the reset value of the HOST bit of the<br>RapidIO Port General Control CSR.<br>0 = Tsi721 is an S-RIO slave.<br>1 = Tsi721 is an S-RIO host.<br>This signal is multiplexed with GPIO[9]. It is a static signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SP_SWAP_RX | 10       | <ul> <li>S-RIO receive lane swap. This signal sets the reset value of the SWAP_RX[1:0] bits of RapidIO PLM Port Implementation Specific Control Register.</li> <li>0 = Disable S-RIO port receive lane swap; that is, set the SWAP_RX[1:0] register bits to 0b00.</li> <li>1 = Enable S-RIO port receive 4x lane swap; that is, set the SWAP_RX[1:0] register bits to 0b10.</li> <li>This signal is multiplexed with GPIO[7].</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### Table 9: Power-Up Signals (Continued)

| Name            | Pin Type | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP_SWAP_TX      | IO       | <ul> <li>S-RIO transmit lane swap. This signal sets the reset value of the SWAP_TX bit of RapidIO PLM Port Implementation Specific Control Register.</li> <li>0 = Disable S-RIO port transmit lane swap.</li> <li>1 = Enable S-RIO port transmit lane swap.</li> <li>This signal is multiplexed with GPIO[8]. It is a static signal.</li> </ul>                                   |

| SR_BOOT         | I-PD     | Boot from S-RIO. It can be asserted high only when I2C_DISABLE is also high.<br>1 = The Tsi721 S-RIO link can start training immediately after a fundamental<br>reset and Tsi721 automatically sets the SRBOOT_CMPL bit of Device Control<br>Register.<br>0 = The Tsi721 S-RIO link can start training only after software sets the<br>SRBOOT_CMPL bit.<br>It is a static signal. |

| STRAP_RATE[2:0] | I-PU     | <ul> <li>S-RIO link rate. These signals control the reset value of the BAUD_SEL field of the RapidIO Port Control 2 CSR . Note that the BAUD_SEL encoding is different than that of STRAP_RATE.</li> <li>0b111 = 5 Gbaud</li> <li>0b110 = 2.5 Gbaud</li> <li>0b101 = 1.25 Gbaud</li> <li>0b010 = 3.125 Gbaud</li> <li>Others: Reserved</li> <li>It is a static signal.</li> </ul> |

### 2.11 Power Supply Signals

Table 10: Power Supply Signals

| Name   | Pin Type | Description                                                                                                                                                                                                                     |  |  |  |  |  |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| VDD    | PWR      | 1.0V core power                                                                                                                                                                                                                 |  |  |  |  |  |

| VDDIO  | PWR      | 3.3/2.5V power for LVTTL IO                                                                                                                                                                                                     |  |  |  |  |  |

| AVDD10 | PWR      | 1.0V PCIe and S-RIO SerDes analog power supply                                                                                                                                                                                  |  |  |  |  |  |

| AVDD25 | PWR      | 2.5V PCIe and S-RIO SerDes analog power supply                                                                                                                                                                                  |  |  |  |  |  |

| AVTT   | PWR      | 1.5V PCIe and S-RIO SerDes transmitter analog voltage                                                                                                                                                                           |  |  |  |  |  |

| VSS    | GND      | Shared digital and analog ground                                                                                                                                                                                                |  |  |  |  |  |

| PCBIAS | IO       | Reference for the corresponding PCIe SerDes bias currents and PLL calibration circuitry. A 200 Ohm 1% 100ppm/C precision resistor should be connected from this pin to ground and isolated from any source of noise injection.  |  |  |  |  |  |

| SRBIAS | 10       | Reference for the corresponding S-RIO SerDes bias currents and PLL calibration circuitry. A 200 Ohm 1% 100ppm/C precision resistor should be connected from this pin to ground and isolated from any source of noise injection. |  |  |  |  |  |

## 3. Electrical Characteristics

Topics discussed include the following:

- Absolute Maximum Ratings

- Recommended Operating Conditions

- Power Consumption

- Power Supply Sequencing

- DC Operating Characteristics

- Decoupling Recommendation

- AC Timing Specifications

### 3.1 Absolute Maximum Ratings

Table 11: Absolute Maximum Ratings<sup>a</sup>

| Symbol                                  | Parameter                                                       | Minimum | Maximum | Units |

|-----------------------------------------|-----------------------------------------------------------------|---------|---------|-------|

| VDDIO                                   | 3.3/2.5V I/O voltage with respect to VSS                        | -0.5    | 3.6     | V     |

| VDD                                     | 1.0V core voltage with respect to VSS                           | -0.5    | 1.10    | V     |

| AVDD10                                  | 1.0V analog voltage with respect to AVSS                        | -0.5    | 1.10    | V     |

| AVDD25                                  | 2.5V analog voltage with respect to AVSS                        | -0.5    | 2.75    | V     |

| AVTT                                    | 1.5V analog voltage for SerDes transmitter with respect to AVSS | -0.5    | 2.75    | V     |

| T <sub>BIAS</sub>                       | Temperature under bias                                          | -40     | 125     | С     |

| T <sub>STG</sub>                        | Storage temperature                                             | -65     | 150     | С     |

| T <sub>JN</sub>                         | Junction temperature                                            | -       | 125     | С     |

| I <sub>OUT</sub> (for VDDIO = 3.3/2.5V) | DC output current                                               | -       | 30      | mA    |

a. Stresses outside the absolute ratings can cause permanent damage to the device and affect its functional performance. Exposure to absolute rating conditions for extended periods can affect reliability.

### 3.2 Recommended Operating Conditions

| Symbol          | Parameter                                     | Minimum | Maximum | Units |

|-----------------|-----------------------------------------------|---------|---------|-------|

| T <sub>A</sub>  | Ambient temperature – Commercial              | 0       | 70      | °C    |

|                 | Ambient temperature – Industrial              | -40     | 85      | °C    |

| T <sub>JN</sub> | Junction temperature                          | -       | 110     | °C    |

| VDDIO           | 3.3V LVTTL I/O supply voltage                 | 3.14    | 3.47    | V     |

|                 | 2.5V LVTTL I/O supply voltage                 | 2.4     | 2.6     | V     |

| VDD             | 1.0V Core supply voltage                      | 0.95    | 1.05    | V     |

| AVDD10          | 1.0V SerDes analog supply voltage             | 0.95    | 1.05    | V     |

| AVDD25          | 2.5V SerDes analog supply voltage             | 2.25    | 2.75    | V     |

| AVTT            | 1.5V SerDes transmitter analog supply voltage | 1.4     | 1.7     | V     |

Table 12: Recommended Operating Conditions<sup>a</sup>

a. Exposure to conditions outside the recommended operating conditions can affect the operation and/or reliability of the device.

### 3.3 **Power Consumption**

Table 13 lists the current draw for each supply group for different environmental conditions. Test characteristics were are follows:

- RapidIO and PCIe links configured at operated at 5 Gbps in x4 mode

- Traffic passed through the Tsi721 with a high incidence of 0/1 toggling

- Power measurements are based on worst case fast silicon processing. A "Total Power" reduction in excess of 5% can be expected for nominal/typical silicon.

| Table 13: | Power | Consum | ption |

|-----------|-------|--------|-------|

|-----------|-------|--------|-------|

| lunction                 |         | VDD            |                 | AVDD10         |                 | AVDD25         |                 | AVTT           |                 | VDDIO          |                 |                    |

|--------------------------|---------|----------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|-----------------|--------------------|

| Junction<br>Temp<br>(ºC) | Voltage | Voltage<br>(V) | Current<br>[mA] | Total<br>Power (W) |

| 125                      | Max.    | 1.05           | 3000            | 1.05           | 330             | 2.75           | 165             | 1.70           | 350             | 3.47           | 20              | 4.61               |

|                          | Тур.    | 1.00           | 2722            | 1.00           | 281             | 2.50           | 153             | 1.50           | 335             | 3.30           | 18              | 3.95               |

|                          | Min.    | 0.95           | 2458            | 0.95           | 242             | 2.25           | 144             | 1.40           | 320             | 3.14           | 17              | 3.39               |

| 25                       | Max.    | 1.05           | 1110            | 1.05           | 214             | 2.75           | 161             | 1.70           | 350             | 3.47           | 20              | 2.50               |

|                          | Тур.    | 1.00           | 1003            | 1.00           | 190             | 2.50           | 151             | 1.50           | 335             | 3.30           | 18              | 2.13               |

|                          | Min.    | 0.95           | 909             | 0.95           | 170             | 2.25           | 142             | 1.40           | 320             | 3.14           | 17              | 1.85               |

#### Table 13: Power Consumption (Continued)

| Junction     |         | VDD            |                 | AVDD10         |                 | AVDD25         |                 | AVTT           |                 | VDDIO          |                 |                    |

|--------------|---------|----------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|-----------------|--------------------|

| Temp<br>(°C) | Voltage | Voltage<br>(V) | Current<br>[mA] | Total<br>Power (W) |

| -40          | Max.    | 1.05           | 829             | 1.05           | 192             | 2.75           | 159             | 1.70           | 350             | 3.47           | 20              | 2.17               |

|              | Тур.    | 1.00           | 765             | 1.00           | 175             | 2.50           | 149             | 1.50           | 335             | 3.30           | 18              | 1.87               |

|              | Min.    | 0.95           | 707             | 0.95           | 159             | 2.25           | 141             | 1.40           | 320             | 3.14           | 17              | 1.64               |

### 3.4 Power Supply Sequencing

This section contains power-up and power-down supply sequencing for the Tsi721.

### 3.4.1 Power-Up Sequencing

The Tsi721 must have its supplies powered up as follows:

1. VDD and AVDD10 (1.0V) must be powered up together.

To achieve this requirement AVDD10 can be supplied from the same regulator as VDD, but must be isolated on the board through a ferrite bead.

- 2. VDDIO, AVDD25, AVTT, and the 1.0V supplies (VDD and AVDD10) can be powered up in any order.

- 3. The voltages on any input or I/O pin cannot exceed its corresponding supply voltage during power supply ramp up.

- 4. The power supply ramp rates must be kept between 10 V/s and 0.5x10E6 V/s to minimize power current spikes during power up. This leads to the ramp times specified in the following table.

|     | V/s       |          |  |  |  |  |

|-----|-----------|----------|--|--|--|--|

| V   | 10        | 5.00E+05 |  |  |  |  |

| 3.3 | 330000 us | 6.6 us   |  |  |  |  |

| 2.5 | 250000 us | 5 us     |  |  |  |  |

| 1.5 | 150000 us | 3 us     |  |  |  |  |

| 1   | 100000 us | 2 us     |  |  |  |  |

### Table 14: Power Supply Sequencing Ramp Times

### 3.4.2 Power-Down Sequencing

The Tsi721 must have its supplies powered down as follows:

- 1. VDD and AVDD10 (1.0V) must be powered down together. To achieve this requirement AVDD10 can be supplied from the same regulator as VDD, but must be isolated on the board through a ferrite bead.

- 2. VDDIO, AVDD25, AVTT, and the 1.0V supplies (VDD and AVDD10) can be powered down in any order.

### 3.5 DC Operating Characteristics

The following table lists the DC operating characteristics for 3.3V LVTTL of the Tsi721.

### Table 15: 3.3V LVTTL DC Operating Characteristics at Recommended Operating Condition of 3.3V

| Symbol           | Parameter                 | Minimum | Maximum | Units |

|------------------|---------------------------|---------|---------|-------|

| V <sub>IH</sub>  | LVTTL input high voltage  | 2.0     | 3.6     | V     |

| V <sub>IL</sub>  | LVTTL input low voltage   | -0.3    | 0.8     | V     |

| V <sub>OH</sub>  | LVTTL output high voltage | 2.4     | -       | V     |

| V <sub>OL</sub>  | LVTTL output low voltage  | -       | 0.4     | V     |

| R pull-up        | Resistor pull-up          | 26K     | 64K     | Ohm   |

| R pull-down      | Resistor pull-down        | 29K     | 79K     | Ohm   |

| C <sub>PAD</sub> | LVTTL pad capacitance     | -       | 4       | pF    |

The following table lists the DC operating characteristics for 2.5V LVTTL of the Tsi721.

| Symbol           | Parameter                 | Minimum | Maximum | Units |

|------------------|---------------------------|---------|---------|-------|

| V <sub>IH</sub>  | LVTTL input high voltage  | 1.7     | 3.6     | V     |

| V <sub>IL</sub>  | LVTTL input low voltage   | -0.3    | 0.7     | V     |

| V <sub>OH</sub>  | LVTTL output high voltage | 1.7     | -       | V     |

| V <sub>OL</sub>  | LVTTL output low voltage  | -       | 0.7     | V     |

| R pull-up        | Resistor pull-up          | 33K     | 93K     | Ohm   |

| R pull-down      | Resistor pull-down        | 34K     | 108K    | Ohm   |

| C <sub>PAD</sub> | LVTTL pad capacitance     | -       | 4       | pF    |

### 3.6 Decoupling Recommendation

Table 17 provides the recommended decoupling for the Tsi721. Use low ESR, low lead inductance ceramic capacitors with X7R or X5R rating.

#### Table 17: Decoupling Recommendation

| Rail   | Decoupling           |

|--------|----------------------|

| VDDIO  | 5x 0.1uF and 1x 10uF |

| AVTT   | 5x 0.1uF and 1x 10uF |

| VDD    | 5x 0.1uF and 1x 10uF |

| AVDD10 | 5x 0.1uF and 1x 10uF |

| AVDD25 | 5x 0.1uF and 1x10uF  |

### 3.7 AC Timing Specifications

This section describes the AC timing specifications and electrical characteristics for the Tsi721.

### 3.7.1 PCIe Differential Receiver Specifications

Table 18 lists the electrical characteristics for the PCIe differential receivers in the Tsi721. Parameters are defined separately for 2.5 Gbps and 5.0 Gbps implementations. Table 18 is duplicated from the *PCI Express Base Specification (Rev. 2.1)* Section 4.3.3.4 Table 4-12 on page 270.

#### Table 18: PCIe Differential Receiver Specifications

|                            |                                                                          | 2.5 Gbps 5.0 Gbps |        |        |        |      |                                                                                             |

|----------------------------|--------------------------------------------------------------------------|-------------------|--------|--------|--------|------|---------------------------------------------------------------------------------------------|

| Symbol                     | Parameter                                                                | Min.              | Max.   | Min.   | Max.   | Unit | Notes                                                                                       |

| UI                         | Unit interval                                                            | 399.88            | 400.12 | 199.94 | 200.06 | ps   | UI does not account for SSC caused variations                                               |

| V <sub>RX-DIFF-PP-CC</sub> | Differential Rx peak-peak<br>voltage                                     | 0.175             | 1.2    | 0.120  | 1.2    | V    | See section 4.3.7.2.2 of the PCI<br>Express Base Specification (Rev. 2.1)                   |

| V <sub>RX-DIFF-PP-DC</sub> | Differential Rx peak-peak<br>voltage for data clocked<br>Rx architecture | 0.175             | 1.2    | 0.100  | 1.2    | V    | See section 4.3.7.2.2 of the <i>PCI</i><br><i>Express Base Specification (Rev. 2.1)</i>     |

| T <sub>RX-EYE</sub>        | Receiver eye time opening                                                | 0.40              | -      | N/A    | -      | UI   | Minimum eye time at Rx pins to produce a 10 <sup>-12</sup> BER. See Note 1.                 |

| T <sub>RX-TJ-CC</sub>      | Maximum Rx inherent timing error                                         | N/A               | -      | -      | 0.40   | UI   | Maximum Rx inherent total timing error<br>for common Refclk Rx architecture. See<br>Note 2. |

| T <sub>RX-TJ-DC</sub>      | Maximum Rx inherent timing error                                         | N/A               | -      | -      | 0.34   | UI   | Maximum Rx inherent total timing error<br>for data clocked Rx architecture. See<br>Note 2.  |

Integrated Device Technology

### Table 18: PCIe Differential Receiver Specifications (Continued)

|                                              |                                                                   | 2.5 Gbps |          | 5.0 C                                                  | Sbps    |      |                                                                                                                                |

|----------------------------------------------|-------------------------------------------------------------------|----------|----------|--------------------------------------------------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                       | Parameter                                                         | Min.     | Max.     | Min.                                                   | Max.    | Unit | Notes                                                                                                                          |

| T <sub>RX-DJ-DD-CC</sub>                     | Maximum Rx inherent deterministic timing error                    | N/A      | -        | -                                                      | 0.30    | UI   | Maximum Rx inherent deterministic<br>timing error for common Refclk Rx<br>architecture. See Note 2.                            |

| T <sub>RX-DJ-DD-DC</sub>                     | Maximum Rx inherent deterministic timing error                    | N/A      | -        | -                                                      | 0.24    | UI   | Maximum Rx inherent deterministic<br>timing error for data clocked Rx<br>architecture. See Note 2.                             |

| T <sub>RX-EYE-MEDIAN</sub><br>-to-MAX-JITTER | Maximum time delta<br>between median and<br>deviation from median | -        | 0.3      | Not sp                                                 | ecified | UI   | Only specified for 2.5 Gbps                                                                                                    |

| T <sub>RX-MIN-PULSE</sub>                    | Minimum width pulse at Rx                                         | Not sp   | becified | 0.6                                                    | -       | UI   | Measured to account for worst Tj at 10 <sup>-12</sup> BER. See Figure 4-29 of <i>PCI Express Base Specification (Rev. 2.1)</i> |

| V <sub>RX-MAX-MIN-RA</sub><br>TIO            | Minimum/Maximum pulse voltage on consecutive UI                   | Not sp   | ecified  | -                                                      | 5       |      | Rx eye must simultaneously meet<br>V <sub>RX-EYE</sub> limits.                                                                 |

| BW <sub>RX-PLL-HI</sub>                      | Maximum Rx PLL bandwidth                                          | -        | 22       | -                                                      | 16      | MHz  | Second order PLL jitter transfer bounding function. See Note 3.                                                                |

| BW <sub>RX-PLL-LO-3D</sub>                   | Minimum Rx PLL BW for<br>3 dB peaking                             | 1.5      | -        | 8                                                      | -       | MHz  | Second order PLL jitter transfer bounding function. See Note 3.                                                                |

| BW <sub>RX-PLL-LO-1D</sub>                   | Minimum Rx PLL BW for 1dB peaking                                 | Not sp   | becified | 5                                                      | -       | MHz  | Second order PLL jitter transfer bounding function. See Note 3.                                                                |

| PKG <sub>RX-PLL1</sub>                       | Rx PLL peaking with<br>8Mhz minimum BW                            | Not sp   | ecified  | 3.0                                                    | -       | dB   | Second order PLL jitter transfer bounding function. See Note 3.                                                                |

| PKG <sub>RX-PLL2</sub>                       | Rx PLL peaking with<br>5MHz minimum BW                            | Not sp   | ecified  | 1.0                                                    | -       | dB   | Second order PLL jitter transfer bounding function. See Note 3.                                                                |