### **TSM1052**

# Constant voltage and constant current controller for battery chargers and adapters

#### **Features**

- Secondary-side constant voltage and constant current control

- Very low voltage operation

- Very low quiescent consumption

- High-accuracy internal reference

- Low external component count

- Wired-or open-drain output stage

- Easy frequency compensation

- SOT23-6 micro package

### **Applications**

- Battery chargers

- AC DC adapters

### **Description**

The TSM1052 is a highly integrated solution for SMPS applications requiring a dual control loop to perform CV (constant voltage) and CC (constant current) regulation.

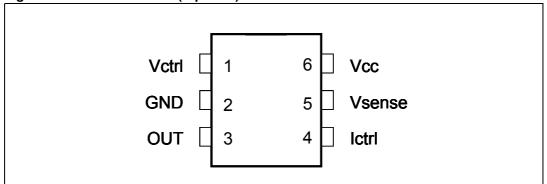

The TSM1052 integrates a voltage reference, two op amps (with OR-ed open-drain outputs), and a low-side current sensing circuit.

The voltage reference, along with one op amp, is the core of the voltage control loop; the current sensing circuit and the other op amp make up the current control loop.

The external components needed to complete the two control loops are:

- A resistor divider that senses the output of the power supply (adapter, battery charger) and fixes the voltage regulation set point at the specified value;

- A sense resistor that feeds the current sensing circuit with a voltage proportional to the dc output current; this resistor determines the current regulation set point and must be adequately rated in terms of power dissipation;

- Frequency compensation components (RC networks) for both loops.

The TSM1052, housed in one of the smallest package available, is ideal for space-shrunk applications such as adapters and chargers.

Table 1. Device summary

| Part number | Package | Packaging     |

|-------------|---------|---------------|

| TSM1052     | SOT23-6 | Tape and reel |

Contents TSM1052

# **Contents**

| 1 | Des  | Description                           |  |  |  |  |

|---|------|---------------------------------------|--|--|--|--|

|   | 1.1  | Pin connection                        |  |  |  |  |

|   | 1.2  | Pin description 3                     |  |  |  |  |

|   | 1.3  | Internal schematic 4                  |  |  |  |  |

|   | 1.4  | Absolute maximum ratings              |  |  |  |  |

|   | 1.5  | Thermal data 4                        |  |  |  |  |

| 2 | Elec | trical characteristics5               |  |  |  |  |

| 3 | Турі | cal characteristics 6                 |  |  |  |  |

| 4 | Арр  | lication information 8                |  |  |  |  |

|   | 4.1  | Typical application schematic         |  |  |  |  |

|   | 4.2  | Voltage and current control           |  |  |  |  |

|   |      | 4.2.1 Voltage control                 |  |  |  |  |

|   |      | 4.2.2 Current control                 |  |  |  |  |

|   | 4.3  | Compensation                          |  |  |  |  |

|   | 4.4  | Start up and short circuit conditions |  |  |  |  |

| 5 | Mec  | hanical data                          |  |  |  |  |

| 6 | Revi | sion history14                        |  |  |  |  |

TSM1052 Description

# 1 Description

#### 1.1 Pin connection

Figure 1. Pin Connection (top view)

# 1.2 Pin description

Table 2. Pin description

| N. | Name               | Function                                                                                                                                                                                                                                          |

|----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | V <sub>ctrl</sub>  | Inverting input of the voltage loop op amp. The pin will be tied to the mid-point of a resistor divider that senses the output voltage.                                                                                                           |

| 2  | GND                | Ground. Return of the bias current of the device. 0 V reference for all voltages. The pin should be tied as close to the ground output terminal of the converter as possible to minimize load current effect on the voltage regulation set point. |

| 3  | OUT                | Common open-drain output of the two internal op amps. The pin, able to sink current only, will be connected to the branch of the optocoupler's photodiode to transmit the error signal to the primary side.                                       |

| 4  | I <sub>ctrl</sub>  | Non-inverting input of the current loop op amp. It will be tied directly to the hot (negative) end of the current sense resistor                                                                                                                  |

| 5  | V <sub>sense</sub> | Inverting input of the current loop op amp. The pin will be tied to the cold end of the current sense resistor through a decoupling resistor.                                                                                                     |

| 6  | Vcc                | Supply Voltage of the device. A small bypass capacitor (0.1 $\mu$ F typ.) to GND, located as close to IC's pins as possible, might be useful to get a clean supply voltage.                                                                       |

Description TSM1052

### 1.3 Internal schematic

Figure 2. Internal schematic

# 1.4 Absolute maximum ratings

Table 3. Absolute maximum ratings

|                  |         | <u> </u>           |                         |      |

|------------------|---------|--------------------|-------------------------|------|

| Symbol           | Pin     | Parameter          | Value                   | Unit |

| $V_{CC}$         | 6       | DC supply voltage  | -0.3 to 20              | V    |

| V <sub>OUT</sub> | 3       | Open-drain voltage | -0.3 to V <sub>CC</sub> | V    |

| I <sub>OUT</sub> | 3       | Max sink current   | 100                     | mA   |

| V                | 1, 4, 5 | Analog inputs      | -0.3 to 3.3             | V    |

### 1.5 Thermal data

Table 4. Thermal data

| Symbol            | Parameter                               | Value      | Unit |

|-------------------|-----------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance, junction-to-ambient | 250        | °C/W |

| T <sub>OP</sub>   | Junction temperature operating range    | -10 to 85  |      |

| Tj <sub>max</sub> | Maximum junction temperature 150        |            | °C   |

| T <sub>STG</sub>  | Storage temperature                     | -55 to 150 |      |

#### 2 Electrical characteristics

$T_J = 25$  °C and  $V_{CC} = 5$  V, unless otherwise specified

Table 5. Electrical characteristics

| Table 5.            | Liectifical characteristics                             |                 |       |      |       |      |  |

|---------------------|---------------------------------------------------------|-----------------|-------|------|-------|------|--|

| Symbol              | Parameter                                               | Test conditions | Min   | Тур  | Max   | Unit |  |

| Device supply       |                                                         |                 |       |      |       |      |  |

| V <sub>CC</sub>     | Voltage operating range                                 |                 | 1.7   |      | 18    | ٧    |  |

|                     | Quiescent current                                       |                 |       | 150  |       |      |  |

| I <sub>CC</sub>     | (Ictrl = Vsense = Vctr = 0,<br>OUT = open)              | (1)             |       |      | 300   | μΑ   |  |

| Voltage o           | control loop op amp                                     |                 |       |      |       |      |  |

| Cm                  | Transconductance                                        |                 | 1     | 3.5  |       | S    |  |

| $Gm_v$              | (sink current only) (2)                                 | (1)             |       | 2.5  |       |      |  |

| Vref                | Voltage reference (3)                                   |                 | 1.198 | 1.21 | 1.222 | V    |  |

|                     |                                                         | (1)             | 1.186 |      | 1.234 |      |  |

| lleiee              | Inverting input bias current                            |                 |       | 50   |       | nA   |  |

| Ibias               |                                                         | (1)             |       | 100  |       |      |  |

| Current             | control loop                                            |                 |       |      |       |      |  |

| 0                   | Transconductance                                        |                 | 1.5   | 7    |       | 0    |  |

| Gm <sub>i</sub>     | (sink current only) (4)                                 | (1)             |       |      |       | S    |  |

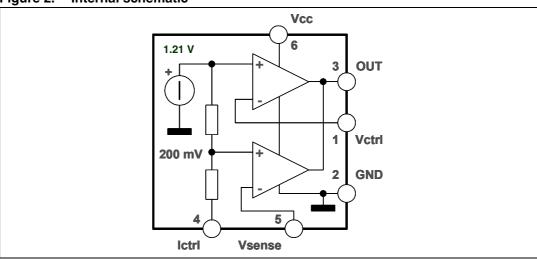

|                     | Current loop reference (5)                              |                 | 196   | 200  | 204   | mV   |  |

|                     | @ I(lout) = 1 mA                                        | (1)             | 192   |      | 208   |      |  |

| Ibias               | Non-inverting input source current @ V(IctrI) = -200 mV |                 |       | 20   |       | μΑ   |  |

|                     |                                                         | (1)             |       | 40   |       |      |  |

| Output s            | tage                                                    |                 |       |      |       |      |  |

| V                   |                                                         |                 |       | 100  |       | m\/  |  |

| V <sub>OUTlow</sub> | Low output level @ 2 mA sink current                    | (1)             |       |      | 200   | - mV |  |

|                     |                                                         |                 |       |      |       |      |  |

<sup>1.</sup> Specification referred to -10  $^{\circ}$ C < T<sub>A</sub> < 85  $^{\circ}$ C

If the voltage on Vctrl (the negative input of the amplifier) is higher than the positive amplifier input (Vref = 1.21 V), and it is increased by 1mV, the sinking current at the output OUT will be increased by 3.5 mA.

<sup>3.</sup> The internal Voltage Reference is set at 1.21 V (bandgap reference). The voltage control loop precision takes into account the cumulative effects of the internal voltage reference deviation as well as the input offset voltage of the transconductance operational amplifier. The internal Voltage Reference is fixed by bandgap, and trimmed to 0.5% accuracy at room temperature.

When the positive input at lctrl is lower than -200 mV, and the voltage is decreased by 1mV, the sinking current at the output Out will be increased by 7 mA.

The internal current sense threshold is set at -200 mV. The current control loop precision takes into

account the cumulative effects of the internal voltage reference deviation as well as the input offset voltage

of the transconductance operational amplifier.

# 3 Typical characteristics

Figure 3. V<sub>ref</sub> vs ambient temperature

Vcc=5V Vcc=1.7V 1.230 1.220 Vref (V) 1.210 1.200 1.190 -20 0 20 40 60 80 100 Temp (°C)

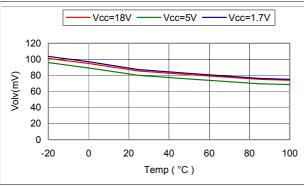

Figure 4. V<sub>SENSE</sub> vs ambient temperature

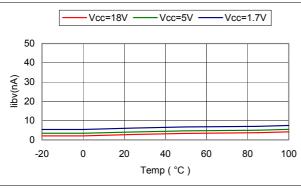

Figure 5. V<sub>SENSE</sub> pin input bias current vs ambient temperature

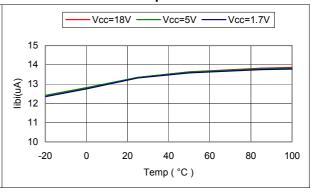

Figure 6. I<sub>CTRL</sub> pin input bias current vs ambient temperature

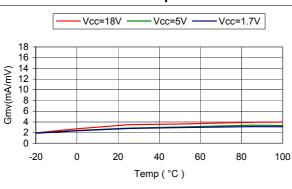

Figure 7. Transconductances (sink current only) of voltage control loop op amp vs ambient temperature

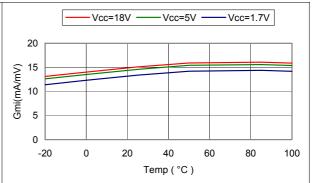

Figure 8. Transconductance (sink current only) of current control loop op amp vs ambient temperature

Figure 9. loop op amp vs ambient temperature (2 mA sink current)

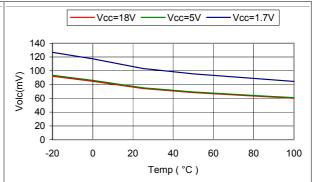

Low output level of voltage control Figure 10. Low output level of current control loop op amp vs ambient temperature (2 mA sink current)

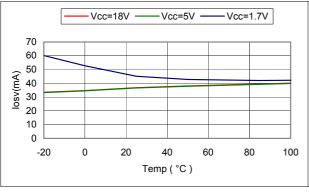

Figure 11. Output short circuit current of voltage control loop op amp vs ambient temperature

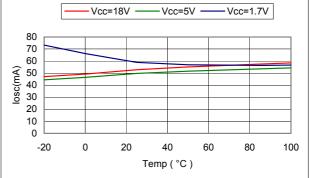

Figure 12. Output short circuit current of current control loop op amp vs ambient temperature

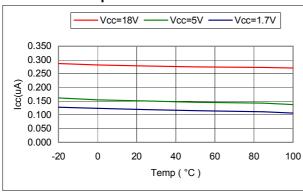

Figure 13. Supply current vs ambient temperature

Figure 14. Low output level vs sink current

### 4 Application information

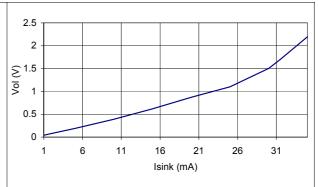

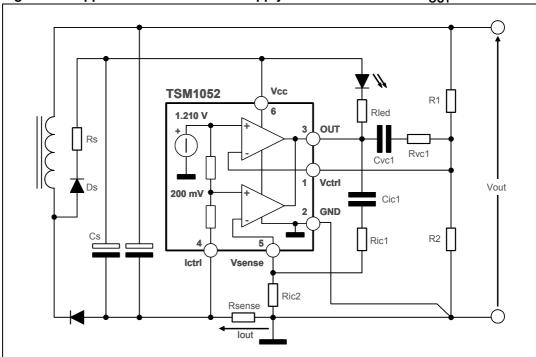

#### 4.1 Typical application schematic

Figure 15. Typical adapter or battery charger application using the device

In the above application schematic, the device is used on the secondary side of a flyback adapter (or battery charger) to provide an accurate control of voltage and current. The above feedback loop is made with an optocoupler.

### 4.2 Voltage and current control

#### 4.2.1 Voltage control

The voltage loop is controlled via a first transconductance operational amplifier, the voltage divider  $R_1$ ,  $R_2$ , and the optocoupler which is directly connected to the output. Its possible to choose the values of R1 and R2 resistors using Equation 1:

#### **Equation 1**

$$V_{out} = V_{ref} \cdot \frac{(R_1 + R_2)}{R_2}$$

b)

$$R_1 = R_2 \cdot \frac{(V_{out} - V_{ref})}{V_{ref}}$$

where Vout is the desired output voltage.

As an example, with R1 = 100 k $\Omega$  and R2 = 27 k $\Omega,\,V_{OUT}$  = 5.7 V

#### 4.2.2 Current control

The current loop is controlled via the second trans-conductance operational amplifier, the sense resistor Rsense, and the optocoupler. The control equation verifies:

#### **Equation 2**

a)

$$R_{\text{sense}} \cdot I_{\text{lim}} = V_{\text{sense}}$$

b)

$$R_{sense} = \frac{V_{sense}}{I_{lim}}$$

where  $I_{lim}$  is the desired limited current, and  $V_{SENSE}$  is the threshold voltage for the current control loop.

As an example, with  $I_{lim} = 1$  A,  $V_{SENSE} = 200$  mV, then  $R_{SENSE} = 200$  m $\Omega$ .

Note:

The Rsense resistor should be chosen taking into account the maximum dissipation ( $P_{lim}$ ) through it during full load operation.

#### **Equation 3**

$$P_{lim} = V_{sense} \cdot I_{lim}$$

As an example, with  $I_{lim} = 1$  A, and  $V_{sense} = 200$  mV,  $P_{lim} = 200$  mW.

Therefore, for most adapter and battery charger applications, a quarter-watt, or half-watt resistor is sufficient.  $V_{SENSE}$  threshold is made internally by a voltage divider tied to the  $V_{ref}$  voltage reference. Its middle point is tied to the positive input of the current control operational amplifier, and its foot is to be connected to lower potential point of the sense resistor as shown in *Figure 15 on page 8*. The resistors of this voltage divider are matched to provide the best possible accuracy. The current sinking outputs of the two transconductance operational amplifiers are common (to the output of the IC). This makes an ORing function which ensures either the voltage control or the current control, driving the optocoupler's photodiode to transmit the feedback to the primary side.

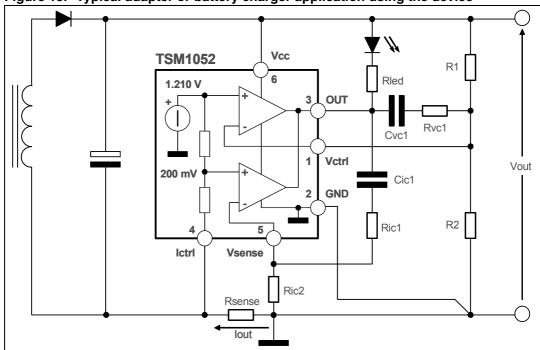

The relation between the controlled current and the controlled output voltage can be described with a square characteristic as shown in the following V/I output-power diagram. (with the power supply of the device indipendent of the output voltage)

Figure 16. Output voltage versus output current

#### 4.3 Compensation

The voltage control transconductance operational amplifier can be fully compensated. Both of its output and negative input are directly accessible for external compensation components.

An example of a suitable compensation network is shown in *Figure 15*. It consists of a capacitor  $C_{VC1} = 2.2$  nF and a resistor  $R_{CV1} = 470$  k $\Omega$  in series.

The current-control transconductance operational amplifier can be fully compensated. Both its output and negative input are directly accessible for external compensation components. An example of a suitable compensation network is shown in *Figure 15*. It consists of a capacitor  $C_{IC1}=2.2$  nF and a resistor  $R_{IC1}=22$  k $\Omega$  in series. In order to increase the stability of the application it is suggested to add a resistor in series with the optocoupler. An example of a suitable  $R_{I,ED}$  value could be 330  $\Omega$  in series with the optocoupler.

### 4.4 Start up and short circuit conditions

Under start-up or short-circuit conditions if the device is supplied from SMPS output and the output voltage is lower than Vcc minimum the current regulation is not guaranteed.

Therefore, the current limitation can only be ensured by the primary PWM module, which should be chosen accordingly.

If the primary current limitation is considered not to be precise enough for the application, then a sufficient supply for the device has to be ensured under any condition. It would then be necessary to add some circuitry to supply the chip with a separate power line. This can be achieved in numerous ways, including an additional winding on the transformer.

The following schematic shows how to realize a low-cost power supply for the device (with no additional windings).

Figure 17. Application circuit able to supply the device even with  $V_{OUT} = 0$

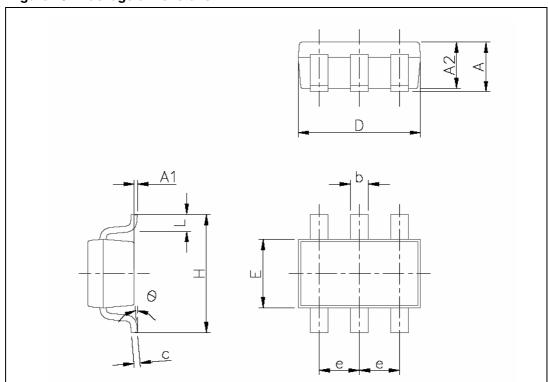

# 5 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK<sup>®</sup> packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

Table 6. SOT23-6 mechanical data

| Dim  | mm.  |      |      | inch  |       |        |

|------|------|------|------|-------|-------|--------|

| Dim. | Min  | Тур  | Max  | Min   | Тур   | Max    |

| Α    |      | 0.9  | 1.45 |       | 0.035 | 0.057  |

| A1   |      | 0    | 0.1  |       | 0     | 0.0039 |

| A2   |      | 0.9  | 1.3  |       | 0.035 | 0.0512 |

| b    |      | 0.35 | 0.5  |       | 0.014 | 0.02   |

| С    |      | 0.09 | 0.2  |       | 0.004 | 0.008  |

| D    |      | 2.8  | 3.05 |       | 0.11  | 0.120  |

| Е    |      | 1.5  | 1.75 |       | 0.059 | 0.0689 |

| е    | 0.95 |      |      | 0.037 |       |        |

| Н    |      | 2.6  | 3    |       | 0.102 | 0.118  |

| L    |      | 0.1  | 0.6  |       | 0.004 | 0.024  |

| θ    |      | 0    | 10°  |       | 0     | 10°    |

Note: Dimensions per JEDEC MO178AB

Figure 18. Package dimensions

Revision history TSM1052

# 6 Revision history

Table 7. Document revision history

| Date        | Revision | Changes                       |  |

|-------------|----------|-------------------------------|--|

| 20-Feb-2007 | 1        | Initial release.              |  |

| 07-Feb-2008 | 2        | Updated: Section 5 on page 12 |  |