# KTTWRCM3120UG TWR-CM3120-EVM Tower System Platform Rev. 2.0 — 8 May 2017

User guide

# TWR-CM3120-EVM

# 2 Important notice

NXP provides the enclosed product(s) under the following conditions:

This evaluation kit is intended for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY. It is provided as a sample IC pre-soldered to a printed circuit board to make it easier to access inputs, outputs, and supply terminals. This evaluation board may be used with any development system or other source of I/O signals by simply connecting it to the host MCU or computer board via off-the-shelf cables. This evaluation board is not a Reference Design and is not intended to represent a final design recommendation for any particular application. Final device in an application will be heavily dependent on proper printed circuit board layout and heat sinking design as well as attention to supply filtering, transient suppression, and I/O signal quality.

The goods provided may not be complete in terms of required design, marketing, and or manufacturing related protective considerations, including product safety measures typically found in the end product incorporating the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge. In order to minimize risks associated with the customers applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. For any safety concerns, contact NXP sales and technical support services.

Should this evaluation kit not meet the specifications indicated in the kit, it may be returned within 30 days from the date of delivery and will be replaced by a new kit.

NXP reserves the right to make changes without further notice to any products herein. NXP makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical", must be validated for each customer application by customer's technical experts.

NXP does not convey any license under its patent rights nor the rights of others. NXP products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the NXP product could create a situation where personal injury or death may occur.

Should the Buyer purchase or use NXP products for any such unintended or unauthorized application, the Buyer shall indemnify and hold NXP and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges NXP was negligent regarding the design or manufacture of the part.

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © NXP B.V. 2017.

# 3 Getting started

# 3.1 Kit contents/packing list

The kit contents include:

- · Assembled and tested TWR-CM3120-EVM tower board in an anti-static bag

- · Quick Start Guide, Analog Tools

- · Warranty card

# 3.2 Jump start

NXP's analog product development boards provide an easy-to-use platform for evaluating NXP products. The boards support a range of analog, mixed-signal and power solutions. They incorporate monolithic ICs and system-in-package devices that use proven high-volume technology. NXP products offer longer battery life, a smaller form factor, reduced component counts, lower cost and improved performance in powering state of the art systems.

- 1. Go to www.nxp.com/TWR-CM3120-EVM

- 2. Review your Tool Summary Page.

- 3. Locate and click:

# Jump Start Your Design

4. Download the documents, software and other information.

Once the files are downloaded, review the user guide in the bundle. The user guide includes setup instructions, BOM and schematics. Jump start bundles are available on each tool summary page with the most relevant and current information. The information includes everything needed for design.

# 3.3 Required equipment

To use this kit, you need:

- Power supply 24 V/3.0 A

- Mini-USB cable (power for the tower logic)

- PC

- IO-Link compatible sensors/actors

# 3.4 System requirements

The kit requires the following:

- USB-enabled PC with Windows® 7 or higher

- NET framework 4.0 or higher

# 4 Understanding the Tower System

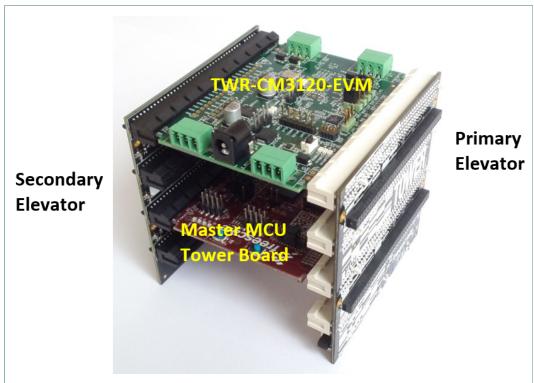

NXP's Tower System peripheral module is designed to be combined and used with other Tower System modules.

The NXP Tower System is a modular development platform for 8-, 16-, and 32-bit MCUs and MPUs, enabling advanced development through rapid prototyping. Featuring more than fifty development boards or modules, the Tower System provides designers with building blocks for entry-level to advanced MCU development.

TWR-CM3120-EVM can be associated with the TWR-K70F120M or TWR-K20D72M. Special care should be taken with the MCU board. TWR-CM3120-EVM can also work as a stand-alone board without using the rest of the tower system. In this case, the USB from PC is connected directly to the TWR-CM3120-EVM USB (placed on the bottom side). When working as a stand-alone board, the provided GUI can be used to control the IO-Link communication.

Figure 2. TWR-CM3120-EVM on Tower System

# 5 Getting to know the hardware

### 5.1 Board overview

The TWR-CM3120-EVM is an easy-to-use tower peripheral module circuit board allowing the user to exercise functions for IO-Link Master Transceivers.

### 5.2 Board features

The hardware system features are as follows:

- Four fully featured IO-Link ports based on two CM3120 and Kinetis MKL17Z64VFM4

- On-board ESD protection

- Modular solution stackable for multiple of four port solution

- Operating voltage range from 8.0 V to 32 V

- Optional external NMOS transistors to control current to the C/Q and L+ lines

- Four IO-Link communication status LEDs

The software system features are as follows:

- · IO-Link stack loaded in the embedded MCU

- Integrated Bootloader through SPI for IO-Link stack updates

- · Graphical Users Interface on PC

- Configurable through a SPI interface

# 5.3 Device features

The tower system feature the following NXP products:

Table 1. Device features

| Device       | Description                                                                                                               | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MKL17Z64VFM4 | Kinetis® KL1x-48 MHz,<br>Mainstream Small Ultra-Low<br>Power Microcontrollers (MCUs)<br>based on ARM® Cortex®-M0+<br>Core | <ul> <li>MCU MKL17Z64VFM4 (ARM® Cortex®-M0+core up to 48 MHz, 64 KB program flash, 16 KB SRAM)</li> <li>Embedded ROM with boot loader for flexible program upgrade</li> <li>High accuracy internal voltage and clock reference</li> <li>FlexIO to support any standard and customized serial peripheral emulation</li> <li>Hardware CRC module</li> <li>Down to 46 μA/MHz in very low power run mode and 1.68 μA in stop mode (RAM + RTC retained)</li> </ul>                                                                                                                                                              |

| MC34CM3120EP | Dual Transceiver IO-Link Master IC                                                                                        | <ul> <li>2 IO-Link channels with three different operation modes (SIO, UART, and frame handler)</li> <li>Protection mechanisms (overcurrent, overtemperature, overvoltage)</li> <li>Configurable through a SPI interface</li> <li>Operating voltage range from 8.0 V to 32 V</li> <li>Suitable for 2/4/8/16 port-applications</li> <li>Can operate as a Master or Device</li> <li>Two integrated LED drivers</li> <li>Integrated hardware frame handler (supports all IO-link v1.1 frames and COM1, COM2, and COM3 baud rates)</li> <li>Integrated NMOS gate drivers to control current to the C/Q and L+ lines</li> </ul> |

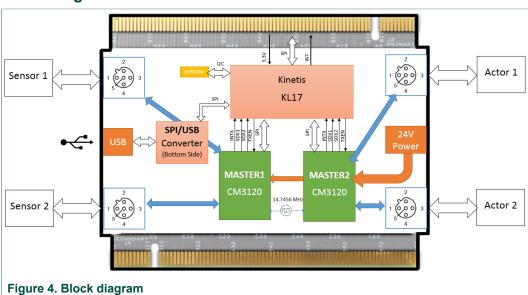

# 5.4 Block diagram

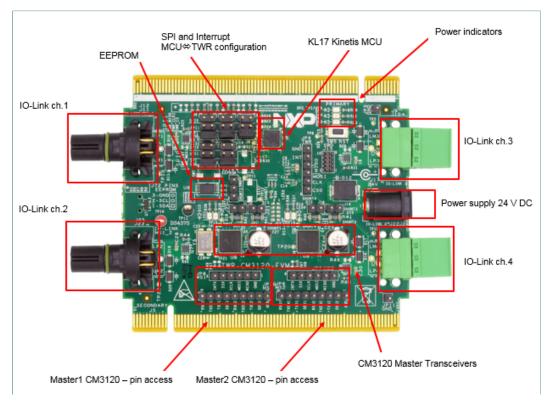

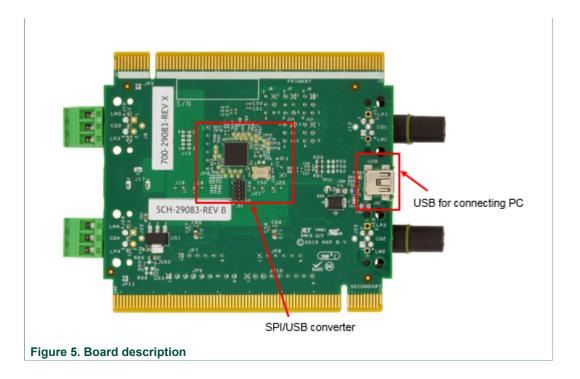

# 5.5 Board description

All the components that support the IO-Link functionality are placed on the top layer. Bottom layer is dedicated to SPI/USB converter that enables users to connect PC and to control IO-Link from the provided GUI.

The board includes two microcontrollers. IO-Link stack runs on Kinetis KL17 (top layer) and the SPI/USB converter on Kinetis KL25. SPI/USB converter can be bypassed by using jumpers J6, J7, J8, J13 and J14. In this case, the SPI is mapped to the standard tower elevators and an additional MCU is used to get information from the IO-Link Master stack.

# 5.5.1 LED display

The following LEDs are provided as visual output devices for the board:

| LED ID | Description                                  |

|--------|----------------------------------------------|

| D5     | Power supply indicator for SPI/USB converter |

| D6     | 24V power supply indicator                   |

| D7     | 3V3 power supply indicator                   |

| D13    | IO-Link channel 3, communication indicator   |

| D14    | IO-Link channel 4, communication indicator   |

| D15    | IO-Link channel 1, communication indicator   |

| D16    | IO-Link channel 2, communication indicator   |

# 5.5.2 Jumper, connector and switch definitions

<u>Table 2</u> describes the function and settings for each jumper, connector and switch.

Table 2. Jumper, connector and switch definitions

| Part reference | Pin number/pin configuration | Pin name | Description                        |

|----------------|------------------------------|----------|------------------------------------|

| J6             | SPI bus MISO - Tower <=> KL1 | 7        |                                    |

|                | 1-2                          |          | SPI0 is used                       |

|                | 3-4                          |          | SPI1 is used                       |

|                | 5-6                          |          | On-board SPI/USB converter is used |

| J8             | SPI bus CS - Tower <=> KL17  |          | ,                                  |

|                | 1-2                          |          | SPI0 is used                       |

|                | 3-4                          |          | SPI1 is used                       |

KTTWRCM3120UG

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2017. All rights reserved.

| Part reference | Pin number/pin configuration                                       | Pin name              | Description                        |

|----------------|--------------------------------------------------------------------|-----------------------|------------------------------------|

|                | 5-6                                                                |                       | On-board SPI/USB converter is used |

| J10            | 1                                                                  | L+                    | Power line (typ. +24 V)            |

|                | 2                                                                  | C/Q                   | Communication line                 |

|                | 3                                                                  | L-                    | Ground                             |

| J11            | 1                                                                  | L+                    | Power line (typ. +24 V)            |

|                | 2                                                                  | C/Q                   | Communication line                 |

|                | 3                                                                  | L-                    | Ground                             |

| J13            | Interrupt - Tower <=> KL17                                         |                       | ,                                  |

|                | 1-2                                                                |                       | TWR_INT1 is used                   |

|                | 3-4                                                                |                       | TWR_INT2 is used                   |

|                | 5-6                                                                |                       | On-board SPI/USB converter is used |

| J14            | SPI bus MOSI - Tower <=> KL1                                       | 7                     |                                    |

|                | 1-2                                                                |                       | SPI0 is used                       |

|                | 3-4                                                                |                       | SPI1 is used                       |

|                | 5-6                                                                |                       | On-board SPI/USB converter is used |

| J16            | EEPROM I2C bus debug conne                                         | ctor (Do not populate | e with a jumper)                   |

|                | 1                                                                  | SDA                   |                                    |

|                | 2                                                                  | SCL                   |                                    |

|                | 3                                                                  | Ground                |                                    |

| J17            | 24 V power input                                                   |                       | <del>- +</del>                     |

| J18            | Shunt 4 bypass (populate jumper if the external sense is not used) |                       |                                    |

| J19            | Shunt 3 bypass (populate jumper if the external sense is not used) |                       |                                    |

| J20            | Shunt 2 bypass (populate jumper if the external sense is not used) |                       |                                    |

| J21            | Shunt 1 bypass (populate jumper if the external sense is not used) |                       |                                    |

| J123           | 1                                                                  | L+                    | Power line (typ. +24V)             |

|                | 2                                                                  | C/Q                   | Communication line                 |

|                | 3                                                                  | L-                    | Ground                             |

| J24            | 1                                                                  | L+                    | Power line (typ. +24V)             |

|                | 2                                                                  | C/Q                   | Communication line                 |

|                | 3                                                                  | L-                    | Ground                             |

| J47            | SPI bus CLK- Tower <=> KL17                                        |                       | J                                  |

| Part reference | Pin number/pin configuration  | Pin name         | Description                          |  |  |  |  |  |

|----------------|-------------------------------|------------------|--------------------------------------|--|--|--|--|--|

|                | 1-2                           |                  | SPI0 is used                         |  |  |  |  |  |

|                | 3-4                           |                  | SPI1 is used                         |  |  |  |  |  |

|                | 5-6                           |                  | On-board SPI/USB converter is used   |  |  |  |  |  |

| J52            | Mini-USB                      |                  |                                      |  |  |  |  |  |

| J54            | IO-Link channel 1             |                  |                                      |  |  |  |  |  |

|                | 1                             | L+               | Power line (typ. +24 V)              |  |  |  |  |  |

|                | 2                             | DI/DQ            | Additional I/O                       |  |  |  |  |  |

|                | 3                             | L-               | Ground                               |  |  |  |  |  |

|                | 4                             | C/Q              | Communication line                   |  |  |  |  |  |

| J55            | IO-Link channel 2             |                  |                                      |  |  |  |  |  |

|                | 1                             | L+               | Power line (typ. +24 V)              |  |  |  |  |  |

|                | 2                             | DI/DQ            | Additional I/O                       |  |  |  |  |  |

|                | 3                             | L-               | Ground                               |  |  |  |  |  |

|                | 4                             | C/Q              | Communication line                   |  |  |  |  |  |

| J56            | IO-Link channel 4             |                  |                                      |  |  |  |  |  |

|                | 1                             | L+               | Power line (typ. +24 V)              |  |  |  |  |  |

|                | 2                             | DI/DQ            | Additional I/O                       |  |  |  |  |  |

|                | 3                             | L-               | Ground                               |  |  |  |  |  |

|                | 4                             | C/Q              | Communication line                   |  |  |  |  |  |

| J57            | IO-Link channel 3             |                  | ,                                    |  |  |  |  |  |

|                | 1                             | L+               | Power line (typ. +24 V)              |  |  |  |  |  |

|                | 2                             | DI/DQ            | Additional I/O                       |  |  |  |  |  |

|                | 3                             | L-               | Ground                               |  |  |  |  |  |

|                | 4                             | C/Q              | Communication line                   |  |  |  |  |  |

| J59            | Serial Wire Debug connector   |                  | ,                                    |  |  |  |  |  |

|                | 1                             | 3V3              |                                      |  |  |  |  |  |

|                | 2                             | SWD_DIO          |                                      |  |  |  |  |  |

|                | 3                             | Ground           |                                      |  |  |  |  |  |

|                | 4                             | SWD_CLK          |                                      |  |  |  |  |  |

|                | 5                             | Ground           |                                      |  |  |  |  |  |

|                | 6                             | NC               |                                      |  |  |  |  |  |

|                | 7                             | NC               |                                      |  |  |  |  |  |

|                | 8                             | NC               |                                      |  |  |  |  |  |

|                | 9                             | NC               |                                      |  |  |  |  |  |

|                | 10                            | RST_MCU          |                                      |  |  |  |  |  |

|                |                               |                  | <del></del>                          |  |  |  |  |  |

| JP5            | Ground - Test point           |                  |                                      |  |  |  |  |  |

| JP6            | SPI bus and interrupt TWR <=> | KL17 debug conne | ctor (Do not populate with a jumper) |  |  |  |  |  |

|                | 1                             | Ground           |                                      |  |  |  |  |  |

|                | 2                             | INTX             |                                      |  |  |  |  |  |

| Part reference | Pin number/pin configuration   | Pin name              | Description    |

|----------------|--------------------------------|-----------------------|----------------|

|                | 3                              | MISO                  |                |

|                | 4                              | MOSI                  |                |

|                | 5                              | CLK                   |                |

|                | 6                              | CS0                   |                |

| JP7            | Master 2 SPI bus debug connec  | tor (Do not populate  | with a jumper) |

|                | 1                              | Ground                |                |

|                | 2                              | MISO                  |                |

|                | 3                              | MOSI                  |                |

|                | 4                              | SCLK                  |                |

|                | 5                              | SSX                   |                |

|                | 6                              | INTX                  |                |

| JP8            | Master 1 SPI bus debug connec  | tor (Do not populate  | with a jumper) |

|                | 1                              | Ground                |                |

|                | 2                              | MISO                  |                |

|                | 3                              | MOSI                  |                |

|                | 4                              | SCLK                  |                |

|                | 5                              | SSX                   |                |

|                | 6                              | INTX                  |                |

| JP9            | Master 2 debug connector (Do n | ot populate with a ju | mper)          |

|                | 1                              | Ground                |                |

|                | 2                              | SDX                   |                |

|                | 3                              | TXD                   |                |

|                | 4                              | TXEN                  |                |

|                | 5                              | RXD                   |                |

|                | 6                              | SDX                   |                |

|                | 7                              | TXD                   |                |

|                | 8                              | TXEN                  |                |

|                | 9                              | RXD                   |                |

| JP10           | Master 1 debug connector (Do n | ot populate with a ju | mper)          |

|                | 1                              | Ground                |                |

|                | 2                              | SDX                   |                |

|                | 3                              | TXD                   |                |

|                | 4                              | TXEN                  |                |

|                | 5                              | RXD                   |                |

|                | 6                              | SDX                   |                |

|                | 7                              | TXD                   |                |

|                | 8                              | TXEN                  |                |

|                | 9                              | RXD                   |                |

| JP11           | Ground - Test point            | l.                    | J              |

| Part reference | Pin number/pin configuration           | Pin name | Description |

|----------------|----------------------------------------|----------|-------------|

| SW5            | Kinetis KL17 reset                     |          |             |

| SW6            | Kinetis KL17 ROM Bootloader activation |          |             |

| SW7            | Kinetis KL25 Bootloader activation     |          |             |

| SW8            | Kinetis KL25 reset                     |          |             |

### 5.5.3 Elevator connections

The board features two expansion card-edge connectors that interface to elevator boards in a Tower System: the Primary and Secondary Elevator connectors. <u>Table 3</u> provides the pinouts for the Primary Elevator connector. There is no connection for the Secondary Elevator connectors.

Table 3. Primary elevator connector pinouts

| Top side of primary connector side B |           |       |            | Bottom side | Bottom side of primary connector side A |          |            |

|--------------------------------------|-----------|-------|------------|-------------|-----------------------------------------|----------|------------|

| Pin#                                 | Name      | Group | Usage      | Pin #       | Name                                    | Group    | Usage      |

| B1                                   | 5V        | Power | 5.0V Power | A1          | 5V                                      | Power    | 5.0V Power |

| B2                                   | GND       | Power | Ground     | A2          | GND                                     | Power    | Ground     |

| В3                                   | 3.3V      | Power | 3.3V Power | А3          | 3.3V                                    | Power    | 3.3V Power |

| B4                                   | NC        |       |            | A4          | 3.3V                                    | Power    | 3.3V Power |

| B5                                   | GND       | Power | Ground     | A5          | GND                                     | Power    | Ground     |

| B6                                   | GND       | Power | Ground     | A6          | GND                                     | Power    | Ground     |

| B7                                   | SPI1_CLK  | SPI 1 |            | A7          |                                         |          |            |

| B8                                   | SPI1_CS1  | SPI 1 |            | A8          |                                         |          |            |

| В9                                   | SPI1_CS0  | SPI 1 |            | A9          |                                         |          |            |

| B10                                  | SPI1_MOSI | SPI 1 |            | A10         |                                         |          |            |

| B11                                  | SPI1_MISO | SPI 1 |            | A11         |                                         |          |            |

| Mechani                              | ical key  |       | ,          | '           | '                                       | <u> </u> | '          |

| B12                                  | NC        |       |            | A12         |                                         |          |            |

| B13                                  | NC        |       |            | A13         |                                         |          |            |

| B14                                  | NC        |       |            | A14         |                                         |          |            |

| B15                                  | NC        |       |            | A15         |                                         |          |            |

| B16                                  | NC        |       |            | A16         |                                         |          |            |

| B17                                  | NC        |       |            | A17         |                                         |          |            |

| B18                                  | NC        |       |            | A18         |                                         |          |            |

| B19                                  | NC        |       |            | A19         |                                         |          |            |

| B20                                  | NC        |       |            | A20         |                                         |          |            |

| B21                                  | NC        |       | 20_IN0     | A21         |                                         |          |            |

| B22                                  | NC        |       | 06_IN1     | A22         |                                         |          |            |

| B23                                  | NC        |       |            | A23         |                                         |          |            |

| B24                                  | NC        |       |            | A24         |                                         |          |            |

| B25                                  | NC        |       |            | A25         |                                         |          |            |

KTTWRCM3120UG

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2017. All rights reserved.

| Top side of primary connector side B |           |            |                       |       | Bottom side of primary connector side A |       |            |

|--------------------------------------|-----------|------------|-----------------------|-------|-----------------------------------------|-------|------------|

| Pin#                                 | Name      | Group      | Usage                 | Pin # | Name                                    | Group | Usage      |

| B26                                  | GND       | Power      | Ground                | A26   | GND                                     | Power | Ground     |

| B27                                  |           |            |                       | A27   |                                         |       |            |

| B28                                  |           |            |                       | A28   |                                         |       |            |

| B29                                  |           |            |                       | A29   |                                         |       |            |

| B30                                  |           |            |                       | A30   |                                         |       |            |

| B31                                  | GND       | Power      | Ground                | A31   | GND                                     | Power | Ground     |

| B32                                  |           |            |                       | A32   |                                         |       |            |

| B33                                  |           |            |                       | A33   |                                         |       |            |

| B34                                  |           |            |                       | A34   |                                         |       |            |

| B35                                  |           |            |                       | A35   |                                         |       |            |

| B36                                  | 3.3V      | Power      | 3.3V Power            | A36   | 3.3V                                    | Power | 3.3V Power |

| B37                                  |           |            |                       | A37   |                                         |       |            |

| B38                                  |           |            |                       | A38   |                                         |       |            |

| B39                                  |           |            |                       | A39   |                                         |       |            |

| B40                                  |           |            |                       | A40   |                                         |       |            |

| B41                                  |           |            |                       | A41   |                                         |       |            |

| B42                                  |           |            |                       | A42   |                                         |       |            |

| B43                                  |           |            |                       | A43   |                                         |       |            |

| B44                                  | SPI0_MISO | SPI 0      | MISO                  | A44   |                                         |       |            |

| B45                                  | SPI0_MOSI | SPI 0      | MOSI                  | A45   |                                         |       |            |

| B46                                  | SPI0_CS0  | SPI 0      |                       | A46   |                                         |       |            |

| B47                                  | SPI0_CS1  | SPI 0      |                       | A47   |                                         |       |            |

| 348                                  | SPI0_CLK  | SPI 0      | CLK                   | A48   |                                         |       |            |

| B49                                  | GND       | Power      | Ground                | A49   | GND                                     | Power | Ground     |

| B50                                  |           | I2C 1      |                       | A50   |                                         |       |            |

| B51                                  |           | I2C 1      |                       | A51   |                                         |       |            |

| B52                                  |           | GPIO/SPI 0 | 50_IN0 <sup>[1]</sup> | A52   |                                         |       |            |

| B53                                  |           | USB 0      |                       | A53   |                                         |       |            |

| B54                                  |           | USB 0      |                       | A54   |                                         |       |            |

| B55                                  |           | Interrupt  |                       | A55   |                                         |       |            |

| B56                                  | IRQ_G     | Interrupt  |                       | A56   |                                         |       |            |

| B57                                  | _         | Interrupt  | 06_FSB                | A57   |                                         |       |            |

| B58                                  | IRQ_E     | Interrupt  | _                     | A58   |                                         |       |            |

| B59                                  |           | Interrupt  | 06_FSB                | A59   |                                         |       |            |

| B60                                  | IRQ_C     | Interrupt  | _                     | A60   |                                         |       |            |

| B61                                  |           | Interrupt  |                       | A61   |                                         |       |            |

| B62                                  | IRQ_A     | Interrupt  | 06_SYNC               | A62   |                                         |       |            |

| B63                                  |           | EBI        |                       | A63   |                                         |       |            |

| B64                                  |           | EBI        |                       | A64   |                                         |       |            |

| B65                                  | GND       | Power      | Ground                | A65   | GND                                     | Power | Ground     |

| Top side of primary connector side B |      |       |            |       | Bottom side | of primary conne | ctor side A |

|--------------------------------------|------|-------|------------|-------|-------------|------------------|-------------|

| Pin#                                 | Name | Group | Usage      | Pin # | Name        | Group            | Usage       |

| B66                                  |      | EBI   |            | A66   |             |                  |             |

| B67                                  |      |       |            | A67   |             |                  |             |

| B68                                  |      |       |            | A68   |             |                  |             |

| B69                                  |      |       |            | A69   |             |                  |             |

| B70                                  |      |       |            | A70   |             |                  |             |

| B71                                  |      |       |            | A71   |             |                  |             |

| B72                                  |      |       |            | A72   |             |                  |             |

| B73                                  |      |       |            | A73   |             |                  |             |

| B74                                  |      |       |            | A74   |             |                  |             |

| B75                                  |      |       |            | A75   |             |                  |             |

| B76                                  |      |       |            | A76   |             |                  |             |

| B77                                  |      |       |            | A77   |             |                  |             |

| B78                                  |      |       |            | A78   |             |                  |             |

| B79                                  |      |       |            | A79   |             |                  |             |

| B80                                  |      |       |            | A80   |             |                  |             |

| B81                                  | GND  | Power | Ground     | A81   | GND         | Power            | Ground      |

| B82                                  | 3.3V | Power | 3.3V Power | A82   | 3.3V        | Power            | 3.3V Power  |

<sup>[1]</sup> The 50\_IN1 is not available.

# 5.6 Installing the software and setting up the hardware

# 5.6.1 Setting up the hardware

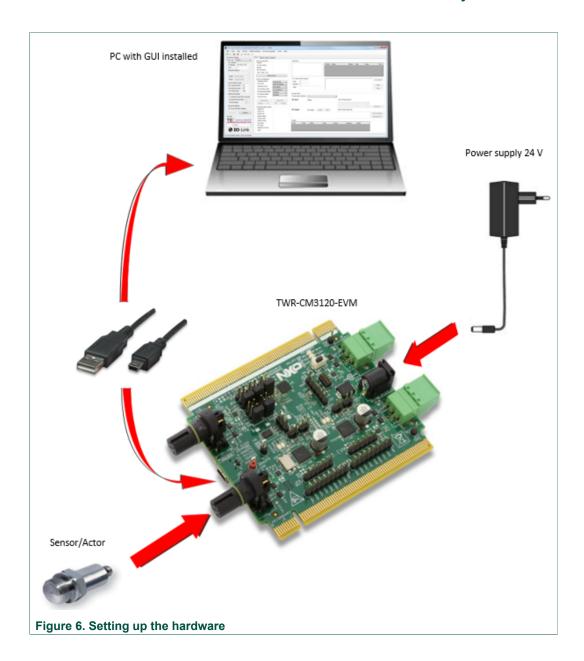

Follow the instructions to setup the demo properly:

- 1. To use the on-board SPI/USB converter, some jumpers are configured as shown in Table 4.

- 2. Connect IO-Link compatible sensor/actor to one of the four IO-Link ports (J11/J54, J23/J55, J10/J57 or J24/J56).

- 3. Plug 24 V DC power supply to the J17 on the TWR-CM3120-EVM (positive pin is in the center).

- 4. Connect J52 (placed on the bottom side) to the PC using a mini-USB cable

- 5. Launch the Graphical User Interface on the PC (see <u>Section 5.6.2 "Installing the software"</u> for details).

# **Table 4. Jumper configuration**

| Jumper | Jumper configuration |

|--------|----------------------|

| J6     | 5-6                  |

| J7     | 5-6                  |

| J8     | 5-6                  |

| J13    | 5-6                  |

| J14    | 5-6                  |

# 5.6.2 Installing the software

# 5.6.2.1 Installing USB driver

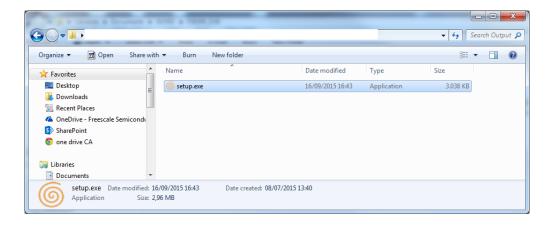

USB driver is compatible with Windows operating systems (Windows 7 and higher).

1. To install the driver, launch "setup.exe" and follow the instructions.

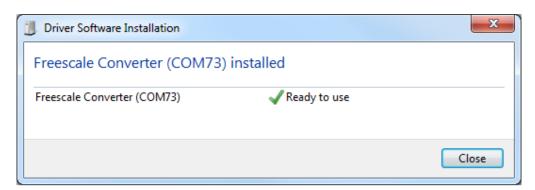

2. Connect HW to your PC and wait for its installation. When the hardware is installed properly, the following screen is displayed.

### Note:

Provided driver is not signed by Microsoft, so it cannot be installed on machines where the signature is mandatory. On Windows 7, the user has a possibility during the installation process to omit this signature (necessary for proper installation). On Windows 8, the user has no choice during installation process and the signature is requested (default Windows 8 configuration). This setting on Windows 8 can be changed in advanced options (for details, see the Windows 8 driver installation troubleshooting).

### Important:

Do not launch the Control tool before the hardware is connected and installed correctly.

### 5.6.2.2 Installing control tool

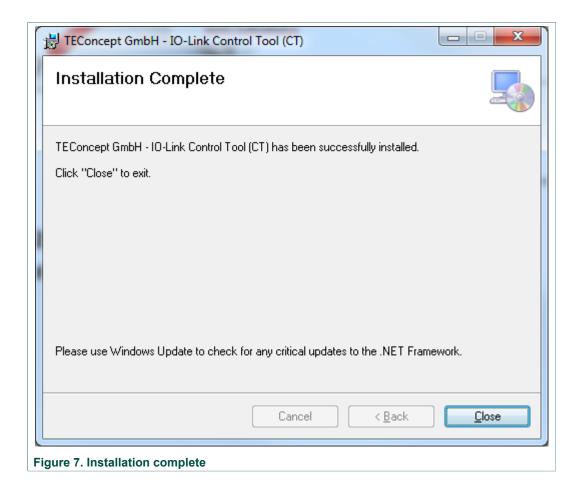

- 1. Launch the "TC\_Installer.msi"

- 2. Follow the instructions.

- 3. If everything goes well, the installation completes in few seconds with the following window:

KTTWRCM3120UG

# 5.6.2.3 Working with the control tool

After successful installation, connect the hardware as described in <u>Section 5.6.1 "Setting</u> up the hardware". Launch the GUI from the Start menu:

To setup the control tool with the TWR-CM3120-EVM properly, follow these instructions.

- Choose the Master:

Master settings -> Add Master -> 4 port Master

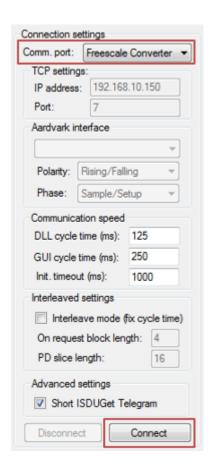

- 2. Choose interface:

- a. Click Connection settings.

b. Select SPI/USB interface (Freescale Converter) and click Connect.

KTTWRCM3120UG

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2017. All rights reserved.

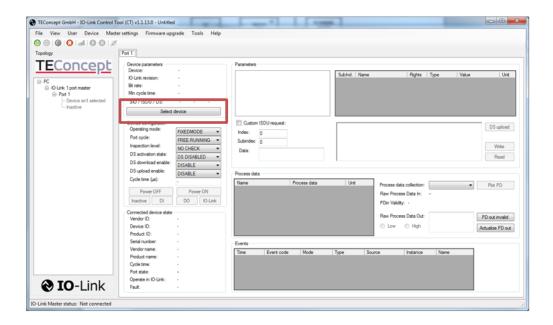

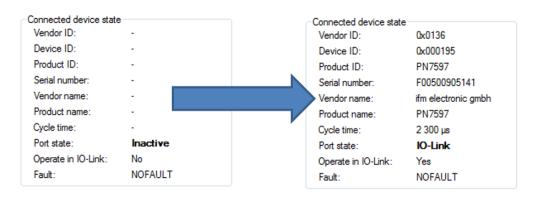

3. If the connection to the Master device is successful, the status bar on the bottom of the main window shows **Connected at**.

4. When the connection is established, the control window appears.

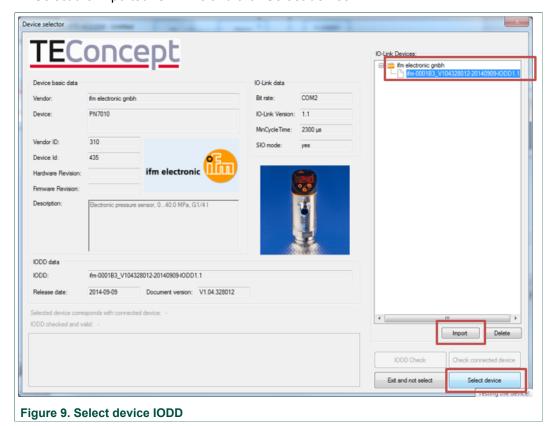

- 5. Select your device by clicking Select device.

- 6. Import IODD description file of your device.

- · Click Import.

- · Select the right IODD file.

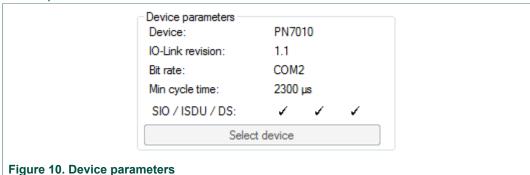

- 7. Select the imported IODD file and click **Select device**.

Now the sensor is successfully connected and ready to be used.

KTTWRCM3120UG

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2017. All rights reserved.

### 5.6.2.4 Read basic data through IO-link

The following instructions guide the user how to read basic data through the IO-link:

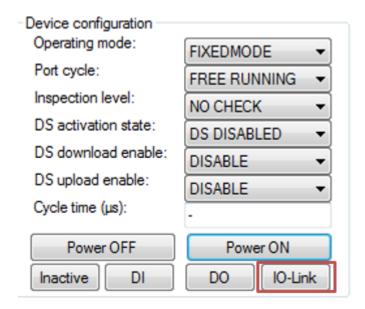

- 1. Try to switch the sensor ON and OFF.

- Click Power OFF (sensor must switch OFF completely).

- Click Power ON (sensor must switch ON).

- 2. Establish IO-Link communication with the sensor (click IO-Link).

3. The sensor parameters appear.

### 5.6.2.5 Interface description

### 5.6.2.5.1 Device parameters

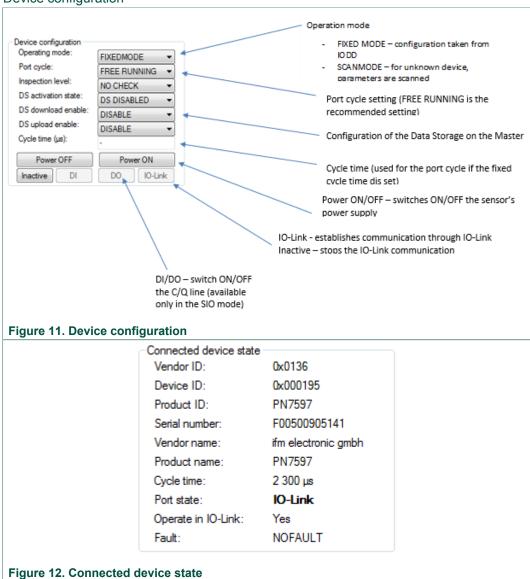

### 5.6.2.5.2 Device configuration

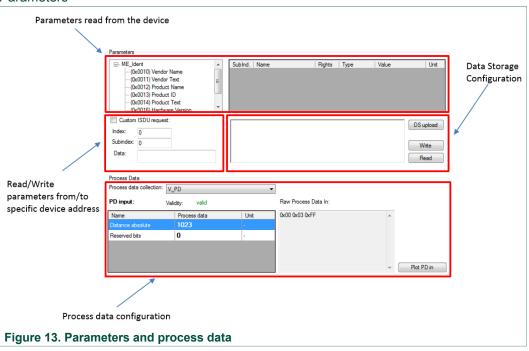

### 5.6.2.5.3 Parameters

# 5.7 Schematics, board layout and bill of materials

Board schematics, board layout and bill of materials are available in the download tab of the tool summary page: <a href="https://www.nxp.com/TWR-CM3120-EVM">www.nxp.com/TWR-CM3120-EVM</a>

# 5.8 References

The following URLs reference related NXP products and application solutions:

| NXP.com support pages | Description                                        | URL                                           |

|-----------------------|----------------------------------------------------|-----------------------------------------------|

|                       | Tool summary page                                  | www.nxp.com/TWR-CM3120-EVM                    |

| TWR-CM3120-EVM        | Schematic, BOM, board layout                       | www.nxp.com/TWR-CM3120-EVM (Download section) |

| Tower System          | Tower System Modular Development<br>Board Platform | www.nxp.com/tower                             |

| TWR-K65F180M          | www.nxp.com/TWR-K65F180M                           | www.nxp.com/TWR-K65F180M                      |

# 5.9 Contact information

Visit <a href="http://www.nxp.com/support">http://www.nxp.com/support</a> for a list of phone numbers within your region.

Visit <a href="http://www.nxp.com/warranty">http://www.nxp.com/warranty</a> to submit a request for tool warranty.

# 5.10 Revision history

Table 5. Revision history

| Document ID        | Release date            | User guide status | Change notice | Supersedes |  |

|--------------------|-------------------------|-------------------|---------------|------------|--|

| KTTWRCM3120UG v2.0 | 20170508                | _                 | _             | 1.0        |  |

| Modifications      | Updated document format |                   |               |            |  |

| KTTWRCM3120UG v1.0 | 20151110                | Initial release   | _             | _          |  |

# 6 Legal information

### 6.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 6.2 Disclaimers

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit,

and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/ or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/salestermsandconditions.

### 6.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

NXP — is a trademark of NXP B.V.

the NXP logo — is a trademark of NXP B.V.

Freescale — is a trademark of NXP B.V.

the Freescale logo — is a trademark of NXP B.V.

**SMARTMOS** — is a trademark of NXP B.V.

# KTTWRCM3120UG

# TWR-CM3120-EVM Tower System Platform

# **Tables**

| Tab. 1.<br>Tab. 2.<br>Tab. 3. | Device features                        | Tab. 4.<br>Tab. 5. | Jumper configuration Revision history |    |

|-------------------------------|----------------------------------------|--------------------|---------------------------------------|----|

| Figur                         | res                                    |                    |                                       |    |

| Fig. 1.                       | TWR-CM3120-EVM1                        | Fig. 8.            | Launching GUI from the Start menu     | 19 |

| Fig. 2.                       | TWR-CM3120-EVM on Tower System5        | Fig. 9.            | Select device IODD                    | 2′ |

| Fig. 3.                       | TWR-CM3120-EVM as a stand-alone board5 | Fig. 10.           | Device parameters                     | 23 |

| Fig. 4.                       | Block diagram7                         | Fig. 11.           | Device configuration                  |    |

| Fig. 5.                       | Board description 8                    | Fig. 12.           | Connected device state                | 23 |

| Fig. 6.                       | Setting up the hardware17              | Fig. 13.           | Parameters and process data           |    |

| Fig. 7                        | Installation complete 10               | -                  | •                                     |    |