# PROTECTION PRODUCTS - MicroClamp™

#### Description

The  $\mu Clamp^{TM}$  series of TVS arrays are designed to protect sensitive electronics from damage or latch-up due to ESD, lightning, and other voltage-induced transient events. Each device will protect up to four lines operating at **5 volts**.

The μClamp<sup>TM</sup>0524P is a solid-state device designed specifically for transient suppression. It is designed to replace multilayer varistors (MLVs) in portable applications such as cell phones, notebook computers, and PDAs. It features large cross-sectional area junctions for conducting high transient currents. It offers superior electrical characteristics such as lower clamping voltage and no device degradation when compared to MLVs.

The μClamp<sup>TM</sup>0524P may be used to meet the immunity requirements of IEC 61000-4-2, level 4 (±15kV air, ±8kV contact discharge). The "flow-thru" design of the device results in enhanced ESD performance due to reduced board trace inductance. The result is lower clamping voltage and a higher level of protection when compared to conventional TVS devices.

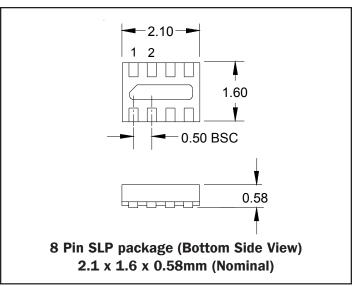

The  $\mu$ Clamp0524P is in an 8-pin, RoHS/WEEE compliant, SLP2116P8 package. It measures 2.1 x 1.6 x 0.58mm. The leads are spaced at a pitch of 0.5mm and are finished with lead-free NiPd. The small package makes it ideal for use in portable electronics such as cell phones, digital still cameras, and notebook computers.

#### Features

- ◆ Transient protection for data lines to IEC 61000-4-2 (ESD) ±15kV (air), ±8kV (contact) IEC 61000-4-4 (EFT) 40A (tp = 5/50ns)

- Small package for use in portable electronics

- Protects four I/O lines

- Working voltage: 5V

- Flow thru design for easy layout

- Low leakage current

- Low operating and clamping voltages

- Solid-state silicon-avalanche technology

#### Mechanical Characteristics

- SLP2116P8 package

- ◆ RoHS/WEEE Compliant

- ◆ Nominal Dimensions: 2.1 x 1.6 x 0.58 mm

- Lead Pitch: 0.5mm

- Lead Finish: NiPd

- Marking: Orientation Mark and Marking Code

- Packaging: Tape and Reel per EIA 481

### **Applications**

- Cellular Handsets & Accessories

- Personal Digital Assistants (PDAs)

- ◆ Notebooks & Handhelds

- Portable Instrumentation

- Digital Cameras

- Peripherals

- MP3 Players

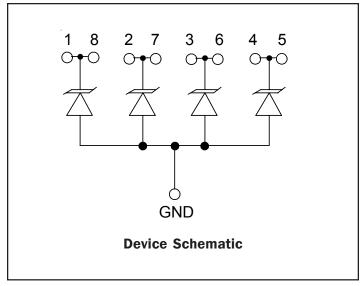

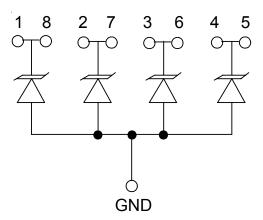

# Circuit Diagram

# Package

# Absolute Maximum Rating

| Rating                                                         | Symbol           | Value            | Units |

|----------------------------------------------------------------|------------------|------------------|-------|

| Peak Pulse Power (tp = 8/20μs)                                 | $P_{pk}$         | 240              | Watts |

| Maximum Peak Pulse Current (tp = 8/20μs)                       | l <sub>pp</sub>  | 16               | Amps  |

| ESD per IEC 61000-4-2 (Air)<br>ESD per IEC 61000-4-2 (Contact) | V <sub>PP</sub>  | +/- 20<br>+/- 15 | kV    |

| Operating Temperature                                          | T <sub>J</sub>   | -55 to +125      | °C    |

| Storage Temperature                                            | T <sub>STG</sub> | -55 to +150      | °C    |

# Electrical Characteristics (T=25°C)

| Parameter                 | Symbol           | Conditions                      | Minimum | Typical | Maximum | Units |

|---------------------------|------------------|---------------------------------|---------|---------|---------|-------|

| Reverse Stand-Off Voltage | V <sub>RWM</sub> |                                 |         |         | 5       | V     |

| Reverse Breakdown Voltage | V <sub>BR</sub>  | I <sub>t</sub> = 1mA            | 6       |         |         | V     |

| Reverse Leakage Current   | I <sub>R</sub>   | V <sub>RWM</sub> = 5V, T=25°C   |         |         | 5       | μΑ    |

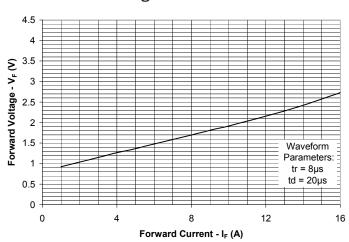

| Forward Voltage           | V <sub>F</sub>   | I <sub>F</sub> = 10mA           |         | 0.80    |         | V     |

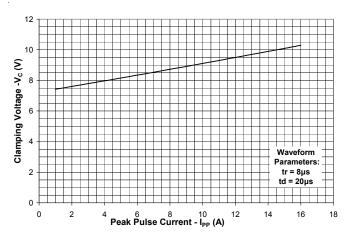

| Clamping Voltage          | V <sub>c</sub>   | $I_{pp} = 5A, t_p = 8/20 \mu s$ |         |         | 9.8     | V     |

| Clamping Voltage          | V <sub>c</sub>   | $I_{pp} = 16A, t_p = 8/20\mu s$ |         |         | 12.5    | V     |

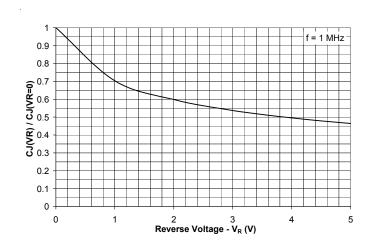

| Junction Capacitance      | C <sub>j</sub>   | V <sub>R</sub> = OV, f = 1MHz   |         |         | 160     | pF    |

# **Typical Characteristics**

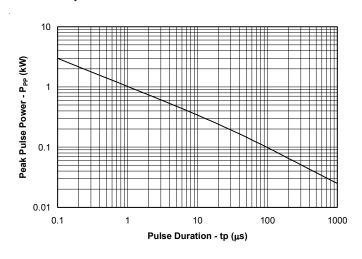

#### Non-Repetitive Peak Pulse Power vs. Pulse Time

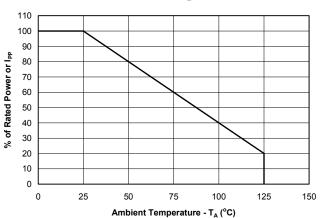

#### **Power Derating Curve**

#### Clamping Voltage vs. Peak Pulse Current

#### Forward Voltage vs. Forward Current

#### Junction Capacitance vs. Reverse Voltage

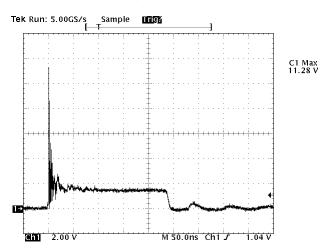

# ESD Clamping (8kV Contact per IEC 61000-4-2)

# **Applications Information**

#### **Device Connection Options**

The  $\mu$ Clamp0524P is designed to protect four lines. It will present a high impedance to the protected line up to 5 volts. The device is unidirectional and may be used on lines where the signal polarity is above ground.

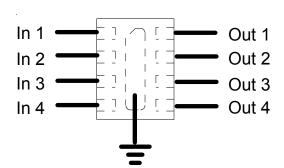

#### Flow Thru Layout

The  $\mu$ Clamp0524P is designed for ease of PCB layout by allowing the traces to enter one side of the device and exit the other side. Figure 2 shows the recommended way to design the PCB board traces in order to use the flow through layout. The solid line represents the PCB trace. Note that the PCB traces enter at the input pin and exit from the opposite pin. (pin 1 to pin 8, pin 2 to pin 7, pin 3 to pin 6, pin 4 to pin 5). For example, line 1 enters at pin 1 and exits at Pin 8. The bottom tab is connected to ground. This connection should be made directly to a ground plane on the board for best results. The path length is kept as short as possible to minimize parasitic inductance.

# Circuit Board Layout Recommendations for Suppression of ESD.

Good circuit board layout is critical for the suppression of ESD induced transients. The following guidelines are recommended:

- Place the TVS near the input terminals or connectors to restrict transient coupling.

- Minimize the path length between the TVS and the protected line.

- Minimize all conductive loops including power and ground loops.

- The ESD transient return path to ground should be kept as short as possible.

- Never run critical signals near board edges.

- Use ground planes whenever possible.

Figure 1 - Circuit Diagram

Figure 2 - PCB Trace Layout

# **Applications Information**

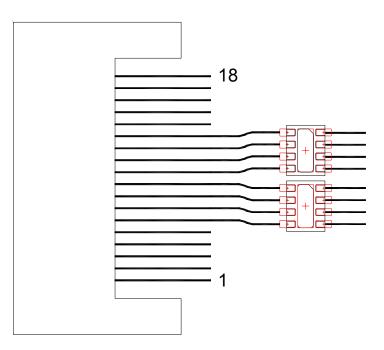

#### **Board Layout Comparison to MLVs**

Traditionally, single line devices such as MLVs have been a favorite solution for ESD protection in portable applications mainly due to their small size. Single-line solutions, are easy for designers to "sprinkle" around the board wherever ESD protection is needed. However, although each MLV takes up a small area on its own, when used as a multiple-line solution on board, PCB designers must consider that the total board space that each device takes up includes not only the package itself, but also the courtyard, or the "keep-out" area of the land pattern and the connecting traces. Using 0402 MLV in a 8-line connector protection as an example, although each 0402 MLV takes up about 0.5mm<sup>2</sup>, the total land pattern and courtyard area needed to reflow the MLVs accurately is about 31.2 mm<sup>2</sup>. Furthermore, because each MLV is spaced out from its neighboring MLVs, the signal traces used to connect from the connector pins to the each MLV are also spread out, and therefore, add to the total board area used.

The  $\mu$ Clamp0524P presents a more compact solution. Each  $\mu$ Clamp0524P integrates 4 TVS in a single, low-profile SLP package. Using the same example of an 8-line connector application, only two  $\mu$ Clamp0524Ps are required to protect all 8 lines. While each  $\mu$ clamp0524P uses about 3.36mm² in board area, the total area required for two devices to protect 8 lines, including the package area and the "keep out" area, is only 17.6mm². Comparing to the 31.2 mm² in area that 8 MLVs need, two  $\mu$ Clamp0524Ps provide a board savings of approximately 77%! Furthermore, since each  $\mu$ Clamp0524P offers flow-through design, the signal traces can be routed directly to the devices from the connector pins without taking extra board space.

Figure 3 - Layout Example

Layout using 2 each uClamp0524P requires less than 18mm<sup>2</sup> of board space.

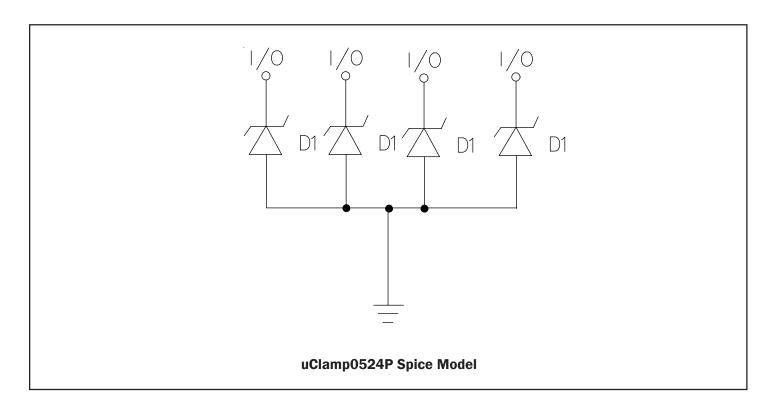

# Applications Information - Spice Model

| Table 1 - uClamp0524P Spice Parameters |       |          |  |

|----------------------------------------|-------|----------|--|

| Parameter                              | Unit  | D1 (TVS) |  |

| IS                                     | Amp   | 2.53e-12 |  |

| BV                                     | Volt  | 7.08     |  |

| ۸٦                                     | Volt  | 0.71     |  |

| RS                                     | Ohm   | 0.129    |  |

| IBV                                    | Amp   | 1.0E-3   |  |

| C10                                    | Farad | 140e-12  |  |

| TT                                     | sec   | 2.541E-9 |  |

| М                                      |       | 0.385    |  |

| N                                      |       | 1.1      |  |

| EG                                     | eV    | 1.11     |  |

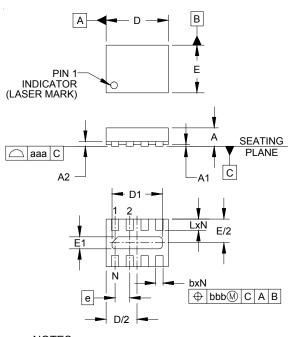

# Outline Drawing - SLP2116P8

|     | DIMENSIONS |      |      |             |      |      |

|-----|------------|------|------|-------------|------|------|

| DIM | INCHES     |      |      | MILLIMETERS |      |      |

| DIM | MIN        | NOM  | MAX  | MIN         | NOM  | MAX  |

| Α   | .020       | .023 | .026 | 0.50        | 0.58 | 0.65 |

| A1  | -          | .001 | .002 | 0.00        | .003 | 0.05 |

| A2  | (.006)     |      |      | (0.15)      |      |      |

| b   | .007       | .010 | .012 | 0.20        | 0.25 | 0.30 |

| D   | .079       | .083 | .087 | 2.00        | 2.10 | 2.20 |

| D1  | .061       | .067 | .071 | 1.55        | 1.70 | 1.80 |

| E   | .059       | .063 | .067 | 1.50        | 1.60 | 1.70 |

| E1  | .010       | .016 | .020 | 0.25        | 0.40 | 0.50 |

| е   | .020 BSC   |      |      | 0.50 BSC    |      |      |

| L   | .011       | .013 | .015 | 0.28        | 0.33 | 0.38 |

| N   | 6          |      | 6    |             |      |      |

| aaa | .003       |      | 0.08 |             |      |      |

| bbb | .004       |      |      |             | 0.10 |      |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

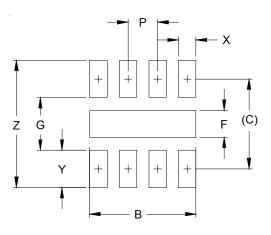

# Land Pattern - SLP2116P8

| DIMENSIONS |        |             |  |  |

|------------|--------|-------------|--|--|

| DIM        | INCHES | MILLIMETERS |  |  |

| В          | .071   | 1.80        |  |  |

| С          | .060   | 1.52        |  |  |

| F          | .018   | 0.45        |  |  |

| G          | .035   | 0.89        |  |  |

| Р          | .020   | 0.50        |  |  |

| Χ          | .012   | 0.30        |  |  |

| Υ          | .025   | 0.63        |  |  |

| Ζ          | .085   | 2.15        |  |  |

|            |        |             |  |  |

#### NOTES:

1. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.