# uClamp3312T Low Voltage µClamp® for Gigabit Ethernet

# PROTECTION PRODUCTS - MicroClamp®

# Description

The µClamp®3312T TVS diode is specifically designed to meet the performance requirements of Gigabit Ethernet interfaces. They are designed to protect sensitive PHY chips from damage or upset due to electrostatic discharge (ESD), lightning, electrical fast transients (EFT), and cable discharge events (CDE).

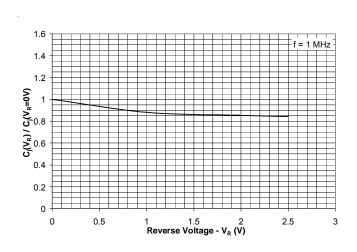

The  $\mu$ Clamp3312T is constructed using Semtech's low voltage EPD process technology. The EPD process provides low operating voltages with significant reductions in leakage current and capacitance over siliconavalanche diode processes. The device features low variation in capacitance over bias for stable operation on GbE lines. This means the  $\mu$ Clamp3312T will introduce zero traffic frame errors on GbE interfaces up to a PHY temperature of 120°C (100M Cat 5/5e Cable). The  $\mu$ Clamp3312T also features high surge capability and is designed to be placed between the magnetics and the PHY chip. In this configuration, the device can withstand intra-building lightning surges per Telcordia GR-1089.

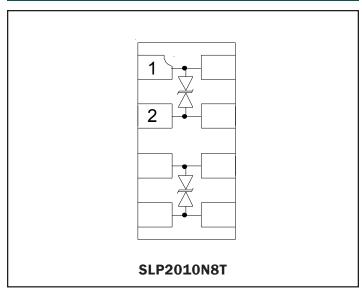

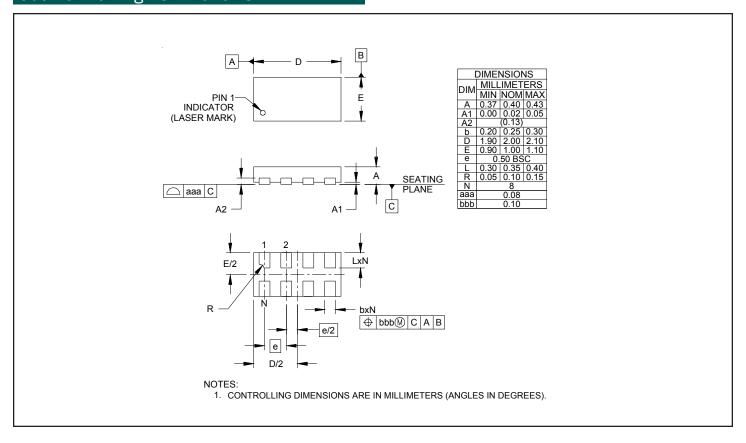

The  $\mu$ Clamp3312T is in a 8-pin SLP2010N8T package. It measures 2.0 x 1.0 x 0.4mm. The leads are spaced at a pitch of 0.5mm and are finished with lead-free NiPdAu. Each device will protect two line pairs operating at 3.3 volts. It gives the designer the flexibility to protect multiple lines in applications where space is at a premium. The small size and easy layout of the uClamp3312T make it ideal for use in RJ-45 connectors with integrated magnetics.

#### **Features**

- ◆ High ESD withstand Voltage: +/-30kV (Contact/Air) per IEC 61000-4-2

- ◆ Able to withstand over 1000 ESD strikes per IEC 61000-4-2 Level 4

- ◆ Flow-through design simplifies layout

- Protects two line pairs

- ◆ Low reverse current: 10nA typical (VR=3.3V)

- ◆ Low variation in capacitance vs. bias voltage: 1.3pF Typical (VR = 0 to 3.3V)

- Working voltage: 3.3V

- Solid-state silicon-avalanche technology

### Mechanical Characteristics

- ◆ SLP2010N8T package

- Pb-Free, Halogen Free, RoHS/WEEE Compliant

- ◆ Nominal Dimensions: 2.0 x 1.0 x 0.4 mm

- ◆ Lead Finish: NiPdAu

- Molding compound flammability rating: UL 94V-0

- Marking: Marking code

- Packaging: Tape and Reel

## **Applications**

- ◆ 10/100/1000 Ethernet

- ◆ Integrated magnetics/RJ-45 connectors

- ◆ LAN/WAN Equipment

- Security Cameras

- Industrial Controls

- Notebooks & Desktop Computers

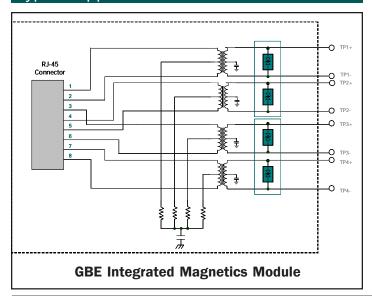

# Typical Application

# Schematic & PIN Configuration

# Absolute Maximum Rating

| Rating                                                         | Symbol           | Value            | Units |

|----------------------------------------------------------------|------------------|------------------|-------|

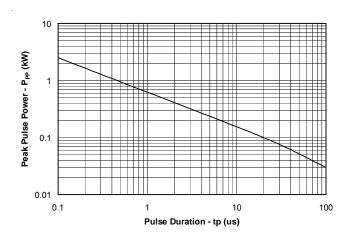

| Peak Pulse Power (tp = 8/20μs)                                 | P <sub>pk</sub>  | 100              | Watts |

| Maximum Peak Pulse Current (tp = 8/20μs)                       | I <sub>pp</sub>  | 10               | Amps  |

| ESD per IEC 61000-4-2 (Air)<br>ESD per IEC 61000-4-2 (Contact) | V <sub>ESD</sub> | +/- 30<br>+/- 30 | kV    |

| Operating Temperature                                          | T <sub>J</sub>   | -40 to +85       | °C    |

| Storage Temperature                                            | T <sub>STG</sub> | -55 to +150      | °C    |

# Electrical Characteristics (T=25°C)

| Parameter                                               | Symbol           | Conditions                                                                                                                                    | Minimum | Typical | Maximum | Units |

|---------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| Reverse Stand-Off Voltage                               | V <sub>RWM</sub> |                                                                                                                                               |         |         | 3.3     | V     |

| Punch-Through Voltage                                   | V <sub>PT</sub>  | Ι <sub>ΡΤ</sub> = 2μΑ                                                                                                                         | 3.5     | 3.8     | 4.3     | V     |

| Snap-Back Voltage                                       | V <sub>SB</sub>  | I <sub>SB</sub> = 50mA                                                                                                                        | 2.8     |         |         | V     |

| Reverse Leakage Current                                 | I <sub>R</sub>   | V <sub>RWM</sub> = 3.3V                                                                                                                       |         | 0.01    | 0.05    | μΑ    |

| Clamping Voltage                                        | V <sub>c</sub>   | I <sub>pp</sub> = 1A, tp = 8/20μs                                                                                                             |         |         | 5.6     | V     |

| Clamping Voltage                                        | V <sub>c</sub>   | $I_{pp} = 10A$ , tp = 8/20 $\mu$ s                                                                                                            |         |         | 11      | V     |

| Variation in capacitance with reverse bias <sup>1</sup> |                  | Pins 1, 8 to 2, 7 and<br>pins 3, 6 to 4, 5<br>VR = 0 to 2.5V<br>f = 1MHz<br>Pins 1, 8 to 2, 7 and<br>pins 3, 6 to 4, 5<br>VR = 2.5V, f = 1MHz |         | 1.3     |         | pF    |

| Junction Capacitance                                    | C <sub>j</sub>   | I/O pin to Gnd<br>V <sub>R</sub> = OV, f = 1MHz                                                                                               |         | 4.5     | 6       | pF    |

Notes:

<sup>1)</sup> This parameter guaranteed by design and characterization and is not production tested

## Non-Repetitive Peak Pulse Power vs. Pulse Time

#### Normalized Junction Capacitance vs. Reverse Voltage

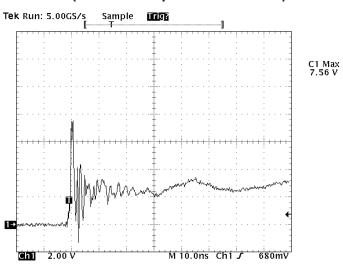

# ESD Clamping (Pin 1 to 2 and 2 to 1) (8kV Contact per IEC 61000-4-2)

Note: Data is taken with a 10x attenuator

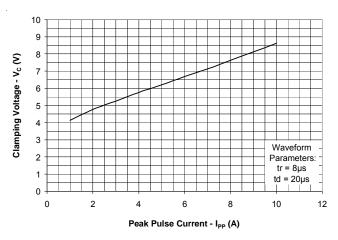

#### Clamping Voltage vs. Peak Pulse Current

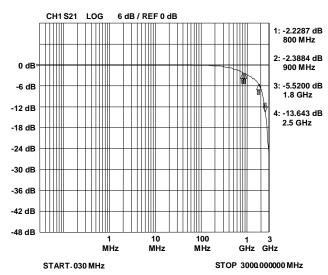

#### **Typical Insertion Loss (S21)**

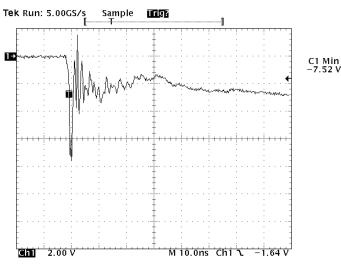

# ESD Clamping (Pin 1 to 2 and 2 to 1) (-8kV Contact per IEC 61000-4-2)

Note: Data is taken with a 10x attenuator

## **Applications Information**

#### **Gigabit Ethernet Protection Solutions**

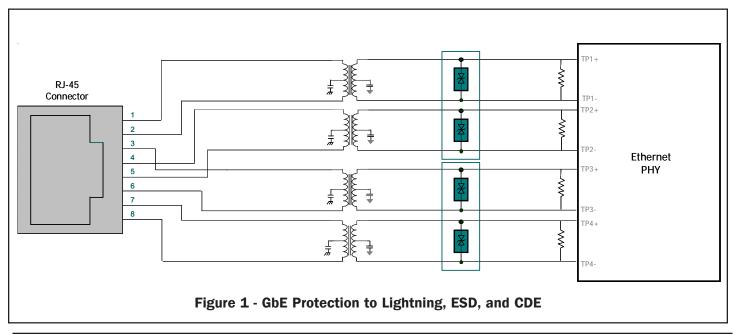

Ethernet systems with connections external to the building are subject to high-level transient threats. This type of equipment may even be required to meet the surge immunity requirements of Telcordia GR-1089. Reliable protection of the Ethernet transceiver requires a device that can absorb the expected transient energy, clamp the incoming surge to a safe level, and yet remain transparent to the system under normal operation. The uClamp3312T has been designed to meet these demanding requirements. Typical IEEE 802.3 template test results for a GbE circuit with uClamp3312T are shown in Figure 2.

#### **Transient Protection**

When designing Ethernet protection, the entire system must be considered. An Ethernet port includes interface magnetics in the form of transformers and common mode chokes. Transformers and chokes can be discrete components, but integrated solutions that include the RJ-45 connector, resistors, capacitors, and protection are also available. In either case, the transformer will provide a high level of common mode isolation to external voltages, but no protection for metallic (line-to-line) surges. During a metallic transient event, current will flow into one line, through the transformer and back to the source. As the current flows, it charges the windings of the transformer on the line side. Once the surge is removed, the windings on the line side will stop

charging and will transfer its stored energy to the IC side where the PHY IC is located. The magnitude and duration of the surge is attenuated by the inductance of the magnetics. The amount of attenuation will vary by vendor and configuration of the magnetics. It is this transferred energy that must be clamped by the protection circuitry.

A typical protection scheme which utilizes the uClamp3312T is shown in Figure 1. One device is placed across two line pairs and is located on the PHY side of the transformer as close to the magnetics as possible. This is done to minimize parasitic inductance and improve clamping performance. In this design, the isolation voltage of the transformer is relied upon to suppress common mode lightning surges. High voltage capacitors and resistors are commonly utilized from the center tap to ground to aid in transient protection. Metallic surges will be transferred in some form to the PHY side and clamped by the uClamp3312T. The uClamp3312T will turn on when the voltage across it exceeds the punch-through voltage of the device. Low voltage turn on is important since many PHY chips have integrated ESD protection structures. These structures are for protection of the device during manufacture and are not designed to handle large amounts of energy. Should they turn on before the external protection, they can be damaged resulting in failure of the PHY chip.

# **Applications Information**

#### **Point A**

#### **Point B**

#### **Point C**

**Point D**

#### **Point F**

#### **Point H**

Figure 2 - Typical IEEE 802.3 Template Test Results (With uClamp3312T)

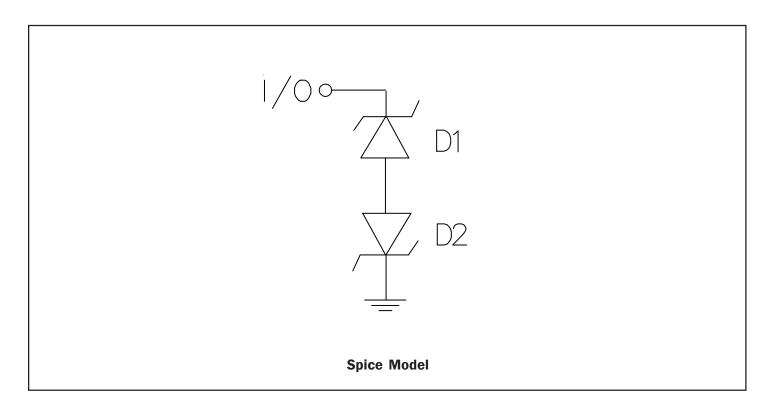

# Applications Information - Spice Model

| uClamp3312T Spice Parameters |       |                   |          |  |

|------------------------------|-------|-------------------|----------|--|

| Parameter                    | Unit  | D1 (TVS) D2 (TVS) |          |  |

| IS                           | Amp   | 1E-20             | 1E-20    |  |

| BV                           | Volt  | 2.8               | 2.8      |  |

| ٧J                           | Volt  | 0.7               | 0.7      |  |

| RS                           | Ohm   | 0.2               | 0.2      |  |

| IBV                          | Amp   | 1E-3              | 1E-3     |  |

| C1O                          | Farad | 10E-12            | 1E-12    |  |

| TT                           | sec   | 2.541E-9          | 2.541E-9 |  |

| М                            |       | 0.05              | 0.05     |  |

| N                            |       | 1.1               | 1.1      |  |

| EG                           | eV    | 1.11              | 1.11     |  |

# Outline Drawing - SLP2010N8T

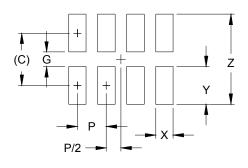

# Land Pattern - SLP2010N8T

| DIMENSIONS |             |

|------------|-------------|

| DIM        | MILLIMETERS |

| С          | (0.90)      |

| G          | 0.25        |

| Р          | 0.50        |

| Х          | 0.30        |

| Υ          | 0.65        |

| Z          | 1.55        |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.