# UJ3C065030B3

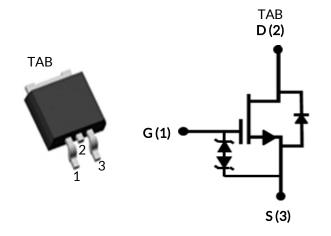

| Part Number  | Package               | Marking      |

|--------------|-----------------------|--------------|

| UJ3C065030B3 | D <sup>2</sup> PAK-3L | UJ3C065030B3 |

# $650V-27m\Omega$ SiC FET

Rev. C, May 2023

## Description

This SiC FET device is based on a unique 'cascode' circuit configuration, in which a normally-on SiC JFET is co-packaged with a Si MOSFET to produce a normally-off SiC FET device. The device's standard gate-drive characteristics allows for a true "drop-in replacement" to Si IGBTs, Si FETs, SiC MOSFETs or Si superjunction devices. Available in the  $D^2PAK\text{-}3L$  package, this device exhibits ultralow gate charge and exceptional reverse recovery characteristics, making it ideal for switching inductive loads and any application requiring standard gate drive.

#### **Features**

- $\bullet$  Typical on-resistance  $R_{DS(on),typ}$  of  $27m\Omega$

- Maximum operating temperature of 175°C

- Excellent reverse recovery

- Low gate charge

- Low intrinsic capacitance

- ESD protected: HBM class 2 and CDM class C3

#### **Typical applications**

- EV charging

- PV inverters

- Switch mode power supplies

- Power factor correction modules

- Motor drives

- Induction heating

## Maximum Ratings

| Parameter                                   | Symbol          | Test Conditions             | Value      | Units |

|---------------------------------------------|-----------------|-----------------------------|------------|-------|

| Drain-source voltage                        | $V_{DS}$        |                             | 650        | V     |

| Gate-source voltage                         | $V_{GS}$        | DC                          | -25 to +25 | V     |

| Continuous drain current <sup>1</sup>       |                 | T <sub>C</sub> = 25°C       | 65         | Α     |

|                                             | I <sub>D</sub>  | T <sub>C</sub> = 100°C      | 47         | Α     |

| Pulsed drain current <sup>2</sup>           | I <sub>DM</sub> | T <sub>C</sub> = 25°C       | 230        | Α     |

| Single pulsed avalanche energy <sup>3</sup> | E <sub>AS</sub> | L=15mH, I <sub>AS</sub> =4A | 120        | mJ    |

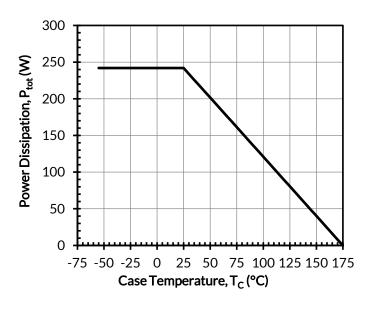

| Power dissipation                           | $P_{tot}$       | T <sub>C</sub> = 25°C       | 242        | W     |

| Maximum junction temperature                | $T_{J,max}$     |                             | 175        | °C    |

| Operating and storage temperature           | $T_J, T_{STG}$  |                             | -55 to 175 | °C    |

| Reflow soldering temperature                | $T_{solder}$    | reflow MSL 1                | 245        | °C    |

- 1. Limited by  $T_{J,\text{max}}$

- 2. Pulse width  $t_p$  limited by  $T_{J,max}$

- 3. Starting  $T_J = 25^{\circ}C$

## **Thermal Characteristics**

| Parameter                            | Symbol        | Test Conditions | Value |      |      | Units |

|--------------------------------------|---------------|-----------------|-------|------|------|-------|

|                                      |               |                 | Min   | Тур  | Max  | Units |

| Thermal resistance, junction-to-case | $R_{	heta$ JC |                 |       | 0.48 | 0.62 | °C/W  |

# **Typical Performance - Static**

| Parameter                      | Symbol              | Test Conditions                                                            |     | Units |      |       |

|--------------------------------|---------------------|----------------------------------------------------------------------------|-----|-------|------|-------|

| Parameter                      |                     |                                                                            | Min | Тур   | Max  | Units |

| Drain-source breakdown voltage | $BV_DS$             | $V_{GS}=0V, I_D=1mA$                                                       | 650 |       |      | V     |

| Total drain leakage current    |                     | V <sub>DS</sub> =650V,<br>V <sub>GS</sub> =0V, T <sub>J</sub> =25°C        |     | 6     | 150  | μΑ    |

|                                | I <sub>DSS</sub>    | V <sub>DS</sub> =650V,<br>V <sub>GS</sub> =0V, T <sub>J</sub> =175°C       |     | 30    |      |       |

| Total gate leakage current     | I <sub>GSS</sub>    | V <sub>DS</sub> =0V, T <sub>J</sub> =25°C,<br>V <sub>GS</sub> =-20V / +20V |     | 6     | ± 20 | μА    |

| Drain-source on-resistance     | R <sub>DS(on)</sub> | $V_{GS}$ =12V, $I_{D}$ =50A, $T_{J}$ =25°C                                 |     | 27    | 35   |       |

|                                |                     | V <sub>GS</sub> =12V, I <sub>D</sub> =50A,<br>T <sub>J</sub> =125°C        |     | 35    |      | mΩ    |

|                                |                     | $V_{GS}$ =12V, $I_{D}$ =50A, $T_{J}$ =175°C                                |     | 43    |      |       |

| Gate threshold voltage         | $V_{G(th)}$         | $V_{DS}$ =5V, $I_{D}$ =10mA                                                | 4   | 5     | 6    | V     |

| Gate resistance                | $R_{G}$             | f=1MHz, open drain                                                         |     | 4.5   |      | Ω     |

# Typical Performance - Reverse Diode

| Parameter                                     | Symbol               | Test Conditions                                                    |     | Linita |     |       |

|-----------------------------------------------|----------------------|--------------------------------------------------------------------|-----|--------|-----|-------|

|                                               |                      |                                                                    | Min | Тур    | Max | Units |

| Diode continuous forward current <sup>1</sup> | I <sub>S</sub>       | T <sub>C</sub> =25°C                                               |     |        | 65  | Α     |

| Diode pulse current <sup>2</sup>              | I <sub>S,pulse</sub> | T <sub>C</sub> =25°C                                               |     |        | 230 | Α     |

| Forward voltage                               | V <sub>FSD</sub>     | V <sub>GS</sub> =0V, I <sub>S</sub> =20A,<br>T <sub>J</sub> =25°C  |     | 1.3    | 1.4 | V     |

|                                               |                      | V <sub>GS</sub> =0V, I <sub>S</sub> =20A,<br>T <sub>J</sub> =175°C |     | 1.35   |     |       |

| Reverse recovery charge                       | Q <sub>rr</sub>      | $V_R$ =400V, $I_S$ =50A, $V_{GS}$ =0V, $R_{G_EXT}$ =20 $\Omega$    |     | 400    |     | nC    |

| Reverse recovery time                         | t <sub>rr</sub>      | di/dt=1550A/μs,<br>Τ <sub>J</sub> =150°C                           |     | 33     |     | ns    |

# Typical Performance - Dynamic

| Parameter                                    | Symbol             | Test Conditions                                                                                                     | Value |      |     | Units |

|----------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------|-------|------|-----|-------|

|                                              |                    |                                                                                                                     | Min   | Тур  | Max | Units |

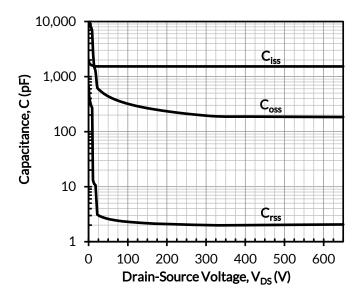

| Input capacitance                            | $C_{iss}$          | - V <sub>DS</sub> =100V, V <sub>GS</sub> =0V - f=100kHz -                                                           |       | 1500 |     |       |

| Output capacitance                           | $C_{oss}$          |                                                                                                                     |       | 320  |     | pF    |

| Reverse transfer capacitance                 | $C_{rss}$          |                                                                                                                     |       | 2.3  |     |       |

| Effective output capacitance, energy related | $C_{oss(er)}$      | $V_{DS}$ =0V to 400V,<br>$V_{GS}$ =0V                                                                               |       | 230  |     | pF    |

| Effective output capacitance, time related   | $C_{oss(tr)}$      | $V_{DS}$ =0V to 400V,<br>$V_{GS}$ =0V                                                                               |       | 520  |     | pF    |

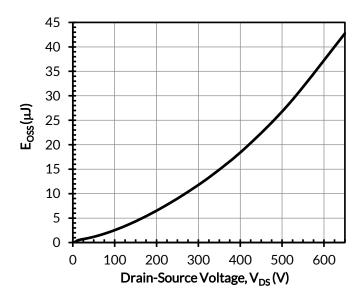

| C <sub>OSS</sub> stored energy               | $E_{oss}$          | $V_{DS}$ =400V, $V_{GS}$ =0V                                                                                        |       | 18.5 |     | μJ    |

| Total gate charge                            | $Q_{G}$            | - V <sub>DS</sub> =400V, I <sub>D</sub> =40A,<br>- V <sub>GS</sub> = -5V to15V                                      |       | 51   |     |       |

| Gate-drain charge                            | $Q_{GD}$           |                                                                                                                     |       | 11   |     | nC    |

| Gate-source charge                           | $Q_{GS}$           |                                                                                                                     |       | 19   |     |       |

| Turn-on delay time                           | $t_{d(on)}$        | V <sub>DS</sub> =400V, I <sub>D</sub> =40A, Gate                                                                    |       | 32   |     |       |

| Rise time                                    | $t_r$              |                                                                                                                     |       | 19   |     | nc    |

| Turn-off delay time                          | $t_{d(off)}$       | Driver =-5V to +15V,                                                                                                |       | 58   |     | ns    |

| Fall time                                    | $t_f$              | Turn-on $R_{G,EXT}$ =1 $\Omega$ , Turn-off $R_{G,EXT}$ =20 $\Omega$ Inductive Load, FWD: UJ3D065030TS, $T_J$ =150°C |       | 15   |     |       |

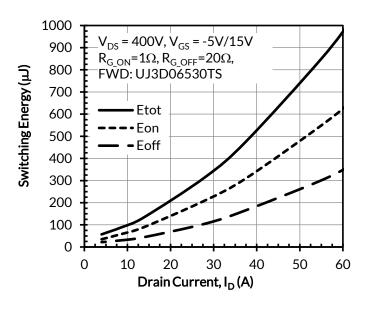

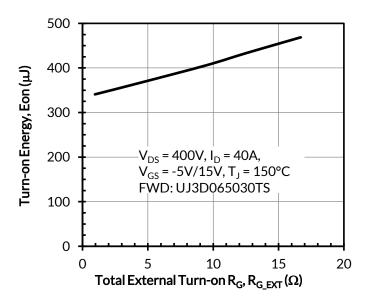

| Turn-on energy                               | E <sub>ON</sub>    |                                                                                                                     |       | 341  |     |       |

| Turn-off energy                              | E <sub>OFF</sub>   |                                                                                                                     |       | 180  |     | μЈ    |

| Total switching energy                       | E <sub>TOTAL</sub> |                                                                                                                     |       | 521  |     |       |

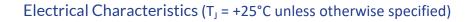

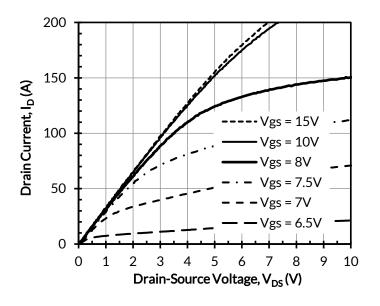

## **Typical Performance Diagrams**

200 150 Drain Current, I<sub>D</sub> (A) Vgs = 15V 100 Vgs = 10V Vgs = 8V 50 - Vgs = 7V Vgs = 6.5V 0 1 2 3 5 10 Drain-Source Voltage,  $V_{DS}(V)$

Figure 1. Typical output characteristics at  $T_J$  = - 55°C, tp < 250 $\mu$ s

Figure 2. Typical output characteristics at  $T_J = 25$ °C, tp < 250 $\mu$ s

Figure 3. Typical output characteristics at  $T_J$  = 175°C, tp < 250 $\mu$ s

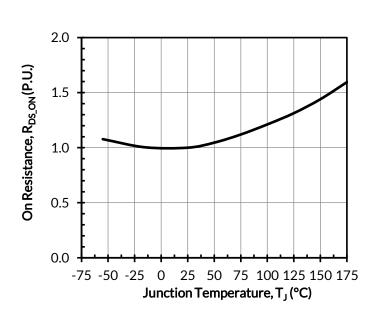

Figure 4. Normalized on-resistance vs. temperature at  $V_{GS}$  = 12V and  $I_{D}$  = 50A

Tj = -55°C Tj = 25°C Drain Current, I<sub>D</sub> (A) Tj = 175°C Gate-Source Voltage,  $V_{GS}(V)$

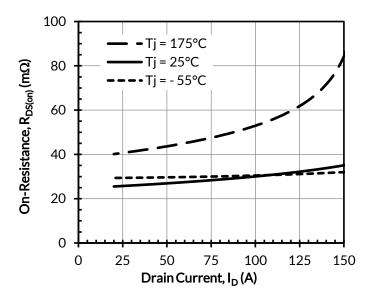

Figure 5. Typical drain-source on-resistances at  $V_{\text{GS}}$  = 12V

Figure 6. Typical transfer characteristics at  $V_{DS}$  = 5V

Gate Charge, Q<sub>G</sub> (nC)

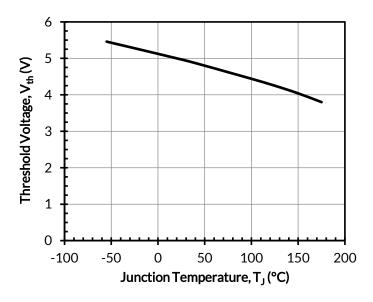

Figure 7. Threshold voltage vs. junction temperature at  $V_{DS}$  = 5V and  $I_{D}$  = 10mA

Figure 8. Typical gate charge at  $V_{DS}$  = 400V and  $I_{D}$  = 40A

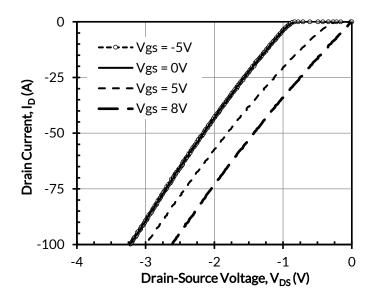

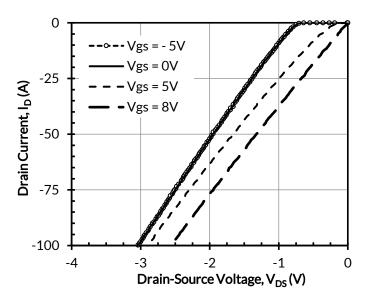

Figure 9. 3rd quadrant characteristics at  $T_J$  = -55°C

Figure 10. 3rd quadrant characteristics at  $T_J = 25$ °C

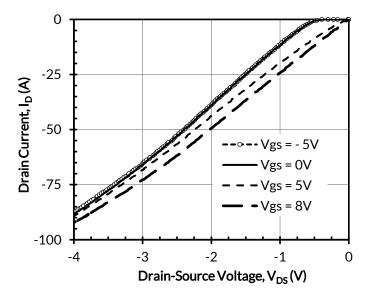

Figure 11. 3rd quadrant characteristics at  $T_J = 175$ °C

Figure 12. Typical stored energy in  $C_{OSS}$  at  $V_{GS} = 0V$

80 70 DC Drain Current, I<sub>D</sub> (A) 60 50 40 30 20 10 0 25 50 75 100 125 150 175 -75 -50 -25 0 Case Temperature, T<sub>C</sub> (°C)

Figure 13. Typical capacitances at f = 100kHz and  $V_{GS}$ = 0V

Figure 14. DC drain current derating

1 Thermal Impedance,  $Z_{\theta JC}$  (°C/W) 0.1 D = 0.5D = 0.3**-** D = 0.1 0.01 - D = 0.05 ···· D = 0.02 -D = 0.01Single Pulse 0.001 1.E-06 1.E-05 1.E-04 1.E-03 1.E-02 1.E-01 Pulse Time, t<sub>p</sub> (s)

Figure 15. Total power dissipation

Figure 16. Maximum transient thermal impedance

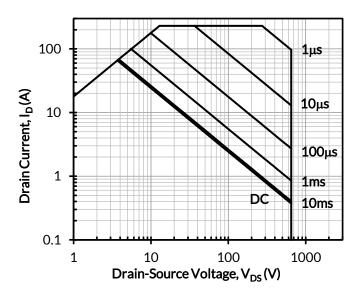

Figure 17. Safe operation area at  $T_C = 25$ °C, D = 0, Parameter t<sub>p</sub>

Figure 18. Clamped inductive switching energy vs. drain current at T<sub>1</sub> = 150°C

Figure 19. Clamped inductive switching turn-on energy vs. R<sub>G,EXT ON</sub>

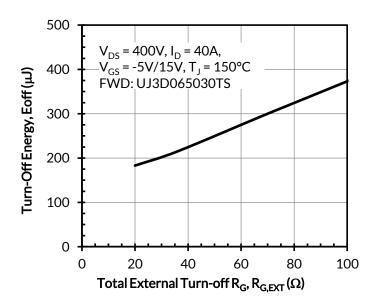

Figure 20. Clamped inductive switching turn-off energy vs. R<sub>G,EXT OFF</sub>

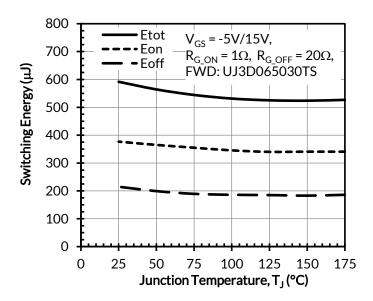

Figure 21. Clamped inductive switching energy vs. junction temperature at  $V_{DS}$  =400V and  $I_{D}$  = 40A

#### **Applications Information**

SiC FETs are enhancement-mode power switches formed by a high-voltage SiC depletion-mode JFET and a low-voltage silicon MOSFET connected in series. The silicon MOSFET serves as the control unit while the SiC JFET provides high voltage blocking in the off state. This combination of devices in a single package provides compatibility with standard gate drivers and offers superior performance in terms of low on-resistance ( $R_{DS(on)}$ ), output capacitance ( $C_{oss}$ ), gate charge ( $C_{oss}$ ), and reverse recovery charge ( $C_{oss}$ ) leading to low conduction and switching losses. The SiC FETs also provide excellent reverse conduction capability eliminating the need for an external anti-parallel diode.

Like other high performance power switches, proper PCB layout design to minimize circuit parasitics is strongly recommended due to the high dv/dt and di/dt rates. An external gate resistor is recommended when the FET is working in the diode mode in order to achieve the optimum reverse recovery performance. For more information on SiC FET operation, see www.unitedsic.com.

A snubber circuit with a small  $R_{(G)}$ , or gate resistor, provides better EMI suppression with higher efficiency compared to using a high  $R_{(G)}$  value. There is no extra gate delay time when using the snubber circuitry, and a small  $R_{(G)}$  will better control both the turn-off  $V_{(DS)}$  peak spike and ringing duration, while a high  $R_{(G)}$  will damp the peak spike but result in a longer delay time. In addition, the total switching loss when using a snubber circuit is less than using high  $R_{(G)}$ , while greatly reducing  $E_{(OFF)}$  from mid-to-full load range with only a small increase in  $E_{(ON)}$ . Efficiency will therefore improve with higher load current. For more information on how a snubber circuit will improve overall system performance, visit the UnitedSiC website at www.unitedsic.com