# iEthernet W5200 Datasheet

Version 1.3.0

# W5200

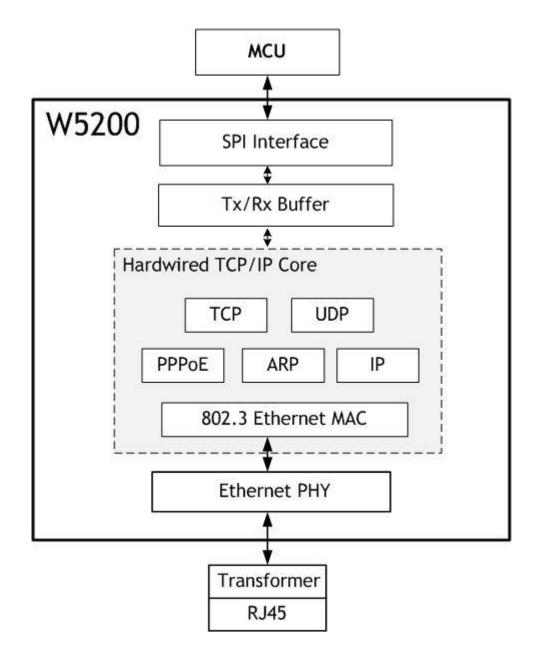

The W5200 chip is a Hardwired TCP/IP embedded Ethernet controller that enables easier internet connection for embedded systems using SPI (Serial Peripheral Interface). W5200 suits best for users who need Internet connectivity for application that uses a single chip to implement TCP/IP Stack, 10/100 Ethernet MAC and PHY.

The W5200 is composed of a fully hardwired market-proven TCP/IP stack and an integrated Ethernet MAC & PHY. Hardwired TCP/IP stack supports TCP, UDP, IPv4, ICMP, ARP, IGMP, and PPPoE, which has been proven in various applications for many years. W5200 uses a 32Kbytes internal buffer as its data communication memory. By using W5200, users can implement the Ethernet application they need by using a simple socket program instead of handling a complex Ethernet Controller.

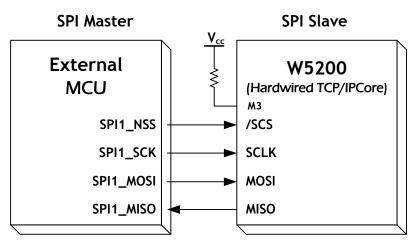

SPI (Serial Peripheral Interface) is provided for easy integration with the external MCU. Using the only 4 pins of SPI to connect with MCU, it is possible to design for small form factor system with the MCU's I/O pin limit.

In order to reduce power consumption of the system, W5200 provides WOL (Wake on LAN) and power down mode. To wake up during WOL, W5200 should be received magic packet, which is the Raw Ethernet packet.

# Features

- Support Hardwired TCP/IP Protocols : TCP, UDP, ICMP, IPv4 ARP, IGMP, PPPoE, Ethernet

- Supports 8 independent sockets simultaneously

- Very small 48 Pin QFN Package

- Support Power down mode

- Support Wake on LAN

- Support High Speed Serial Peripheral Interface(SPI MODE 0, 3)

- Internal 32Kbytes Memory for Tx/Rx Buffers

- 10BaseT/100BaseTX Ethernet PHY embedded

- Support Auto Negotiation (Full and half duplex, 10 and 100-based )

- Support Auto MDI/MDIX

- Support ADSL connection (with support PPPoE Protocol with PAP/CHAP Authentication mode)

- Not support IP Fragmentation

- 3.3V operation with 5V I/O signal tolerance

- Lead-Free Package

- Multi-function LED outputs (Full/Half duplex, Link, Speed)

# **Target Applications**

The W5200 is well suited for many embedded applications, including:

- Home Network Devices: Set-Top Boxes, PVRs, Digital Media Adapters

- Serial-to-Ethernet: Access Controls, LED displays, Wireless AP relays, etc.

- Parallel-to-Ethernet: POS / Mini Printers, Copiers

- USB-to-Ethernet: Storage Devices, Network Printers

- GPIO-to-Ethernet: Home Network Sensors

- Security Systems: DVRs, Network Cameras, Kiosks

- Factory and Building Automations

- Medical Monitoring Equipments

- Embedded Servers

# Block Diagram

# Table of Contents

| 1 | Pin As | ssignmen  | nt                                         | 8    |

|---|--------|-----------|--------------------------------------------|------|

|   | 1.1    | MCU       | J Interface Signals                        | 8    |

|   | 1.2    | PHY       | Śignals                                    | . 10 |

|   | 1.3    | Misc      | cellaneous Signals                         | . 10 |

|   | 1.4    | Powe      | er Supply Signals                          | . 11 |

|   | 1.5    | Cloc      | ck Signals                                 | . 12 |

|   | 1.6    | LED       | Signals                                    | . 13 |

| 2 | Memo   | ory Map . |                                            | . 14 |

| 3 | W520   | 0 Registe | ers                                        | . 15 |

|   | 3.1    | com       | nmon registers                             | . 15 |

|   | 3.2    | Sock      | ket registers                              | . 16 |

| 4 | Regist | ter Desci | riptions                                   | . 17 |

|   | 4.1    | Com       | nmon Registers                             | . 17 |

|   | 4.2    | Sock      | ket Registers                              | . 24 |

| 5 | Funct  | ional De  | escriptions                                | . 43 |

|   | 5.1    | Initia    | alization                                  | . 43 |

|   | 5.2    | Data      | a Communications                           | . 46 |

|   | 5      | .2.1      | тср                                        | . 46 |

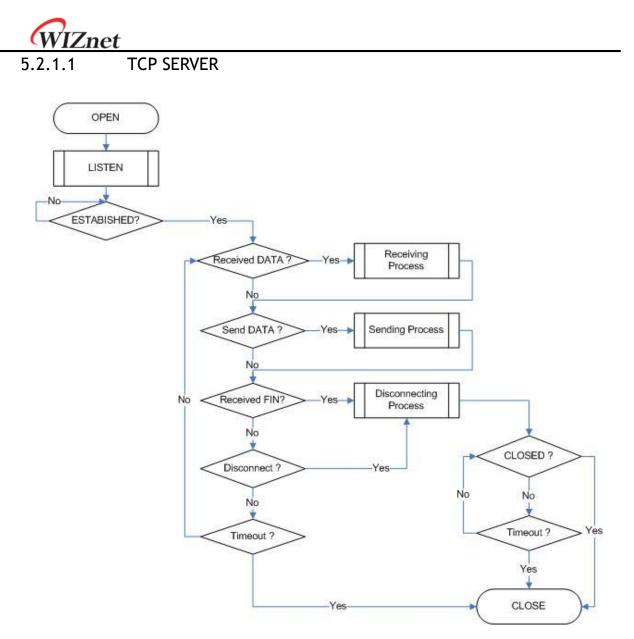

|   |        | 5.2.1     | 1.1 TCP SERVER                             | . 47 |

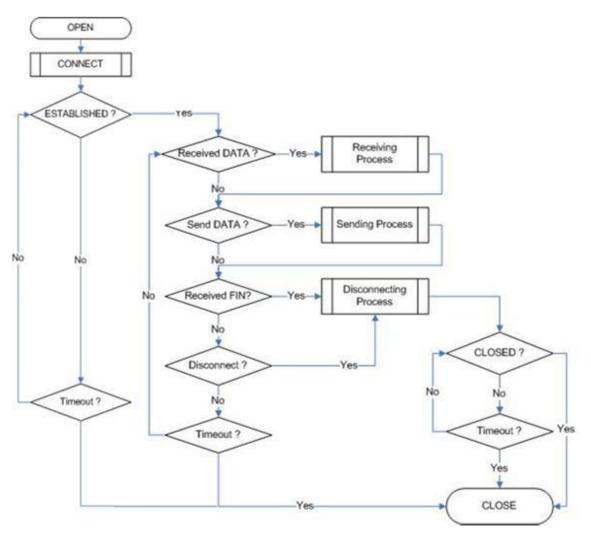

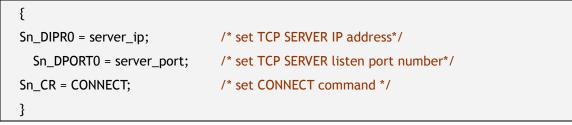

|   |        | 5.2.1     | 1.2 TCP CLIENT                             | . 54 |

|   | 5      | .2.2      | UDP                                        | . 55 |

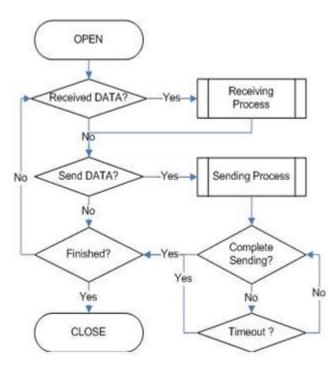

|   |        | 5.2.2     | 2.1 Unicast and Broadcast                  | . 55 |

|   |        | 5.2.2     | 2.2 Multicast                              | . 62 |

|   | 5      | .2.3      | IPRAW                                      | . 65 |

|   | 5      | .2.4      | MACRAW                                     | . 67 |

| 6 | Exter  | nal Inter | rface                                      | . 73 |

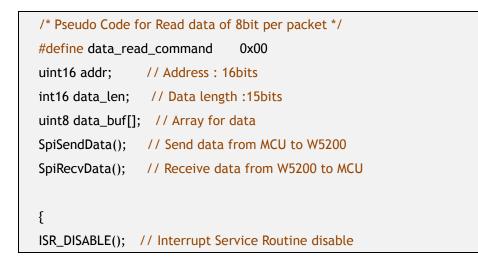

|   | 6.1    | SPI (     | (Serial Peripheral Interface) mode         | . 73 |

|   | 6.2    | Devi      | ice Operations                             | . 73 |

|   | 6.3    | Proc      | cess of using general SPI Master device    | . 74 |

| 7 | Electi | rical Spe | ecifications                               | . 79 |

|   | 7.1    | Abso      | olute Maximum Ratings                      | . 79 |

|   | 7.2    | DC C      | Characteristics                            | . 79 |

|   | 7.3    | POW       | VER DISSIPATION(Vcc 3.3V Temperature 25°C) | . 79 |

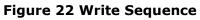

|   | 7.4    | AC C      | Characteristics                            | . 80 |

|   | 7      | .4.1      | Reset Timing                               | . 80 |

|   | 7      | .4.2      | Crystal Characteristics                    | . 80 |

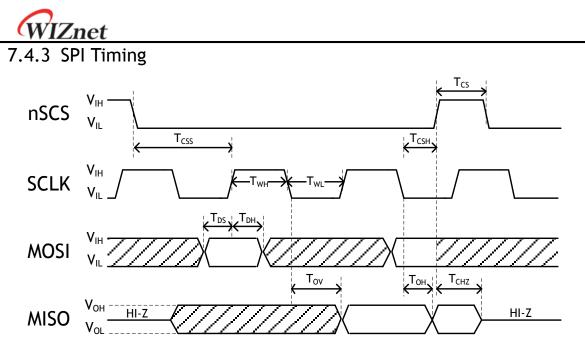

|   | 7      | .4.3      | SPI Timing                                 | . 81 |

|      | 7.4.4          | Transformer Characteristics   | 82 |

|------|----------------|-------------------------------|----|

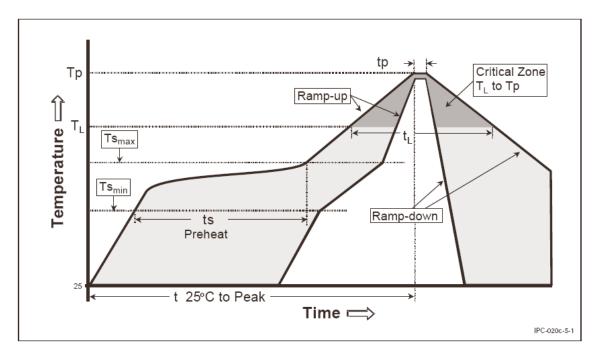

| 8    | IR Reflow Terr | nperature Profile (Lead-Free) | 83 |

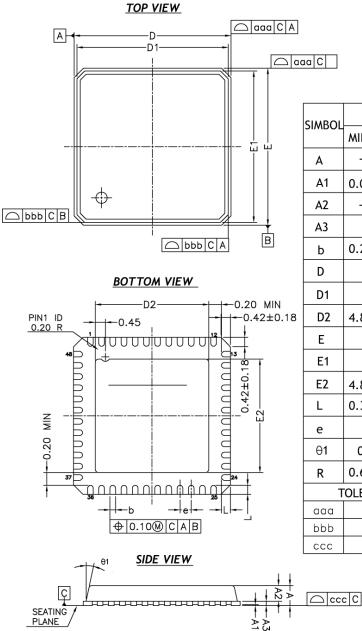

| 9    | Package Desc   | riptions                      | 84 |

| Docι | lment History  | Information                   | 86 |

# Table of Figure

| Figure 1 Pin Description W52008                         |

|---------------------------------------------------------|

| Figure 2 XTAL_VDD Reference Schematic11                 |

| Figure 3 Power Design 12                                |

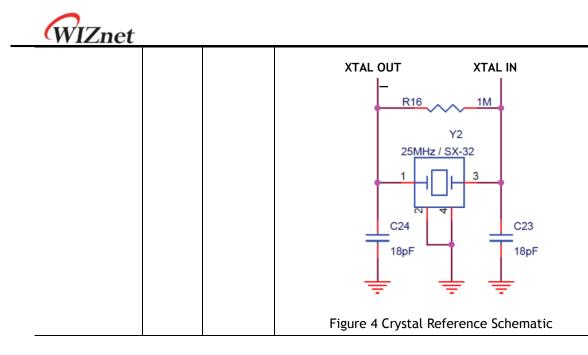

| Figure 4 Crystal Reference Schematic 13                 |

| Figure 5 INTLEVEL Timing 21                             |

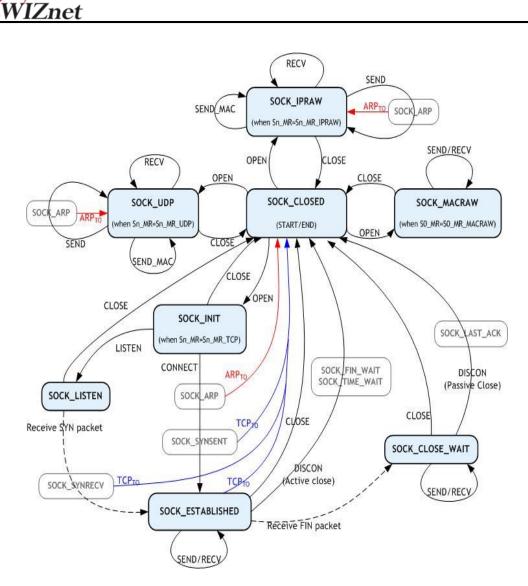

| Figure 6 Socket Status Transition 33                    |

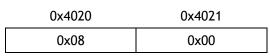

| Figure 7 Physical Address Calculation 39                |

| Figure 8 Allocation Internal TX/RX memory of Socket n   |

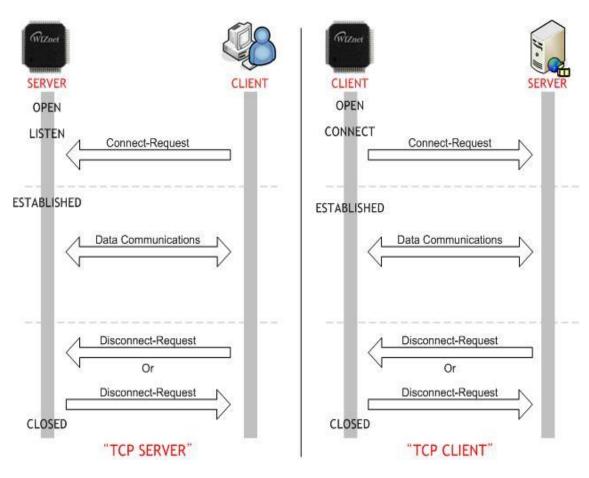

| Figure 9 TCP SERVER and TCP CLIENT 46                   |

| Figure 10 TCP SERVER Operation Flow 47                  |

| Figure 11 TCP CLIENT Operation Flow54                   |

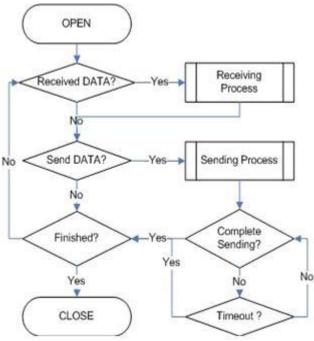

| Figure 12 UDP Operation Flow 55                         |

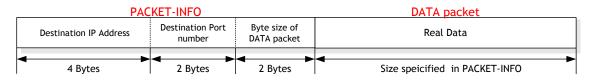

| Figure 13 The Received UDP data Format 57               |

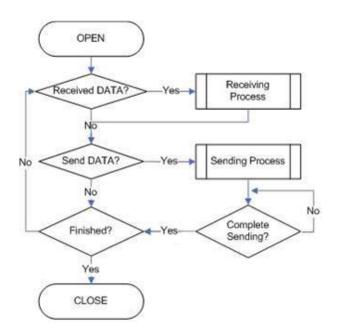

| Figure 14 IPRAW Operation Flow                          |

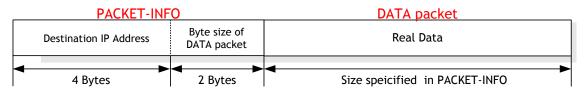

| Figure 15 The receive IPRAW data Format                 |

| Figure 16 MACRAW Operation Flow                         |

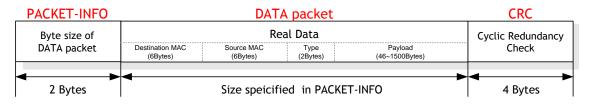

| Figure 17 The received MACRAW data Format               |

| Figure 18 SPI Interface73                               |

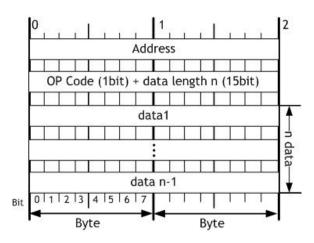

| Figure 19 W5200 SPI Frame Format74                      |

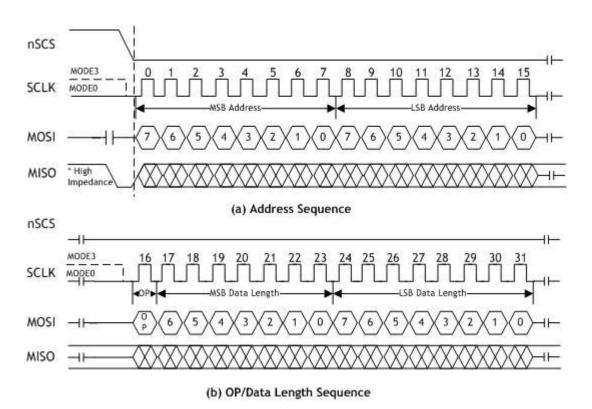

| Figure 20 Address and OP/DATA Length Sequence Diagram74 |

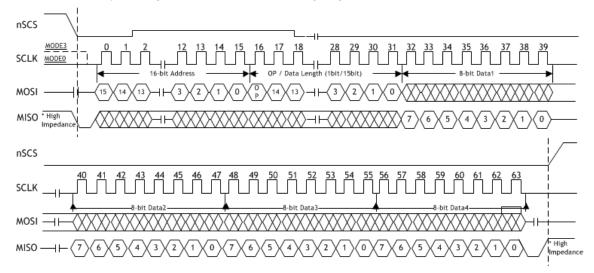

| Figure 21 READ Sequence75                               |

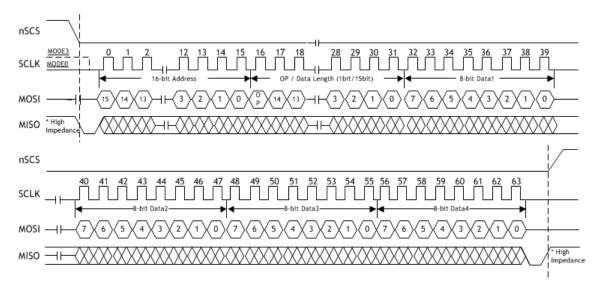

| Figure 22 Write Sequence                                |

| Figure 23 Reset Timing 80                               |

| Figure 24 SPI Timing 81                                 |

| Figure 25 Transformer Type                              |

| Figure 26 IR Reflow Temperature                         |

| Figure 27 Package Dimensions 84                         |

1 Pin Assignment

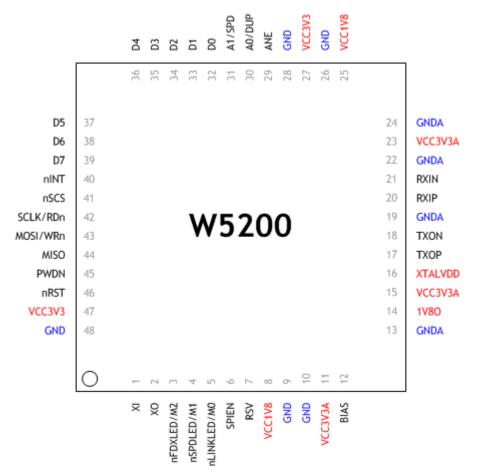

#### Figure 1 Pin Description W5200

| 1.1 MCU Interface Signals |      |         |                                                             |  |  |

|---------------------------|------|---------|-------------------------------------------------------------|--|--|

| Symbol                    | Туре | Pin No  | Description                                                 |  |  |

| A0/DUP                    | I    | 30      | (*)ADDRESS[0]                                               |  |  |

|                           |      |         | This pin is used to select a register or memory when        |  |  |

| _                         |      |         | using indirect interface.                                   |  |  |

| A1/SPD                    | I    | 31      | (*)ADDRESS[1]                                               |  |  |

|                           |      |         | This pin is used to select a register or memory when        |  |  |

|                           |      |         | using indirect interface.                                   |  |  |

| D7-0                      | I/0  | 32, 33, | 2, 33, <b>(*)DATA</b>                                       |  |  |

|                           |      | 34, 35, | These pins are used to read and write register or           |  |  |

|                           |      | 36, 37, | memory data.                                                |  |  |

|                           |      | 38, 39  |                                                             |  |  |

| RSTn                      | I    | 46      | RESET ( Active LOW )                                        |  |  |

|                           |      |         | This pin is active Low input to initialize or re-initialize |  |  |

|                           |      |         | W5200.                                                      |  |  |

|                           |      |         | RESET should be held at least 2us after low assert, and     |  |  |

#### 1.1 MCU Interface Signals

| WIZno    | et |    |                                                            |

|----------|----|----|------------------------------------------------------------|

|          |    |    | wait for at least 150ms after high de-assert in order for  |

|          |    |    | PLL logic to be stable. Refer to RESET timing of "7        |

|          |    |    | Electrical Specification"                                  |

| CSn      | I  | 41 | SPI SLAVE SELECT ( Active LOW )                            |

|          |    |    | This pin is used to SPI Slave Select signal Pin when using |

|          |    |    | SPI interface.                                             |

|          |    |    | (*)CHIP SELECT ( Active LOW )                              |

|          |    |    | Chip Select is for MCU to access to internal registers or  |

|          |    |    | memory when using indirect interface.                      |

| INTn     | 0  | 40 | INTERRUPT (Active LOW )                                    |

|          |    |    | This pin indicates that W5200 requires MCU attention       |

|          |    |    | after socket connecting, disconnecting, data receiving     |

|          |    |    | timeout, and WOL (Wake on LAN). The interrupt is           |

|          |    |    | cleared by writing IR(Interrupt Register) or Sn_IR (Socket |

|          |    |    | n Interrupt Register). All interrupts are maskable. This   |

|          |    |    | pin is active low.                                         |

| SCLK/RDn | I  | 42 | SPI CLOCK                                                  |

|          |    |    | This pin is used to SPI Clock signal Pin when using SPI    |

|          |    |    | interface.                                                 |

|          |    |    | (*)READ ENABLE ( Active LOW )                              |

|          |    |    | Strobe from MCU to read an internal register/memory        |

|          |    |    | selected by A[1:0] when using indirect interface.          |

| MOSI/WRn | I  | 43 | SPI MASTER OUT SLAVE IN                                    |

|          |    |    | This pin is used to SPI MOSI signal pin when using SPI     |

|          |    |    | interface.                                                 |

|          |    |    | (*)WRITE ENABLE ( Active LOW )                             |

|          |    |    | Strobe from MCU to write an internal register/memory       |

|          |    |    | selected by A[1:0] when using indirect interface. Data is  |

|          |    |    | latched into the W5200 on the rising edge of this input.   |

| MISO     | 0  | 44 | SPI MASTER IN SLAVE OUT                                    |

|          |    |    | This pin is used to SPI MISO signal pin.                   |

| PWDN     | I  | 45 | POWER DOWN ( Active HIGH )                                 |

|          |    |    | This pin is used to power down pin.                        |

|          |    |    | Low : Normal Mode Enable                                   |

|          |    |    | High : Power Down Mode Enable                              |

| SPIEN    | I  | 6  | (*)SPI ENABLE ( Active HIGH )                              |

|          |    |    | This pin selects Enable/disable of the SPI Mode.           |

|          |    |    | Low = SPI Mode Disable                                     |

|          |    |    | High = SPI Mode Enable                                     |

© Copyright 2013 WIZnet Co.,Ltd. All rights reserved.

If you don't use SPI mode, in other words, if you want to use indirect mode, then you tied this signal to '0'. This function activate only when reset period.

(\*) These pins are related with indirect interface mode. If you need details, Please refer to the W5200\_AN\_Indirect.pdf file.

### 1.2 PHY Signals

| Symbol | Туре | Pin No | Description                                               |

|--------|------|--------|-----------------------------------------------------------|

| RXIP   | I    | 20     | RXIP/RXIN Signal Pair                                     |

|        |      |        | The differential data from the media is received on       |

| RXIN   | I    | 21     | the RXIP/RXIN signal pair.                                |

|        |      |        |                                                           |

| ТХОР   | 0    | 17     | TXOP/TXON Signal Pair                                     |

| TXON   | 0    | 18     | The differential data is transmitted to the media on      |

|        | Ŭ    | 10     | the TXOP/TXIN signal pair.                                |

| BIAS   | 0    | 12     | BIAS Register                                             |

|        |      |        | Connect a resistor of 28.7 $k\Omega\pm1\%$ to the ground. |

|        |      |        | Refer to the "Reference schematic".                       |

| ANE    | I    | 29     | Auto Negotiation Mode Enable                              |

|        |      |        | This pin selects Enable/Disable of Auto Negotiation       |

|        |      |        | Mode.                                                     |

|        |      |        | Low :Auto Negotiation Mode Disable                        |

|        |      |        | High : Auto Negotiation Mode Enable                       |

| A0/DUP | I    | 30     | Full Duplex Mode Enable                                   |

|        |      |        | This pin selects Enable/Disable of Full Duplex Mode.      |

|        |      |        | Low = Half Duplex Mode Enable                             |

|        |      |        | High = Full Duplex Mode Enable                            |

|        |      |        | This function activates only during reset period.         |

| A1/SPD | I    | 31     | Speed Mode                                                |

|        |      |        | This pin selects 100M/10M Speed Mode.                     |

|        |      |        | Low = 10M Speed Mode                                      |

|        |      |        | High = 100M Speed Mode                                    |

|        |      |        | This function activates only during reset period.         |

## 1.3 Miscellaneous Signals

|      | ¥         |                                          |

|------|-----------|------------------------------------------|

| Туре | Pin No    | Description                              |

| Ι    | 3,        | W5200 MODE SELECT                        |

|      | 4,        | Normal mode : 111                        |

|      | 5         | Other test modes are internal test mode. |

|      | Type<br>I | I 3,<br>4,                               |

© Copyright 2013 WIZnet Co.,Ltd. All rights reserved.

|     |   |   | This function activates only during reset |

|-----|---|---|-------------------------------------------|

|     |   |   | period                                    |

| RSV | Ι | 7 | Reserved Pin                              |

|     |   |   |                                           |

• Notes: Pull-Up/Down resistor = Typical value are 10KΩ.

| Symbol  | Туре   | Pin No         | Description                                                                                                                                                                                                                                                                                                                                     |

|---------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC3V3A | Power  | 11, 15, 23     | 3.3V power supply for Analog part                                                                                                                                                                                                                                                                                                               |

| VCC3V3  | Power  | 27, 47         | 3.3V power supply for Digital part                                                                                                                                                                                                                                                                                                              |

| VCC1V8  | Power  | 8, 25          | 1.8V power supply for Digital part                                                                                                                                                                                                                                                                                                              |

| GNDA    | Ground | 13, 19, 22, 24 | Analog ground                                                                                                                                                                                                                                                                                                                                   |

| GND     | Ground | 9, 10, 26,     | Digital ground                                                                                                                                                                                                                                                                                                                                  |

|         |        | 28, 48         |                                                                                                                                                                                                                                                                                                                                                 |

| 1V80    | 0      | 14             | <ul> <li>1.8V regulator output voltage</li> <li>1.8V/200mA power created by internal power regulator, is used for core operation power (VCC1V8).</li> <li>Be sure to connect tantalum capacitor between 1V80 and GND for output frequency compensation, and selectively connect 0.1uF capacitor for high frequency noise decoupling.</li> </ul> |

|         |        |                | Notice: 1V80 is the power for W5200 core operation. It should not be connected to the                                                                                                                                                                                                                                                           |

|         |        |                | power of other devices.                                                                                                                                                                                                                                                                                                                         |

| XTALVDD | 1      | 16             | C20<br>0.1uF<br>UT-Ngr-11                                                                                                                                                                                                                                                                                                                       |

|         |        |                | Figure 2 XTAL_VDD Reference Schematic<br>Connect a capacitor of 10.1uF to the ground.                                                                                                                                                                                                                                                           |

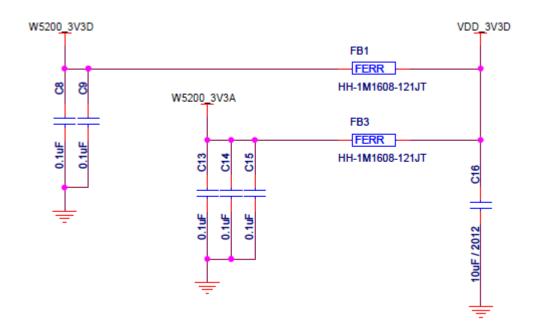

# 1.4 Power Supply Signals

W5200\_1V8\_OUT

C12

10uF/16V-TT

iEthernet W5200

FB2 FERR HH-1M1608-121JT

Figure 3 Power Design

Recommend for power design.

WIZnet

W5200\_1V8D

C10 C11

0.1uF

S

0uF/16V-TT

- 1. Locate decoupling capacitor as close as possible to W5200.

- 2. Use ground plane as wide as possible.

- 3. If ground plane width is adequate, having a separate analog ground plane and digital ground plane is good practice.

- 4. If ground plane is not wide, design analog and digital ground planes as a single ground plane, rather than separate them.

| Symbol | Туре | Pin No | Description                                     |  |  |

|--------|------|--------|-------------------------------------------------|--|--|

| XI     | I    | 1      | 25MHz crystal input/output. A 25MHz crystal and |  |  |

|        |      |        | Oscillator is used to connect these pins.       |  |  |

| XO     | 0    | 2      |                                                 |  |  |

#### 1.5 Clock Signals

## 1.6 LED Signals

| Symbol      | Туре | Pin No | Description                   |  |  |

|-------------|------|--------|-------------------------------|--|--|

| FDXLEDn/M2  | 0    | 3      | Full Duplex/Collision LED     |  |  |

|             |      |        | Low: Full-duplex              |  |  |

|             |      |        | High: Half-duplex.            |  |  |

| SPDLEDn/M1  | 0    | 4      | Link speed LED                |  |  |

|             |      |        | Low: 100Mbps                  |  |  |

|             |      |        | High: 10Mbps                  |  |  |

| LINKLEDn/M0 | 0    | 5      | Link LED                      |  |  |

|             |      |        | Low: Link (10/100M)           |  |  |

|             |      |        | High: Un-Link                 |  |  |

|             |      |        | blink: TX or RX state on Link |  |  |

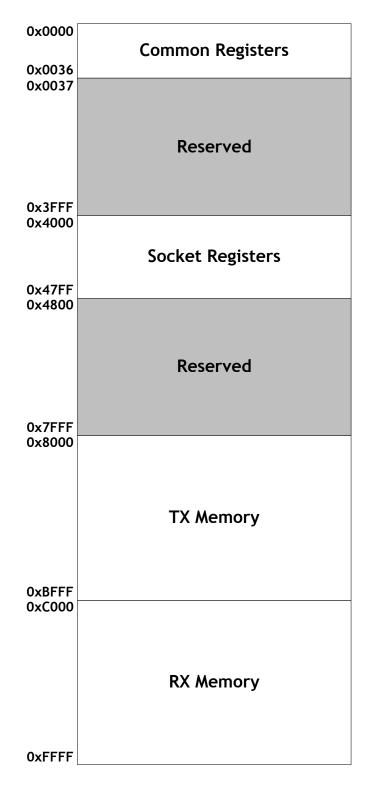

# 2 Memory Map

W5200 is composed of Common Register, Socket Register, TX Memory, and RX Memory as shown below.

#### W5200 Memory Map

# 3 W5200 Registers

# 3.1 common registers

| Address | Register                |  |  |  |

|---------|-------------------------|--|--|--|

| 0x0000  | Mode (MR)               |  |  |  |

|         | Gateway Address         |  |  |  |

| 0x0001  | (GAR0)                  |  |  |  |

| 0x0002  | (GAR1)                  |  |  |  |

| 0x0003  | (GAR2)                  |  |  |  |

| 0x0004  | (GAR3)                  |  |  |  |

|         | Subnet mask Address     |  |  |  |

| 0x0005  | (SUBRO)                 |  |  |  |

| 0x0006  | (SUBR1)                 |  |  |  |

| 0x0007  | (SUBR2)                 |  |  |  |

| 0x0008  | (SUBR3)                 |  |  |  |

|         | Source Hardware Address |  |  |  |

| 0x0009  | (SHARO)                 |  |  |  |

| 0x000A  | (SHAR1)                 |  |  |  |

| 0x000B  | (SHAR2)                 |  |  |  |

| 0x000C  | (SHAR3)                 |  |  |  |

| 0x000D  | (SHAR4)                 |  |  |  |

| 0x000E  | (SHAR5)                 |  |  |  |

|         | Source IP Address       |  |  |  |

| 0x000F  | (SIPRO)                 |  |  |  |

| 0x0010  | (SIPR1)                 |  |  |  |

| 0x0011  | (SIPR2)                 |  |  |  |

| 0x0012  | (SIPR3)                 |  |  |  |

| 0x0013  | Reserved                |  |  |  |

| 0x0014  |                         |  |  |  |

| 0x0015  | Interrupt (IR)          |  |  |  |

| 0x0016  | Interrupt Mask (IMR)    |  |  |  |

|         | Retry Time              |  |  |  |

| 0x0017  | (RTRO)                  |  |  |  |

| 0x0018  | (RTR1)                  |  |  |  |

| 0x0019  | Retry Count (RCR)       |  |  |  |

| 0x001A  | Perenued                |  |  |  |

| 0x001B  | Reserved                |  |  |  |

| Address | Register               |

|---------|------------------------|

|         | Authentication Type    |

|         | in PPPoE               |

| 0x001C  | (PATRO)                |

| 0x001D  | (PATR1)                |

|         | Authentication         |

|         | Algorithm in PPPoE     |

| 0x001E  | (PPPALGO)              |

| 0x001F  | Chip version(VERSIONR) |

| 0x0020  |                        |

| ~       | Reserved               |

| 0x0027  |                        |

|         | PPP LCP                |

|         | RequestTimer           |

| 0x0028  | (PTIMER)               |

|         | PPP LCP Magic          |

| 0x0029  | number (PMAGIC)        |

| 0x002A  |                        |

| ~       | Reserved               |

| 0x002F  |                        |

|         | Interrupt Low Level    |

| 0x0030  | Timer                  |

| 0x0031  | (INTLEVEL0)            |

|         | (INTLEVEL1)            |

|         |                        |

| 0x0032  | Potorvod               |

| ~       | Reserved               |

| 0x0033  |                        |

| 0x0034  | Socket Interrupt       |

|         | (IR2)                  |

| 0x0035  | PHY Status(PSTATUS)    |

| 0x0036  | Socket Interrupt       |

|         | Mask (IMR2)            |

# 3.2 Socket registers

Note : n is socket number ( 0, 1, 2, 3, 4, 5, 6, 7 )

| Address | Register                         | Address | Register                              |

|---------|----------------------------------|---------|---------------------------------------|

| 0x4n00  | Socket n Mode (Sn_MR)            |         | Receive Memory Size                   |

| 0x4n01  | Socket n Command (Sn_CR)         | 0x4n1E  | (Sn_RXMEM_SIZE)                       |

| 0x4n01  | Socket n Interrupt (Sn_IR)       | UXHITE  | Transmit Memory Size                  |

|         | $\cdot$ $\cdot$ $ \cdot$         | 0x4n1F  | (Sn_TXMEM_SIZE)                       |

| 0x4n03  | Socket n Status (Sn_SR)          | 0841115 | Socket n TX Free Size                 |

| 0 4 0 4 | Socket n Source Port             | 0.4-20  |                                       |

| 0x4n04  | (Sn_PORTO)                       | 0x4n20  | (Sn_TX_FSR0)                          |

| 0x4n05  | (Sn_PORT1)                       | 0x4n21  | (Sn_TX_FSR1)                          |

|         | Socket n Destination Hardware    |         | Socket n TX Read Pointer              |

|         | Address                          | 0x4n22  | (Sn_TX_RD0)                           |

| 0x4n06  | (Sn_DHAR0)                       | 0x4n23  | (Sn_TX_RD1)                           |

| 0x4n07  | (Sn_DHAR1)                       |         | Socket n TX Write Pointer             |

| 0x4n08  | (Sn_DHAR2)                       | 0x4n24  | (Sn_TX_WR0)                           |

| 0x4n09  | (Sn_DHAR3)                       | 0x4n25  | (Sn_TX_WR1)                           |

| 0x4n0A  | (Sn_DHAR4)                       |         | Socket n RX Received Size             |

| 0x4n0B  | (Sn_DHAR5)                       | 0x4n26  | (Sn_RX_RSR0)                          |

|         | Socket n Destination IP Address  | 0x4n27  | (Sn_RX_RSR1)                          |

| 0x4n0C  | (Sn_DIPR0)                       |         | Socket n RX Read Pointer              |

| 0x4n0D  | (Sn_DIPR1)                       | 0x4n28  | (Sn_RX_RD0)                           |

| 0x4n0E  | (Sn_DIPR2)                       | 0x4n29  | (Sn_RX_RD1)                           |

| 0x4n0F  | (Sn_DIPR3)                       |         | Socket n RX Write Pointer             |

|         | Socket n Destination Port        | 0x4n2A  | (Sn_RX_WR0)                           |

| 0x4n10  | (Sn_DPORT0)                      | 0x4n2B  | (Sn_RX_WR1)                           |

| 0x4n11  | (Sn_DPORT1)                      |         | Socket n Interrupt Mask               |

|         | Socket n Maximum Segment Size    | 0x4n2C  | (Sn_IMR)                              |

| 0x4n12  | (Sn_MSSR0)                       |         | Socket n Fragment Offset in IP header |

| 0x4n13  | (Sn_MSSR1)                       | 0x4n2D  | (Sn_FRAG0)                            |

|         | Socket n Protocol in IP Raw mode | 0x4n2E  | (Sn_FRAG1)                            |

| 0x4n14  | (Sn_PROTO)                       | 0x4n30  |                                       |

| 0x4n15  | Socket n IP TOS (Sn_TOS)         | ~       | Reserved                              |

| 0x4n16  | Socket n IP TTL (Sn_TTL)         | 0x4nFF  |                                       |

| 0x4n17  |                                  |         | l                                     |

| ~       | Reserved                         |         |                                       |

| 0x4n1D  |                                  |         |                                       |

|         |                                  |         |                                       |

# 4 Register Descriptions

### 4.1 Common Registers

#### MR (Mode Register) [R/W] [0x0000] [0x00]

This register is used for S/W reset, ping block mode and PPPoE mode.

| 7   | 6 | 5   | 4  | 3     | 2 | 1 | 0 |

|-----|---|-----|----|-------|---|---|---|

| RST |   | WOL | РВ | PPPoE |   |   |   |

| Bit | Symbol   | Description                                                                                                                                                                                                                  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RST      | S/W Reset<br>If this bit is '1', internal register will be initialized. It will be<br>automatically cleared after reset.                                                                                                     |

| 6   | Reserved | Reserved                                                                                                                                                                                                                     |

| 5   | WOL      | Wake on LAN<br>0:Normal Mode<br>1:WOL mode<br>If the bit is set as '1', there is waiting for the Magic Packet.                                                                                                               |

| 4   | РВ       | <b>Ping Block Mode</b><br>0 : Disable Ping block<br>1 : Enable Ping block<br>If the bit is set as '1', there is no response to the ping request.                                                                             |

| 3   | PPPoE    | PPPoE Mode 0 : DisablePPPoE mode 1 : EnablePPPoE mode If you use ADSL without router or etc, you should set the bit as '1' to connect to ADSL Server. For more detail, refer to the application note, "How to connect ADSL". |

| 2   | Reserved | Reserved                                                                                                                                                                                                                     |

| 1   | Reserved | Reserved                                                                                                                                                                                                                     |

| 0   | Reserved | Reserved                                                                                                                                                                                                                     |

#### GAR (Gateway IP Address Register) [R/W] [0x0001 - 0x0004] [0x00]

This Register sets up the default gateway address.

Ex) In case of "192.168.0.1"

| 0x0001     | 0x0002     | 0x0003   | 0x0004   |  |

|------------|------------|----------|----------|--|

| 192 (0xC0) | 168 (0xA8) | 0 (0x00) | 1 (0x01) |  |

#### SUBR (Subnet Mask Register) [R/W] [0x0005 - 0x0008] [0x00]

This register sets up the subnet mask address.

| Ex) In case of "25 | 5.255.255.0" |            |          |  |

|--------------------|--------------|------------|----------|--|

| 0x0005             | 0x0006       | 0x0007     | 0x0008   |  |

| 255 (0xFF)         | 255 (0xFF)   | 255 (0xFF) | 0 (0x00) |  |

SHAR (Source Hardware Address Register) [R/W] [0x0009 - 0x000E] [0x00]

This register sets up the Source Hardware address.

Ex) In case of "00.08.DC.01.02.03"

| 0x0009 | 0x000A | 0x000B | 0x000C | 0x000D | 0x000E |

|--------|--------|--------|--------|--------|--------|

| 0x00   | 0×08   | 0xDC   | 0x01   | 0x02   | 0x03   |

SIPR (Source IP Address Register) [R/W] [0x000F - 0x0012] [0x00]

This register sets up the Source IP address.

Ex) In case of "192.168.0.2"

| 0×  | 000F   | 0x0010     | 0x0011   | 0x0012   |

|-----|--------|------------|----------|----------|

| 192 | (0xC0) | 168 (0xA8) | 0 (0x00) | 2 (0x02) |

|     |        |            |          |          |

IR (Interrupt Register) [R] [0x0015] [0x00]

This register is accessed by the host processor to know the cause of interrupt. Any interruption can be masked in the Interrupt Mask Register (IMR2). The INTn signal retain low as long as any masked signal is set, and will not go high until all masked bits in this Register have been cleared.

| 7        | 6        | 5     | 4        | 3        | 2        | 1        | 0        |

|----------|----------|-------|----------|----------|----------|----------|----------|

| CONFLICT | Reserved | PPPoE | Reserved | Reserved | Reserved | Reserved | Reserved |

| Bit | Symbol   | Description                                                                                                                                                                                                  |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CONFLICT | IP Conflict<br>It is set as '1' when there is ARP request with same IP address<br>as Source IP address. This bit is cleared to '0' by writing '1' to<br>this bit.                                            |

| 6   | Reserved | Reserved                                                                                                                                                                                                     |

| 5   | PPPoE    | <b>PPPoE Connection Close</b><br>In the Point-to-Point Protocol over Ethernet (PPPoE) Mode, if<br>the PPPoE connection is closed, '1' is set. This bit will be<br>cleared to '0' by writing '1' to this bit. |

| 4   | Reserved | Reserved                                                                                                                                                                                                     |

| 3   | Reserved | Reserved                                                                                                                                                                                                     |

| 2   | Reserved | Reserved                                                                                                                                                                                                     |

| 1   | Reserved | Reserved                                                                                                                                                                                                     |

| 0   | Reserved | Reserved                                                                                                                                                                                                     |

© Copyright 2013 WIZnet Co.,Ltd. All rights reserved.

#### IMR(Interrupt Mask Register)[R/W][0x0016][0x00]

The Interrupt Mask Register is used to mask interrupts. Each interrupt mask bit corresponds to a bit in the Interrupt Register2 (IR2). If an interrupt mask bit is set, an interruption will be issued whenever the corresponding bit in the IR2 is set. If any bit in the IMR is set as '0' an interrupt will not occur though the bit.

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| S7_IMR | S6_IMR | S5_IMR | S4_IMR | S3_IMR | S2_IMR | S1_IMR | SO_IMR |

| Bit | Symbol | Description                |

|-----|--------|----------------------------|

| 7   | S7_IMR | IR2(S7_INT) Interrupt Mask |

| 6   | S6_IMR | IR2(S6_INT) Interrupt Mask |

| 5   | S5_IMR | IR2(S5_INT) Interrupt Mask |

| 4   | S4_IMR | IR2(S4_INT) Interrupt Mask |

| 3   | S3_IMR | IR2(S3_INT) Interrupt Mask |

| 2   | S2_IMR | IR2(S2_INT) Interrupt Mask |

| 1   | S1_IMR | IR2(S1_INT) Interrupt Mask |

| 0   | SO_IMR | IR2(S0_INT) Interrupt Mask |

#### RTR (Retry Time-value Register) [R/W] [0x0017 - 0x0018] [0x07D0]

It configures the retransmission timeout-period. The standard unit of RTR is 100us. RTR is initialized with 2000(0x07D0) and has 200ms timeout-period.

| 0x0017 | 0x0018 |

|--------|--------|

| 0x0F   | 0xA0   |

Re-transmission will occur if there is no response from the remote peer to the commands of CONNECT, DISCON, CLOSE, SEND, SEND\_MAC and SEND\_KEEP, or the response is delayed.

#### RCR (Retry Count Register) [R/W] [0x0019] [0x08]

It configures the number of retransmission times. When retransmission occurs as many as 'RCR+1' times, Timeout interrupt is set ('TIMEOUT' bit of Sn\_IR is set as '1').

In case of using TCP communication, the value of Sn\_SR (Socket n Status Register) is changed to 'SOCK\_CLOSED' and Sn\_IR(Socket n Status Register) (TIMEOUT) turns into '1'. In case of not using TCP communication, only Sn\_IR(TIMEOUT) turns into '1'.

**Ex)** RCR = 0x0007

The timeout of W5200 can be configurable with RTR and RCR. W5200's timeout has Address Resolution Protocol (ARP) and TCP retransmission timeout.

At the ARP (Refer to RFC 826, <u>http://www.ietf.org/rfc.html</u>) retransmission timeout, W5200 automatically sends ARP-request to the peer's IP address in order to acquire MAC address information (used for communication of IP, UDP, or TCP). As waiting for ARP-response from the peer, if there is no response during the time set in RTR, Timeout occurs and ARP-request is retransmitted. It is repeated as many as 'RCR + 1' times.

Even after ARP-request retransmissions are repeated 'RCR + 1' times, if there is no ARP-response, the final timeout occurs and Sn\_IR(TIMEOUT) becomes '1'.

The value of final timeout  $(ARP_{TO})$  of ARP-request is as below.

#### $ARP_{TO} = (RTR X 0.1ms) X (RCR + 1)$

At the TCP packet retransmission timeout, W5200 transmits TCP packets (SYN, FIN, RST, DATA packets) and waits for the acknowledgement (ACK) during the time set in RTR and RCR. If there is no ACK from the peer, Timeout occurs and TCP packets (sent earlier) are retransmitted. The retransmissions are repeated as many as 'RCR + 1' times. Even after TCP packet retransmissions are repeated 'RCR +1' times, if there is no ACK from the peer, final timeout occurs and Sn\_SR is changed to 'SOCK\_CLOSED" at the same time with Sn\_IR(TIMEOUT) = '1'

$$TCP_{TO} = \left(\begin{array}{c} M \\ \sum_{N=0}^{M} (RTR X 2^{N}) + ((RCR-M) X RTR_{MAX}) \end{array}\right) X 0.1 ms$$

$$N \quad : \quad \text{Retransmission count}, \quad 0 \le N \le M$$

$$M \quad : \quad \text{Minimum value when RTR X 2}^{(M+1)} > 65535 \text{ and } 0 \le M \le RCR$$

$$RTR_{MAX}: \quad RTR X 2^{M}$$

**Ex)** When RTR = 2000(0x07D0), RCR = 8(0x0008),

ARP<sub>TO</sub> = 2000 X 0.1ms X 9 = 1800ms = 1.8s

TCP<sub>TO</sub> = (0x07D0 + 0x0FA0 + 0x1F40 + 0x3E80 + 0x7D00 + 0xFA00 + 0xFA00 + 0xFA00 + 0xFA00) X 0.1ms

- = (2000 + 4000 + 8000 + 16000 + 32000 + ((8 4) X 64000)) X 0.1ms

- = 318000 X 0.1ms = 31.8s

The value of final timeout  $(TCP_{TO})$  of TCP packet retransmission can be calculated as below,

#### PATR (Authentication Type in PPPoE mode) [R] [0x001C-0x001D] [0x0000]

This register notifies authentication method that has been agreed at the connection with PPPoE Server. W5200 supports two types of Authentication method - PAP and CHAP.

| Value  | Authentication Type |

|--------|---------------------|

| 0xC023 | PAP                 |

| 0xC223 | СНАР                |

© Copyright 2013 WIZnet Co., Ltd. All rights reserved.

#### PPPALGO(Authentication Algorithm in PPPoE mode)[R][0x001E][0x00]

This register notifies authentication algorithm in PPPoE mode. For detailed information, please refer to PPPoE application note.

#### VERSIONR (W5200 Chip Version Register)[R][0x001F][0x03]

This register is the W5200 chip version register.

#### PTIMER (PPP Link Control Protocol Request Timer Register) [R/W] [0x0028]

This register indicates the duration for sending LCP Echo Request. Value 1 is about 25ms.

Ex) in case that PTIMER is 200,

200 \* 25(ms) = 5000(ms) = 5 seconds

#### PMAGIC (PPP Link Control Protocol Magic number Register) [R/W] [0x0029][0x00]

This register is used in Magic number option during LCP negotiation. Refer to the application note, *"How to connect ADSL"*.

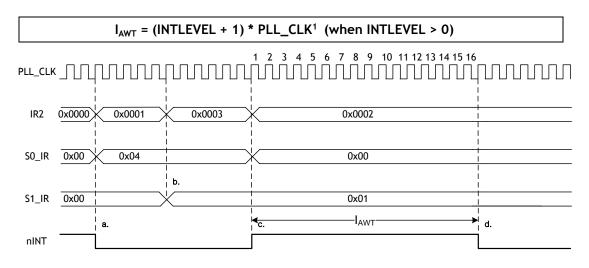

#### INTLEVEL (Interrupt Low Level Timer Register)[R/W][0x0030 - 0x0031][0x0000]

It sets Interrupt Assert wait time ( $I_{AWT}$ ). It configures INTn Low Assert waiting time until the next interrupt.

#### Figure 5 INTLEVEL Timing

- a. At SOCKET 0, Receive Timeout Interrupt occurs (S0\_IR(3) = '1') and corresponding IR2 bit is set as '1' (IR(S0\_IR) = '1'). INTn signal is asserted low.

- b. At SOCKET 1, Connected Interrupt occurs (S1\_IR(0) = '1') and corresponding IR2 bit set as '1' (IR2(S1\_IR) = '1').

- c. The Host clears  $SO_{IR}(SO_{IR} = 0x00)$  and corresponding IR2 bit is automatically cleared

#### <sup>1</sup> PLL\_CLK is 125MHz

© Copyright 2013 WIZnet Co., Ltd. All rights reserved.

(IR2(S0\_IR) = '0'). INTn signal becomes High.

d. S0\_IR is cleared. As IR2 is not 0x00, INTn should be asserted low right after 1PLL\_CLK. However, as INTLEVEL is 0x000F, the interrupt about IR is processed after  $I_{AWT}$ (16 PLL\_CLK).

#### IR2(W5200 SOCKET Interrupt Register)[R/W][0x0034][0x00]

IR2 is the Register to notify W5200 SOCKET interrupt to the Host. If any interrupt occurs, the related bit of IR2 is set as '1'. When related Mask Bit is '1', INTn signal is asserted low. INTn keeps low until all bits of Sn\_IR becomes '0'. If all bits of Sn\_IR become '0', it becomes high automatically.

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| S7_INT | S6_INT | S5_INT | S4_INT | S3_INT | S2_INT | S1_INT | S0_INT |

| Bit | Symbol | Description                                                             |

|-----|--------|-------------------------------------------------------------------------|

|     |        | When an interrupt occurs at SOCKET 7 , it becomes '1'. This interrupt   |

| 7   | S7_INT | information is applied to S7_IR. This bit is automatically cleared when |

|     |        | S7_IR is cleared to 0x00 by host.                                       |

|     |        | When an interrupt occurs at SOCKET 6 , it becomes '1'. This interrupt   |

| 6   | S6_INT | information is applied to S6_IR. This bit is automatically cleared when |

|     |        | S6_IR is cleared to 0x00 by host.                                       |

|     |        | When an interrupt occurs at SOCKET 5 , it becomes '1'. This interrupt   |

| 5   | S5_INT | information is applied to S5_IR. This bit is automatically cleared when |

|     |        | S5_IR is cleared to 0x00 by host.                                       |

|     |        | When an interrupt occurs at SOCKET 4 , it becomes '1'. This interrupt   |

| 4   | S4_INT | information is applied to S4_IR. This bit is automatically cleared when |

| _   |        | S4_IR is cleared to 0x00 by host.                                       |

|     |        | When an interrupt occurs at SOCKET 3 , it becomes '1'. This interrupt   |

| 3   | S3_INT | information is applied to S3_IR. This bit is automatically cleared when |

|     |        | S3_IR is cleared to 0x00 by host.                                       |

|     |        | When an interrupt occurs at SOCKET 2 , it becomes '1'. This interrupt   |

| 2   | S2_INT | information is applied to S2_IR. This bit is automatically cleared when |

|     |        | S2_IR is cleared to 0x00 by host.                                       |

|     |        | When an interrupt occurs at SOCKET 1 , it becomes '1'. This interrupt   |

| 1   | S1_INT | information is applied to S1_IR. This bit is automatically cleared when |

|     |        | S1_IR is cleared to 0x00 by host.                                       |

|     |        | When an interrupt occurs at SOCKET 0 , it becomes '0'. This interrupt   |

| 0   | S0_INT | information is applied to SO_IR. This bit is automatically cleared when |

|     |        | S0_IR is cleared to 0x00 by host.                                       |

#### PHYSTATUS(W5200 PHY status Register)[R/W][0x0035][0x00]

PHYSTATUS is the Register to indicate W5200 status of PHY.

| Bit | Symbol    | Description                                       |

|-----|-----------|---------------------------------------------------|

| 7   | Reserved  | Reserved                                          |

| 6   | Reserved  | Reserved                                          |

|     |           | Link Status Register[Read Only]                   |

| 5   | LINK      | This register indicates Link status.              |

| J   | LINK      | 0 : Link down                                     |

|     |           | 1 : Link Up                                       |

| 4   | Reserved  | Reserved                                          |

|     |           | Power down mode of PHY[Read/Write]                |

| 3   | POWERDOWN | This register indicates status of Power down mode |

| 5   | FOWERDOWN | 0 : Disable Power down mode(operates normal mode) |

|     |           | 1 : Enable Power down mode                        |

| 2   | Reserved  | Reserved                                          |

| 1   | Reserved  | Reserved                                          |

| 0   | Reserved  | Reserved                                          |

#### IMR2 (Socket Interrupt Mask Register2) [R/W] [0x0036] [0x00]

The IMR2(Socket Interrupt Mask Register) is used to mask interrupts. Each interrupt mask bit corresponds to a bit in the Interrupt Register (IR). If an interrupt mask bit is set, an interrupt will be issued whenever the corresponding bit in the IR is set. If any bit in the IMR2 is set as '0', an interrupt will not occur though the bit in the IR is set.

| 7      | 6        | 5      | 4        | 3        | 2        | 1        | 0        |

|--------|----------|--------|----------|----------|----------|----------|----------|

| IM_IR7 | Reserved | IM_IR5 | Reserved | Reserved | Reserved | Reserved | Reserved |

| Bit | Symbol   | Description        |

|-----|----------|--------------------|

| 7   | IM_IR7   | IP Conflict Enable |

| 6   | Reserved | Reserved           |

| 5   | IM_IR5   | PPPoE Close Enable |

| 4   | Reserved | Reserved           |

| 3   | Reserved | Reserved           |

| 2   | Reserved | Reserved           |

| 1   | Reserved | Reserved           |

| 0   | Reserved | Reserved           |

#### Socket Registers 4.2

#### Sn<sup>2</sup>\_MR (Socket n Mode Register) [R/W] [0x4000+0x0n00] [0x00]<sup>3</sup>

This register sets up socket option or protocol type for each socket.

| 7     | 6  | 5       | 4 | 3  | 2  | 1  | 0  |

|-------|----|---------|---|----|----|----|----|

| MULTI | MF | ND / MC |   | P3 | P2 | P1 | P0 |

| Bit | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MULTI  | Multicasting<br>0 : disable Multicasting<br>1 : enable Multicasting<br>It is applied only in case of UDP.<br>For using multicasting, write multicast group address to Socket n<br>Destination IP and multicast group port number to Socket n<br>Destination Port Register, before OPEN command.                                                                                                                                                                                                                                                                                                                                                                |

| 6   | MF     | MAC Filter<br>0 : Disable MAC filter<br>1 : Enable MAC filter<br>It is used in MACRAW (P3-P0: "0100").<br>When this bit is set as '1', W5200 can receive packet that is belong in<br>itself or broadcasting. When this bit is set as '0', W5200 can receive all<br>packets on Ethernet. When using the hybrid TCP/IP stack, it is<br>recommended to be set as '1' for reducing the receiving overhead of<br>host.                                                                                                                                                                                                                                              |

| 5   | ND/MC  | Use No Delayed ACK<br>0 : Disable No Delayed ACK option<br>1 : Enable No Delayed ACK option,<br>This only applies to TCP case (P3-P0 : "0001") If this bit is set as '1',<br>ACK packet is immediately transmitted after receiving data packet<br>from a peer. If this bit is cleared, ACK packet is transmitted according<br>to internal timeout mechanism.<br>Multicast<br>0 : using IGMP version 2<br>1 : using IGMP version 1<br>This bit is valid when MULTI bit is enabled and UDP mode is used (P3-<br>P0 : "0010"). In addition, multicast can be used to send out the version<br>number in IGMP messages such as Join/Leave/Report to multicast-group |

<sup>2</sup>*n* is Socket n-thumber (0, 1, 2, 3, 4, 5, 6, 7). <sup>3</sup>[Read/Write] [address of socket 0, address of socket 1, address of socket 2, address of socket 3, address of socket 4, address of socket 5, address of socket 6, address of socket 7] [Reset value]

<sup>©</sup> Copyright 2013 WIZnet Co., Ltd. All rights reserved.

| 4 | Reserved | Reserve  | d                          |                            |                             |                        |                             |

|---|----------|----------|----------------------------|----------------------------|-----------------------------|------------------------|-----------------------------|

|   |          | Protoco  | l                          |                            |                             |                        |                             |

| 3 | P3       | Sets u   | ip corre                   | sponding                   | g socket                    | as TCP,                | UDP, or IP RAW mode         |

|   |          | _        | Р                          | Р                          | Р                           | Р                      | Mooning                     |

|   |          |          | 3                          | 2                          | 1                           | 0                      | Meaning                     |

| 2 | P2       |          | 0                          | 0                          | 0                           | 0                      | Closed                      |

|   |          | -        | 0                          | 0                          | 0                           | 1                      | ТСР                         |

| 4 | D1       |          | 0                          | 0                          | 1                           | 0                      | UDP                         |

| 1 | P1       |          | 0                          | 0                          | 1                           | 1                      | IPRAW                       |

|   |          |          |                            | 1                          | 1                           | 1                      |                             |

|   |          | * In cas |                            |                            |                             |                        | PPoE mode exist.            |

|   |          | * In cas | Р                          | Р                          | Р                           | Р                      | PPoE mode exist.<br>Meaning |

|   |          | * In cas |                            |                            |                             |                        |                             |

| 0 | PO       | * In cas | P<br>3                     | P<br>2                     | P<br>1                      | P<br>0                 | Meaning                     |

| 0 | PO       |          | P<br>3<br>0<br>0           | P<br>2<br>1<br>1           | P<br>1<br>0<br>0            | P<br>0<br>0<br>1       | Meaning<br>MACRAW           |

| 0 | PO       | SO_MI    | P<br>3<br>0<br>0<br>R_MACR | P<br>2<br>1<br>1<br>AW and | P<br>1<br>0<br>0<br>S0_MR_I | P<br>0<br>1<br>PPPoE a | Meaning<br>MACRAW<br>PPPoE  |

Sn\_CR (Socket n Command Register) [R/W] [0x4001+0x0n00] [0x00]

This is used to set the command for Socket n such as OPEN, CLOSE, CONNECT, LISTEN, SEND, and RECEIVE. After W5200 identifies the command, the Sn\_CR register is automatically cleared to 0x00. Even though Sn\_CR is cleared to 0x00, the command is still being processed. To verify whether the command is completed or not, please check the Sn\_IR or Sn\_SR registers.

| Value | Symbol    | Description                                                               |                                        |  |  |  |  |  |

|-------|-----------|---------------------------------------------------------------------------|----------------------------------------|--|--|--|--|--|

|       |           | Socket n is initialized and opened a                                      | according to the protocol selected in  |  |  |  |  |  |

|       | 0x01 OPEN | Sn_MR (P3:P0). The table below shows the value of Sn_SR corresponding     |                                        |  |  |  |  |  |

|       |           | to Sn_MR                                                                  |                                        |  |  |  |  |  |

|       |           | Sn_MR(P3:P0)                                                              | Sn_SR                                  |  |  |  |  |  |

| 0x01  |           | Sn_MR_CLOSE (0x00)                                                        | -                                      |  |  |  |  |  |

| 0.01  | OFLIN     | Sn_MR_TCP (0x01)                                                          | SOCK_INIT (0x13)                       |  |  |  |  |  |

|       |           | Sn_MR_UDP (0x02)                                                          | SOCK_UDP (0x22)                        |  |  |  |  |  |

|       |           | Sn_MR_IPRAW (0x03)                                                        | SOCK_IPRAW (0x32)                      |  |  |  |  |  |

|       |           | S0_MR_MACRAW (0x04)                                                       | SOCK_MACRAW (0x42)                     |  |  |  |  |  |

|       |           | S0_MR_PPPoE (0x05)                                                        | SOCK_PPPoE (0x5F)                      |  |  |  |  |  |

|       |           | This is valid only in TCP mode (S                                         | n_MR(P3:P0) = Sn_MR_TCP). In this      |  |  |  |  |  |

|       |           | mode, the Socket n is configured                                          | as a TCP server which is waiting for   |  |  |  |  |  |

|       |           | connection-request (SYN packet) f                                         | rom any "TCP CLIENT". The Sn_SR        |  |  |  |  |  |

|       |           | register changes the state from SOCK_INIT to SOCKET_LISTEN.               |                                        |  |  |  |  |  |

|       |           | When a client's connection request is successfully established, the Sn_SR |                                        |  |  |  |  |  |

| 0x02  |           | changes from SOCK_LISTEN to SOCK_ESTABLISHED and the Sn_IR(0)             |                                        |  |  |  |  |  |

| UXUZ  | LISTEN    | becomes '1'. On the other hand, Sn_IR(3) is set as '1' and Sn_SR changes  |                                        |  |  |  |  |  |

|       |           | to SOCK_CLOSED during a connection failure(SYN/ACK packet failed to       |                                        |  |  |  |  |  |

|       |           | transfer)                                                                 |                                        |  |  |  |  |  |

|       |           | cf> If the destination port of the                                        | TCP Client does not exist during a     |  |  |  |  |  |

|       |           | connection request, W5200 will transmit a RST packet and Sn_SR is         |                                        |  |  |  |  |  |

|       |           | unchanged.                                                                |                                        |  |  |  |  |  |

|       |           | This mode is only valid in TCP mode                                       | and operates the Socket n as a TCP     |  |  |  |  |  |

|       |           | client.A connect-request (SYN packet) is sent to the TCP server by        |                                        |  |  |  |  |  |

|       |           | connecting to the IP address and port stored in destination address and   |                                        |  |  |  |  |  |

|       |           | port registers (Sn_DIPR0 and Sn_DPORT0)                                   |                                        |  |  |  |  |  |

| 0x04  | CONNECT   | When a client's connection request i                                      | is successfully established, the Sn_SR |  |  |  |  |  |

| 0x04  | CONNECT   | register is changed to SOCK_ESTA                                          | BLISHED and the Sn_IR(0) becomes       |  |  |  |  |  |

|       |           | '1'.In the following cases, the cor                                       | nnect-request fails When a ARPTO       |  |  |  |  |  |

|       |           | occurs (Sn_IR(s)='1') because the E                                       | Destination Hardware Address is not    |  |  |  |  |  |

|       |           | acquired through the ARP process                                          |                                        |  |  |  |  |  |

|       |           | When a SYN/ACK packet is not receive                                      | ved and TCPTO(Sn_IR(3)) is'1'          |  |  |  |  |  |

| W    | WIZnet    |                                                                          |  |  |

|------|-----------|--------------------------------------------------------------------------|--|--|

|      |           | When a RST packet is received instead of a SYN/ACK packet                |  |  |

|      |           | Above three cases, Sn_SR is changed to SOCK_CLOSED.                      |  |  |

|      |           | Only valid in TCP mode                                                   |  |  |

|      |           | Regardless of "TCP SERVER" or "TCP CLIENT", this disconnect command      |  |  |

|      |           | processes the                                                            |  |  |

|      |           | Active close: it transmits disconnect-request(FIN packet) to the         |  |  |

|      |           | connected peer                                                           |  |  |

|      |           | Passive close: When FIN packet is received from peer, a FIN packet is    |  |  |

| 0x08 | DISCON    | replied back to the peer                                                 |  |  |

| UNUU | DISCON    | when FIN/ACK packet is received, Sn_SR is changed to SOCK_CLOSED.        |  |  |

|      |           | When a disconnect request is not received, TCPTO occurs (Sn_IR(3)='1')   |  |  |

|      |           | and Sn_SR is changed to SOCK_CLOSED.                                     |  |  |

|      |           | cf> If CLOSE is used instead of DISCON, only Sn_SR is changed to         |  |  |

|      |           | SOCK_CLOSED without disconnect-process(disconnect-request). If a RST     |  |  |

|      |           | packet is received from a peer during communication, Sn_SR is            |  |  |

|      |           | unconditionally changed to SOCK_CLOSED.                                  |  |  |

| 0x10 | CLOSE     | Closes Socket n .                                                        |  |  |

|      |           | Sn_SR is changed to SOCK_CLOSED.                                         |  |  |

|      |           | SEND transmits all the data buffered in the TX memory. For more details, |  |  |

|      |           | please refer to Socket n TX Free Size Register (Sn_TX_FSRO), Socket n    |  |  |

| 0x20 | SEND      | TX Write Pointer Register(Sn_TX_WR0), and Socket n TX Read Pointer       |  |  |

|      |           | Register(Sn_TX_RD0).                                                     |  |  |

|      |           | Used in UDP mode only                                                    |  |  |

|      |           | The basic operation is same as SEND. Normally SEND operation needs       |  |  |

| 0.04 |           | Destination Hardware Address which can be retrieved by the ARP           |  |  |

| 0x21 | SEND_MAC  | (Address Resolution Protocol) process. SEND_MAC uses Socket n            |  |  |

|      |           | Destination Hardware Address(Sn_DHAR0) that is chosen by the user        |  |  |

|      |           | without going through the ARP process.                                   |  |  |

|      |           | Used in TCP mode                                                         |  |  |

| 0x22 |           | It checks the connection status by sending 1byte data. If the connection |  |  |

| UXZZ | SEND_KEEP | has no response from peers or is terminated, the Timeout interrupt will  |  |  |

|      |           | occur.                                                                   |  |  |

|      |           | RECV processes the data received by using a RX read pointer              |  |  |

|      |           | register(Sn_RX_RD).                                                      |  |  |

| 0x40 | RECV      | For more detail, please refer to 5.2.1.1 SERVER mode Receiving Process   |  |  |

| 0,40 |           | with Socket n RX Received Size Register (Sn_RX_RSRO), Socket n RX        |  |  |

|      |           | Write Pointer Register(Sn_RX_WR), and Socket n RX Read Pointer           |  |  |

|      |           | Register(Sn_RX_RD).                                                      |  |  |

© Copyright 2013 WIZnet Co.,Ltd. All rights reserved.

Below commands are only valid for SOCKET 0 and SO\_MR(P3:P0) = SO\_MR\_PPPoE. For more detail refer to the "How to use ADSL".

| Value | Symbol Description |                                                                |

|-------|--------------------|----------------------------------------------------------------|

| 0x23  | PCON               | PPPoE connection begins by transmitting PPPoE discovery packet |

| 0x24  | PDISCON            | Closes PPPoE connection                                        |

| 0x25  | PCR                | In each phase, it transmits REQ message.                       |

| 0x26  | PCN                | In each phase, it transmits NAK message.                       |

| 0x27  | PCJ                | In each phase, it transmits REJECT message.                    |

Sn\_IR (Socket n Interrupt Register) [R] [0x4002+0x0n00] [0x00]

Sn\_IR register provides information such as the type of interrupt (establishment, termination, receiving data, timeout) used in Socket n. When an interrupt occurs and the mask bit of Sn\_IMR is '1', the interrupt bit of Sn\_IR becomes '1'.

In order to clear the Sn\_IR bit, the host should write the bit as '1'. When all the bits of Sn\_IR is cleared ('0'), IR(n) is automatically cleared.

| 7     | 6     | 5     | 4       | 3       | 2    | 1      | 0   |

|-------|-------|-------|---------|---------|------|--------|-----|

| PRECV | PFAIL | PNEXT | SEND_OK | TIMEOUT | RECV | DISCON | CON |

| Bit | Symbol  | Description                                                         |

|-----|---------|---------------------------------------------------------------------|

|     |         | Sn_IR(PRECV) Interrupt                                              |

| 7   | PRECV   | Valid only in case of 'SOCKET=0' and 'S0_MR(P3:P0)=S0_MR_PPPoE'     |

| ,   | TRECT   | PPP Receive Interrupts when the option which is not supported is    |

|     |         | received                                                            |

|     |         | Sn_IR(PFAIL) Interrupt                                              |

| 6   | PFAIL   | Valid only in case of 'SOCKET=0' & 'S0_MR(P3:P0)=S0_MR_PPPoE'       |

|     |         | PPP Fail Interrupts when PAP Authentication is failed               |

|     |         | Sn_IR(PNEXT) Interrupt                                              |

| 5   | PNEXT   | Valid only in case of 'SOCKET=0' & 'S0_MR(P3:P0)=S0_MR_PPPoE'       |

| 5   |         | PPP Next Phase Interrupts when the phase is changed during ADSL     |

|     |         | connection process                                                  |

| 4   | SEND_OK | Sn_IR(SENDOK) Interrupt                                             |

|     |         | SEND OK Interrupts when the SEND command is completed               |

| 3   | TIMEOUT | Sn_IR(TIMEOUT) Interrupt                                            |

|     |         | TIMEOUT Interrupts when $ARP_{TO}$ or $TCP_{TO}$ occurs             |

| 2   | RECV    | Sn_IR(RECV) Interrupt                                               |

|     | NEC V   | Receive Interrupts whenever data packet is received from a peer     |

|     |         | Sn_IR(DISCON) Interrupt                                             |

| 1   | DISCON  | Disconnect Interrupts when FIN of FIN/ACK packet is received from a |

|     |         | peer                                                                |

| 0   | CON     | Sn_IR(CON) Interrupt                                                |

|     | CON     | Connect Interrupts when a connection is established with a peer     |

#### Sn\_SR (Socket n Status Register) [R] [0x4003+0x0n00] [0x00]

This register provides the status of Socket n. SOCKET status are changed when using the Sn\_CR register or during packet transmission/reception. The table below describes the different states of Socket n.

| Value | Symbol           | Description                                                         |

|-------|------------------|---------------------------------------------------------------------|

| 0x00  | SOCK_CLOSED      | It is the status that resource of SOCKETn is released. When         |

|       |                  | DISCON or CLOSE command is performed, or $ARP_{TO}$ , or $TCP_{TO}$ |

|       |                  | occurs, it is changed to SOCK_CLOSED regardless of                  |

|       |                  | previous value.                                                     |

| 0x13  | SOCK_INIT        | It is shown in case that Sn_MR is set as TCP and OPEN               |

|       |                  | commands are given to Sn_CR. It is changed to SOCK_INIT             |

|       |                  | when Sn_MR (P3:P0) is Sn_MR_TCP and OPEN command is                 |

|       |                  | performed. It is the initial step of TCP connection                 |

|       |                  | establishment.                                                      |

|       |                  | It is possible to perform LISTEN command at the "TCP                |

|       |                  | SERVER" mode and CONNECT command at the "TCP CLIENT".               |

|       |                  | It is the status that SOCKETn operates as "TCP SERVER" and          |

|       |                  | waits for connect-request (SYN packet) from "TCP CLIENT".           |

| 0x14  | SOCK_LISTEN      | Socket n operates in TCP Server Mode and waits for a                |

|       |                  | connection-request (SYN packet) from a "TCP CLIENT".                |

|       |                  | When the LISTEN command is used, the stage changes to               |

|       |                  | SOCK_LISTEN                                                         |

|       |                  | Once the connection is established, the SOCKET state                |

|       |                  | changes from SOCK_LISTEN to SOCK_ESTABLISHED; however,              |

|       |                  | if the connection fails, $TCP_{TO}$ occurs (Sn_IR(TIME_OUT) =       |

|       |                  | '1') and the state changes to SOCK_CLOSED.                          |

| 0x17  | SOCK_ESTABLISHED | It is shown in case that connection is established. It is           |

|       |                  | changed to SOCK_ESTABLISHED when SYN packet from "TCP               |

|       |                  | CLIENT" is successfully processed at the SOCK_LISTEN, or            |

|       |                  | CONNECTS command is successfully performed. At this                 |

|       |                  | status, DATA packet can be transferred, that is, SEND or            |

|       |                  | RECV command can be performed.                                      |

| 0x1C  | SOCK_CLOSE_WAIT  | It is the status that disconnect-request (FIN packet) is            |

|       |                  | received from the peer As TCP connection is half-closed, it         |

|       |                  | is possible to transfer data packet. In order to complete the       |

|       |                  | TCP disconnection, DISCON command should be performed.              |

|       |                  | For SOCKETn close without disconnection-process, CLOSE              |

|       |                  | command should be just performed.                                   |

| <b>WIZ</b> | net                                                                   | 1                                                         |  |

|------------|-----------------------------------------------------------------------|-----------------------------------------------------------|--|

| 0x22       | SOCK_UDP                                                              | It is the status that SOCKETn is open as UDP mode. It is  |  |

|            |                                                                       | changed to SOCK_UDP when Sn_MR(P3:P0) is Sn_MR_UDP        |  |

|            |                                                                       | and OPEN command is performed. DATA packet can be         |  |

|            |                                                                       | transferred without connection that is necessary to TCP   |  |

|            |                                                                       | mode SOCKET.                                              |  |

| 0x32       | SOCK_IPRAW                                                            | The socket is opened in IPRAW mode. The SOCKET status is  |  |

|            |                                                                       | change to SOCK_IPRAW when Sn_MR (P3:P0) is                |  |

|            |                                                                       | Sn_MR_IPRAW and OPEN command is used. IP Packet can be    |  |

|            |                                                                       | transferred without a connection similar to the UDP mode. |  |

| 0x42       | SOCK_MACRAW                                                           | It is changed to SOCK_MACRAW in case of SO_CR=OPEN and    |  |

|            |                                                                       | S0_MR (P3:P0)=S0_MR_MACRAW. MACRAW packet (Ethernet       |  |

|            |                                                                       | frame) can be transferred similar to UDP mode.            |  |

| 0x5F       | SOCK_PPPOE It is the status that SOCKETO is open as PPPoE mode. It is |                                                           |  |

|            |                                                                       | changed to SOCK_PPPoE in case of SO_CR=OPEN and SO_M      |  |

|            |                                                                       | (P3:P0)=S0_MR_PPPoE . It is temporarily used at the PPPoE |  |

|            |                                                                       | connection.                                               |  |

Below is shown during changing the status.

| Value | Symbol         | Description                                                    |