# W6100

## Hardwired Dual TCP/IP Stack Controller

V1.0.4

## W6100

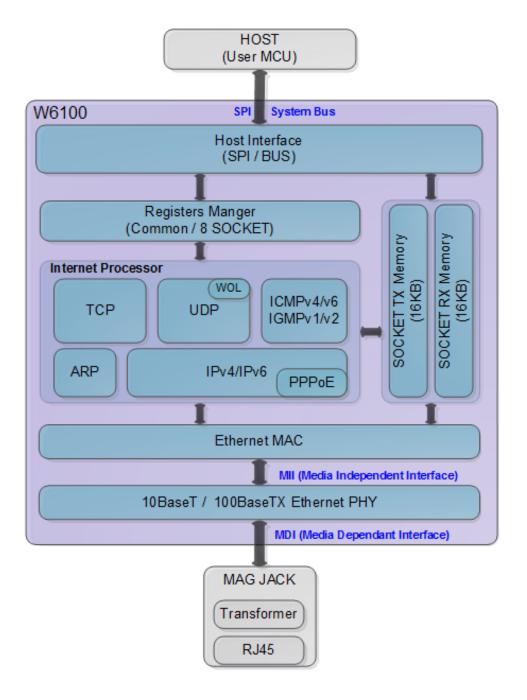

W6100 is a hardwired Internet controller chip supporting IPv4/IPv6 dual stack by adding IPv6 functions on the basis of WIZnet's patented hardwired TCP/IP core technology. W6100 supports TCP/IP protocols such as TCP, UDP, IPv6, IPv4, ICMPv6, ICMPv4, IGMP, ARP and PPPoE. W6100 also includes 10Base-T / 10Base-Te / 100Base-TX Ethernet PHY and Ethernet MAC Controller which makes it suitable for embedded internet-enabled devices.

W6100 has 8 independent hardwired SOCKETs and supports various SOCKET-less commands, which are for IPv6 auto-configuration, monitoring, and managing the network via ARP, PINGv4, and PINGv6.

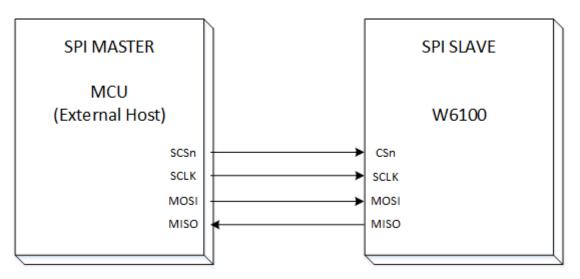

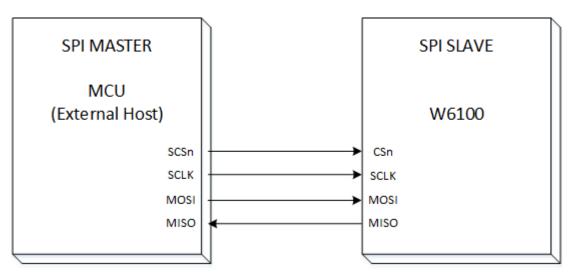

W6100 supports two kinds of HOST interfaces; SPI and parallel system BUS. It has 32KB internal memory for sending and receiving data. Designed for low power and low heat, W6100 provides WOL (Wake On LAN), Ethernet PHY power down mode and etc.

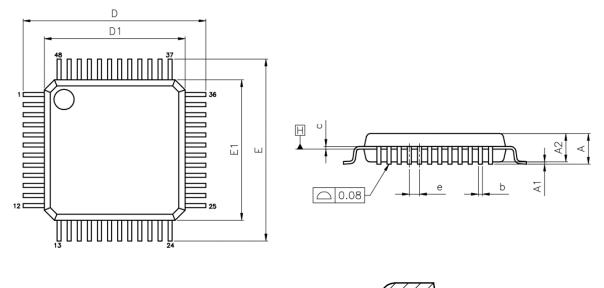

W6100 has two package types, 48 LQFP and 48 QFN lead-free. Both versions are PIN-2-PIN compatible with W5100S.

### Features

- Supports hardwired TCP/IP protocols

- : TCP, UDP, IPv6, IPv4, ICMPv6, ICMPv4, IGMP, MLDv1, ARP, PPPoE

- Supports IPv4/IPv6 dual stack

- Supports 8 independent SOCKETs simultaneously with 32KB memory

- Supports SOCKET-less commands

- : ARP, ICMPv6 (ARP, DAD, NA, RS) command for IPv6 auto-configuration & network monitoring (PING, PING6)

- Supports Ethernet PHY power down mode & system clock switching for power save

- Supports wake on LAN over UDP

- Supports serial & parallel HOST interface

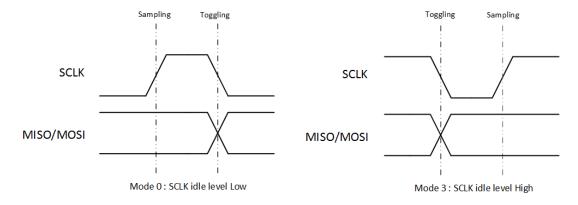

- : High speed SPI (MODE 0/3), system BUS with 2 address signal & 8bit data

- Internal 32Kbytes memory for TX/ RX Buffers

- 10BaseT/ 10BaseTe / 100BaseTX Ethernet PHY integrated

- Supports auto negotiation (full/half duplex, 10 and 100-based)

- Supports auto-MDIX only on auto-negotiation mode

- Does not support IP fragmentation & jumbo packet

- 3V operation with 5V I/O signal tolerance

- Network indicator LEDs (full/half duplex, link, 10/100 speed, active)

- 48 Pin LQFP & QFN lead-free package (7x7mm, 0.5mm pitch)

- PIN-2-PIN compatible with W5100S

### **Target Applications**

W6100 can be used in various applications.

- Home network devices: set-top boxes, PVRs, digital media adapters

- Serial-to-Ethernet: access control, LED display, wireless AP relay

- Parallel-to-Ethernet: POS / mini printers, copy machine

- USB-to-Ethernet: storage devices, network printers

- GPIO-to-Ethernet: Home network sensors

- Security systems: DVR, network cameras, kiosks

- Factory & home automation

- Medical monitoring equipment

- Embedded servers

- Internet of Thing (IoT) devices

- IoT cloud devices

- Etc

## **Block Diagram**

Figure 1 Block Diagram

## Contents

| 1. | PIN         | Description 12                                                   |

|----|-------------|------------------------------------------------------------------|

|    | 1.1         | PIN Description13                                                |

| 2. | Men         | nory Map 17                                                      |

| 3. | <b>W6</b> 1 | 100 Registers                                                    |

|    | 3.1         | Common Register19                                                |

|    | 3.2         | SOCKET Register25                                                |

| 4. | Reg         | ister Descriptions                                               |

|    | 4.1         | Common Registers28                                               |

|    |             | 4.1.1 CIDR (Chip Identification Register)                        |

|    |             | 4.1.2 VER (Version Register)                                     |

|    |             | 4.1.3 SYSR (System Status Register)28                            |

|    |             | 4.1.4 SYCR0 (System Config Register 0)29                         |

|    |             | 4.1.5 SYCR1 (System Config Register 1)                           |

|    |             | 4.1.6 TCNTR (Tick Counter Register)                              |

|    |             | 4.1.7 TCNTRCLR (TCNTR Clear Register)                            |

|    |             | 4.1.8 IR (Interrupt Register)                                    |

|    |             | 4.1.9 SIR (SOCKET Interrupt Register)                            |

|    |             | 4.1.10 SLIR (SOCKET-less Interrupt Register)                     |

|    |             | 4.1.11 IMR (Interrupt Mask Register)                             |

|    |             | 4.1.12 IRCLR (IR Clear Register)                                 |

|    |             | 4.1.13 SIMR (SOCKET Interrupt Mask Register)                     |

|    |             | 4.1.14 SLIMR (SOCKET-less Interrupt Mask Register)               |

|    |             | 4.1.15 SLIRCLR (SLIR Clear Register)                             |

|    |             | 4.1.16 SLPSR (SOCKET-less Prefer Source IPv6 Address Register)35 |

|    |             | 4.1.17 SLCR (SOCKET-less Command Register)                       |

|    |             | 4.1.18 PHYSR (PHY Status Register)                               |

|    |             | 4.1.19 PHYRAR (PHY Register Address Register)                    |

|    |             | 4.1.20 PHYDIR (PHY Data Input Register)                          |

|    |             | 4.1.21 PHYDOR (PHY Data Output Register)                         |

|    |             | 4.1.22 PHYACR (PHY Access Control Register)                      |

|    |             | 4.1.23 PHYDIVR (PHY Division Register)                           |

|    |             | 4.1.24 PHYCR0 (PHY Control Register 0)                           |

|    |             | 4.1.25 PHYCR1 (PHY Control Register 1)                           |

|    |             | 4.1.26 NET4MR (Network IPv4 Mode Register)40                     |

|    |             | 4.1.27 NET6MR (Network IPv6 Mode Register)41                     |

|    |             | 4.1.28 NETMR (Network Mode Register)42                           |

|    |             | 4.1.29 NETMR2 (Network Mode Register 2)43                        |

|     | 4.1.30 PTMR (PPP Link Control Protocol Request Timer Register)43    |

|-----|---------------------------------------------------------------------|

|     | 4.1.31 PMNR (PPP Link Control Protocol Magic number Register)43     |

|     | 4.1.32 PHAR (PPPoE Server Hardware Address Register on PPPoE)44     |

|     | 4.1.33 PSIDR (PPPoE Session ID Register on PPPoE)44                 |

|     | 4.1.34 PMRUR (PPPoE Maximum Receive Unit Register)44                |

|     | 4.1.35 SHAR (Source Hardware Address Register)44                    |

|     | 4.1.36 GAR (Gateway IP Address Register)45                          |

|     | 4.1.37 SUBR (Subnet Mask Register)45                                |

|     | 4.1.38 SIPR (IPv4 Source Address Register)45                        |

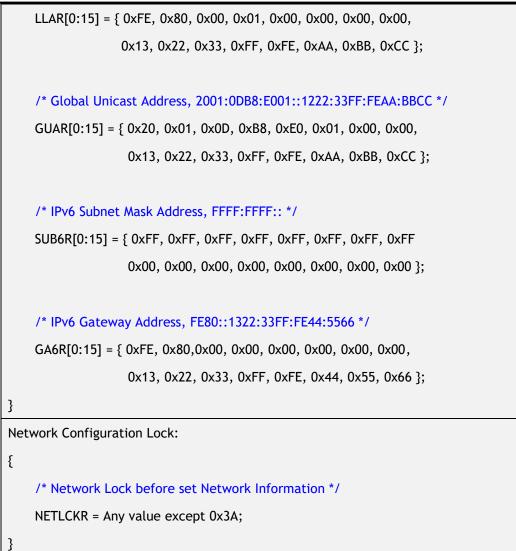

|     | 4.1.39 LLAR (Link Local Address Register)46                         |

|     | 4.1.40 GUAR (Global Unicast Address Register)46                     |

|     | 4.1.41 SUB6R (IPv6 Subnet Prefix Register)                          |

|     | 4.1.42 GA6R (IPv6 Gateway Address Register)47                       |

|     | 4.1.43 SLDIP6R (SOCKET-less Destination IPv6 Address Register)47    |

|     | 4.1.44 SLDIPR (SOCKET-less Destination IPv4 Address Register)47     |

|     | 4.1.45 SLDHAR (SOCKET-less Destination Hardware Address Register)48 |

|     | 4.1.46 PINGIDR (PING ID Register)                                   |

|     | 4.1.47 PINGSEQR (PING Sequence-number Register)                     |

|     | 4.1.48 UIPR (Unreachable IP Address Register)                       |

|     | 4.1.49 UPORTR (Unreachable Port Register)                           |

|     | 4.1.50 UIP6R (Unreachable IPv6 Address Register)49                  |

|     | 4.1.51 UPORT6R (Unreachable IPv6 Port Register)49                   |

|     | 4.1.52 INTPTMR (Interrupt Pending Time Register)50                  |

|     | 4.1.53 PLR (Prefix Length Register)                                 |

|     | 4.1.54 PFR (Prefix Flag Register)                                   |

|     | 4.1.55 VLTR (Valid Life Time Register)                              |

|     | 4.1.56 PLTR (Preferred Life Time Register)51                        |

|     | 4.1.57 PAR (Prefix Address Register)51                              |

|     | 4.1.58 ICMP6BLKR (ICMPv6 Block Register)51                          |

|     | 4.1.59 CHPLCKR (Chip Lock Register)                                 |

|     | 4.1.60 NETLCKR (Network Lock Register)                              |

|     | 4.1.61 PHYLCKR (PHY Lock Register)                                  |

|     | 4.1.62 RTR (Retransmission Time Register)                           |

|     | 4.1.63 RCR (Retransmission Count Register)53                        |

|     | 4.1.64 SLRTR (SOCKET-less Retransmission Time Register)53           |

|     | 4.1.65 SLRCR (SOCKET-less Retransmission Count Register)54          |

|     | 4.1.66 SLHOPR (Hop limit Register)                                  |

| 4.2 | SOCKET Register55                                                   |

|     | 4.2.1 Sn_MR (SOCKET n Mode Register)55                              |

5.

6.

|     | 4.2.2 Sn_PSR (SOCKET n Prefer Source IPv6 Address Register)57     |

|-----|-------------------------------------------------------------------|

|     | 4.2.3 Sn_CR (SOCKET n Command Register)57                         |

|     | 4.2.4 Sn_IR (SOCKET n Interrupt Register)60                       |

|     | 4.2.5 Sn_IMR (SOCKET n Interrupt Mask Register)60                 |

|     | 4.2.6 Sn_IRCLR (Sn_IR Clear Register)61                           |

|     | 4.2.7 Sn_SR (SOCKET n Status Register)61                          |

|     | 4.2.8 Sn_ESR (SOCKET n Extension Status Register)62               |

|     | 4.2.9 Sn_PNR (SOCKET n IP Protocol Number Register)63             |

|     | 4.2.10 Sn_TOSR (SOCKET n IP Type of Service Register)63           |

|     | 4.2.11 Sn_TTLR (SOCKET n IP Time To Live Register)63              |

|     | 4.2.12 Sn_FRGR (SOCKET n Fragment Offset in IP Header Register)63 |

|     | 4.2.13 Sn_MSSR (SOCKET n Maximum Segment Size Register)64         |

|     | 4.2.14 Sn_PORTR (SOCKET n Source Port Register)64                 |

|     | 4.2.15 Sn_DHAR (SOCKET n Destination Hardware Address Register)65 |

|     | 4.2.16 Sn_DIPR (SOCKET n Destination IPv4 Address Register)       |

|     | 4.2.17 Sn_DIP6R (SOCKET n Destination IPv6 Address Register)65    |

|     | 4.2.18 Sn_DPORTR (SOCKET n Destination Port Register)66           |

|     | 4.2.19 Sn_MR2 (SOCKET n Mode register 2)67                        |

|     | 4.2.20 Sn_RTR (SOCKET n Retransmission Time Register)68           |

|     | 4.2.21 Sn_RCR (SOCKET n Retransmission Count Register)68          |

|     | 4.2.22 Sn_KPALVTR (SOCKET n Keep Alive Time Register)68           |

|     | 4.2.23 Sn_TX_BSR (SOCKET n TX Buffer Size Register)68             |

|     | 4.2.24 Sn_TX_FSR (SOCKET n TX Free Buffer Size Register)69        |

|     | 4.2.25 Sn_TX_RD (SOCKET n TX Read Pointer Register)               |

|     | 4.2.26 Sn_TX_WR (SOCKET n TX Write Pointer Register)70            |

|     | 4.2.27 Sn_RX_BSR (SOCKET n RX Buffer Size Register)               |

|     | 4.2.28 Sn_RX_RSR (SOCKET n RX Received Size Register)70           |

|     | 4.2.29 Sn_RX_RD (SOCKET n RX Read Pointer Register)71             |

|     | 4.2.30 Sn_RX_WR (SOCKET n RX Write Pointer Register)71            |

| HOS | T Interface Mode                                                  |

| 5.1 | SPI Mode                                                          |

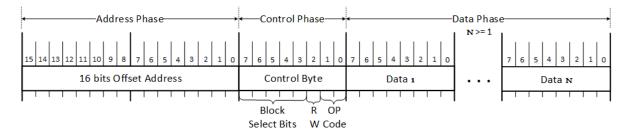

|     | 5.1.1 SPI Frame                                                   |

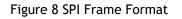

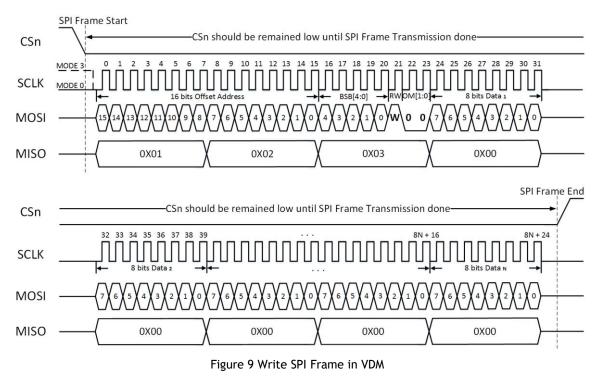

|     | 5.1.2 Variable Length Data Mode (VDM)76                           |

|     | 5.1.3 Fixed Length Data Mode (FDM)77                              |

| 5.2 | Parallel BUS Mode                                                 |

|     | 5.2.1 Parallel BUS Data Write                                     |

|     | 5.2.2 Parallel BUS Data Read82                                    |

| Fun | ctional Description                                               |

| 6.1 | Initialization83                                                  |

|                |                  | 6.1.1 Network Information Setting83              |  |  |  |

|----------------|------------------|--------------------------------------------------|--|--|--|

|                |                  | 6.1.2 SOCKET TX/RX Buffer Size Setting           |  |  |  |

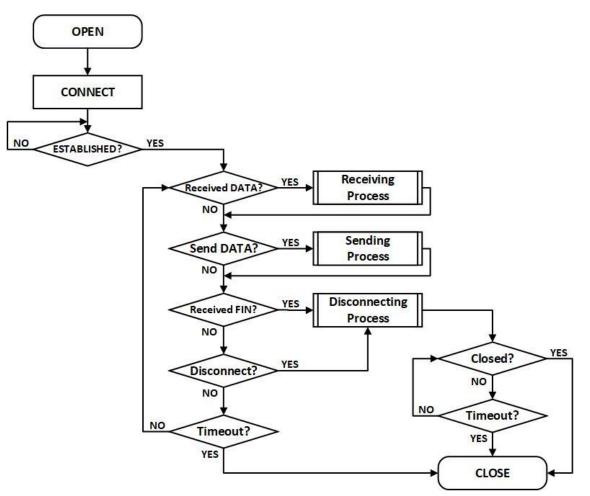

| 6.             | 6.2 TCP          |                                                  |  |  |  |

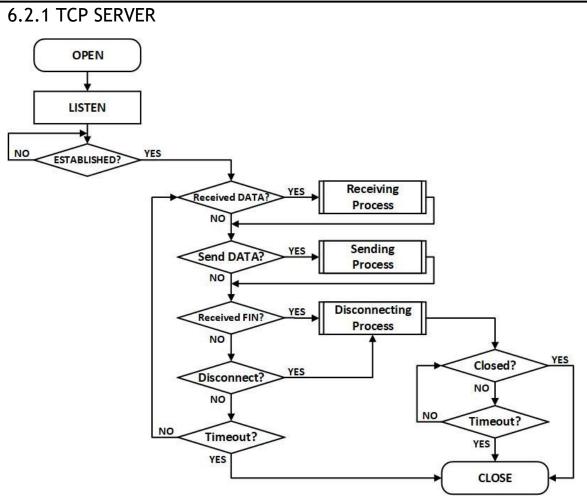

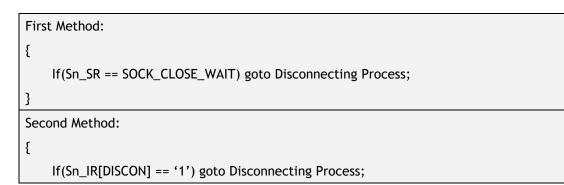

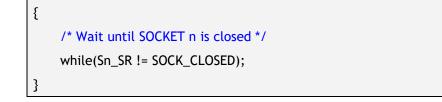

|                | 6.2.1 TCP SERVER |                                                  |  |  |  |

|                |                  | 6.2.2 TCP CLIENT93                               |  |  |  |

| 6.2.3 TCP DUAL |                  |                                                  |  |  |  |

|                |                  | 6.2.4 Other Functions96                          |  |  |  |

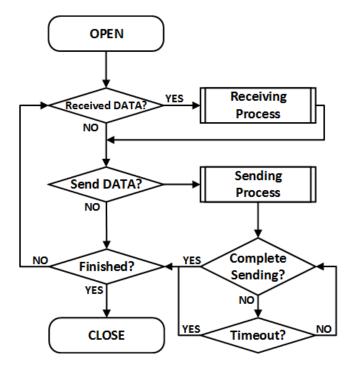

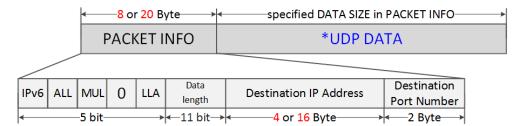

| 6.             | 3                | UDP98                                            |  |  |  |

|                |                  | 6.3.1 UDP Unicast                                |  |  |  |

|                |                  | 6.3.2 UDP Broadcast 102                          |  |  |  |

|                |                  | 6.3.3 UDP Multicast 104                          |  |  |  |

|                |                  | 6.3.4 UDP DUAL                                   |  |  |  |

|                |                  | 6.3.5 Other Functions 108                        |  |  |  |

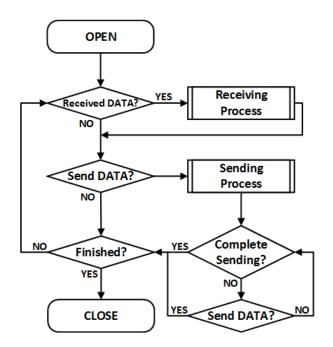

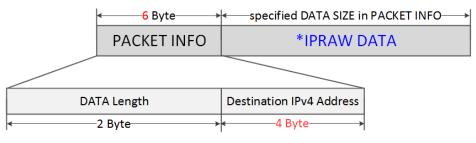

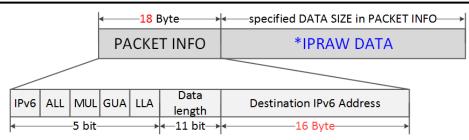

| 6.             | .4               | IPRAW                                            |  |  |  |

|                |                  | 6.4.1 Other Functions 114                        |  |  |  |

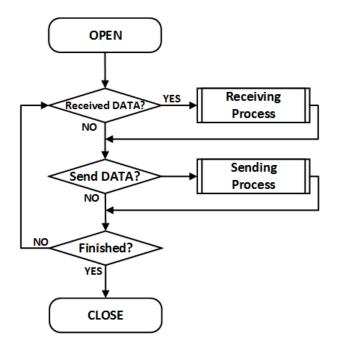

| 6.             | .5               | MACRAW                                           |  |  |  |

| 6.             | .6               | SOCKET-less Command (SLCR) 117                   |  |  |  |

|                |                  | 6.6.1 ARP117                                     |  |  |  |

|                |                  | 6.6.2 PING                                       |  |  |  |

|                |                  | 6.6.3 ARP6 (ND, Neighbor Discovery) 121          |  |  |  |

|                |                  | 6.6.4 PING6 (ICMPv6 Echo) 122                    |  |  |  |

|                |                  | 6.6.5 DAD (Duplicate Address Detection) 124      |  |  |  |

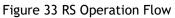

|                |                  | 6.6.6 RS (Router Solicitation) 126               |  |  |  |

|                |                  | 6.6.7 Unsolicited NA(Neighbor Advertisement) 128 |  |  |  |

| 6.             | .7               | Retransmission                                   |  |  |  |

|                |                  | 6.7.1 ARP & PING & ND Retransmission 130         |  |  |  |

|                |                  | 6.7.2 TCP Retransmission                         |  |  |  |

| 6.             | .8               | Others Functions 132                             |  |  |  |

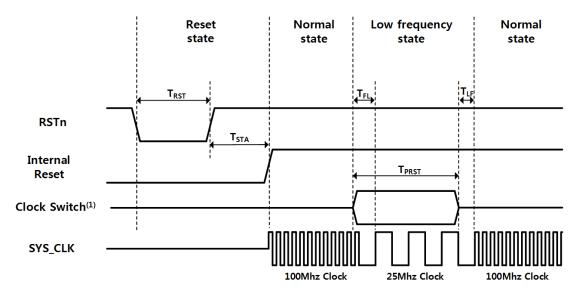

|                |                  | 6.8.1 System Clock(SYS_CLK) Switching            |  |  |  |

|                |                  | 6.8.2 Ethernet PHY Operation Mode Configuration  |  |  |  |

|                |                  | 6.8.3 Ethernet PHY Parallel Detection            |  |  |  |

|                |                  | 6.8.4 Ethernet PHY Auto MDIX 133                 |  |  |  |

|                |                  | 6.8.5 Ethernet PHY Power Down Mode 133           |  |  |  |

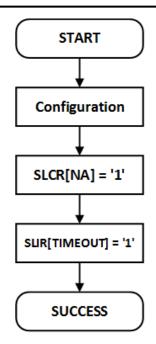

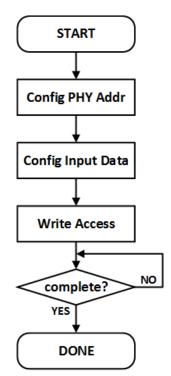

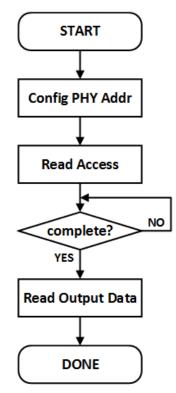

|                |                  | 6.8.6 Ethernet PHY's Registers Control           |  |  |  |

|                |                  | 6.8.7 Ethernet PHY 10BASE-Te Mode 137            |  |  |  |

| 7. C           | loc              | k & Transformer Requirements138                  |  |  |  |

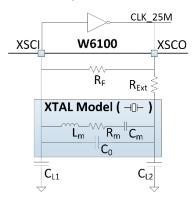

| 7.             | .1               | Quartz Crystal Requirements                      |  |  |  |

| 7.             | .2               | Oscillator requirements                          |  |  |  |

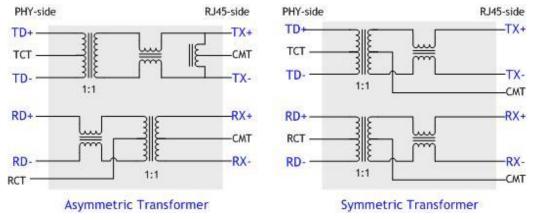

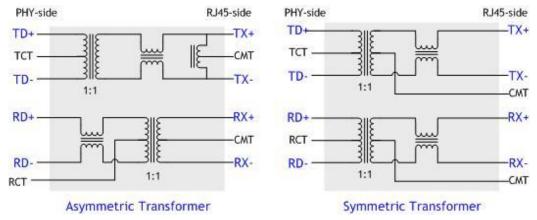

| 7.             | .3               | Transformer Characteristics                      |  |  |  |

| 8. Electrical Specification140 |                                                   |  |  |  |  |  |

|--------------------------------|---------------------------------------------------|--|--|--|--|--|

| 8.1                            | 8.1 Absolute Maximum ratings 140                  |  |  |  |  |  |

| 8.2                            | Absolute Maximum ratings (Electrical Sensitivity) |  |  |  |  |  |

| 8.3                            | DC Characteristics 141                            |  |  |  |  |  |

| 8.4                            | AC Characteristics 142                            |  |  |  |  |  |

|                                | 8.4.1 Reset Timing 142                            |  |  |  |  |  |

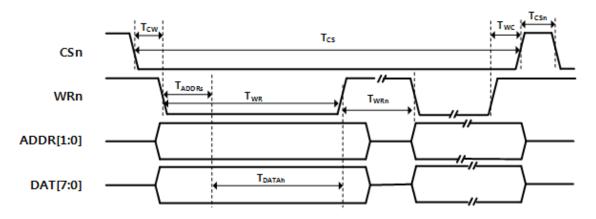

|                                | 8.4.2 BUS ACCESS TIMING                           |  |  |  |  |  |

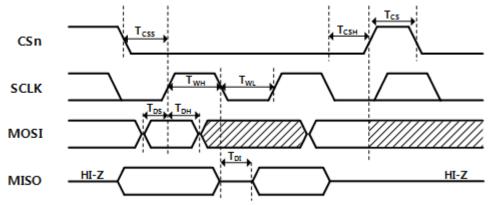

|                                | 8.4.3 SPI ACCESS TIMING                           |  |  |  |  |  |

|                                | 8.4.4 Transformer Characteristics 145             |  |  |  |  |  |

|                                | 8.4.5 MDIX                                        |  |  |  |  |  |

| 8.5                            | POWER DISSIPATION                                 |  |  |  |  |  |

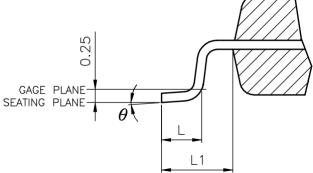

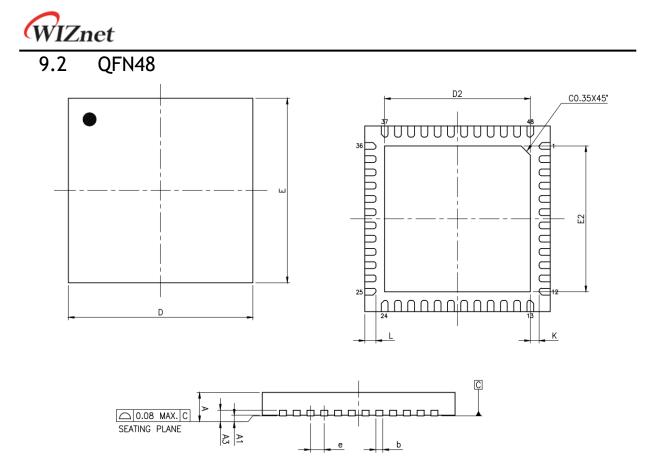

| 9. Pac                         | 9. Package Information                            |  |  |  |  |  |

| 9.1                            | LQFP48                                            |  |  |  |  |  |

| 9.2                            | QFN48                                             |  |  |  |  |  |

| 10.                            | 10. Document Revision History149                  |  |  |  |  |  |

## List of Figures

| Figure 1 Block Diagram                                              |

|---------------------------------------------------------------------|

| Figure 2 W6100 Pin Layout 12                                        |

| Figure 3 W6100 Memory Map 17                                        |

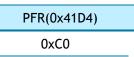

| Figure 4 State Diagram                                              |

| Figure 5 Variable Length Data Mode (CSn controlled by HOST)         |

| Figure 6 Fixed Length Data Mode (CSn is always connected by Ground) |

| Figure 7 SPI Mode 0 & Mode 3 73                                     |

| Figure 8 SPI Frame Format                                           |

| Figure 9 Write SPI Frame in VDM                                     |

| Figure 10 Read SPI Frame in VDM77                                   |

| Figure 11 1 byte Data Write Access SPI Frame in FDM                 |

| Figure 12 2 bytes Data Write Access SPI Frame in FDM                |

| Figure 13 4 bytes Data Write Access SPI Frame in FDM                |

| Figure 14 1byte Data Read Access SPI Frame in FDM                   |

| Figure 15 2 bytes Data Read Access SPI Frame in FDM                 |

| Figure 16 4 bytes Data Read Access SPI Frame in FDM                 |

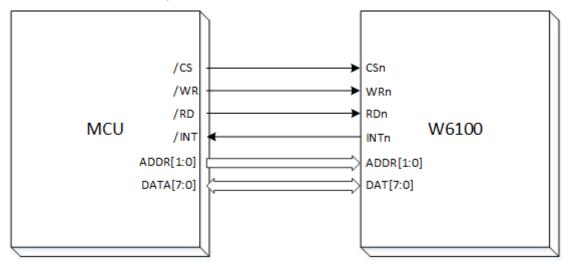

| Figure 17 HOST Interface in Parallel BUS Mode                       |

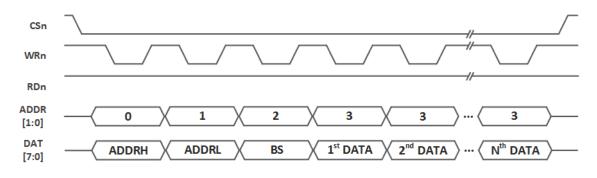

| Figure 18 Parallel BUS N-Bytes Data Write Access                    |

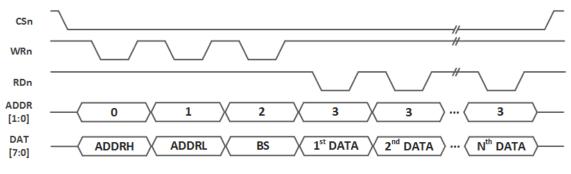

| Figure 19 Parallel Mode Continuous Read Access                      |

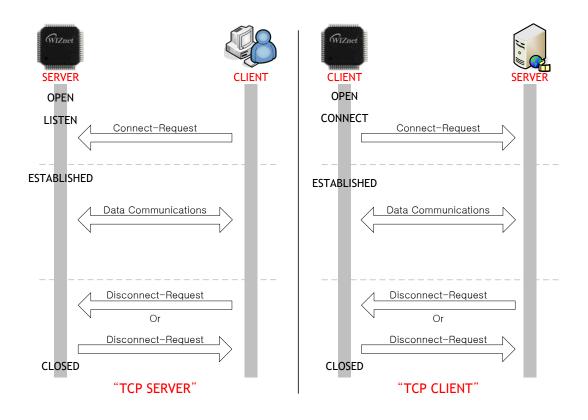

| Figure 20 TCP SERVER and TCP CLIENT                                 |

| Figure 21 TCP SERVER Operation Flow 86                              |

| Figure 22 TCP CLIENT Operation Flow                                 |

| Figure 23 UDP Operation Flow                                        |

| Figure 24 Received DATA in UDP Mode SOCKET RX Buffer Block          |

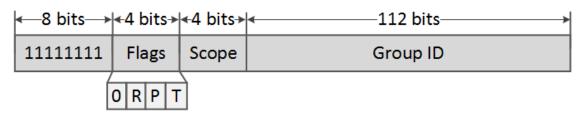

| Figure 25 IPv6 Multicast-Group Address Format104                    |

| Figure 26 IPRAW Operation Flow110                                   |

| Figure 27 Received DATA in IPRAW4 Mode SOCKET RX Buffer Block111    |

| Figure 28 Received DATA in IPRAW6 Mode SOCKET RX Buffer Block112    |

| Figure 29 MACRAW Operation Flow115                                  |

| Figure 30 Received DATA Format in MACRAW116                         |

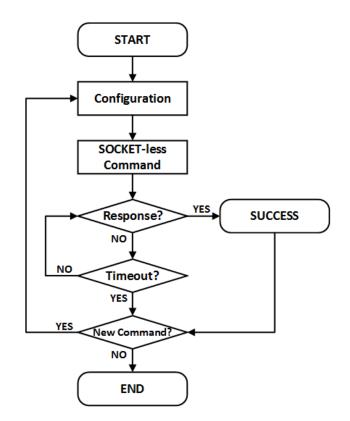

| Figure 31 SOCKET-less Command Operation Flow117                     |

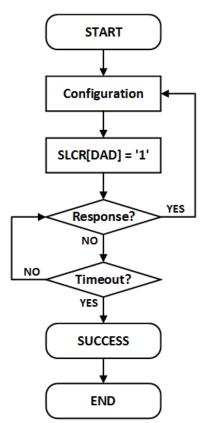

| Figure 32 DAD Operation Flow124                                     |

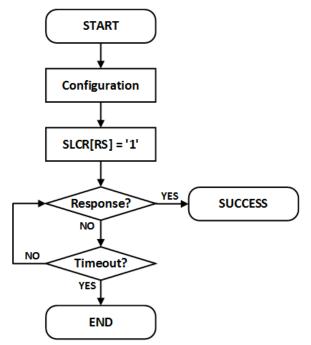

| Figure 33 RS Operation Flow                                         |

| Figure 34 Unsolicited NA Operation Flow129                          |

| Figure 35 MDC/MDIO Write Control Flow135                            |

| Figure 36 MDC/MDIO Read Control Flow136                             |

| Figure 37 Quartz Crystal Model138                                   |

| Figure 38 Transformer Type  | . 139 |

|-----------------------------|-------|

| Figure 39 Reset Timing      | . 142 |

| Figure 40 BUS Read Timing   | . 143 |

| Figure 41 BUS Write Timing  | . 143 |

| Figure 42 SPI Access Timing | . 144 |

| Figure 43 Transformer Type  | . 145 |

## List of Tables

| Table 1 Pin Type Notation    12                                   |

|-------------------------------------------------------------------|

| Table 2 PIN Description                                           |

| Table 3 Parallel Mode Address Value         80                    |

| Table 4 Parameter Description in PACKET INFO         99           |

| Table 5 Parameters of Flags in IPv6 Multicast Address         104 |

| Table 6 Definition of Scope in IPv6 Multicast Address         104 |

| Table 7 Internet Protocol supported in IPRAW Mode                 |

| Table 8 parameters of 'PACKET INFO' in IPRAW4 Mode                |

| Table 9 parameters of 'PACKET INFO' in IPRAW6 Mode                |

| Table 10 Quartz Crystal    138                                    |

| Table 11 Crystal Recommendation Characteristics         138       |

| Table 12 Oscillator Characteristics         139                   |

| Table 13 Transformer Characteristics         139                  |

| Table 14 Absolute Maximum ratings         140                     |

| Table 15 Electro Static Discharge (ESD)         140               |

| Table 16 Latch up Test    140                                     |

| Table 17 DC Characteristics    141                                |

| Table 18 Reset Table   142                                        |

| Table 19 BUS Read Timing    143                                   |

| Table 20 BUS Write timing    144                                  |

| Table 21 SPI Access Timing    144                                 |

| Table 22 Transformer Characteristics         145                  |

| Table 23 Power Dissipation    145                                 |

| Table 24 LQFP48 VARIATIONS (ALL DEMINSIONS SHOWN IN MM)146        |

| Table 25 QFN48 VARIATIONS (ALL DEMINSIONS SHOWN IN MM)148         |

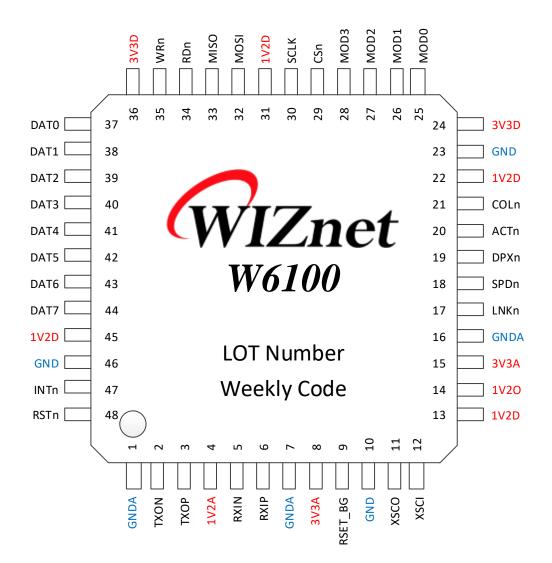

### 1. PIN Description

Figure 2 W6100 Pin Layout

#### Table 1 Pin Type Notation

| Туре                               | Description                          |  |  |  |

|------------------------------------|--------------------------------------|--|--|--|

| I                                  | Input                                |  |  |  |

| 0                                  | O Output                             |  |  |  |

| Μ                                  | Alternate (Multi-function) Signal    |  |  |  |

| U Internal pulled-up 75KΩ resistor |                                      |  |  |  |

| D                                  | D Internal pulled-down 75KΩ resistor |  |  |  |

| А                                  | A Analog                             |  |  |  |

| P Power & Ground                   |                                      |  |  |  |

## 1.1 PIN Description

| Table 2 PIN Description |         |      |                                                              |

|-------------------------|---------|------|--------------------------------------------------------------|

| PIN #                   | Symbol  | Туре | Description                                                  |

| 1                       | GNDA    | AP   | Analog Ground                                                |

| 2                       | TXON    | AO   | Differential Transmitted Signal Pair                         |

|                         |         |      | Data is transmitted to Media in TXOP/TXON differential       |

| 3                       | TXOP    | AO   | signal pair on MDI Mode.                                     |

|                         |         |      | Analog 1.2V Power                                            |

| 4                       | 1V2A    | AP   | 1V2O(PIN14) voltage source must be supplied back to this     |

|                         |         |      | pin.                                                         |

| 5                       | RXIN    | AI   | Differential Received Signal Pair                            |

|                         | D)//D   |      | Data is received from Media in RXIP/RXIN differential signal |

| 6                       | RXIP    | Al   | pair on MDI Mode.                                            |

| 7                       | GNDA    | AP   | Analog Ground                                                |

| 8                       | 3V3A    | AP   | Analog 3.3V Power                                            |

|                         |         |      | Off-chip Bias Resistor                                       |

| 9                       | RSET_BG | AO   | Must be connected to Analog Ground through external          |

|                         |         |      | 12.3K $\Omega$ , tolerance rate 1% Resistance.               |

| 10                      | GND     | AP   | Digital Ground                                               |

|                         |         |      | 25MHz Clock                                                  |

|                         |         |      | Connect 25MHz Crystal Oscillator (XTAL) or Oscillator        |

| 11                      | xsco    | AO   | (OSC) for internal operation clock (SYS_CLK).                |

|                         |         |      | W6100 can convert it to 25MHz or 100MHz and uses the         |

|                         |         |      | converted clock as SYS_CLK.                                  |

|                         |         |      | In normal mode, SYS_CLK is 100MHz.                           |

|                         |         |      | In low frequency mode, SYS_CLK is 25MHz                      |

|                         |         |      |                                                              |

| 12                      | XSCI    | AI   | * CAUTION If OSC is used, 25MHz@1.2V must be used and only   |

|                         |         |      | XSCI must be connected and XSCO must be floated.             |

|                         |         |      |                                                              |

|                         |         |      | ref) " <u>Clock Selection Guide</u> ", same as W5100S        |

| 10                      | 1\/2D   | Р    | Digital 1.2V Power                                           |

| 13                      | 1V2D    | Р    | 1V2O voltage source must be supplied to this pin.            |

|                         |         |      | Internal Regulator 1.2V Power Output                         |

| 14                      | 1V2O    | PO   | Power which Internal Regulator of W6100 supplies. It         |

|                         |         |      | supports Max 150mA.                                          |

|                         |         |      |                                                              |

|   |    |       |    | Make sure to supply it to 1V2D and 1V2A through External    |

|---|----|-------|----|-------------------------------------------------------------|

|   |    |       |    | Capacitor 3.3uF for stabilization.                          |

|   |    |       |    | When 1V2O is supplied, 1V2D and 1V2A must be separated      |

|   |    |       |    | through Ferrite Bead.                                       |

|   |    |       |    |                                                             |

|   |    |       |    | * CAUTION This power is only for W6100. It must not be used |

| _ |    |       |    | for others device.                                          |

| _ | 15 | 3V3A  | AP | Analog 3.3V Power                                           |

| _ | 16 | GNDA  | AP | Analog Ground                                               |

|   |    |       |    | Link Status LED                                             |

|   |    |       |    | It is valid in case of SPI and Parallel BUS Mode.           |

|   | 17 | LNKn  | OU |                                                             |

|   |    |       |    | Low: Link up                                                |

| _ |    |       |    | High: Link down                                             |

|   |    |       |    | Link Speed LED                                              |

|   |    |       |    | It is valid in case of SPI and Parallel BUS Mode.           |

|   | 18 | SPDn  | OU |                                                             |

|   |    |       |    | Low: 100Mbps                                                |

| _ |    |       |    | High: 10Mbps                                                |

|   |    |       |    | Link Duplex LED                                             |

|   |    |       |    | It is valid in case of SPI and Parallel BUS Mode.           |

|   | 19 | DPXn  | OU |                                                             |

|   |    |       |    | Low: Full-Duplex                                            |

| _ |    |       |    | High: Half-Duplex                                           |

|   |    |       |    | Link Activity LED                                           |

|   |    |       |    | It is valid in case of SPI and Parallel BUS Mode.           |

|   | 20 | ACTn  | OU |                                                             |

|   | 20 | ACTI  | 00 | Low: Link up state without TX/RX                            |

|   |    |       |    | Blinking: Link up state with TX/RX data                     |

|   |    |       |    | High: Link-down state                                       |

|   |    |       |    | Link Collision Detect LED                                   |

|   |    |       |    | It is valid in case of SPI and Parallel BUS Mode.           |

|   | 21 | COLn  | OU | It indicates a collision during Data transmission.          |

|   | 21 | COLII | 00 |                                                             |

|   |    |       |    | Low: Collision Detected                                     |

|   |    |       |    | High: No Collision                                          |

| _ | 22 | 1\/2D | П  | Digital 1.2V Power                                          |

| _ | 22 | 1V2D  | Р  | 1V2O voltage source must be supplied to.                    |

|   | 23 | GND   | Р  | Digital Ground                                              |

| _ |    |       |    |                                                             |

| 24  | 3V3D            | Р    | Digital 3.3V power                                      |

|-----|-----------------|------|---------------------------------------------------------|

| 25  | MOD[0]          | ID   | W6100 Mode Selection                                    |

| 26  | MOD[1]          | ID   | Interface Mode is selected by MOD [3:0].                |

|     |                 |      | "000X":SPI Mode                                         |

| 27  | MOD[2]          | ID   | "010X" : Parallel BUS Mode                              |

| 28  | MOD[3]          | ID   | Others : Reserved                                       |

|     |                 |      | W6100 Chip Select                                       |

| 29  | CSn             | IU   | Low: Select                                             |

|     |                 |      | High: No Select                                         |

|     |                 |      | SPI Clock                                               |

| 30  | SCLK            | ID   | On SPI Mode, SPI Clock should be supplied.              |

|     |                 |      | However, on Parallel BUS Mode, it must be connected to  |

|     |                 |      | GND or be floated.                                      |

| 31  | 1V2D            | Р    | Digital 1.2V Power                                      |

| ••• |                 |      | 1V2O voltage source must be supplied.                   |

|     | MOSI            |      | SPI Master Output Slave Input / Address 0               |

| 32  | /ADDR0          | IDM  | On SPI Mode, it operates as MOSI.                       |

|     |                 |      | On Parallel BUS Mode, it is used as Address 0.          |

|     | MISO<br>/ ADDR1 | IOPM | SPI Master Input Slave Output / Address 1               |

| 33  |                 |      | On SPI Mode, it operates as MISO.                       |

|     |                 |      | On Parallel BUS Mode, It is used to Address 1           |

|     |                 |      | Read Strobe                                             |

| 34  | RDn             | IU   | On Parallel BUS Mode, it indicates Read Operation       |

|     |                 |      | On SPI Mode, it must be connected to 3V3D or be floated |

|     |                 |      | Write Strobe                                            |

| 35  | WRn             | IU   | On Parallel BUS Mode, it indicates Write Operation.     |

|     |                 |      | On SPI Mode, it must be connected to 3V3D or be floated |

| 36  | 3V3D            | Р    | Digital 3.3V Power                                      |

| 37  | DAT0            | IOU  | 8 Bits Data BUS                                         |

| 38  | DAT1            | IOU  |                                                         |

| 39  | DAT2            | IOU  | On Parallel BUS Mode, Data is carried over DAT [7:0]    |

| 40  | DAT3            | IOU  | between HOST and W6100.                                 |

| 41  | DAT4            | IOU  | On SPI Mode, DAT [7:0] must be floated.                 |

| 42  | DAT5            | IOU  |                                                         |

| 43  | DAT6            | IOU  |                                                         |

| 44  | DAT7            | IOU  |                                                         |

| 45  | 1V2D            | Р    | Digital 1.2V Power                                      |

| 46  | GND             | Р    | Digital Ground                                          |

| 47  | INTn            | OP   | Interrupt                                               |

|    |      |    | When the event occurs during Ethernet communication,<br>INTn is triggered.<br>Lo : Interrupt Occurred<br>High: No Interrupt                                                                       |

|----|------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |      |    | ref) IEN(Interrupt Enable) in SYCR1(System Config Register1) ,<br>INTPTMR(Interrupt Pending Time Register), IR(Interrupt                                                                          |

|    |      |    | Register), SIR(SOCKET Interrupt Register), SLIR(SOCKET-less<br>Interrupt Register)                                                                                                                |

| 48 | RSTn | IP | Reset<br>RSTn initializes W6100. RSTn must be asserted to Low for<br>longer than 1.0us. After asserted RSTn, W5100S spends<br>60.3ms for initialization.<br><i>ref)</i> 8.4.1 <i>Reset Timing</i> |

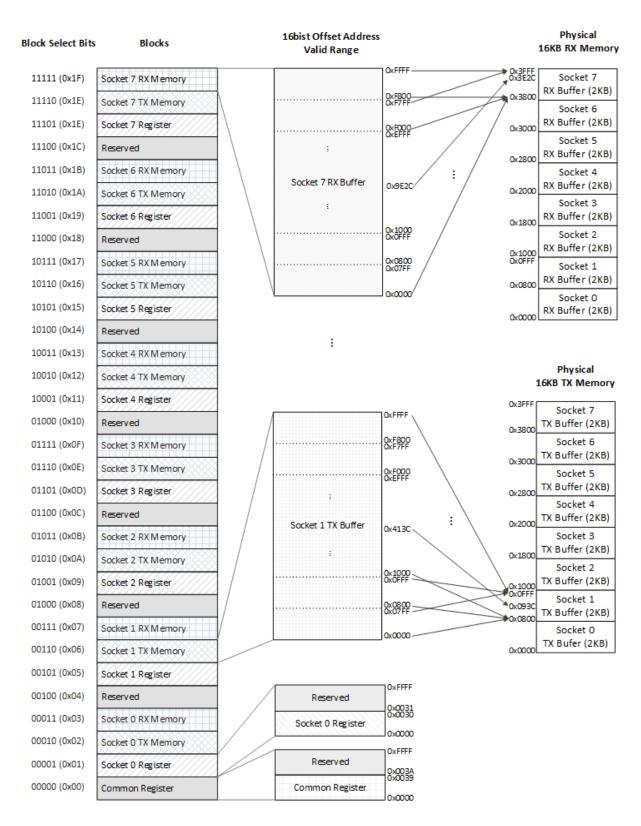

### 2. Memory Map

Figure 3 W6100 Memory Map

In Figure 3, W6100 consists the below blocks.

- 1 x Common Register Block, 7 x Reserved Block

- 8 x SOCKET n Register Block

- 8 x SOCKET n TX Buffer Block

- 8 x SOCKET n RX Buffer Block

These blocks are classified by block select 5bits. Each block is accessed with 16 bits offset address.

SOCKET n TX Buffer Blocks ( $0 \le n \le 7$ ) are initially allocated to 2KB each in 16KB TX memory. And each Block can be reallocated to 0, 1, 2, 4, 8, or 16KB through Sn\_TX\_BSR(4.2.23). The total allocated size of SOCKET n TX Buffer Blocks must not exceed 16KB.

SOCKET n RX Buffer Blocks ( $0 \le n \le 7$ ) are also initially allocated to 2KB each in 16KB RX memory. And each SOCKET n RX Buffer Block is reallocated in 0, 1, 2, 4, 8 or 16KB through Sn\_RX\_BSR(4.2.27). The total Size of allocated SOCKET n RX Buffer Block must not exceed 16KB.

### 3. W6100 Registers

### 3.1 Common Register

| Offset | Register                                                | Type <sup>1</sup> | Reset |

|--------|---------------------------------------------------------|-------------------|-------|

| 0x0000 | CIDR0 (Chip Identification Register)                    | RO                | 0x61  |

| 0x0001 | CIDR1                                                   | RO                | 0x00  |

| 0x0002 | VER0 (Chip Version Register)                            | RO                | 0x46  |

| 0x0003 | VER1                                                    | RO                | 0x61  |

| 0x2000 | SYSR (System Status Register)                           | RO                | 0xEU  |

| 0x2004 | SYCR0 (System Config Register 0)                        | WO                | 0x80  |

| 0x2005 | SYCR1                                                   | R=W               | 0x80  |

| 0x2016 | TCNTR0 (Tick Counter Register)                          | RO                | 0x00  |

| 0x2017 | TCNTR1                                                  | RO                | 0x00  |

| 0x2020 | TCNTCLR (TCNTR Clear Register)                          | WO                | 0x00  |

| 0x2100 | IR (Interrupt Register)                                 | RO                | 0x00  |

| 0x2101 | SIR (SOCKET Interrupt Register)                         | RO                | 0x00  |

| 0x2102 | SLIR (SOCKET-less Interrupt Register)                   | RO                | 0x00  |

| 0x2104 | IMR (Interrupt Mask Register)                           | R=W               | 0x00  |

| 0x2108 | IRCLR (IR Clear Register)                               | WO                | 0x00  |

| 0x2114 | SIMR (SOCKET Interrupt Mask Register)                   | R=W               | 0x00  |

| 0x2124 | SLIMR (SOCKET-less Interrupt Mask Register)             | R=W               | 0x00  |

| 0x2128 | SLIRCLR (SLIR Clear Register)                           | WO                | 0x00  |

| 0x212C | SLPSR (SOCKET-less Prefer Source IPv6 Address Register) | R=W               | 0x00  |

| 0x2130 | SLCR (SOCKET-less Command Register)                     | RW,AC             | 0x00  |

| 0x3000 | PHYSR (PHY Status Register)                             | RO                | 0x00  |

| 0x3008 | PHYRAR (PHY Register Address Register)                  | R=W               | 0x00  |

| 0x300C | PHYDIR0 (PHY Data Input Register)                       | R=W               | 0x00  |

| 0x300D | PHYDIR1                                                 | R=W               | 0x00  |

| 0x3010 | PHYDOR0 (PHY Data Output Register)                      | RO                | 0x00  |

| 0x3011 | PHYDOR1                                                 | RO                | 0x00  |

| 0x3014 | PHYACR (PHY Access Control Register)                    | RW,AC             | 0x00  |

| 0x3018 | PHYDIVR (PHY Division Register)                         | R=W               | 0x01  |

| 0x301C | PHYCR0 (PHY Control Register 0)                         | WO                | 0x00  |

| 0x301D | PHYCR1                                                  | R=W               | 0x40  |

| 0x4000 | NET4MR (Network IPv4 Mode Register)                     | R=W               | 0x00  |

<sup>1</sup> r*ef*) 4. *Register Descriptions*

W6100 - Hardwired Dual TCP/IP Stack Controller

| 0x4004 | NET6MR (Network IPv6 Mode Register)                     | R=W | 0x00 |

|--------|---------------------------------------------------------|-----|------|

| 0x4008 | NETMR (Network Mode Register)                           | R=W | 0x00 |

| 0x4009 | NETMR2 (Network Mode Register 2)                        | R=W | 0x00 |

| 0x4100 | PTMR (PPP Link Control Protocol Request Timer Register) | R=W | 0x28 |

| 0x4104 | PMNR (PPP Link Control Protocol Magic number Register)  | R=W | 0x00 |

| 0x4108 | PHAR0 (PPPoE Hardware Address Register on PPPoE)        | R=W | 0x00 |

| 0x4109 | PHAR1                                                   | R=W | 0x00 |

| 0x410A | PHAR2                                                   | R=W | 0x00 |

| 0x410B | PHAR3                                                   | R=W | 0x00 |

| 0x410C | PHAR4                                                   | R=W | 0x00 |

| 0x410D | PHAR5                                                   | R=W | 0x00 |

| 0x4110 | PSIDR0 (PPPoE Session ID Register)                      | R=W | 0x00 |

| 0x4111 | PSIDR1                                                  | R=W | 0x00 |

| 0x4114 | PMRUR0 (PPPoE Maximum Receive Unit Register)            | R=W | 0xFF |

| 0x4115 | PMRUR1                                                  | R=W | 0xFF |

| 0x4120 | SHAR0 (Source Hardware Address Register)                | R=W | 0x00 |

| 0x4121 | SHAR1                                                   | R=W | 0x00 |

| 0x4122 | SHAR2                                                   | R=W | 0x00 |

| 0x4123 | SHAR3                                                   | R=W | 0x00 |

| 0x4124 | SHAR4                                                   | R=W | 0x00 |

| 0x4125 | SHAR5                                                   | R=W | 0x00 |

| 0x4130 | GAR0 (Gateway IP Address Register)                      | R=W | 0x00 |

| 0x4131 | GAR1                                                    | R=W | 0x00 |

| 0x4132 | GAR2                                                    | R=W | 0x00 |

| 0x4133 | GAR3                                                    | R=W | 0x00 |

| 0x4134 | SUBRO (Subnet Mask Register)                            | R=W | 0x00 |

| 0x4135 | SUBR1                                                   | R=W | 0x00 |

| 0x4136 | SUBR2                                                   | R=W | 0x00 |

| 0x4137 | SUBR3                                                   | R=W | 0x00 |

| 0x4138 | SIPR0 (IPv4 Source Address Register)                    | R=W | 0x00 |

| 0x4139 | SIPR1                                                   | R=W | 0x00 |

| 0x413A | SIPR2                                                   | R=W | 0x00 |

| 0x413B | SIPR3                                                   | R=W | 0x00 |

| 0x4140 | LLAR0 (Link Local Address Register)                     | R=W | 0x00 |

| 0x4141 | LLAR1                                                   | R=W | 0x00 |

| 0x4142 | LLAR2                                                   | R=W | 0x00 |

| 0x4143 | LLAR3                                                   | R=W | 0x00 |

| 0x4144 | LLAR4                                                   | R=W | 0x00 |

|        | -                                       |     |      |

|--------|-----------------------------------------|-----|------|

| 0x4145 | LLAR5                                   | R=W | 0x00 |

| 0x4146 | LLAR6                                   | R=W | 0x00 |

| 0x4147 | LLAR7                                   | R=W | 0x00 |

| 0x4148 | LLAR8                                   | R=W | 0x00 |

| 0x4149 | LLAR9                                   | R=W | 0x00 |

| 0x414A | LLAR10                                  | R=W | 0x00 |

| 0x414B | LLAR11                                  | R=W | 0x00 |

| 0x414C | LLAR12                                  | R=W | 0x00 |

| 0x414D | LLAR13                                  | R=W | 0x00 |

| 0x414E | LLAR14                                  | R=W | 0x00 |

| 0x414F | LLAR15                                  | R=W | 0x00 |

| 0x4150 | GUAR0 (Global Unicast Address Register) | R=W | 0x00 |

| 0x4151 | GUAR1                                   | R=W | 0x00 |

| 0x4152 | GUAR2                                   | R=W | 0x00 |

| 0x4153 | GUAR3                                   | R=W | 0x00 |

| 0x4154 | GUAR4                                   | R=W | 0x00 |

| 0x4155 | GUAR5                                   | R=W | 0x00 |

| 0x4156 | GUAR6                                   | R=W | 0x00 |

| 0x4157 | GUAR7                                   | R=W | 0x00 |

| 0x4158 | GUAR8                                   | R=W | 0x00 |

| 0x4159 | GUAR9                                   | R=W | 0x00 |

| 0x415A | GUAR10                                  | R=W | 0x00 |

| 0x415B | GUAR11                                  | R=W | 0x00 |

| 0x415C | GUAR12                                  | R=W | 0x00 |

| 0x415D | GUAR13                                  | R=W | 0x00 |

| 0x415E | GUAR14                                  | R=W | 0x00 |

| 0x415F | GUAR15                                  | R=W | 0x00 |

| 0x4160 | SUB6R0 (IPv6 Subnet Prefix Register)    | R=W | 0x00 |

| 0x4161 | SUB6R1                                  | R=W | 0x00 |

| 0x4162 | SUB6R2                                  | R=W | 0x00 |

| 0x4163 | SUB6R3                                  | R=W | 0x00 |

| 0x4164 | SUB6R4                                  | R=W | 0x00 |

| 0x4165 | SUB6R5                                  | R=W | 0x00 |

| 0x4166 | SUB6R6                                  | R=W | 0x00 |

| 0x4167 | SUB6R7                                  | R=W | 0x00 |

| 0x4168 | SUB6R8                                  | R=W | 0x00 |

| 0x4169 | SUB6R9                                  | R=W | 0x00 |

| 0x416A | SUB6R10                                 | R=W | 0x00 |

| 0x416B | SUB6R11                                                | R=W | 0x00 |

|--------|--------------------------------------------------------|-----|------|

| 0x416C | SUB6R12                                                | R=W | 0x00 |

| 0x416D | SUB6R13                                                | R=W | 0x00 |

| 0x416E | SUB6R14                                                | R=W | 0x00 |

| 0x416F | SUB6R15                                                | R=W | 0x00 |

| 0x4170 | GA6R0 (IPv6 Gateway Address Register)                  | R=W | 0x00 |

| 0x4171 | GA6R1                                                  | R=W | 0x00 |

| 0x4172 | GA6R2                                                  | R=W | 0x00 |

| 0x4173 | GA6R3                                                  | R=W | 0x00 |

| 0x4174 | GA6R4                                                  | R=W | 0x00 |

| 0x4175 | GA6R5                                                  | R=W | 0x00 |

| 0x4176 | GA6R6                                                  | R=W | 0x00 |

| 0x4177 | GA6R7                                                  | R=W | 0x00 |

| 0x4178 | GA6R8                                                  | R=W | 0x00 |

| 0x4179 | GA6R9                                                  | R=W | 0x00 |

| 0x417A | GA6R10                                                 | R=W | 0x00 |

| 0x417B | GA6R11                                                 | R=W | 0x00 |

| 0x417C | GA6R12                                                 | R=W | 0x00 |

| 0x417D | GA6R13                                                 | R=W | 0x00 |

| 0x417E | GA6R14                                                 | R=W | 0x00 |

| 0x417F | GA6R15                                                 | R=W | 0x00 |

| 0x4180 | SLDIP6R0 (SOCKET-less Destination IP Address Register) | R=W | 0x00 |

| 0x4181 | SLDIP6R1                                               | R=W | 0x00 |

| 0x4182 | SLDIP6R2                                               | R=W | 0x00 |

| 0x4183 | SLDIP6R3                                               | R=W | 0x00 |

| 0x4184 | SLDIP6R4                                               | R=W | 0x00 |

| 0x4185 | SLDIP6R5                                               | R=W | 0x00 |

| 0x4186 | SLDIP6R6                                               | R=W | 0x00 |

| 0x4187 | SLDIP6R7                                               | R=W | 0x00 |

| 0x4188 | SLDIP6R8                                               | R=W | 0x00 |

| 0x4189 | SLDIP6R9                                               | R=W | 0x00 |

| 0x418A | SLDIP6R10                                              | R=W | 0x00 |

| 0x418B | SLDIP6R11                                              | R=W | 0x00 |

| 0x418C | SLDIP6R12                                              | R=W | 0x00 |

| 0x418D | SLDIP6R13                                              | R=W | 0x00 |

| 0x418E | SLDIP6R14                                              | R=W | 0x00 |

| 0x418F | SLDIP6R15                                              | R=W | 0x00 |

| 0x4190 | SLDHARO (SOCKET-less Destination Hardware Address Register) | RO  | 0x00         |

|--------|-------------------------------------------------------------|-----|--------------|

| 0x4191 | SLDHAR1                                                     | RO  | 0x00         |

| 0x4192 | SLDHAR2                                                     | RO  | 0x00         |

| 0x4192 | SLDHAR3                                                     | RO  | 0x00         |

| 0x4194 | SLDHAR4                                                     | RO  | 0x00         |

| 0x4195 | SLDHAR5                                                     | RO  | 0x00         |

| 0x4198 | PINGIDRO (PING ID Register)                                 | R=W | 0x00         |

| 0x4199 | PINGIDR1                                                    | R=W | 0x00         |

| 0x419C | PINGSEQR0 (PING Sequence-number Register)                   | R=W | 0x00         |

| 0x419D | PINGSEQR1                                                   | R=W | 0x00         |

| 0x41A0 | UIPRO (Unreachable IP Address Register)                     | RO  | 0x00         |

| 0x41A1 | UIPR1                                                       | RO  | 0x00         |

| 0x41A1 | UIPR2                                                       | RO  | 0x00         |

| 0x41A2 | UIPR3                                                       | RO  | 0x00         |

| 0x41A3 | UPORTRO (Unreachable Port Register)                         | RO  | 0x00         |

| 0x41A4 | UPORTR1                                                     | RO  | 0x00         |

| 0x41A3 | UIP6R0 (Unreachable IPv6 Address Register)                  | RO  | 0x00         |

| 0x41B0 | UIP6R1                                                      | RO  | 0x00         |

| 0x41B1 | UIP6R2                                                      | RO  | 0x00         |

| 0x41B2 | UIP6R3                                                      |     | 0x00         |

| 0x41B3 |                                                             | RO  |              |

| 0x41B4 | UIP6R4<br>UIP6R5                                            |     | 0x00<br>0x00 |

|        |                                                             | RO  |              |

| 0x41B6 | UIP6R6                                                      | RO  | 0x00         |

| 0x41B7 | UIP6R7                                                      | RO  | 0x00         |

| 0x41B8 | UIP6R8                                                      | RO  | 0x00         |

| 0x41B9 | UIP6R9                                                      | RO  | 0x00         |

| Ox41BA | UIP6R10                                                     | RO  | 0x00         |

| 0x41BB | UIP6R11                                                     | RO  | 0x00         |

| 0x41BC | UIP6R12                                                     | RO  | 0x00         |

| 0x41BD | UIP6R13                                                     | RO  | 0x00         |

| 0x41BE | UIP6R14                                                     | RO  | 0x00         |

| 0x41BF | UIP6R15                                                     | RO  | 0x00         |

| 0x41C0 | UPORT6R0 (Unreachable IPv6 Port Register)                   | RO  | 0x00         |

| 0x41C1 | UPORT6R1                                                    | RO  | 0x00         |

| 0x41C5 | INTPTMR0 (Interrupt Pending Time Register)                  | R=W | 0x00         |

| 0x41C6 | INTPTMR1                                                    | R=W | 0x00         |

| 0x41D0 | PLR (Prefix Length Register)                                | RO  | 0x00         |

|        | -                                                 |     |      |

|--------|---------------------------------------------------|-----|------|

| 0x41D4 | PFR (Prefix Flag Register)                        | RO  | 0x00 |

| 0x41D8 | VLTR0 (Valid Life Time Register)                  | RO  | 0x00 |

| 0x41D9 | VLTR1                                             | RO  | 0x00 |

| 0x41DA | VLTR2                                             | RO  | 0x00 |

| 0x41DB | VLTR3                                             | RO  | 0x00 |

| 0x41DC | PLTR0 (Preferred Life Time Register)              | RO  | 0x00 |

| 0x41DD | PLTR1                                             | RO  | 0x00 |

| 0x41DE | PLTR2                                             | RO  | 0x00 |

| 0x41DF | PLTR3                                             | RO  | 0x00 |

| 0x41E0 | PAR0 (Prefix Address Register)                    | RO  | 0x00 |

| 0x41E1 | PAR1                                              | RO  | 0x00 |

| 0x41E2 | PAR2                                              | RO  | 0x00 |

| 0x41E3 | PAR3                                              | RO  | 0x00 |

| 0x41E4 | PAR4                                              | RO  | 0x00 |

| 0x41E5 | PAR5                                              | RO  | 0x00 |

| 0x41E6 | PAR6                                              | RO  | 0x00 |

| 0x41E7 | PAR7                                              | RO  | 0x00 |

| 0x41E8 | PAR8                                              | RO  | 0x00 |

| 0x41E9 | PAR9                                              | RO  | 0x00 |

| 0x41EA | PAR10                                             | RO  | 0x00 |

| 0x41EB | PAR11                                             | RO  | 0x00 |

| 0x41EC | PAR12                                             | RO  | 0x00 |

| 0x41ED | PAR13                                             | RO  | 0x00 |

| 0x41EE | PAR14                                             | RO  | 0x00 |

| 0x41EF | PAR15                                             | RO  | 0x00 |

| 0x41F0 | ICMP6BLKR (ICMPv6 Block Register)                 | R=W | 0x00 |

| 0x41F4 | CHPLCKR (Chip Lock Register)                      | WO  | 0x00 |

| 0x41F5 | NETLCKR (Network Lock Register)                   | WO  | 0x00 |

| 0x41F6 | PHYLCKR (PHY Lock Register)                       | WO  | 0x00 |

| 0x4200 | RTR0 (Retransmission Time Register)               | R=W | 0x07 |

| 0x4201 | RTR1                                              | R=W | 0xD0 |

| 0x4204 | RCR (Retransmission Count Register)               | R=W | 0x08 |

| 0x4208 | SLRTR0 (SOCKET-less Retransmission Time Register) | R=W | 0x07 |

| 0x4209 | SLRTR1                                            | R=W | 0xD0 |

| 0x420C | SLRCR (SOCKET-less Retransmission Count Register) | R=W | 0x00 |

| 0x420F | SLHOPR (Hop limit Register)                       | R=W | 0x80 |

## 3.2 SOCKET Register

| Offset | Register                                                  | Туре  | Reset |

|--------|-----------------------------------------------------------|-------|-------|

| 0x0000 | Sn_MR (SOCKET n Mode Register)                            | R=W   | 0x00  |

| 0x0004 | Sn_PSR (SOCKET n Prefer Source IPv6 Address Register)     | R=W   | 0x00  |

| 0x0010 | Sn_CR (SOCKET n Command Register)                         | RW,AC | 0x00  |

| 0x0020 | Sn_IR (SOCKET n Interrupt Register)                       | WO    | 0x00  |

| 0x0024 | Sn_IMR (SOCKET n Interrupt Mask Register)                 | R=W   | 0xFF  |

| 0x0028 | Sn_IRCLR (Sn_IR Clear Register)                           | WO    | 0xFF  |

| 0x0030 | Sn_SR (SOCKET n Status Register)                          | RO    | 0x00  |

| 0x0031 | Sn_ESR (SOCKET n Extension Status Register)               | RO    | 0x00  |

| 0x0100 | Sn_PNR (SOCKET n IP Protocol Number Register)             | R=W   | 0x00  |

| 0x0104 | Sn_TOSR (SOCKET n IP Type Of Service Register)            | R=W   | 0x00  |

| 0x0108 | Sn_TTLR (SOCKET n IP Time To Live Register)               | R=W   | 0x80  |

| 0x010C | Sn_FRGR0 (SOCKET n Fragment Offset in IP Header Register) | R=W   | 0x40  |

| 0x010D | Sn_FRGR1                                                  | R=W   | 0x00  |

| 0x0110 | Sn_MSSR0 (SOCKET n Maximum Segment Size Register)         | RW    | 0x00  |

| 0x0111 | Sn_MSSR1                                                  | RW    | 0x00  |

| 0x0114 | Sn_PORTR0 (SOCKET n Source Port Register)                 | R=W   | 0x00  |

| 0x0115 | Sn_PORTR1                                                 | R=W   | 0x00  |

| 0x0118 | Sn_DHAR0 (SOCKET n Destination Hardware Address Register) | RW    | 0x00  |

| 0x0119 | Sn_DHAR1                                                  | RW    | 0x00  |

| 0x011A | Sn_DHAR2                                                  | RW    | 0x00  |

| 0x011B | Sn_DHAR3 RW                                               |       | 0x00  |

| 0x011C | Sn_DHAR4                                                  | RW    | 0x00  |

| 0x011D | Sn_DHAR5                                                  | RW    | 0x00  |

| 0x0120 | Sn_DIPR0 (SOCKET n Destination IPv4 Address Register)     | RW    | 0x00  |

| 0x0121 | Sn_DIPR1                                                  | RW    | 0x00  |

| 0x0122 | Sn_DIPR2                                                  | RW    | 0x00  |

| 0x0123 | Sn_DIPR3                                                  | RW    | 0x00  |

| 0x0130 | Sn_DIP6R0 (SOCKET n Destination IPv6 Address Register)    | RW    | 0x00  |

| 0x0131 | Sn_DIP6R1                                                 | RW    | 0x00  |

| 0x0132 | Sn_DIP6R2 RW                                              |       | 0x00  |

| 0x0133 | Sn_DIP6R3                                                 | RW    | 0x00  |

| 0x0134 | Sn_DIP6R4                                                 | RW    | 0x00  |

| 0x0135 | Sn_DIP6R5                                                 | RW    | 0x00  |

| 0x0136 | Sn_DIP6R6                                                 | RW    | 0x00  |

| 0x0137 | Sn_DIP6R7                                                 | RW    | 0x00  |

W6100 - Hardwired Dual TCP/IP Stack Controller

| 0x0138 | Sn_DIP6R8                                       | RW  | 0x00 |

|--------|-------------------------------------------------|-----|------|

| 0x0139 | Sn_DIP6R9                                       | RW  | 0x00 |

| 0x013A | Sn_DIP6R10                                      | RW  | 0x00 |

| 0x013B | Sn_DIP6R11                                      | RW  | 0x00 |

| 0x013C | Sn_DIP6R12                                      | RW  | 0x00 |

| 0x013D | Sn_DIP6R13                                      | RW  | 0x00 |

| 0x013E | Sn_DIP6R14                                      | RW  | 0x00 |

| 0x013F | Sn_DIP6R15                                      | RW  | 0x00 |

| 0x0140 | Sn_DPORTR0 (SOCKET n Destination Port Register) | RW  | 0x00 |

| 0x0141 | Sn_DPORTR1                                      | RW  | 0x00 |

| 0x0144 | Sn_MR2 (SOCKET n Mode Register 2)               | R=W | 0x00 |

| 0x0180 | Sn_RTR0 (SOCKET n Retransmission Time Register) | RW  | 0x00 |

| 0x0181 | Sn_RTR1                                         | RW  | 0x00 |

| 0x0184 | Sn_RCR (SOCKET n Retransmission Count Register) | RW  | 0x00 |

| 0x0188 | Sn_KPALVTR (SOCKET n Keep Alive Time Register)  | R=W | 0x00 |

| 0x0200 | Sn_TX_BSR (SOCKET n TX Buffer Size Register)    | R=W | 0x02 |

| 0x0204 | Sn_TX_FSR0 (SOCKET n TX Free Size Register)     | RO  | 0x00 |

| 0x0205 | Sn_TX_FSR1                                      | RO  | 0x00 |

| 0x0208 | Sn_TX_RD0 (SOCKET n TX Read Pointer Register)   | RO  | 0x00 |

| 0x0209 | Sn_TX_RD1                                       | RO  | 0x00 |

| 0x020C | Sn_TX_WR0 (SOCKET n TX Write Pointer Register)  | RW  | 0x00 |

| 0x020D | Sn_TX_WR1                                       | RW  | 0x00 |

| 0x0220 | Sn_RX_BSR (SOCKET n RX Buffer Size Register)    | R=W | 0x02 |

| 0x0224 | Sn_RX_RSR0 (SOCKET n RX Received Size Register) | RO  | 0x00 |

| 0x0225 | Sn_RX_RSR1                                      | RO  | 0x00 |

| 0x0228 | Sn_RX_RD0 (SOCKET n RX Read Pointer Register)   | RW  | 0x00 |

| 0x0229 | Sn_RX_RD1                                       | RW  | 0x00 |

| 0x022C | Sn_RX_WR0 (SOCKET n RX Write Pointer Register)  | RO  | 0x00 |

| 0x022D | Sn_RX_WR1                                       | RO  | 0x00 |

#### 4. Register Descriptions

**Register Notation**

| * Register | * Register Symbol (Register full Name) |             |          |              |            |          |          |

|------------|----------------------------------------|-------------|----------|--------------|------------|----------|----------|

| - [Registe | er Type, Re                            | gister Type | ,][Addre | ss Offset][R | eset Value | ]        |          |

| Register D | escription                             |             |          |              |            |          |          |

| 7          | 6                                      | 5           | 4        | 3            | 2          | 1        | 0        |

| Bit7       | Bit6                                   | Bit5        | Bit4     | Bit3         | Bit2       | Bit1     | Bit0     |

| Bit Type   | Bit Type                               | Bit Type    | Bit Type | Bit Type     | Bit Type   | Bit Type | Bit Type |

|            |                                        |             |          |              |            |          |          |

Ex) Sn\_IR[3:0] denotes Register Symbol[Upper bit : Lower bit].

Sn\_IR[3:0] = "0001" is meaning Sn\_IR[3]='0', Sn\_IR[2]='0', Sn\_IR[1]='0' and Sn\_IR[0]='1'

#### [Register/bit Type]: Type of Register.

- [RW : Register / bit available to Read and Write Both

- [R=W]: Register / bit which written value and the read value are the same.

- [RO]: Read Only Register/bit

- [WO]: Write Only Register/bit

- [W]: Write Only Register/bit

- [WC]: Register/Bit to be clear by writing '1'

- [W0]: Register/Bit which only '0' can be written

- [W1]: Register/bit which only '1' can be written

- [AC]: Auto Clear Register/bit

- [1]: Always read '1'

- [0]: Always read '0'

- [-]: Not available

[Address Offset]: The address offset of the register

[Reset Value]: Default Value.

Ex1) 4.1.28 NETMR (Network Mode Register)

[R=W][0x4008][0x00]

NETMR sets all kinds of block mode and WOL.

| 7 | 6 | 5   | 4   | 3 | 2   | 1    | 0    |

|---|---|-----|-----|---|-----|------|------|

| - | - | ANB | M6B |   | WOL | IP6B | IP4B |

|   |   | R=W | R=W |   | R=W | R=W  | R=W  |

Ex2) NETMR[ANB]

ANB bit of NETMR

#### Ex3) NETMR[7:0]

From 7<sup>th</sup> bit to 0<sup>th</sup> bit of NETMR

#### 4.1 Common Registers

#### 4.1.1 CIDR (Chip Identification Register) [R0][0x0000~0x0001] [0x6100]

CHIP ID is 0x6100 and fixed.

| CIDR0(0x0000) | CIDR1(0x0001) |

|---------------|---------------|

| 0x61          | 0x00          |

#### 4.1.2 VER (Version Register) [R0][0x0002~0x0003] [0x4661]

Version is 0x4661.

| VER0(0x0002) | VER1(0x0003) |  |  |  |

|--------------|--------------|--|--|--|

| 0x46         | 0x61         |  |  |  |

#### 4.1.3 SYSR (System Status Register) [R0][0x2000] [0xEU]

It shows the status of CHIP/NET/PHY configuration lock and HOST interface mode.

| 7    | 6    | 5    | 4 | 3 | 2 | 1   | 0   |

|------|------|------|---|---|---|-----|-----|

| CHPL | NETL | PHYL | - | - | - | IND | SPI |

| RO   | RO   | RO   |   |   |   | RO  | RO  |

| Bit | Symbol | Description |                                                           |             |                                         |  |  |  |

|-----|--------|-------------|-----------------------------------------------------------|-------------|-----------------------------------------|--|--|--|

|     |        | CHIP        | Lock Statı                                                | JS          |                                         |  |  |  |

|     |        | CHIP I      | _ock is set                                               | by CHPLO    | CKR(Chip Configuration Lock Register).  |  |  |  |

| 7   | CHPL   |             |                                                           |             |                                         |  |  |  |

|     |        | 0: Unl      | .ock - poss                                               | ible to se  | t SYCOR & SYC1R                         |  |  |  |

| _   |        | 1: Loc      | :k - unable                                               | e to set SY | COR & SYC1R                             |  |  |  |

|     |        | NET L       | NET Lock Status                                           |             |                                         |  |  |  |

|     |        | NET L       | ock is set                                                | by NETLC    | KR(Network Configuration Lock Register) |  |  |  |

|     |        |             |                                                           |             |                                         |  |  |  |

|     |        | 0: Unl      | ock - poss                                                | ible to se  | t Network Configuration Registers       |  |  |  |

| 6   | NETL   | 1: Loc      | :k - unable                                               | e to set Ne | etwork Configuration Registers          |  |  |  |

|     |        |             |                                                           |             |                                         |  |  |  |

|     |        | ref) N      | ref) Network Configuration Registers to be locked by NETL |             |                                         |  |  |  |

|     |        |             | SHAR Source Hardware Address Register                     |             |                                         |  |  |  |

|     |        |             | 15 44                                                     | GAR         | Gateway IP Address Register             |  |  |  |

|       |      |                           |                           | SUBR        | Subnet Mask Register                                          |    |  |  |

|-------|------|---------------------------|---------------------------|-------------|---------------------------------------------------------------|----|--|--|

|       |      |                           |                           | SIPR        | Source IP Address Register                                    |    |  |  |

|       |      |                           |                           | LLAR        | Link Local Address Register                                   |    |  |  |

|       |      |                           |                           | GUAR        | Global Unicast Address Register                               |    |  |  |

|       |      |                           | IPv6                      | SUB6R       | IPv6 Subnet Prefix Register                                   |    |  |  |

|       |      |                           |                           | GA6R        | IPv6 Gateway IP Address<br>It is excluded from lock mechanism |    |  |  |

|       |      | * CAU                     | TION : GAO                | 6R can be   | set regardless of setting of NETL.                            |    |  |  |

|       |      |                           | PHY Lock Status           |             |                                                               |    |  |  |

|       |      | PHY L                     | ock can be                | e set by P  | HYLCKR(PHY Configuration Lock Register)                       | ). |  |  |

| 5     | PHYL |                           |                           |             |                                                               |    |  |  |

|       |      | 0: Unl                    | ock - poss                | ible to se  | t PHYCOR, PHYC1R                                              |    |  |  |

|       |      | 1: Loc                    | :k - unable               | e to set PH | HY Control Register (PHYC0R, PHYC1R)                          |    |  |  |

| [4:2] | -    | Reserv                    | ved                       |             |                                                               |    |  |  |

|       |      | Parall                    | el BUS Int                | terface M   | ode                                                           |    |  |  |

| 1     | IND  | 0: Oth                    | ners                      |             |                                                               |    |  |  |

|       |      | 1: PIN                    | 1: PIN MODE[3:0] = "010X" |             |                                                               |    |  |  |

|       |      | SPI In                    | terface M                 | ode         |                                                               |    |  |  |

| 0     | SPI  | 0: Oth                    | ners                      |             |                                                               |    |  |  |

|       |      | 1: PIN MODE[3:0] = "000X" |                           |             |                                                               |    |  |  |

# 4.1.4 SYCR0 (System Config Register 0) [w0][0x2004] [0x80]

SYCR0 softly resets to W6100

SYCR0 can be set in case of only SYSR[CHPL] = '0' .

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|

| RST | - | - | - | - | - | - | - |

| WO  |   |   |   |   |   |   |   |

| Bit   | Symbol | Description                                     |

|-------|--------|-------------------------------------------------|

|       |        | Software Reset                                  |

|       |        | W6100 S/W reset. All registers are initialized. |

| 7     | RST    |                                                 |

|       |        | 0 : W6100 reset                                 |

|       |        | 1 : Normal operation                            |

| [6:0] | -      | Reserved                                        |

#### 4.1.5 SYCR1 (System Config Register 1) [R=W][0x2005] [0x80]

Interrupt enable and system operation clock (SYS\_CLK) can be set by this register.

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|-----|---|---|---|---|---|---|--------|

| IEN | - | - | - | - | - | - | CLKSEL |

| R=W |   |   |   |   |   |   | R=W    |

| Bit   | Symbol | Description                                        |

|-------|--------|----------------------------------------------------|

|       |        | Interrupt Enable                                   |

|       |        | It makes Interrupt enable.                         |

| 7     | IEN    |                                                    |

|       |        | 0 : Disable - INTn is always High.                 |

|       |        | 1 : Enable - When the event occurs, INTn goes low. |

| [6:1] | -      | Reserved                                           |

|       |        | System Operation Clock Select                      |

|       |        | In case of SYSR[CHPL] = '0', Select SYS_CLK.       |

| 0     | CLKSEL |                                                    |

|       |        | 0:100MHz                                           |

|       |        | 1:25MHz                                            |

#### 4.1.6 TCNTR (Tick Counter Register) [R0][0x2016-0x2017][0x0000]

It is automatically increased every 100us.

# 4.1.7 TCNTRCLR (TCNTR Clear Register) [w0][0x2020][0x00]

With Write operation to TCNTCLR, TCNTR counter value is initialized.

## 4.1.8 IR (Interrupt Register) [R0] [0x2100] [0x00]

When an event such as WOL (Wake On LAN) or destination unreachable occurs, the corresponding bit of IR is set to 1.

| 7   | 6 | 5 | 4    | 3 | 2      | 1    | 0     |

|-----|---|---|------|---|--------|------|-------|

| WOL |   |   | UNR6 |   | IPCONF | UNR4 | PTERM |

| RO  |   |   | RO   |   | RO     | RO   | RO    |

| Bit   | Symbol    | Description                                                           |

|-------|-----------|-----------------------------------------------------------------------|

|       |           | WOL(Wake On LAN) Magic Packet                                         |

| 7     | WOL       | 0 : Others                                                            |

|       |           | 1 : WOL MAGIC Packet received                                         |

| [6:5] | -         | Reserved                                                              |

|       |           | Destination IPv6 Port Unreachable                                     |

|       |           | 0 : Others                                                            |

|       |           | 1 : ICMPv6 Destination Port Unreachable Packet received               |

| 4     | UNR6      |                                                                       |

|       |           | ref) The Unreachable IPv6 Address and the Port Number of the received |

|       |           | Unreachable Packet are stored in UIP6R (Unreachable IPv6 Address      |

|       |           | Register) and UPORT6R (Unreachable IPv6 Port Register), respectively. |

| 3     | -         | Reserved                                                              |

|       |           | IP Conflict                                                           |

| 2     | IPCONF    | 0 : Others                                                            |

|       |           | 1 : IPv4 Address Conflict occurred                                    |

|       |           | Destination Port Unreachable                                          |

|       |           | 0: Others                                                             |

|       |           | 1: ICMPv4 Destination Port Unreachable Packet received                |

| 1     | UNR4      |                                                                       |

|       |           | ref) The Unreachable IP Address and Port Number of the received       |

|       |           | Unreachable Packet are stored in UIPR (Unreachable IP Address         |

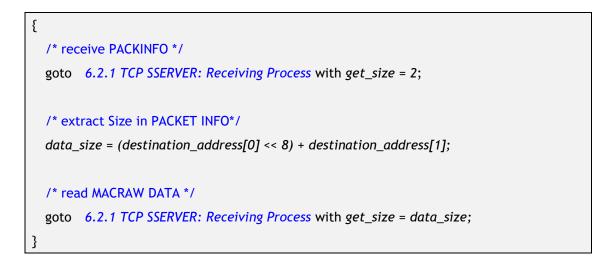

|       |           | Register) and UPORTR (Unreachable Port Register), respectively.       |