W65C134S Datasheet

WDC reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. Information contained herein is provided gratuitously and without liability, to any user. Reasonable efforts have been made to verify the accuracy of the information but no guarantee whatsoever is given as to the accuracy or as to its applicability to particular uses. In every instance, it must be the responsibility of the user to determine the suitability of the products for each application. WDC products are not authorized for use as critical components in life support devices or systems. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents or other rights of third parties. The sale of any WDC product is subject to all WDC Terms and Conditions of Sales and Sales Policies, copies of which are available upon request.

Copyright (C) 1981-2019 by The Western Design Center, Inc. All rights reserved, including the right of reproduction in whole or in part in any form.

October 15, 2019

W65C134S Datasheet

# TABLE OF CONTENTS

| DOCUMENT REVISION HISTORY                                                                                              | 5  |

|------------------------------------------------------------------------------------------------------------------------|----|

| 1 INTRODUCTION                                                                                                         | 6  |

| 1.1 KEY FEATURES OF THE W65C134S                                                                                       | 6  |

| 2 W65C134S FUNCTION DESCRIPTION                                                                                        | 6  |

| 2.1 Monitor ROM                                                                                                        | 6  |

| 2.2 SRAM (\$0040-FF and \$0140-FF)                                                                                     | 7  |

| 2.3 Bus Control Register (BCR) (\$001B)                                                                                | 7  |

| Figure 2.3-1 BE Timing Relative to RESB Input                                                                          |    |

| Table 2.3-1 BCR7 and BE Control                                                                                        |    |

| 2.3.1 Bus Control Register (BCR) Description                                                                           | 8  |

| 2.4 Port Chip Select 3 (PCS3) Register (\$0007)                                                                        | 9  |

| 2.4.1 Chip Select Register on Port 3 (PCS3) Description                                                                | 9  |

| 2.5 The Timers                                                                                                         |    |

| 2.5.1 Timer Control Register One (TCR1) Description                                                                    |    |

| 2.5.2 Timer Control Register Two (TCR2) Description                                                                    | 12 |

| 2.6 Interrupt Flag Registers (IFR1, IFR2) (\$002C, \$0008)                                                             |    |

| 2.6.1 Read of IFR1 and IFR2.                                                                                           |    |

| 2.6.2 Interrupt Priority                                                                                               |    |

| 2.6.1 Interrupt Flag Register One (IFR1) Description<br>2.6.2 Interrupt Flag Register One (IFR2) Description           |    |

|                                                                                                                        | 45 |

| 2.7 Interrupt Enable Registers (IER1, IER2) (\$002D, \$0009)<br>2.7.1 Interrupt Enable Register One (IER1) Description |    |

| 2.7.2 Interrupt Flag Register One (IER2) Description                                                                   |    |

|                                                                                                                        |    |

| 2.8 Universal Asynchronous Receiver/Transmitters (UARTs)                                                               |    |

| 2.8.1 Transmitter Operation                                                                                            |    |

| 2.8.2 UART Data Register Description                                                                                   |    |

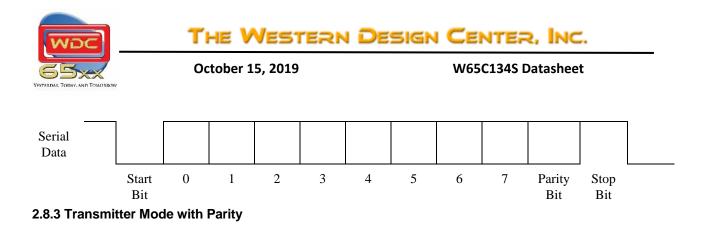

| 2.8.3 Transmitter Mode with Parity                                                                                     |    |

| 2.8.4 Receiver Operation                                                                                               | 18 |

October 15, 2019

#### W65C134S Datasheet

| 2.8.5 Data Timing for 7-bit Data without Parity and two stop bits1 | 8 |

|--------------------------------------------------------------------|---|

| 2.8.6 UART RXD and TXD Data Rate Generation.                       |   |

| 2.8.7 Asynchronous Control and Status Registers (ACSR) Description | 0 |

| 2.9 The Serial Interface Bus (SIB)                                            | 21 |

|-------------------------------------------------------------------------------|----|

| 2.9.1 The STATE Register                                                      |    |

| 2.9.2 STATE Register (STATE) Description                                      |    |

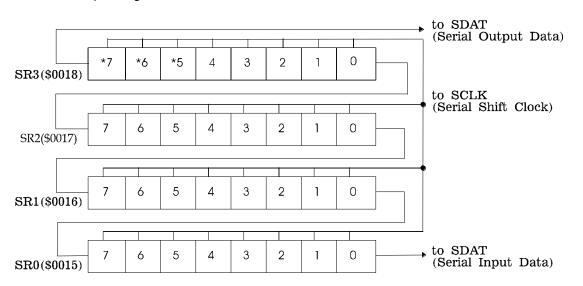

| 2.9.3 SR0, SR1, SR2, and SR3 Shift Register                                   | 22 |

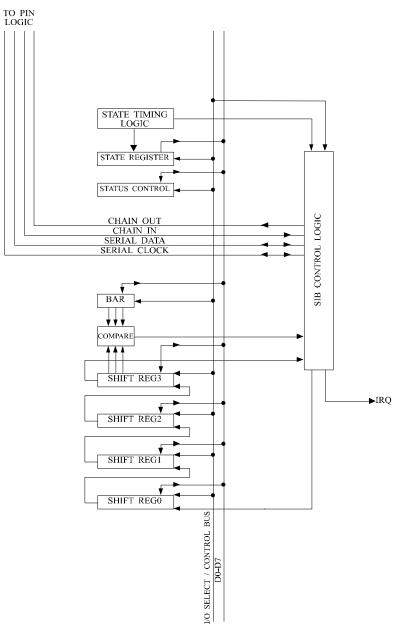

| Figure 2.9.3-1 SR0, SR1, SR2, and SR3 Shift Register                          | 22 |

| 2.9.4 SIB Shift Register Description                                          | 22 |

| 2.9.5 SIB Control and Status Register (SCSR)                                  |    |

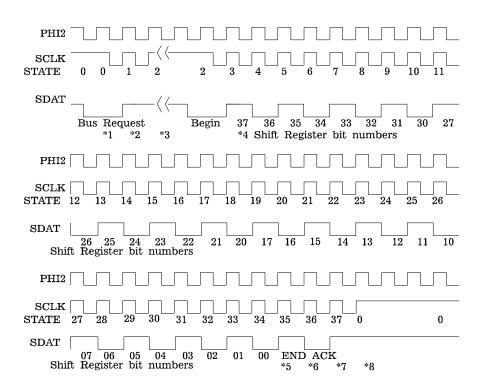

| 2.9.6 Sequence of events for the SIB message transmission.                    | 24 |

| Figure 2.9.6-1 Serial Interface Bus (SIB) Message Transmission Timing Diagram |    |

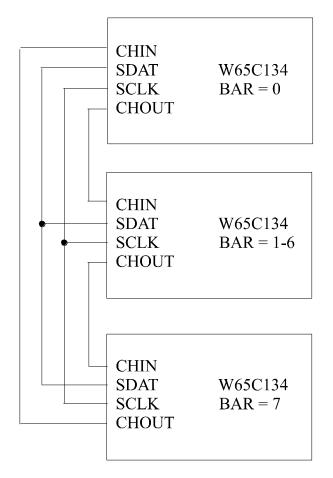

| Figure 2.9.6-2 Serial Interface Bus (SIB) Wiring Diagram                      |    |

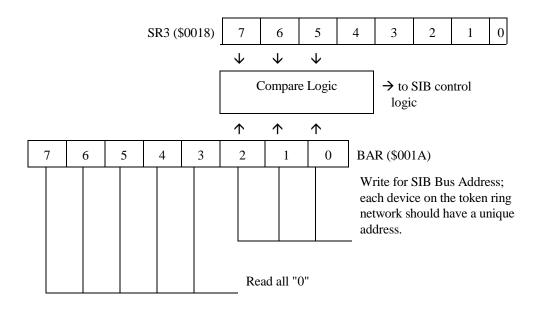

| Figure 2.9.6-3 Bus Address Register (BAR)                                     |    |

|                                                                               |    |

| 3 Memory Map                |  |

|-----------------------------|--|

| Table 3-1 System Memory Map |  |

| Table 3-2 I/O Memory Map    |  |

| Table 3-3 Vector Table      |  |

|                             |  |

| 4 Pin List                                         |  |

|----------------------------------------------------|--|

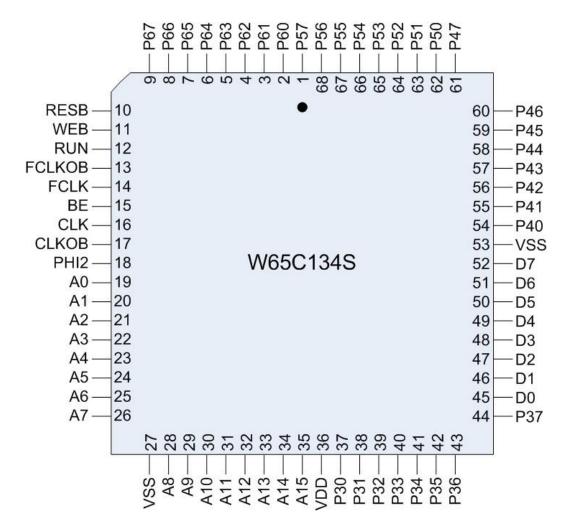

| Table 4-1 68 Lead Pin Map (continued on next page) |  |

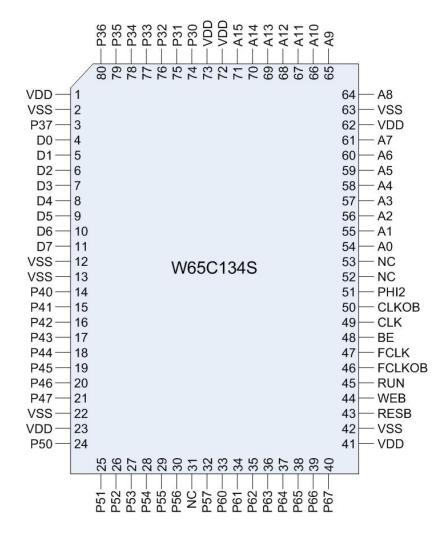

| 5 PIN FUNCTION DESCRIPTION                                                        | 34 |

|-----------------------------------------------------------------------------------|----|

| Figure 5-1 Interface Diagram                                                      | 34 |

| Figure 5-2 68 Lead PLCC Pinout                                                    |    |

| Figure 5-3 80 Lead QFP Pinout                                                     | 36 |

| 5.1 WEB Write Enable (WEB) (active low)                                           | 37 |

| 5.2 RUN and SYNC outputs with WAI and STP defined (RUN)                           | 37 |

| 5.3 FCLK                                                                          |    |

| 5.4 Phase 2 Clock Output (PHI2)                                                   |    |

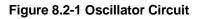

| 5.5 Clock Inputs (CLK, FCLK), Clock Outputs (CLKOB, FCLKOB)                       | 37 |

| 5.6 Bus Enable and RDY Input (BE)                                                 |    |

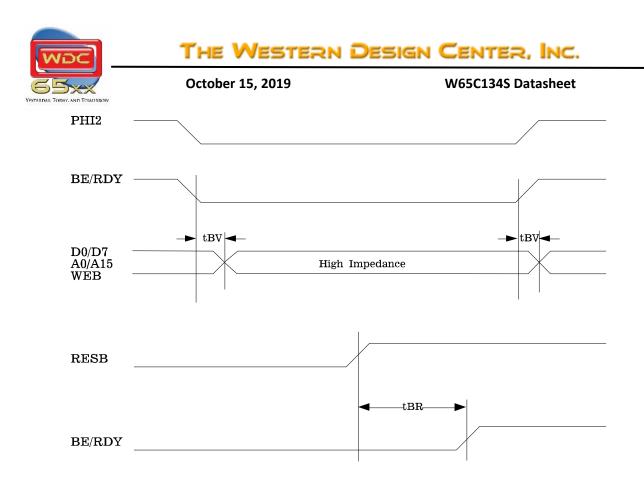

| Figure 5-1 BE Timing Relative to PHI2                                             |    |

| 5.7 Reset Input/Output RESB (RESB)                                                | 39 |

| 5.8 Positive Power Supply (VDD)                                                   | 39 |

| 5.9 Internal Logic Ground (VSS)                                                   |    |

| 5.10 I/O Port Pins (Pxx)                                                          | 39 |

| 5.11 Address Bus (Axx)                                                            |    |

| 5.12 Data Bus (Dx)                                                                | 40 |

| 5.13 Positive Edge Interrupt inputs (PExx)                                        | 40 |

| 5.14 Negative Edge Interrupt inputs (NExx)                                        | 40 |

| 5.15 Chip Select outputs (active low) (CSxB)                                      | 40 |

| 5.16 Level Sensitive Interrupt Request inputs (IRQxB)                             |    |

| 5.17 Non-Maskable Edge Interrupt Input (NMIB)                                     | 41 |

| 5.19 Timer A Input and Output (TIN, TOUT)                                         |    |

| 5.20 The Serial Interface Bus (SIB) pins. (See Serial Interface Bus (SIB) Message |    |

October 15, 2019

W65C134S Datasheet

Transmission Timing diagram.).....41

| 6 TIMING, AC AND DC CHARACTERISTICS   |    |

|---------------------------------------|----|

| 6.1 Absolute Maximum Ratings (Note 1) | 42 |

| Table 6-1 Absolute Maximum Ratings    |    |

| 6.2 DC Characteristics                | 43 |

| Table 6.2-1 DC Characteristics        | 43 |

| 6.3 AC Characteristics                |    |

| Table 6.3-1 AC Characteristics        |    |

| 6.4 AC Parameters                     |    |

| 6.5.1 AC Timing Diagram Notes         |    |

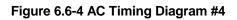

| 6.6 AC Timing Diagrams                |    |

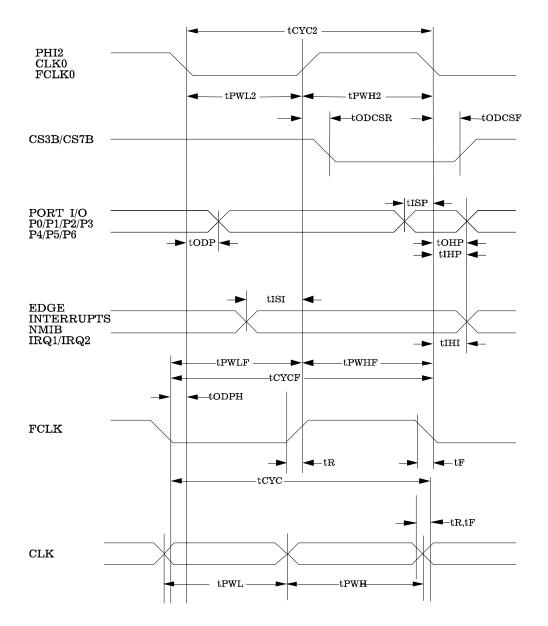

| Figure 6.6-1 AC Timing Diagram #1     |    |

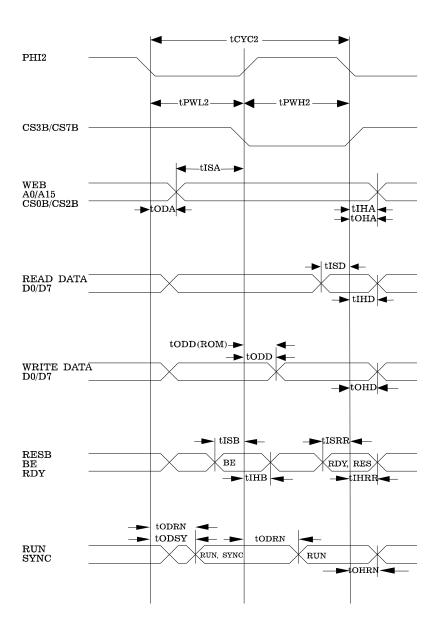

| Figure 6.6-2 AC Timing Diagram #2     |    |

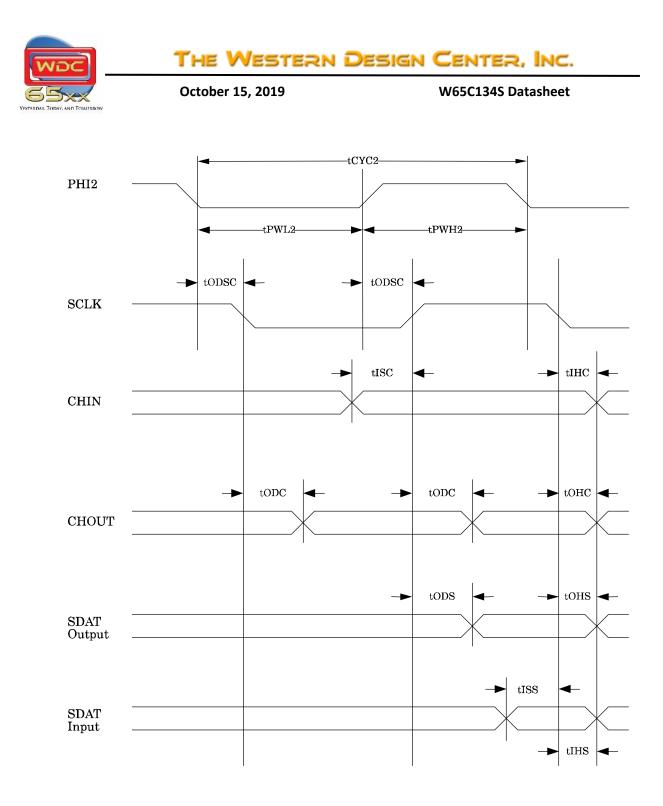

| Figure 6.6-3 AC Timing Diagram #3     |    |

| Figure 6.6-4 AC Timing Diagram #4     |    |

| Figure 6.6-5 AC Timing Diagram #5     |    |

|                                       |    |

|                                       |    |

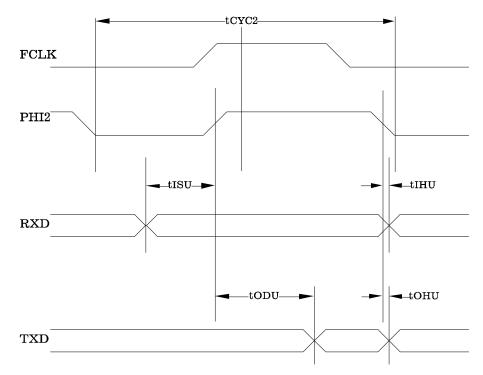

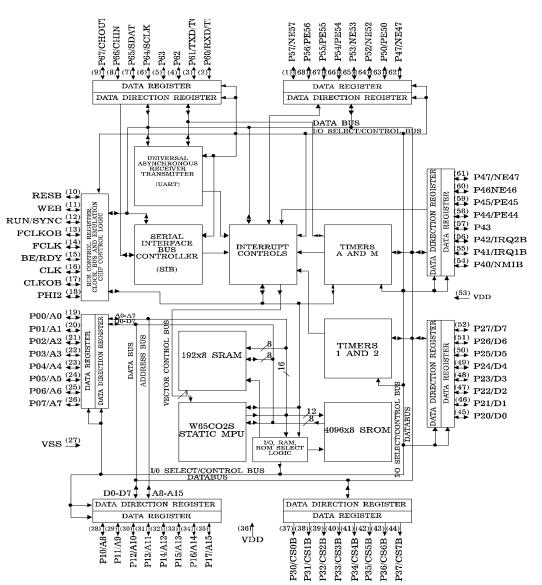

| 7 Block Diagrams                                                            | 51 |

|-----------------------------------------------------------------------------|----|

| Figure 7-1 W65C134S Block Diagrams                                          |    |

| Figure 7-2 Interrupt Controller Block Diagram                               |    |

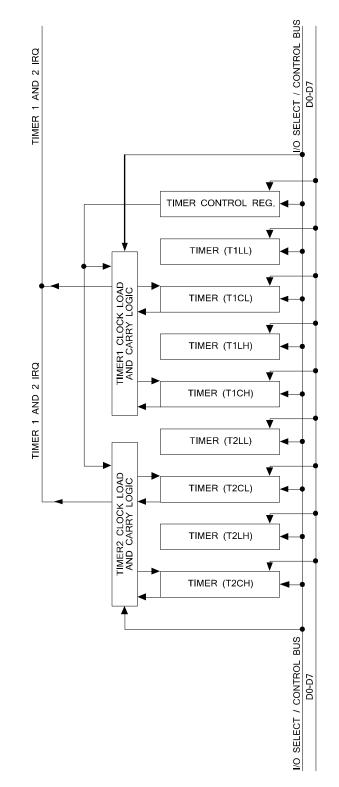

| Figure 7-3 T1 and T2 Block Diagram                                          |    |

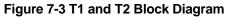

| Figure 7-4 Timer A and M (TA and TM) Block Diagram                          |    |

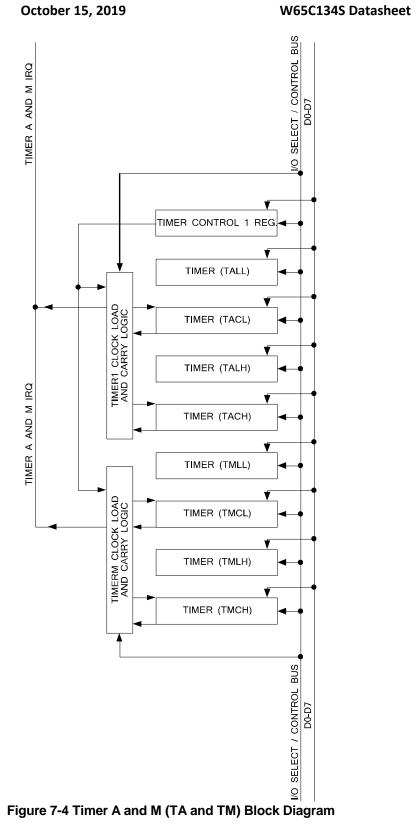

| Figure 7-5 Universal Asynchronous Receiver Transmitter (UART) Block Diagram | 55 |

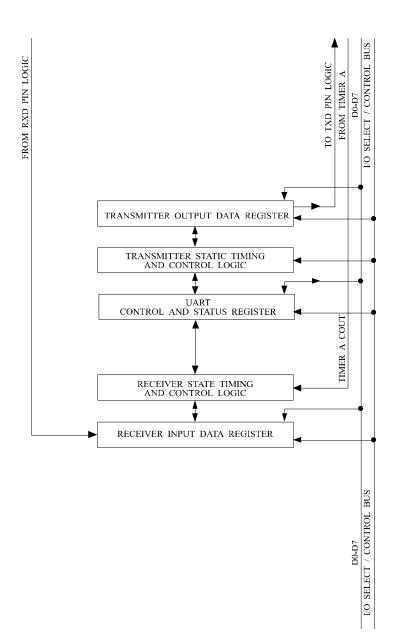

| Figure 7-6 Serial Interface Bus (SIB) Block Diagram                         | 56 |

|                                                                             |    |

| 8 Application Information                                 | 57 |

|-----------------------------------------------------------|----|

| 8.1 External ROM Startup with W65C134S Mask ROMs          |    |

| 8.2 Recommended clock (CLK) and fclock (FCLK) oscillators |    |

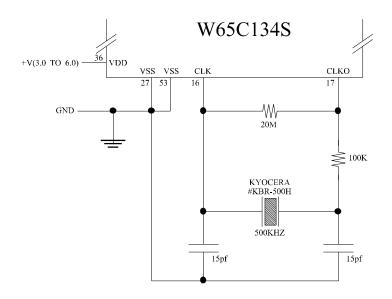

| Figure 8.2-1 Oscillator Circuit                           |    |

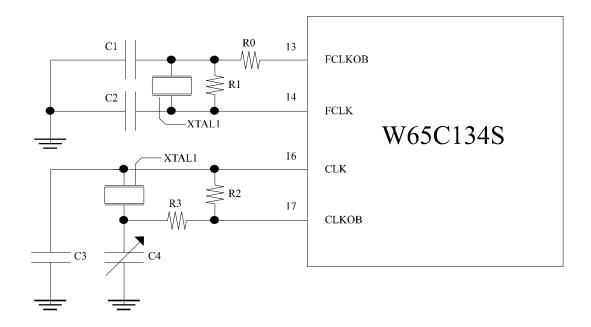

| Figure 8.2-2 Circuit Board Layout for Oscillator Circuit  |    |

| Figure 8.2-3 W65C134S Resonator Circuit                   | 60 |

| 8.3 Wait state information and uses for the BE pin        | 60 |

| 9 ORDERING INFORMATION |

|------------------------|

|------------------------|

October 15, 2019

W65C134S Datasheet

# **DOCUMENT REVISION HISTORY**

| Version | Date       | Authors     | Description                       |

|---------|------------|-------------|-----------------------------------|

| 2.0     | 10/15/2019 | Bill Mensch | Rewrite of the W65C134S Datasheet |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

|         |            |             |                                   |

October 15, 2019

W65C134S Datasheet

## **1 INTRODUCTION**

The WDC W65C134S microcontroller is a complete fully static 8-bit computer fabricated on a single chip using a low power CMOS process. The W65C134S has been developed with life support features recommended by medical electronics firms. The Serial Interface Bus (SIB) was designed for an in-the-human-body token passing local area network (LAN) for eight (8) networked controllers.

This product description assumes that the reader is familiar with the W65C02S CPU hardware and programming capabilities. Refer to the <u>W65C02S Datasheet</u>, <u>Programming the 65816</u>: <u>Including the 6502</u>, <u>65C02 and 65802</u> and <u>W65C134SXB Single Board Computer (SBC)</u> for more information.

#### 1.1 KEY FEATURES OF THE W65C134S

- CMOS low power process

- Operating TA= -40EC to +85EC

- Single 2.8V to 5.5V power supply

- Static to 8MHz clock operation

- W65C02S compatible CPU

- 8-bit parallel processing

- Variable length stack

- True indexing capability

- Fifteen addressing modes

- Decimal or binary arithmetic

- Pipeline architecture

- Fully static CPU

- W65C816S 16-bit CPU compatible

- Single chip microcomputer

- Many power saving features

- 56 CMOS compatible I/O lines

- 4096 x 8 ROM on chip

- 192 x 8 RAM on chip

- Low power modes

- WAlt for interrupt

- SToP the clock

- Fast oscillator start and stop feature

- Twenty-two priority encoded interrupts

- BRK software interrupt

- RESET "RESTART" interrupt

- NMIB Non-Maskable Interrupt input

- SIB Interrupt

- IRQ1B level interrupt input

- IRQ2B level interrupt input

- 2 timer edge interrupts

- 7 positive edge interrupt inputs

- 5 negative edge interrupt inputs

- Asynchronous Receiver Interrupt

- Asynchronous Transmitter Interrupt

- UART 7/8-bit w/wo odd or even parity

- 16M byte segmented address space

- 64K byte linear address space

- 4 x 16 bit timer/counters

- Bus control register for external memory

- Internal or external ROM

- 8 Decoded Chip Select outputs

- Surface mount 68 and 80 lead packages

- Real time clock features

- Third party tools available

## 2 W65C134S FUNCTION DESCRIPTION

The embedded microprocessor is the W65C02 Static 8-bit Microprocessor Core that does not include the bit-manipulation instructions made popular by Rockwell Semiconductor.

#### 2.1 Monitor ROM

The W65C134S 4096 x 8 bit Read Only Memory (ROM) Monitor contains the user's programmer terminal interface with a library of built-in functions. These program instructions and constants are mask-programmed into the ROM during fabrication of the W65C134S device. The W65C134S ROM is memory mapped from \$F000 to \$FFFF. The W65C134S Monitor ROM Reference Manual, Monitor Rom code listing, and WDCTools for Assembly and C language software development are available for developers.

October 15, 2019

W65C134S Datasheet

#### 2.2 SRAM (\$0040-FF and \$0140-FF)

The 192 x 8 bit Static Random Access Memory (SRAM) contains the user program stack and is used for scratch pad memory during system operation. This RAM is completely static in operation and requires no clock or dynamic refresh. The data contained in RAM is read out nondestructively with the same polarity as the input data. In order to take advantage of zero page addressing capabilities, the W65C134S RAM is assigned to both page zero memory addresses \$0040 to \$00FF and to page one stack addresses \$0140 to \$01FF.

#### 2.3 Bus Control Register (BCR) (\$001B)

The Bus Control Register (BCR) controls the various modes of I/O and external memory interface. During power-up the value of BE defines the initial values of BCR0, BCR3 and BCR7, three bits in the BCR that set up the W65C134S for normal or test mode operation. When BE goes high after RESB goes high the BCR sets up the W65C134S for test mode. Port 0 and 1 are the address outputs, Port 2 is the data I/O bus and RUN is the multiplexed RUN function. See RUN pin function description. When BE goes high before RESB goes high, all bits in the BCR are "0". After RESB goes high BE no longer effects the BCR register, and BCR may be written under software control to reconfigure the W65C134S as desired. Table 2.3-1 indicates how BCR7 and BE define the W65C134S configuration.

|         | Figure 2.3-1 BE Timing Relative to RESB Input. |  |  |

|---------|------------------------------------------------|--|--|

| RESB_   |                                                |  |  |

| BE/RDY  | BCR0=BCR3=BCR7=1                               |  |  |

| BE/RDY_ | BCR0=BCR3=BCR7=0                               |  |  |

Table 2.3-1 BCR7 and BE Control

| BCR7 | BE | W65C134S configuration                          |

|------|----|-------------------------------------------------|

| 0    | 0  | Internal ROM External Processor (DMA test mode) |

| 0    | 1  | Internal ROM Internal Processor                 |

| 1    | 0  | External ROM External Processor (DMA test mode) |

| 1    | 1  | External ROM Internal Processor                 |

W65C134S Datasheet

# 2.3.1 Bus Control Register (BCR) Description

| Addres | ss = \$001B | BCR: BCR | Register                                  |                 |               |              | Reset Va       | lue = 0x00   |  |  |

|--------|-------------|----------|-------------------------------------------|-----------------|---------------|--------------|----------------|--------------|--|--|

| 7:0->  | BCR7        | BCR6     | BCR5 BCR4 BCR3 BCR2 BCR1 BCR0             |                 |               |              |                |              |  |  |

| HWRES  | 0 = BE High | 0        | 0                                         | 0               | 0             | 0            | 0              | 0            |  |  |

| BERES  | 1 = BE Low  | -        | -                                         | -               | 1             | -            | -              | 1            |  |  |

| Bit    | Name        | Access   | Description                               |                 |               |              |                |              |  |  |

| 7      | BCR7        | R/W      | 1 = External I                            | ROM at \$F00    | 0-FFFF        |              |                |              |  |  |

| 1      | BCR/        | r(/ VV   | 0 = Internal ROM at \$F000-FFFF           |                 |               |              |                |              |  |  |

| G      | BCDC        | R/W      | 1 = P40=NMIB, P41=IRQ1B, P42=IRQ2B inputs |                 |               |              |                |              |  |  |

| 6      | BCR6        | R/W      | <b>0</b> = Pins 40-4                      | 2 are standar   | d I/O         |              |                |              |  |  |

| 5      | BCR5        | R/W      | 1 = EDGE int                              | terrupt inputs  | on P54-57     |              |                |              |  |  |

| 5      | BCKJ        | 17/17    | 0 = No EDGE                               | E interrupt inj | outs on P54-5 | 7            |                |              |  |  |

| 4      | BCR4        | R/W      | 1 = EDGE int                              | terrupt inputs  | on P50-53     |              |                |              |  |  |

| 4      | BORT        |          | 0 = No EDGE                               | E interrupt inj | outs on P50-5 | 3            |                |              |  |  |

| 3      | BCR3        | R/W      | 1 = Test Mo<br>are output of              |                 |               | ed memory o  | r I/O for read | ls or writes |  |  |

| -      |             |          | 0 = Normal (                              | Operation R     | UN=RUN        |              |                |              |  |  |

| 2      | BCR2        | R/W      | 1 = SIB Enab<br>P67=CHOUT                 |                 | rupt (P64=S0  | CLK, P65=SDA | AT, P66=CHIN   | Ν,           |  |  |

|        |             |          | 0 = SIB Disat                             | oled            |               |              |                |              |  |  |

| 4      | BCR1        |          | 1 = Edge Interrupt Inputs on P44-47       |                 |               |              |                |              |  |  |

| 1      | DUKI        | R/W      | 0 = No Edge Interrupt Inputs on P44-47    |                 |               |              |                |              |  |  |

|        | BCR0        |          | 1 = Ports 0,                              | 1,2 are add     | ress and da   | ta bus pins  |                |              |  |  |

| 0      | DURU        | R/W      | 0 = Ports 0,                              | 1,2 are I/O     | oins          |              |                |              |  |  |

October 15, 2019

W65C134S Datasheet

#### 2.4 Port Chip Select 3 (PCS3) Register (\$0007)

The Port Chip Select (PCS3) Register. The PCS3 provides enables or disables the chip select output on Port 3. When PCS30-PCS37 are equal to a "1", then CS0B to CS7B will be active. When CS1B is active, the defined memory space for CS3B and/or CS6B is reduced. It is reduced by the memory space 0100-011F for CS1B. When CS2B is active, the defined memory space for CS3B and/or CS6B is reduced. It is reduced by the memory space 0120-013F for CS2B.

CS7B is automatically enabled when BCR7=1.

The W65C134S will use the internal RAM as stack when PCS33 and PCS36 are disabled. If PCS33 or PCS36 are enabled then the off chip stack is used.

#### 2.4.1 Chip Select Register on Port 3 (PCS3) Description

|       |        |        | er Interrupt E             | nable Registe            | r     |       | Reset Value = 0x00 |       |  |

|-------|--------|--------|----------------------------|--------------------------|-------|-------|--------------------|-------|--|

| 7:0-> | PCS37  | PCS36  | PCS35                      | PCS34                    | PCS33 | PCS32 | PCS31              | PCS30 |  |

| Bit   | Name   | Access | Description                | l                        |       |       |                    |       |  |

| 7     | PCS37  | R/W    | 1 = Chip Sel               | ect 7 Enabled            |       |       |                    |       |  |

| '     | FC337  | r./ W  | 0 = Chip Sel               | ect 7 Disabled           |       |       |                    |       |  |

| 6     | PCS36  | R/W    | 1 = Chip Sel               | = Chip Select 6 Enabled  |       |       |                    |       |  |

| 0     | FC330  | r./ W  | 0 = Chip Sel               | = Chip Select 6 Disabled |       |       |                    |       |  |

| 5     | PCS35  | R/W    | 1 = Chip Sel               | ect 5 Enabled            |       |       |                    |       |  |

| 5     | F0333  | 11/ 44 | 0 = Chip Sel               | ect 5 Disabled           |       |       |                    |       |  |

| 4     | PCS34  | R/W    | 1 = Chip Sel               | ect 4 Enabled            |       |       |                    |       |  |

| 4     | F0004  | 11/ 44 | 0 = Chip Sel               | ect 4 Disabled           |       |       |                    |       |  |

| 3     | PCS33  | R/W    | 1 = Chip Sel               | ect 3 Enabled            |       |       |                    |       |  |

| 5     | F 0000 | 17/ 44 | 0 = Chip Sel               | ect 3 Disabled           |       |       |                    |       |  |

| 2     | PCS32  | R/W    | 1 = Chip Sel               | ect 2 Enabled            |       |       |                    |       |  |

|       | F 0052 | 11/ 44 | 0 = Chip Sel               | ect 2 Disabled           |       |       |                    |       |  |

| 1     | PCS31  | R/W    | 1 = Chip Select 1 Enabled  |                          |       |       |                    |       |  |

| •     | FC331  | r./ W  | 0 = Chip Select 1 Disabled |                          |       |       |                    |       |  |

| 0     | PCS30  | R/W    | 1 = Chip Sel               | ect 0 Enabled            |       |       |                    |       |  |

| U     | F0330  |        | 0 = Chip Sel               | ect 0 Disabled           |       |       |                    |       |  |

October 15, 2019

W65C134S Datasheet

#### 2.5 The Timers

Upon Timer clock input negative edge the timer low counter is decremented by 1.

When T1 or T2 prescaler mode is enabled, (making timer low counter a divide-by-N+1 prescaler) then timer low counter is reloaded from timer low latch. Monitor Timer M does not have a prescaler mode.

A write to the timer low counter writes the timer low latch.

A read of the timer high or low counter reads the timer high or low counter.

Upon Timer clock input negative edge when the timer low counter reaches zero, the timer high counter is decremented by 1.

Upon Timer clock input positive edge, when the timer high counter reaches zero, this sequence occurs:

Timer 1 and 2 set their associated interrupt flag. If the interrupt is enabled the MPU is then interrupted and control is transferred to the vector associated with the interrupt. When Timer M times out, the W65C134S is restarted: On-chip logic pulls RESB pin low for 2 CLK cycles and releases RESB to go high, "restarting" the W65C134S.

The timer hi counter is loaded from the timer hi latch, and timer low counter is loaded from timer low latch.

A write to the Timer 1, 2 or A high counter writes to the timer hi latch and this sequence occurs:

The timer hi latch is loaded from data bus. The timer low counter is loaded from the timer low latch, and the timer hi counter is loaded from the timer hi latch.

Timer M is disabled after RESB and is activated by the first Timer Control Register One (TCR10) transition from "0" to "1" (the first load of Timer M).

The Timer M counter is reloaded with the value in the Timer M latches when the TCR10 bit 0 makes a transition from a "0" to "1". TCR10 transition from a "1" to a "0" has no effect on the timer.

October 15, 2019

W65C134S Datasheet

# 2.5.1 Timer Control Register One (TCR1) Description

| Addres | ss = \$000A | TCR1: Time          | er Control Register One Reset Value = 0x0                                          |                                                                                 |                                   |                          |                |              |  |  |

|--------|-------------|---------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------|--------------------------|----------------|--------------|--|--|

| 7:0->  | TCR17       | TCR16               | TCR15                                                                              | TCR15 TCR14 TCR13 TCR12 TCR11 TCR10                                             |                                   |                          |                |              |  |  |

| Bit    | Name        | Access              | Description                                                                        |                                                                                 |                                   |                          |                |              |  |  |

| 7      | TCR17       | R/<br>W=1<br>Clears | Asynchronous<br>a "1" to it. W                                                     | edge Interrupt has<br>Transmitter veo<br>riting a "0" to th<br>Edge Interrupt h | ctor location.<br>is bit has no a | This bit is c<br>affect. | leared to a "0 | " by writing |  |  |

| 6      | TCR16       | R/W                 |                                                                                    | 1 = Timer A Interrupt Enabled.                                                  |                                   |                          |                |              |  |  |

| 5      | TCR15       | R/W                 | 1 = Timer A<br>the UART.                                                           | Interrupt Disable<br>FOUT enabled.<br>Dutput disabled                           |                                   | 0=1, Timer               | A and TXD a    | re used for  |  |  |

| 4      | TCR14       | R/W                 | are used for th                                                                    | counts TIN nega<br>the UART and the<br>counts PHI2 close                        | is bit should b                   |                          |                | A and RXD    |  |  |

| 3      | TCR13       | R/W                 |                                                                                    | clock enabled 1<br>clock disabled (c                                            |                                   |                          |                |              |  |  |

| 2      | TCR12       | R/W                 | 1 = Start FCL<br>0 = Stop FCL                                                      |                                                                                 |                                   |                          |                |              |  |  |

| 1      | TCR11       | R/W                 | 1 = PHI2 clock source is FCLK (Fast Clock)<br>0 = PHI2 clock source is CLK (Clock) |                                                                                 |                                   |                          |                |              |  |  |

| 0      | TCR10       | R/W                 |                                                                                    | no effect on M<br>sition loads the                                              | -                                 |                          |                |              |  |  |

October 15, 2019

W65C134S Datasheet

# 2.5.2 Timer Control Register Two (TCR2) Description

| Addres | s = \$000B | TCR1: Time | r Control Register One Reset Value = 0 |                                     |                |              |       |  |  |  |

|--------|------------|------------|----------------------------------------|-------------------------------------|----------------|--------------|-------|--|--|--|

| 7:0->  | TCR27      | TCR26      | TCR25                                  | TCR25 TCR24 TCR23 TCR22 TCR21 TCR20 |                |              |       |  |  |  |

| Bit    | Name       | Access     | Description                            | า                                   |                |              |       |  |  |  |

| 7      | TCR27      | P alwaya 0 | 1 = Never                              | 1 = Never                           |                |              |       |  |  |  |

| '      | ICKZI      | R always 0 | 0 = Does no                            | othing                              |                |              |       |  |  |  |

| 6      | TCR26      | R/W        | 1 = Timer A                            | 1 = Timer A Interrupt Enabled.      |                |              |       |  |  |  |

| 0      | I CK20     | FX/ ¥¥     | 0 = Timer A                            | 0 = Timer A Interrupt Disabled.     |                |              |       |  |  |  |

| 5      | TCR25      | R/W        | 1 = 8 bit pres                         | scaled with 8 bit                   | counter mode   | e            |       |  |  |  |

| 5      | TORZJ      | 11/ 44     | 0 = 16 bit co                          | unter mode                          |                |              |       |  |  |  |

| 4      | TCR24      | R/W        | 1 = T2  count                          | s CLK clock pu                      | lses           |              |       |  |  |  |

| 4      | I GRZ4     | r./ W      | 0 = T2  count                          | s PHI2 clock pu                     | lses           |              |       |  |  |  |

| 3      | TCR23      | R/W        | 1 = T2 clock                           | enabled (counti                     | ng clock as se | elected by T | CR24) |  |  |  |

| 5      | TGN25      | 11/ 44     | 0 = T2 clock                           | disabled (count                     | er stopped)    |              |       |  |  |  |

| 2      | TCR22      | R/W        | 1 = 8 bit pres                         | scaler with 8 bit                   | counter mode   | •            |       |  |  |  |

| 2      | TORZZ      | 11/ 11     | 0 = 16 bit co                          | unter mode                          |                |              |       |  |  |  |

| 1      | TCR21      | R/W        | 1 = T1 counts CLK clock pulses         |                                     |                |              |       |  |  |  |

|        | TONZT      | 11/ 44     | 0 = T1 counts PHI2 clock pulses        |                                     |                |              |       |  |  |  |

| 0      | TCR20      | R/W        | 1 = T1 clock                           | enabled (counti                     | ng clock as se | elected by T | CR21) |  |  |  |

| Ŭ      | TONZO      | 11/ 44     | 0 = T1 clock                           | disabled (count                     | er stopped)    |              |       |  |  |  |

October 15, 2019

W65C134S Datasheet

## 2.6 Interrupt Flag Registers (IFR1, IFR2) (\$002C, \$0008)

Each bit of these interrupt flag registers is set to a "1" in response to a interrupt source. Sources specified as level-triggered assert the corresponding IFR bit if an edge occurs and is held to a "1" as long as the IRQxB input is held low. Sources specified as edge-triggered assert the corresponding IFR bit upon and only upon transition to the specified polarity. Note that changes for edge-triggered bits are asynchronous with PHI2.

#### 2.6.1 Read of IFR1 and IFR2.

A read from an IFR register transfers its value to the internal data bus.

Write to IFR1 and IFR2

A write of a "1" to any bits of these registers disserts those bits but has no further effect when execution of that write instruction is completed; that is, the bit is reset by a pulse but not held reset. A write of a "0" to any bits of these registers has no effect.

#### 2.6.2 Interrupt Priority

If more than one bit of the Interrupt Flag Registers are set to a "1" and enabled, the vector corresponding to the highest bit number asserted is used. For example, if both the IFR10 and IFR23 were asserted and enabled, then the vector corresponding to IFR23 would be used. For another example, if both the IFR13 and IFR20 were asserted and enabled, then the vector corresponding to IFR23 would be used.

| Addres | s = \$002C | IFR1: Interr | upt Flag Reg                                   | ister One                                      |               |         | Reset Va | lue = 0x00 |  |  |  |

|--------|------------|--------------|------------------------------------------------|------------------------------------------------|---------------|---------|----------|------------|--|--|--|

| 7:0->  | IFR17      | IFR16        | IFR15                                          | IFR15 IFR14 IFR13 IFR12 IFR11 IFR10            |               |         |          |            |  |  |  |

| Bit    | Name       | Access       | Description                                    |                                                |               |         |          |            |  |  |  |

| 7      | IFR17      | R/W          | 1 = NE53 Neg                                   | 1 = NE53 Negative Edge Interrupt Occurred      |               |         |          |            |  |  |  |

| 1      |            | F\/ ¥¥       | 0 = NE53 Neg                                   | gative Edge Inter                              | rupt Did Not  | Occur   |          |            |  |  |  |

| 6      | IFR16      | R/W          | 1 = NE52 Neg                                   | 1 = NE52 Negative Edge Interrupt Occurred      |               |         |          |            |  |  |  |

| 0      | IFKIO      | F\/ ¥¥       | 0 = NE52 Neg                                   | 0 = NE52 Negative Edge Interrupt Did Not Occur |               |         |          |            |  |  |  |

| 5      | IFR15      | R/W          | 1 = PE51 Posi                                  | 1 = PE51 Positive Edge Interrupt Occurred      |               |         |          |            |  |  |  |

| 5      | IFRIJ      | r/w          | 0 = PE51 Posi                                  | 0 = PE51 Positive Edge Interrupt Did Not Occur |               |         |          |            |  |  |  |

| 4      | IFR14      | R/W          | 1 = PE50 Posi                                  | itive Edge Interr                              | upt Occurred  | l       |          |            |  |  |  |

| 4      | IFK 14     | r/w          | 0 = PE50 Posi                                  | itive Edge Interr                              | upt Did Not   | Occur   |          |            |  |  |  |

| 3      | IFR13      | R/W          | 1 = NE47 Neg                                   | gative Edge Inter                              | rupt Occurre  | ed      |          |            |  |  |  |

| 3      | IFRIJ      | r./ vv       | 0 = NE47 Neg                                   | gative Edge Inter                              | rupt Did No   | t Occur |          |            |  |  |  |

| 2      | IFR12      | R/W          | 1 = NE46 Neg                                   | gative Edge Inter                              | rupt Occurre  | ed      |          |            |  |  |  |

| 2      |            | r/w          | 0 = NE46 Neg                                   | gative Edge Inter                              | rupt Did No   | t Occur |          |            |  |  |  |

|        |            | D/M/         | 1 = PE45 Positive Edge Interrupt Occurred      |                                                |               |         |          |            |  |  |  |

| 1      | IFR11      | R/W          | 0 = PE45 Positive Edge Interrupt Did Not Occur |                                                |               |         |          |            |  |  |  |

| •      |            | D/M/         | 1 = PE44 Positive Edge Interrupt Occurred      |                                                |               |         |          |            |  |  |  |

| 0      | IFR10      | R/W          | 0 = PE44 Posi                                  | tive Edge Interr                               | upt Did Not ( | Dccur   |          |            |  |  |  |

#### 2.6.1 Interrupt Flag Register One (IFR1) Description

October 15, 2019

W65C134S Datasheet

# 2.6.2 Interrupt Flag Register One (IFR2) Description

| Addres | ss = \$0008 | IFR2: Interr | upt Flag Reg    | Reset Va                                       | lue = 0x00    |       |  |  |  |  |  |

|--------|-------------|--------------|-----------------|------------------------------------------------|---------------|-------|--|--|--|--|--|

| 7:0->  | IFR27       | IFR26        | IFR25           | IFR25 IFR24 IFR23 IFR22 IFR21 IFR20            |               |       |  |  |  |  |  |

| Bit    | Name        | Access       | Description     |                                                |               |       |  |  |  |  |  |

| 7      |             | D/M/         | 1 = IRQ2B Lo    | 1 = IRQ2B Low Level Interrupt Occurred         |               |       |  |  |  |  |  |

| 7      | IFR27       | R/W          | 0 = IRQ2B Lc    | 0 = IRQ2B Low Level Interrupt Did Not Occur    |               |       |  |  |  |  |  |

| 6      | IFR26       | R/W          | 1 = IRQ1B Lc    | 1 = IRQ1B Low Level Interrupt Occurred         |               |       |  |  |  |  |  |

| 0      | IFR20       | r/w          | 0 = IRQ1B Lc    | 0 = IRQ1B Low Level Interrupt Did Not Occur    |               |       |  |  |  |  |  |

| E      | IED 25      | R/W          | 1 = Timer  2  E | dge Interrupt Oc                               | curred        |       |  |  |  |  |  |

| 5      | IFR25       | R/W          | 0 = Timer  2  E | dge Interrupt Di                               | d Not Occur   |       |  |  |  |  |  |

|        |             | D () A (     | 1 = Timer 1 E   | 1 = Timer 1 Edge Interrupt Occurred            |               |       |  |  |  |  |  |

| 4      | IFR24       | R/W          | 0 = Timer 1 E   | dge Interrupt Di                               | d Not Occur   |       |  |  |  |  |  |

|        |             | DAA          | 1 = NE57 Neg    | gative Edge Inter                              | rupt Occurre  | d     |  |  |  |  |  |

| 3      | IFR23       | R/W          | 0 = NE57 Neg    | gative Edge Inter                              | rupt Did Not  | Occur |  |  |  |  |  |

|        |             | D () A (     | 1 = PE56 Post   | tive Edge Interr                               | upt Occurred  |       |  |  |  |  |  |

| 2      | IFR22       | R/W          | 0 = PE56 Post   | tive Edge Interr                               | upt Did Not ( | Decur |  |  |  |  |  |

|        |             | D/M/         | 1 = PE55 Post   | 1 = PE55 Positive Edge Interrupt Occurred      |               |       |  |  |  |  |  |

| 1      | IFR21       | R/W          | 0 = PE55 Post   | 0 = PE55 Positive Edge Interrupt Did Not Occur |               |       |  |  |  |  |  |

|        |             | D/M/         | 1 = PE54 Post   | itive Edge Interr                              | upt Occurred  |       |  |  |  |  |  |

| 0      | IFR20       | R/W          | 0 = PE54 Post   | tive Edge Interr                               | upt Did Not ( | Dccur |  |  |  |  |  |

W65C134S Datasheet

## 2.7 Interrupt Enable Registers (IER1, IER2) (\$002D, \$0009)

IER1 and IER2 are the interrupt enable registers. Reading an IER register reads its contents and puts the value on the internal data bus. Writing an IER writes a value from the data bus into the register. Setting a bit in an IER to "1" permits the interrupt corresponding to the same bit in the IFR to cause a processor interrupt. Also, if the RUN pin was low prior to the interrupt, the pin will go high if BCR3 = 0.

#### 2.7.1 Interrupt Enable Register One (IER1) Description

| Addres | ss = \$002D | IFR1: Interr | upt Enable R                              | egister One                               |               |       | Reset Va | lue = 0x00 |  |  |  |

|--------|-------------|--------------|-------------------------------------------|-------------------------------------------|---------------|-------|----------|------------|--|--|--|

| 7:0->  | IER17       | IER16        | IER15                                     | IER14                                     | IER13         | IER12 | IER11    | IER10      |  |  |  |

| Bit    | Name        | Access       | Description                               | l                                         |               |       |          |            |  |  |  |

| 7      |             | R/W          | 1 = NE53 Neg                              | 1 = NE53 Negative Edge Interrupt Enabled  |               |       |          |            |  |  |  |

| 1      | IER17       | FK/ VV       | 0 = NE53 Neg                              | 0 = NE53 Negative Edge Interrupt Disabled |               |       |          |            |  |  |  |

| 6      |             | D/M/         | 1 = NE52 Neg                              | 1 = NE52 Negative Edge Interrupt Enabled  |               |       |          |            |  |  |  |

| 6      | IER16       | R/W          | 0 = NE52 Neg                              | gative Edge Inter                         | rupt Disabled | 1     |          |            |  |  |  |

| _      |             | D/M/         | 1 = PE51 Post                             | itive Edge Interr                         | upt Enabled   |       |          |            |  |  |  |

| 5      | IER15       | R/W          | 0 = PE51 Post                             | itive Edge Interr                         | upt Disabled  |       |          |            |  |  |  |

|        |             | D/M/         | 1 = PE50 Post                             | itive Edge Interr                         | upt Enabled   |       |          |            |  |  |  |

| 4      | IER14       | R/W          | 0 = PE50 Post                             | itive Edge Interr                         | upt Disabled  |       |          |            |  |  |  |

|        |             | D ////       | 1 = NE47 Neg                              | gative Edge Inter                         | rupt Enabled  |       |          |            |  |  |  |

| 3      | IER13       | R/W          | 0 = NE47 Neg                              | gative Edge Inter                         | rupt Disabled | 1     |          |            |  |  |  |

| 2      |             | D/M/         | 1 = NE46 Neg                              | gative Edge Inter                         | rupt Enabled  |       |          |            |  |  |  |

| 2      | IER12       | R/W          | 0 = NE46 Neg                              | gative Edge Inter                         | rupt Disabled | 1     |          |            |  |  |  |

|        |             | D/M          | 1 = PE45 Post                             | 1 = PE45 Positive Edge Interrupt Enabled  |               |       |          |            |  |  |  |

| 1      | IER11       | R/W          | 0 = PE45 Positive Edge Interrupt Disabled |                                           |               |       |          |            |  |  |  |

| •      |             | D/M/         | 1 = PE44 Positive Edge Interrupt Enabled  |                                           |               |       |          |            |  |  |  |

| 0      | IER10       | R/W          | 0 = PE44 Posi                             | itive Edge Interr                         | upt Disabled  |       |          |            |  |  |  |

October 15, 2019

W65C134S Datasheet

# 2.7.2 Interrupt Flag Register One (IER2) Description

| Addres | ss = \$0009 | IFR2: Interr | rupt Enable Register Two Reset Valu       |                                          |               |       |       |       |  |  |  |

|--------|-------------|--------------|-------------------------------------------|------------------------------------------|---------------|-------|-------|-------|--|--|--|

| 7:0->  | IER27       | IER26        | IER25                                     | IER24                                    | IER23         | IER22 | IER21 | IER20 |  |  |  |

| Bit    | Name        | Access       | Description                               |                                          |               |       |       |       |  |  |  |

| 7      | IER27       | R/W          | 1 = IRQ2B Lc                              | 1 = IRQ2B Low Level Interrupt Enabled    |               |       |       |       |  |  |  |

| 1      | IER21       | r./ W        | 0 = IRQ2B Lc                              | ) = IRQ2B Low Level Interrupt Disabled   |               |       |       |       |  |  |  |

| 6      | IEDae       | R/W          | 1 = IRQ1B Lc                              | 1 = IRQ1B Low Level Interrupt Enabled    |               |       |       |       |  |  |  |

| 0      | IER26       | R/W          | 0 = IRQ1B Lc                              | ow Level Interru                         | pt Disabled   |       |       |       |  |  |  |

| E      |             | R/W          | 1 = Timer  2  E                           | dge Interrupt En                         | abled         |       |       |       |  |  |  |

| 5      | IER25       | R/W          | 0 = Timer  2  E                           | dge Interrupt Di                         | sabled        |       |       |       |  |  |  |

|        |             | D (14/       | 1 = Timer 1 E                             | dge Interrupt En                         | abled         |       |       |       |  |  |  |

| 4      | IER24       | R/W          | 0 = Timer 1 E                             | dge Interrupt Di                         | sabled        |       |       |       |  |  |  |

|        |             | D/M/         | 1 = NE57 Neg                              | gative Edge Inter                        | rupt Enabled  |       |       |       |  |  |  |

| 3      | IER23       | R/W          | 0 = NE57 Neg                              | gative Edge Inter                        | rupt Disabled | 1     |       |       |  |  |  |

| _      |             | D (14/       | 1 = PE56 Positi                           | itive Edge Interr                        | upt Enabled   |       |       |       |  |  |  |

| 2      | IER22       | R/W          | 0 = PE56 Positi                           | tive Edge Interr                         | upt Disabled  |       |       |       |  |  |  |

|        |             | D/M/         | 1 = PE55 Posi                             | 1 = PE55 Positive Edge Interrupt Enabled |               |       |       |       |  |  |  |

| 1      | IER21       | R/W          | 0 = PE55 Positive Edge Interrupt Disabled |                                          |               |       |       |       |  |  |  |

| •      |             | D/M/         | 1 = PE54 Positive Edge Interrupt Enabled  |                                          |               |       |       |       |  |  |  |

| 0      | IER20       | R/W          | 0 = PE54 Posi                             | tive Edge Interr                         | upt Disabled  |       |       |       |  |  |  |

October 15, 2019

#### W65C134S Datasheet

#### 2.8 Universal Asynchronous Receiver/Transmitters (UARTs)

The W65C134S has one full duplex Universal Asynchronous Receiver/Transmitter (UART) with programmable bit rates. The serial I/O functions are controlled by the Asynchronous Communication Control and Status Registers (ACSR). The serial bit rate is determined by Timer A for all modes for the UART's. The maximum data rate using the internal clock is 0.5MHz bits per second (FCLK = 8MHz). The Asynchronous Transmitter and Asynchronous Receiver can be independently enabled or disabled.

All transmitter and receiver bit rates will occur at one sixteenth of Timer A as selected.

Whenever Timer A is required as a timing source, it must be loaded with the hexadecimal code that selects the data rate for the serial I/O Port. Refer to Table 2.8.6-1 for a table of hexadecimal values that represent the desired data rate.

#### Standard UART Features

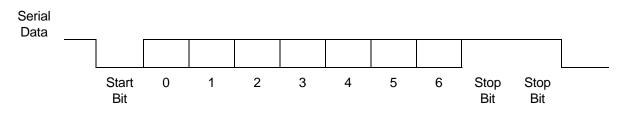

- 7 or 8 bit data with or without Odd or Even parity.

- The Transmitter has 1 stop bit with parity or 2 stop bits without parity.

- The Receiver requires only 1 stop bit for all modes.

- Both the Receiver and Transmitter have priority encoded interrupts for service routines.

- The Receiver has error detection for parity error, framing error, or over-run error conditions that may require re-transmission of the message.

- The Receiver Interrupt occurs due to a receiver data register full condition.

- The Transmitter Interrupt can be selected to occur on either the data register empty (end-of-byte transmission) or both the data register empty and the shift register empty (end-of-message transmission) condition.

#### 2.8.1 Transmitter Operation

The transmitter operation is controlled by the Asynchronous Control and Status Register (ACSR). The transmitter automatically adds a start bit, parity bit and one or two stop bits as defined by the ACSR. A word of transmitted data is 7 or 8 bits of data.

The Transmitter Data Register (ARTD) is located at addresses \$ and is loaded on a write. The Receiver is read at this same address.

#### 2.8.2 UART Data Register Description

| Addre | ess = \$0023       | ARTDx: U | ART Data Register Reset Value = 0 |                                 |             |        |        |        |  |  |

|-------|--------------------|----------|-----------------------------------|---------------------------------|-------------|--------|--------|--------|--|--|

| 7:0-> | ARTDx7             | ARTDx6   | ARTDx5                            | ARTDx4                          | ARTDx3      | ARTDx2 | ARTDx1 | ARTDx0 |  |  |

| Bit   | Name               | Access   | Description                       | 1                               |             |        |        |        |  |  |

| 7 0   |                    | R/W      | R = Read R                        | R = Read Receiver Data Register |             |        |        |        |  |  |

| 7 - 0 | <b>ARTDx</b> [7-0] | R/ VV    | W = Write T                       | ransmitter                      | Data Regist | er     |        |        |  |  |

The Transmitter Interrupt is controlled by the Asynchronous Control Status Register bit ACSRx1.

IRQATx = ACSRx0 ((ACSRx1B) (DATA REGISTER EMPTY) + (ACSRx1) (DATA REGISTER AND SHIFT REGISTER EMPTY))

#### 2.8.4 Receiver Operation

The receiver and its selected control and status functions are enabled when ACSRx5 is set to a "1". The data format must have a start bit, 7 or 8 data bits, and one stop bit or one parity bit and one stop bit. The receiver bit period is divided into 16 sub-intervals for internal synchronization. The receiver bit stream is synchronized by the start bit, and a strobe signal is generated at the approximate center of each incoming bit. The character assembly process does not start if the start bit signal is less than one-half the bit time after a low level is detected on the Receive Data Input. A framing error, parity error or an over-run will set ASCRx7 the receiver error detection bit. An over-run condition occurs when the receiver data register has not been read and new data byte is transferred from the receiver shift register.

#### 2.8.5 Data Timing for 7-bit Data without Parity and two stop bits.

The receiver requires only one stop bit but the transmitter supplies two stop bits for older system timing.

A receiver interrupt (IRQARx) is generated whenever the receiver shift register is transferred to the receiver data register.

October 15, 2019

W65C134S Datasheet

#### 2.8.6 UART RXD and TXD Data Rate Generation.

Timer 3 and 4 provide clock timing for the RXD and TXD data rate. Timer 3 and 4 operate as configured by Timer Control Register (TCRx) and Timer Enable Register (TERx) should be set up prior to enabling the UARTx.

The table below identifies the values to be loaded into Timer 3 and 4 to select standard data rates. Any data rate can be selected by using the formula:

N = (FCLK / (16 x bps)) - 1

N = decimal value to be loaded into timer using its hexadecimal equivalent FCLK = the clock frequency bps = bits per second data rate

Note that one may notice slight differences between the standard rate and the actual data rate. However, transmitter and receiver error of 1.5% or less is acceptable.

#### Table 2.9.6-1 Timer 3 and 4 Values for Baud Rate Selection

| Standard<br>Baud Rate | 1.8432MHz | 2.4576MHz | 3.6864MHz | 4.9152MHz | 6.1440MHz |

|-----------------------|-----------|-----------|-----------|-----------|-----------|

| 110                   | \$0416    | \$0573    | \$082E    | \$0AE8    | \$0DA2    |

| 150                   | \$02FF    | \$03FF    | \$05FF    | \$07FF    | \$09FF    |

| 300                   | \$017F    | \$01FF    | \$02FF    | \$03FF    | \$04FF    |

| 600                   | \$00BF    | \$00FF    | \$017F    | \$01FF    | \$027F    |

| 1200                  | \$005F    | \$007F    | \$00BF    | \$00FF    | \$013F    |

| 1800                  | \$003F    | \$0054    | \$007F    | \$00AA    | \$00DF    |

| 2400                  | \$002F    | \$003F    | \$005F    | \$007F    | \$009F    |

| 4800                  | \$0017    | \$001F    | \$002F    | \$003F    | \$004F    |

| 9600                  | \$000B    | \$000F    | \$0017    | \$001F    | \$0027    |

| 19200                 | \$0005    | \$0007    | \$000B    | \$000F    | \$0013    |

| 38400                 | \$0002    | \$0003    | \$0005    | \$0007    | \$0009    |

| 57600                 | \$0001    | \$0002    | \$0003    | \$0004    | \$0006    |

Note: Shading indicates transmitter or receiver error greater than 1.5%.

W65C134S Datasheet

#### 2.8.7 Asynchronous Control and Status Registers (ACSR) Description

The Asynchronous Control and Status Register (ACSR) enables the Receiver and Transmitter and holds information on communication status error conditions.

| Addres | ss = \$0022 | ACSR: Asy | nchronous C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ontrol and St                                                                                                                                                                                                                                                                                                      | atus Regist    | er           | Reset Va      | lue = 0x00 |  |  |

|--------|-------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|---------------|------------|--|--|

| 7:0->  | ACSR7       | ACSR6     | ACSR5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ACSR4                                                                                                                                                                                                                                                                                                              | ACSR3          | ACSR2        | ACSR1         | ACSR0      |  |  |

| Bit    | Name        | Access    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                    |                |              |               |            |  |  |

| 7      | ACSR7       | R/W       | <ul> <li>1 = <u>Receiver Error Flag</u>. The Receiver logic detects three possible error conditions and sets ACSR7: parity, framing or over-run. A parity error occurs when the parity bit received does not match the parity generated on the receive data. A framing error occurs when the stop bit time finds a "0" instead of a "1". An over-run occurs when the last data in the Receiver Data Register has not been read and new data is transferred from the <u>Receive Shift Register</u>.</li> <li>0 = Cleared by writing a "1" to ACSR7. Writing a "0" to ACSR7 has not effect on ACSR7.</li> </ul>                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                    |                |              |               |            |  |  |

| 6      | ACSR6       | R/W       | among routir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 = Software Semaphore. ACSRx6 may be used for communications<br>among routines which access the UART. This bit has no effect on the<br>UART operation. The bit can be thought of as a manually set busy<br>signal.                                                                                                |                |              |               |            |  |  |

|        |             |           | 1 = Enable F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Receiver, Rece                                                                                                                                                                                                                                                                                                     | eiver Interrup | t, and RXD   | ) output on F | Port 6.    |  |  |

| 5      | ACSR5       | R/W       | 0 = Disable I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                    |                |              |               |            |  |  |

| 4      | ACSR4       | R/W       | data register<br>0 = Odd pari                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>1 = Even parity is enabled. Even parity is when the number of ones in the data register plus parity bit equal an even number of "1's".</li> <li>0 = Odd parity is enabled. Odd parity is generated where the number of ones is the data register plus parity bit equal an odd number of "1's".</li> </ul> |                |              |               |            |  |  |

| 3      | ACSR3       | R/W       | 1 = Enable P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Parity.                                                                                                                                                                                                                                                                                                            |                |              |               |            |  |  |

| 5      |             | 10.00     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                    |                |              |               |            |  |  |

| 2      | ACSR2       | R/W       | <ul> <li>0 = Disable Parity</li> <li>1 = Transmitter and Receiver send and receive 8-bit data. The<br/>Transmitter sends 11 bits of information (one start, 8 data, one parity and<br/>one stop or two stop bits). The Receiver receives 10 or 11 bits of<br/>information (one start, 8 data, one stop or one parity and one stop bit).</li> <li>0 = Transmitter and Receiver send and receive 7-bit data. The<br/>Transmitter sends a total of 10 bits of information (one start, 7 data, one<br/>parity and one stop or 2 stop bits). The Receiver receives 9 or 10 bits of<br/>information (one start, 7 data, and one stop or one stop and one parity<br/>bits). When writing to the Transmitter in seven bit mode, bit 7 is<br/>discarded. When reading from the receive data register during seven bit<br/>mode, bit 7 is always zero.</li> </ul> |                                                                                                                                                                                                                                                                                                                    |                |              |               |            |  |  |

| 1      | ACSR1       | R/W       | <ul> <li>1 = Transmitter Interrupt occurs due to both the Transmitter Data and<br/>Shift register empty condition (end-of-message transmission. ACSR0 = 0<br/>clears this bit if set.</li> <li>0 = Transmitter Interrupt occurs due to a Transmitter Data Register<br/>Empty condition (end-of-byte transmission).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                    |                |              |               |            |  |  |

| 0      | ACSR0       | R/W       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Transmitter, T                                                                                                                                                                                                                                                                                                     |                |              |               |            |  |  |

|        |             |           | 0 = Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | transmitter, T                                                                                                                                                                                                                                                                                                     | ransmitter Ir  | nterrupt, an | id TXD on F   | ort 6      |  |  |

October 15, 2019

W65C134S Datasheet

#### 2.9 The Serial Interface Bus (SIB)

The Serial Interface Bus (SIB) is configured as a token passing Local Area Network, and is intended for inter-chip communications in parallel processing applications. The Serial Interface Bus has four pins associated with its use: CHIN CHOUT, SDAT, and SCLK (see Section 2.19 for more information). The SIB has seven (7) registers associated with its use: STATE, SR0, SR1, SR2, SR3, SCSR, and BAR.

#### 2.9.1 The STATE Register

The STATE register is a read-only register that provides the host processor with the timing state of the SIB (see Figure 1-13 for more information on activities during each timing state). The STATE register is the decoded output of a "state machine" that counts up from 0 to 37 and then back to 0 on positive transitions of SCLK. Only one decoded output is asserted at a time. STATE has the same value at the same time in all devices and is used to synchronize message transfer. It is reset to State 0 upon system RESET.

STATE is normally read only during manufacturing test. A read of the state register can produce invalid results if the SCLK is not synchronous with the processor clock. When the SCLK is enabled on the chip with its MPU, it is always synchronized with the SIB.

| Addres | ss = \$0014 | STATE: Sta | ate Register Reset Value = 0x00 |              |        |        | lue = 0x00 |        |