## General description

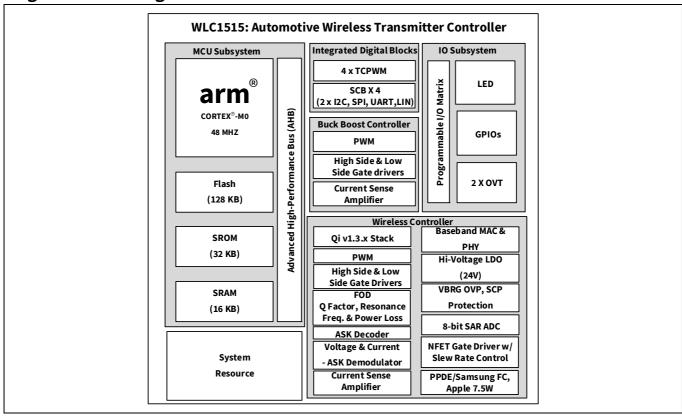

WLC1515 is a highly integrated, Qi 1.3.x certifiable wireless power transmitter with an integrated buckboost controller. WLC1515 is ideal for up to 15-W charging applications.

WLC1515 has integrated gate drivers for the BuckBoost and inverter power supplies that are necessary for wireless transmitter applications. WLC1515 supports a wide input voltage range and offers many programmable features for creating distinct wireless transmitter solutions.

WLC1515 is a highly programmable wireless power transmitter solution with an on-chip 32-bit Arm® Cortex®-M0 processor, 128KB flash, 16KB RAM, and 32KB ROM. It also includes various analog and digital peripherals such as ADC, PWMs, and timers. The inclusion of a fully programmable MCU with analog and digital peripherals enables scalable multi-coil wireless charging solutions for free positioning transmitter designs.

## **Potential applications**

- Wireless charging pads for extended power profile (EPP) (15W) and basic power profile (BPP) (5W)

- Portable accessories

- In-cabin wireless charging application

- Automotive wireless charger

#### **Features**

- Qi v1.3.x extended power profile (EPP) and basic power profile (BPP) transmitter (MP-A13 and similar)

- · Free positioning

- Multiple coils (single coil, double coils, and three coils)

- AEC-Q100 qualified

- Integrated buckboost controller for VBRIDGE (VBRG)

- · Integrated gate drivers for buckboost converter and inverter

- · Integrated Q factor detection

- Integrated FSK modulator

- Integrated ASK decoder

- Integrated FOD by power loss, Ofactor, and resonance frequency

- Wide input voltage range: 4.5V-24V

- Communication ports: I<sup>2</sup>C, UART, SPI, and LIN

#### Protection

- Overcurrent protection (OCP), overvoltage protection (OVP)

- Supports over-temperature protection through integrated ADC circuit and internal temperature sensor

#### Temperature range

- Supports automotive ambient temperature range (-40°C to +105°C) with 125°C operating junction temperature

#### Package

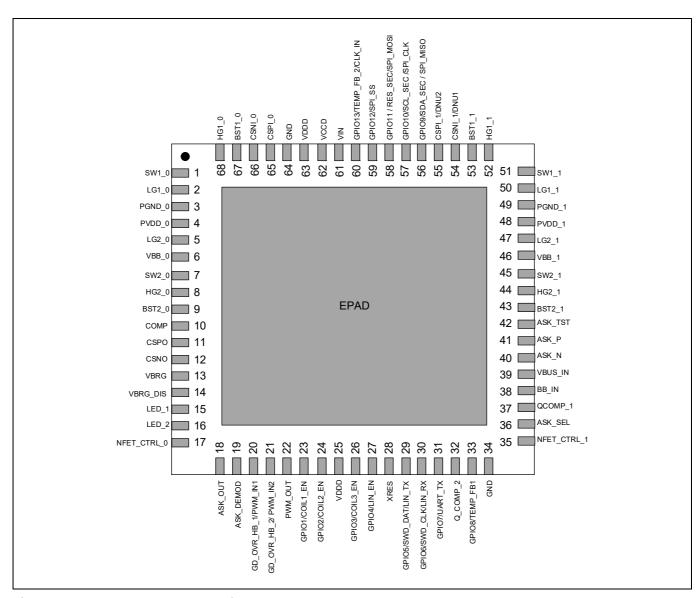

- 68-pin QFN, wettable flank, AEC-Q100

infineon

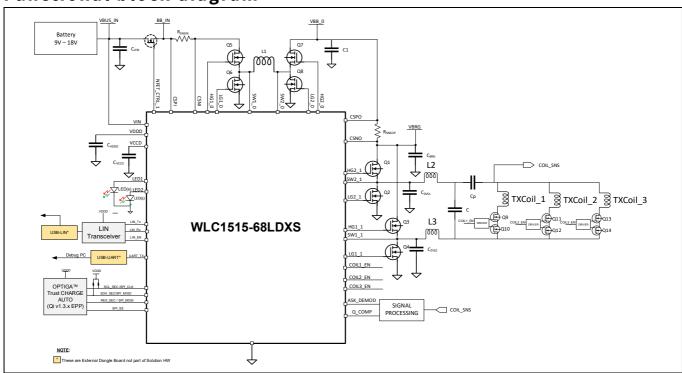

Functional block diagram

## Functional block diagram

## Logic block diagram

#### Note

1. Customers need to acquire their own licensing for Samsung FC.

Table of contents

## Table of contents

| General description                                                               | 1  |

|-----------------------------------------------------------------------------------|----|

| Potential applications                                                            |    |

| Features                                                                          |    |

| Functional block diagram                                                          |    |

| Logic block diagram                                                               |    |

| Table of contents                                                                 |    |

| 1 Application diagram for 15W automotive transmitter solution with MP-A13 Tx coil |    |

| 2 Pin information                                                                 |    |

| 3 Electrical specifications                                                       |    |

| 3.1 Absolute maximum ratings                                                      |    |

| 3.2 Device-level specifications                                                   |    |

| 3.3 DC specifications                                                             |    |

| 3.3.1 CPU                                                                         |    |

| 3.3.2 GPIO                                                                        |    |

| 3.3.3 XRES and POR                                                                |    |

| 3.4 Digital peripherals                                                           |    |

| 3.4.1 Inverter pulse-width modulation (PWM) for GPIO pins                         |    |

| 3.4.2 I2C, UART, SWD interface, SPI, and LIN                                      |    |

| 3.4.3 Memory                                                                      |    |

| 3.5 System resources                                                              | 19 |

| 3.5.1 Internal main oscillator clock                                              | 19 |

| 3.5.2 ADC                                                                         | 20 |

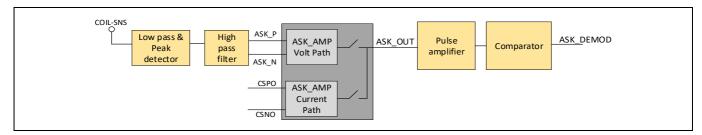

| 3.5.3 Current sense amplifier (CSA) / ASK amplifier (ASK_P and ASK_N)             | 20 |

| 3.5.4 VIN UV/OV                                                                   |    |

| 3.5.5 Voltage regulation - VBRG                                                   |    |

| 3.5.6 NFET gate driver specifications                                             |    |

| 3.5.7 BuckBoost PWM controller                                                    |    |

| 3.5.8 Thermal                                                                     |    |

| 4 Functional overview                                                             |    |

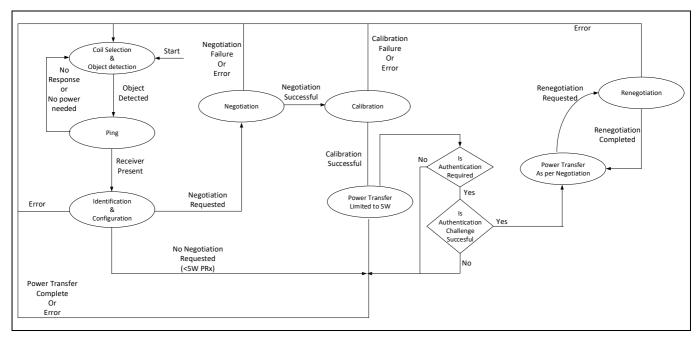

| 4.1 Wireless power transmitter                                                    |    |

| 4.2 WPC system control                                                            |    |

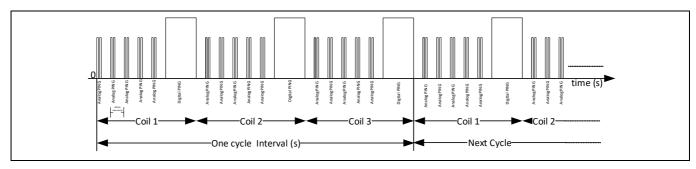

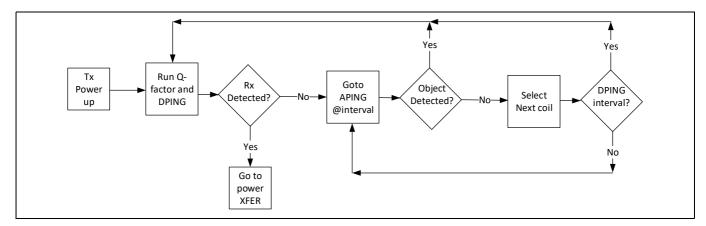

| 4.2.1 Coil selection and object detection phase                                   |    |

| 4.2.2 Digital ping phase                                                          |    |

| 4.2.3 Identification and configuration phase                                      |    |

| 4.2.4 Negotiation                                                                 |    |

| 4.2.5 Calibration                                                                 |    |

| 4.2.6 Authentication                                                              |    |

| 4.2.7 Renegotiation phase                                                         |    |

| 4.2.8 Power transfer phase                                                        |    |

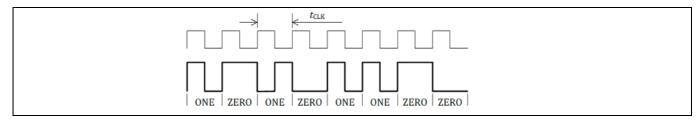

| 4.2.9 Bidirectional in-band communication interface                               |    |

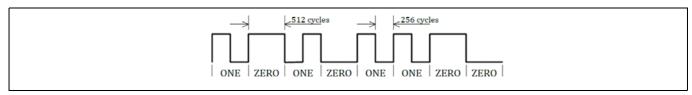

| 4.3 Communication from Tx to Rx - FSK                                             |    |

| 4.4 Communication from Rx to Tx - ASK                                             |    |

| 4.5 Demodulation                                                                  |    |

| 4.6 Inverter                                                                      |    |

| 4.7 Rx detection                                                                  |    |

| 4.7.1 Foreign object detection (FOD)                                              | 29 |

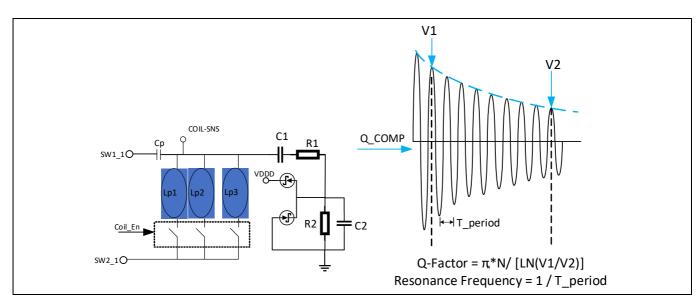

| 4.7.2 Q factor FOD and resonance frequency FOD                                    |    |

| 4.7.3 Power loss FOD                                                              |    |

| 4.7.4 Over temperature FOD                                                        |    |

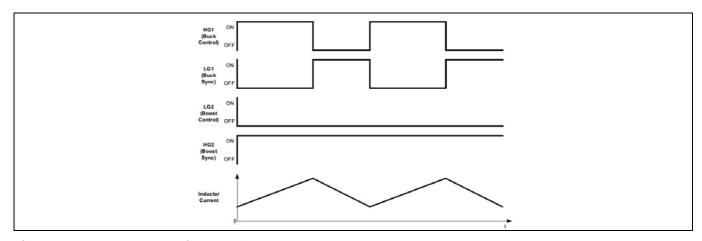

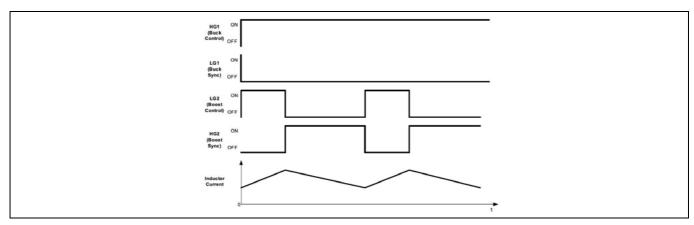

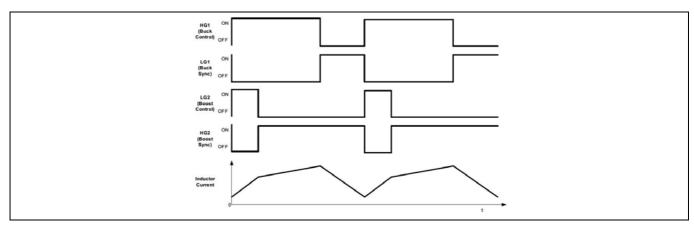

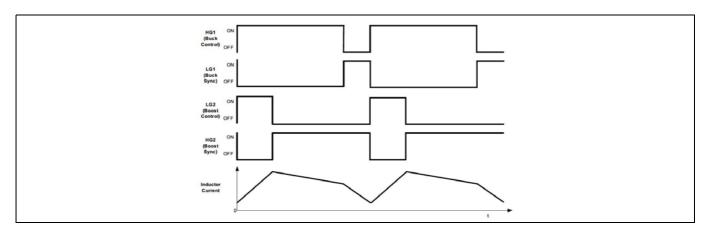

| 4.8 BuckBoost regulator4.9 BuckBoost operating modes4.9 BuckBoost operating modes |    |

| 4.J DUCKDOOSI OPELATIIK IIIOUES                                                   |    |

2023-05-18

### Table of contents

| 4.9.1 BuckBoost converter                           | 31  |

|-----------------------------------------------------|-----|

| 4.9.2 Pulse-width modulator (PWM)                   | 33  |

| 4.9.3 Pulse skipping mode (PSM)                     |     |

| 4.9.4 Forced-continuous-conduction mode (FCCM)      | 33  |

| 4.9.5 Overvoltage protection (OVP)                  |     |

| 4.9.6 Overcurrent protection (OCP)                  |     |

| 4.9.7 MCU                                           | 33  |

| 4.9.8 ADC                                           | 34  |

| 4.9.9 Serial communications block (SCB)             | 34  |

| 4.9.10 I/O subsystem                                | 34  |

| 4.9.11 LDOs (VDDD and VCCD)                         |     |

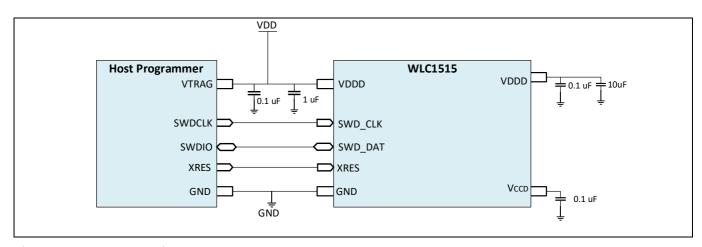

| 5 Programming the WLC1515 device                    |     |

| 5.1 Programming the device Flash over SWD interface | 35  |

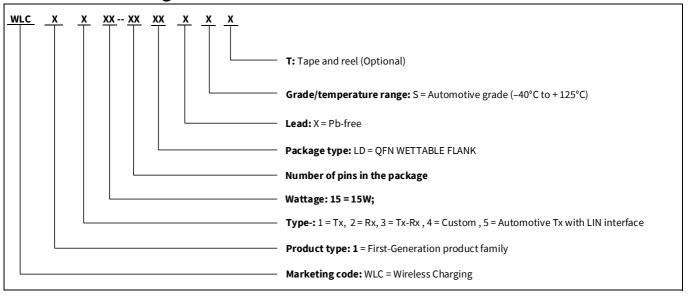

| 6 Ordering information                              | 36  |

| 6.1 Ordering code definitions                       | 36  |

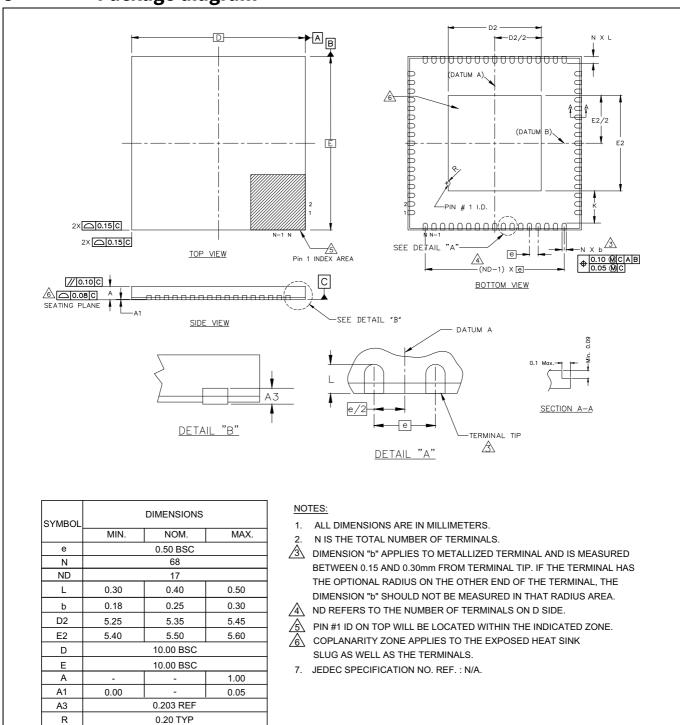

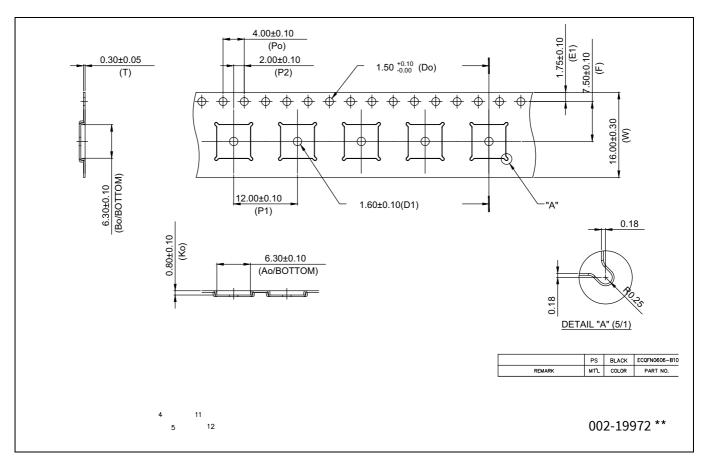

| 7 Packaging                                         | 37  |

| 8 Package diagram                                   | 38  |

| 9 Acronyms                                          |     |

| 10 Document conventions                             | 42  |

| 10.1 Units of measure                               |     |

| Pavision history                                    | /12 |

Application diagram for 15W automotive transmitter solution with MP-A13 Tx coil

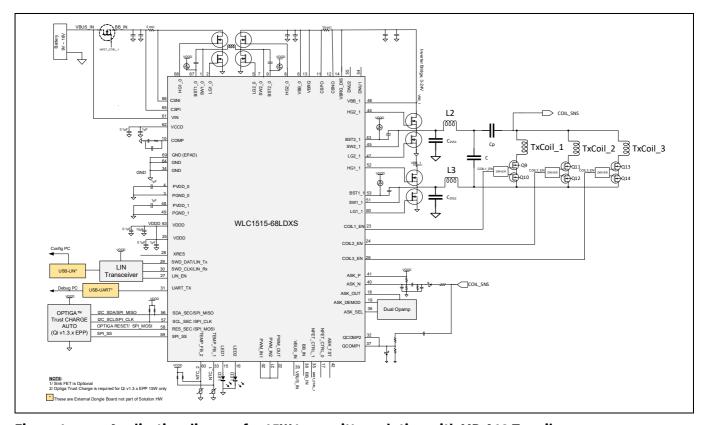

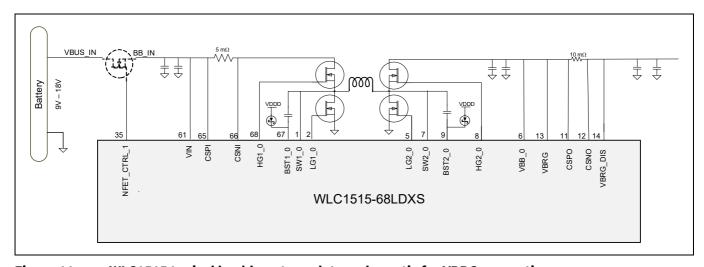

#### Application diagram for 15W automotive transmitter solution 1 with MP-A13 Tx coil

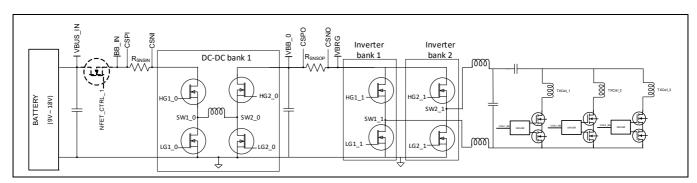

Figure 1 illustrates a typical application of WLC1515 for 15W, Qi v1.3.x certifiable transmitter for fixed frequency and voltage control-based MP-A13 Qi transmitter coil. The input power to the system is through an input connector, powering the buckboost converter. The buckboost converter powers the full bridge inverter which in turn drives the transmitter coil. The WLC1515 controls the inverter bridge voltage (VBRG) using the buckboost converter to regulate the power flow to the transmitter coil powering the receiver. The WLC1515 gives control signal to connect one coil to resonant circuits at a time. The WLC1515 provides two dedicated output pin LED0, and LED1 to indicate the status of the Wireless power transmitter. The WLC1515 provides internal device thermal management (DIE temperature) as well as external device thermal management function with an external NTC thermistor connector between TEMP\_FB\_1 and TEMP\_FB\_2 to GND as shown in Figure 1. A dual opamp is used for converting the amplitude shift key (ASK) modulated power signal into binary signal. WLC1515 uses a digital logic for decoding the binary signals. The OPTIGA™ Trust Security IC is interfaced over I2C/SPI for authentication requirements per Qi v1.3.x.

Figure 1 Application diagram for 15W transmitter solution with MP-A13 Tx coil

infineon

Pin information

## **2** Pin information

### Table 1 WLC1515 pinouts

|      |          | WLC1515                                                        |                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|------|----------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin# | Pin name | Example pin assignment<br>for 15W 3-Coil<br>MP-A13 transmitter | Description                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 1    | SW1_0    |                                                                | Negative power rail of DC-DC converter bank 1's buck high-side gate driver. This is also connected to one input terminal of zero current detection of buck low-side gate driver.  Connect to the switch node (inductor) on the buck (input) side. Use a short and wide trace to minimize the inductance and resistance of this connection. |  |  |  |  |

| 2    |          | LG1_0                                                          | Buck low-side gate driver output of (DC-DC bank 1). Connect to the buck (input) side sync (low-side) FET gate. Use a wide trace to minimize inductance of this connection.                                                                                                                                                                 |  |  |  |  |

| 3    |          | PGND_0                                                         | Ground for gate driver (DC-DC). Connect all grounds (GND) and PGND pins (PNGD_0 and PGND_1) together. Connect directly PCB ground plane and exposed pad (EPAD).                                                                                                                                                                            |  |  |  |  |

| 4    |          | PVDD_0                                                         | Supply of low-side gate driver of DC-DC converter bank 1. Connect to VDDD. Use 1 $\mu$ F and 0.1 $\mu$ F bypass capacitors as close to the WLC1515 IC as possible.                                                                                                                                                                         |  |  |  |  |

| 5    |          | LG2_0                                                          | Boost low-side gate driver output of DC-DC bank 1.<br>Connect to the boost (output) side control (low-side) FET gate. Use a wide trace to minimize inductance of this connection.                                                                                                                                                          |  |  |  |  |

| 6    | VBB_0    |                                                                | Input rail of inverter bridge, connected to output of the buckboost converter. Connect this to the buckboost side terminal of current sense resistor for inverter bridge input current sensing. Use a dedicated (Kelvin) trace for this connection.                                                                                        |  |  |  |  |

| 7    |          | SW2_0                                                          | Negative power rail of DC-DC converter bank 1's boost high-side gate driver. This is also connected to one input terminal of RCP of boost high-side gate driver.  Connect to the switch node (inductor) on the boost (output) side. Use a short and wide trace to minimize the inductance and resistance of this connection.               |  |  |  |  |

| 8    |          | HG2_0                                                          | Boost high-side gate driver output of DC-DC converter bank 1.<br>Connect to the boost (output) side sync (high-side) FET gate. Use a wide trace to minimize inductance of this connection.                                                                                                                                                 |  |  |  |  |

| 9    |          | BST2_0                                                         | Boosted power supply of DC-DC bank 1's boost high-side gate driver. Bootstrap capacitor node. Connect Schottky diode from VDDD to BST2_0. Also, connect a bootstrap capacitor from this pin to SW2_0.                                                                                                                                      |  |  |  |  |

| 10   |          | COMP                                                           | Error amplifier (EA) output for buckboost controller.<br>Connect the RC compensation network to GND.                                                                                                                                                                                                                                       |  |  |  |  |

| 11   |          | CSPO                                                           | Positive input of current sensing amplifier (CSA) of inverter bridge input current. Connect to positive terminal of the output current sense resistor (VBB_0).                                                                                                                                                                             |  |  |  |  |

| 12   |          | CSNO                                                           | Negative input of current sensing amplifier of inverter bridge input current. Connect to negative terminal of the current sense resistor.                                                                                                                                                                                                  |  |  |  |  |

| 13   |          | VBRG                                                           | Feedback pin for buckboost output voltage. Connect it to buckboost output before inverter bridge input current sense resistor.                                                                                                                                                                                                             |  |  |  |  |

| 14   |          | VBRG_DIS                                                       | Inverter input power supply voltage. Connect to buckboost output before inverter bridge input current sense resistor. Used as weak discharge of VBRG.                                                                                                                                                                                      |  |  |  |  |

| 15   |          | LED_1                                                          | LED1 for 15W MP-A13 application/configurable GPIO. Float this pin if it is not used.                                                                                                                                                                                                                                                       |  |  |  |  |

| 16   |          | LED_2                                                          | LED2 for 15W MP-A13 application/configurable GPIO. Float this pin if it is not used.                                                                                                                                                                                                                                                       |  |  |  |  |

| 17   |          | NFET_CTRL_0                                                    | NFET gate driver output. Float this pin if it is not used.                                                                                                                                                                                                                                                                                 |  |  |  |  |

Pin information

Table 1 WLC1515 pinouts (continued)

| rable | T MFC12     | 15 pinouts (continued)                                         |                                                                                                                                                                                    |

|-------|-------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |             | WLC1515                                                        |                                                                                                                                                                                    |

| Pin#  | Pin name    | Example pin assignment<br>for 15W 3-Coil<br>MP-A13 transmitter | Description                                                                                                                                                                        |

| 18    |             | ASK_OUT                                                        | ASK voltage/current sensing path. IC output for ASK signal processing.                                                                                                             |

| 19    | A           | ASK_DEMOD                                                      | Input for ASK signal decoding. Connect external ASK comparator output to this pin. Short this pin to pin-36 (ASK_SEL).                                                             |

| 20    | GD_OVR_HB_1 | PWM_IN1                                                        | Inverter gate driver input signal for inverter bank 1. Short this pin to pin-22. PWM_OUT.                                                                                          |

| 21    | GD_OVR_HB_2 | PWM_IN2                                                        | Inverter gate driver input signal for inverter bank 2. Short this pin to pin-22 PWM_OUT.                                                                                           |

| 22    |             | PWM_OUT                                                        | Inverter PWM signal output used for the inverter gate drive inputs. Short this pin to pin 20 (PWM_IN1) and pin 21 (PWN_IN2).                                                       |

| 23    | GPIO1       | COIL1_EN                                                       | Default Coil1_EN / configurable GPIO.                                                                                                                                              |

| 24    | GPIO2       | COIL2_EN                                                       | Default Coil2_EN / configurable GPIO.                                                                                                                                              |

| 25    |             | VDDD                                                           | VDDD 5V LDO output from VIN. Connect a ceramic bypass capacitor (recommended value $1\mu F$ ) from this pin to GND close to the IC. Connect all VDDD pins together.                |

| 26    | GPIO3       | COIL3_EN                                                       | Default Coil3_EN / configurable GPIO.                                                                                                                                              |

| 27    | GPIO4       | LIN_EN                                                         | Configurable GPIO / LIN transceiver enable. Float this pin if it is not used.                                                                                                      |

| 28    |             | XRES                                                           | External reset – active low, internally pulled-up (~6k $\Omega$ ). Float this pin if it is not used.                                                                               |

| 29    | GPIO5       | SWD_DAT/LIN_TX                                                 | Used for I <sup>2</sup> C/SWD register access or programming/LIN transceiver Tx / configurable GPIO.                                                                               |

| 30    | GPIO6       | SWD_CLK/LIN_RX                                                 | Used for I <sup>2</sup> C/SCL register access or programming/LIN transceiver Rx / configurable GPIO.                                                                               |

| 31    | GPIO7       | UART_TX                                                        | Default UART Tx for debug/configurable GPIO. Float this pin if it is not used.                                                                                                     |

| 32    |             | Q_COMP_2                                                       | Q-factor based foreign object detection (FOD) pre-charge measurement input for frequency counting. Short this pin to pin 37 (QCOMP1).                                              |

| 33    | GPIO8       | TEMP_FB_1                                                      | Tx coil 1 temperature measurement via thermistor monitoring for 15W MP-A13 application/configurable GPIO. Float this pin if it is not used.                                        |

| 34    |             | GND                                                            | Ground. Connect directly to the EPAD and to ground plane                                                                                                                           |

| 35    | NFET_CTRL_1 | NC                                                             | NFET gate driver output. Float this pin if it is not used.                                                                                                                         |

| 36    |             | ASK_SEL                                                        | Input for ASK signal decoding. Short this pin to pin-19 (ASK_DEMOD).                                                                                                               |

| 37    |             | QCOMP_1                                                        | Q-factor based FOD pre-charge measurement input for peak voltage detect. Short this pin to pin 32 (QCOMP2).                                                                        |

| 38    |             | BB_IN                                                          | Input voltage to buckboost (DC-DC) controller. Connect to connector's positive pin. If EMI filter/choke is used after connector then connect it to output of the EMI filter/choke. |

| 39    |             | VBUS_IN                                                        | Input of feedback voltage of error amplifier of DC-DC bank 1<br>Connect to the connector positive node between the output current<br>sense resistor and the VBUS provider NFET.    |

| 40    |             | ASK_N                                                          | Negative input of ASK voltage sensing signal input to internal amplifier.                                                                                                          |

| 41    |             | ASK_P                                                          | Positive input of ASK voltage sensing signal input to internal amplifier.                                                                                                          |

| 42    |             | ASK_TST                                                        | ASK voltage sensing comparator output. Float this pin if it is not used.                                                                                                           |

|       |             |                                                                |                                                                                                                                                                                    |

Pin information

Table 1WLC1515 pinouts (continued)

| Table 1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 515 pillouts (continued)                                       | 1                                                                                                                                                                                                                                |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | WLC1515                                                        |                                                                                                                                                                                                                                  |  |

| Pin#    | Pin name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Example pin assignment<br>for 15W 3-Coil<br>MP-A13 transmitter | Description                                                                                                                                                                                                                      |  |

| 43      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BST2_1                                                         | Bootstrap power supply for (inverter bank 2) inverter high-side gate driver. Connect a capacitor (recommended value 0.1µF) from this pin to SW2_1. Also, connect a Schottky diode from VDDD to BST2_1.                           |  |

| 44      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HG2_1                                                          | High-side gate driver for inverter FET (inverter bank 2). Connect to the Inverter bank 2, high-side FET gate. Use a wide trace to minimize inductance of this connection.                                                        |  |

| 45      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SW2_1                                                          | Inverter switching node for inverter bank 2. Connect this pin to the inverter bank 2 switching node with a short and wide trace.                                                                                                 |  |

| 46      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VBB_1                                                          | Inverter input voltage sense. Connect to inverter input voltage, after the current sense resistor. Use a dedicated (Kelvin) trace for this connection.                                                                           |  |

| 47      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LG2_1                                                          | Low-side gate driver for inverter FET (inverter bank 2). Connect to the inverter bank 2 low side FET gate.                                                                                                                       |  |

| 48      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PVDD_1                                                         | Connect to VDDD pin. Connect bypass capacitors (recommended values 1μF and 0.1μF) as close to the IC as possible.                                                                                                                |  |

| 49      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PGND_1                                                         | Ground for inverter gate driver. Connect directly to PCB ground plane and EPAD. Connect all GND and PGND pins together.                                                                                                          |  |

| 50      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LG1_1                                                          | Low-side gate driver for inverter FET (inverter bank 1). Connect to the inverter bank 1 Low side FET gate.                                                                                                                       |  |

| 51      | SW1_1 Inverter switching node for inverter bank 1. Connect this pin to the last of the las |                                                                |                                                                                                                                                                                                                                  |  |

| 52      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HG1_1                                                          | High-side gate driver for inverter FET (inverter bank 1). Connect to the inverter bank 1 high side FET gate.                                                                                                                     |  |

| 53      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BST1_1                                                         | Bootstrap power supply for (inverter bank 1) inverter high-side gate driver. Connect a capacitor (recommended values $0.1\mu\text{F}$ ) from this pin to SW1_1. Also, connect a Schottky diode from VDDD to BST1_1.              |  |

| 54      | CSNI_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DNU1                                                           | Negative input of input current sense amplifier for inverter. Float this pin if it is not used.                                                                                                                                  |  |

| 55      | CSPI_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DNU2                                                           | Positive input of input current sense amplifier for inverter. Float this pin if it is not used.                                                                                                                                  |  |

| 56      | GPIO9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SDA_SEC / SPI_MISO                                             | Used for interfacing as Master, with OPTIGA™ Trust I <sup>2</sup> C SDA or With OPTIGA™ Trust SPI MISO. The pin is configured for open drain connection, connect an external pull-up resistor. Float this pin if it is not used. |  |

| 57      | GPIO10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SCL_SEC /SPI_CLK                                               | Used for interfacing with OPTIGA™ Trust I <sup>2</sup> C SCL or With OPTIGA™ Trust SPI CLK. The pin is configured for open drain connection, connect an external pull-up resistor. Float this pin if it is not used.             |  |

| 58      | GPIO11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RES_SEC/SPI_MOSI                                               | RESET for OPTIGA™ Trust IC (I2C Version) / MOSI for OPTIGA™ Trust IC Chip select for OPTIGA™ TRUST IC(SPI Version) / Configurable GPIO.                                                                                          |  |

| 59      | GPIO12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SPI_SS                                                         | Configured for using OPTIGA™ Trust in low power mode. Configurable GPIO.                                                                                                                                                         |  |

| 60      | GPIO13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TEMP_FB_2/CLK_IN                                               | Tx coil 2 temperature measurement via thermistor monitoring for 15W MP-A13 application/External Clock / configurable GPIO. Float this pin if it is not used.                                                                     |  |