# nRF9160

**Product Specification**

v1.2

# nRF9160 features

#### Features:

#### Microcontroller:

- ARM Cortex -M33

- 243 EEMBC CoreMark score running from flash memory

- Data watchpoint and trace (DWT), embedded trace macrocell (ETM), and instrumentation trace macrocell (ITM)

- Serial wire debug (SWD)

- Trace port

- 1 MB flash

- 256 kB low leakage RAM

- ARM Trustzone

- ARM Cryptocell 310

- Up to 4x SPI master/slave with EasyDMA

- Up to 4x I2C compatible two-wire master/slave with EasyDMA

- Up to 4x UART (CTS/RTS) with EasyDMA

- I2S with EasyDMA

- Digital microphone interface (PDM) with EasyDMA

- 4x pulse width modulator (PWM) unit with EasyDMA

- 12-bit, 200 ksps ADC with EasyDMA eight configurable channels with programmable gain

- 3x 32-bit timer with counter mode

- 2x real-time counter (RTC)

- Programmable peripheral interconnect (PPI)

- 32 general purpose I/O pins

- Single supply voltage: 3.0 5.5 V

- All necessary clock sources integrated

- Package: 10 × 16 x 1.04 mm LGA

#### LTE modem:

- Transceiver and baseband

- 3GPP LTE release 13 Cat-M1 and Cat-NB1 compliant

- 3GPP release 13 coverage enhancement

- 3GPP LTE release 14 Cat-NB2 compliant

- GPS receiver

- GPS L1 C/A supported

- RF transceiver for global coverage

- Up to 23 dBm output power

- -108 dBm sensitivity (LTE-M) for low band, -107 dBm for mid band

- Single 50 Ω antenna interface

- LTE band support in hardware:

- Cat-M1: B1, B2, B3, B4, B5, B8, B12, B13, B14, B17, B18, B19,

B20, B25, B26, B28, B66

- Cat-NB1/NB2: B1, B2, B3, B4, B5, B8, B12, B13, B17, B18, B20, B25, B26, B28, B66

- Supports SIM and eSIM with an ETSI TS 102 221 compatible UICC interface

- Power saving features: DRX, eDRX, PSM

- IP v4/v6 stack

- Secure socket (TLS/DTLS) API

#### Current consumption @ 3.7 V:

- Power saving mode (PSM) floor current: 4 μA

- Application core idle: 1.8 μA

- Modem: 2.2 μA

- eDRX @ 82.91s: 21 μA in Cat-M1, 37 μA in Cat-NB1 (UICC included)

#### Applications:

- Sensor networks

- Logistics and asset tracking

- Smart energy

- Smart building automation

- Smart agriculture

- Industrial

- Retail and monitor devices

- Medical devices

- Wearables

# Contents

|   | nRF9160 features.                                                | ii   |

|---|------------------------------------------------------------------|------|

| 1 | Revision history.                                                | . 9  |

| 2 | About this document.                                             | 10   |

|   | 2.1 Document status                                              | . 10 |

|   | 2.2 Peripheral chapters                                          |      |

|   | 2.3 Register tables                                              |      |

|   | 2.3.1 Fields and values                                          |      |

|   | 2.3.2 Permissions                                                |      |

|   | 2.4 Registers                                                    |      |

|   | 2.4.1 DUMMY                                                      |      |

| 3 | Product overview.                                                | 13   |

|   | 3.1 Introduction                                                 | . 13 |

|   | 3.2 Block diagram                                                |      |

|   | 3.3 Peripheral interface                                         |      |

|   | 3.3.1 Peripheral ID                                              |      |

|   | 3.3.2 Peripherals with shared ID                                 |      |

|   | 3.3.3 Peripheral registers                                       |      |

|   | 3.3.4 Bit set and clear                                          |      |

|   | 3.3.5 Tasks                                                      |      |

|   | 3.3.6 Events                                                     |      |

|   | 3.3.7 Publish / Subscribe                                        | 17   |

|   | 3.3.8 Shortcuts                                                  |      |

|   | 3.3.9 Interrupts                                                 |      |

|   | 3.3.10 Secure/non-secure peripherals                             |      |

| 4 | Application core                                                 | 19   |

|   | • •                                                              | _    |

|   | 4.1 CPU                                                          |      |

|   | 4.1.1 CPU and support module configuration                       |      |

|   | 4.1.2 Electrical specification                                   |      |

|   | 4.2 Memory                                                       | . 20 |

|   | 4.2.1 Memory map                                                 |      |

|   | 4.2.3 Peripheral access control capabilities                     |      |

|   | 4.3 VMC — Volatile memory controller                             | . 26 |

|   | 4.3.1 Registers                                                  |      |

|   | 4.4 NVMC — Non-volatile memory controller                        |      |

|   | 4.4.1 Writing to flash                                           |      |

|   | 4.4.2 Erasing a secure page in flash                             |      |

|   | 4.4.3 Erasing a non-secure page in flash                         |      |

|   | 4.4.4 Writing to user information configuration registers (UICR) | . 29 |

|   | 4.4.5 Erase all                                                  |      |

|   | 4.4.6 NVMC protection mechanisms                                 |      |

|   | 4.4.7 Cache                                                      |      |

|   | 4.4.8 Registers                                                  |      |

|   | 4.4.9 Electrical specification                                   |      |

|   | 4.5 FICR — Factory information configuration registers           |      |

4418\_1315 v1.2 iii

|   | 4.5.1 Registers                                                                                           | 35       |

|---|-----------------------------------------------------------------------------------------------------------|----------|

|   | 4.6 UICR — User information configuration registers                                                       | 40       |

|   | 4.6.1 Registers                                                                                           | 40       |

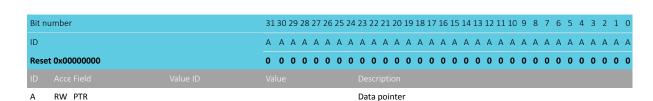

|   | 4.7 EasyDMA                                                                                               |          |

|   | 4.7.1 EasyDMA error handling                                                                              | 46       |

|   | 4.7.2 EasyDMA array list                                                                                  |          |

|   | 4.8 AHB multilayer interconnect                                                                           | 47       |

|   |                                                                                                           |          |

| 5 | Power and clock management.                                                                               |          |

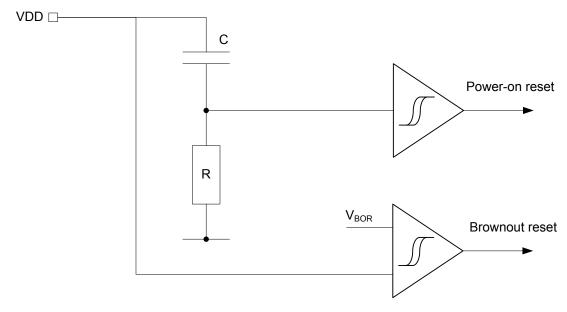

|   | 5.1 Functional description                                                                                |          |

|   | 5.1.1 Power management                                                                                    |          |

|   | 5.1.2 Power supply                                                                                        |          |

|   | 5.1.3 Power supply monitoring                                                                             |          |

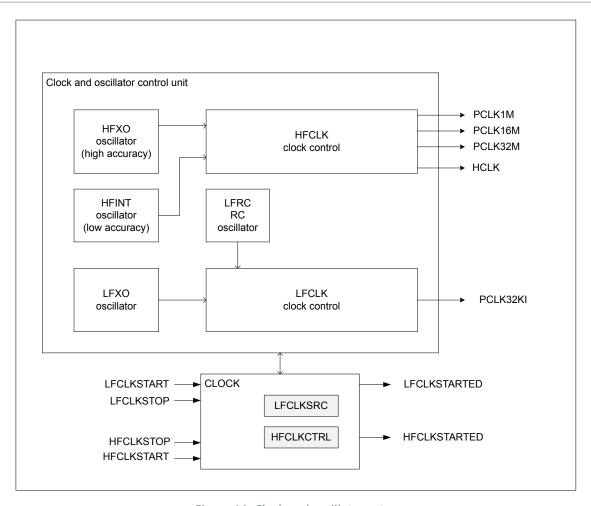

|   | 5.1.4 Clock management                                                                                    | 52       |

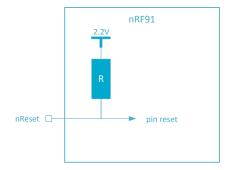

|   | 5.1.5 Reset                                                                                               | 55       |

|   | 5.2 Current consumption                                                                                   | 57       |

|   | 5.2.1 Electrical specification                                                                            |          |

|   | 5.3 Register description                                                                                  |          |

|   | 5.3.1 POWER — Power control                                                                               |          |

|   | 5.3.2 CLOCK — Clock control                                                                               |          |

|   | 5.3.3 REGULATORS — Voltage regulators control                                                             | . 76     |

|   |                                                                                                           |          |

| 6 | Peripherals                                                                                               | 78       |

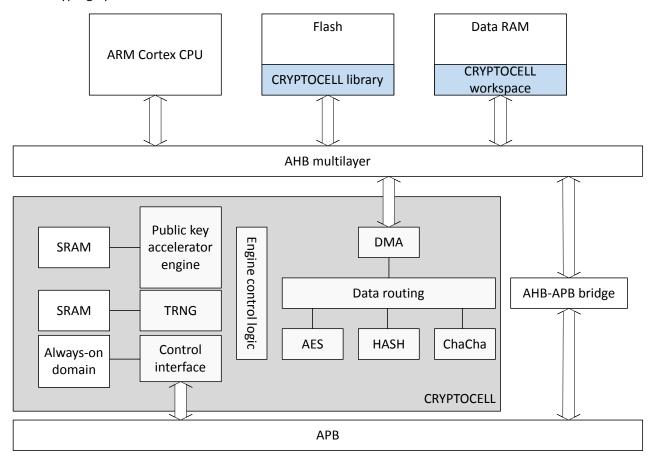

|   | 6.1 CRYPTOCELL — ARM TrustZone CryptoCell 310                                                             | . 78     |

|   | 6.1.1 Usage                                                                                               | 79       |

|   | 6.1.2 Always-on (AO) power domain                                                                         | . 79     |

|   | 6.1.3 Lifecycle state (LCS)                                                                               | 79       |

|   | 6.1.4 Cryptographic key selection                                                                         |          |

|   | 6.1.5 Direct memory access (DMA)                                                                          |          |

|   | 6.1.6 Standards                                                                                           |          |

|   | 6.1.7 Registers                                                                                           |          |

|   | 6.1.8 Host interface                                                                                      |          |

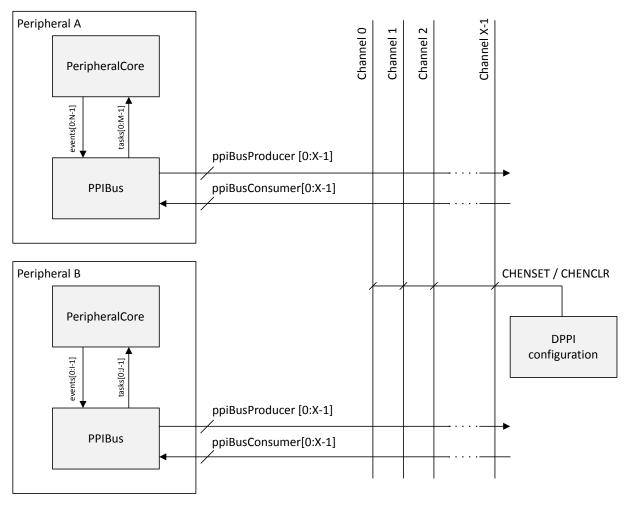

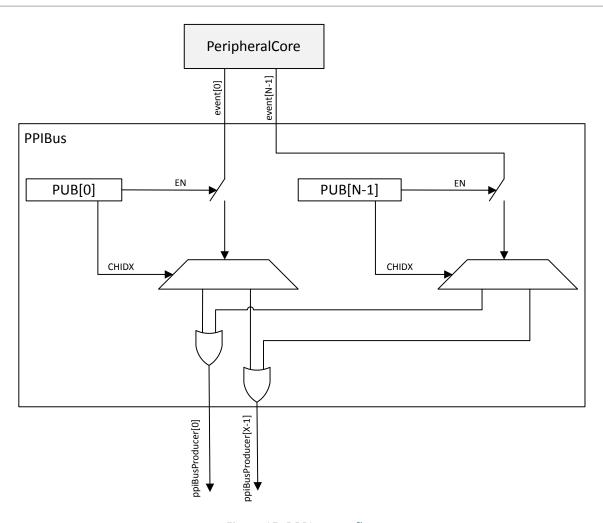

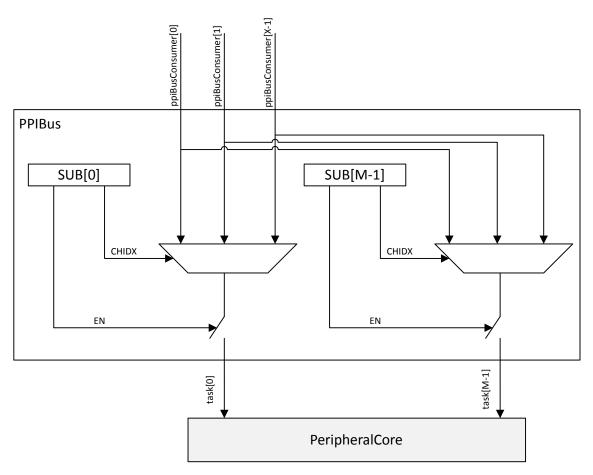

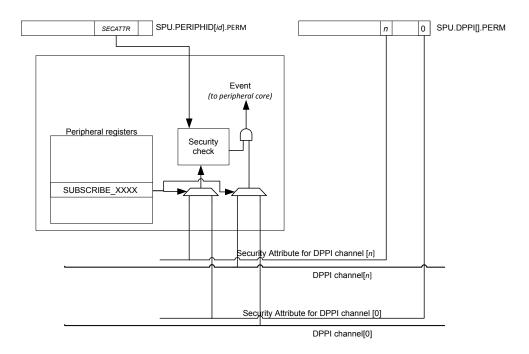

|   | 6.2 DPPI - Distributed programmable peripheral interconnect                                               |          |

|   | 6.2.1 Subscribing to and publishing on channels                                                           |          |

|   | 6.2.2 DPPI configuration (DPPIC)                                                                          | 88       |

|   | 6.2.3 Connection examples                                                                                 | 88       |

|   | 6.2.4 Special considerations for a system implementing TrustZone for Cortex-M processors 6.3.5. Beginning |          |

|   | 6.2.5 Registers                                                                                           |          |

|   | 6.3 EGU — Event generator unit                                                                            | 94<br>94 |

|   | 6.3.2 Electrical specification                                                                            | 98       |

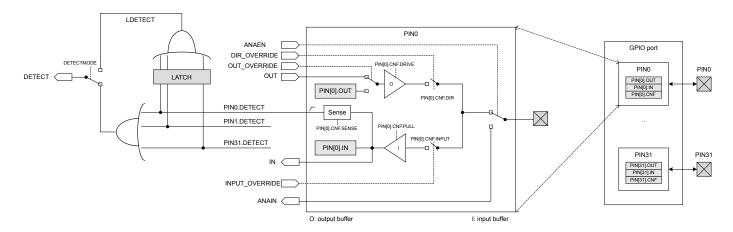

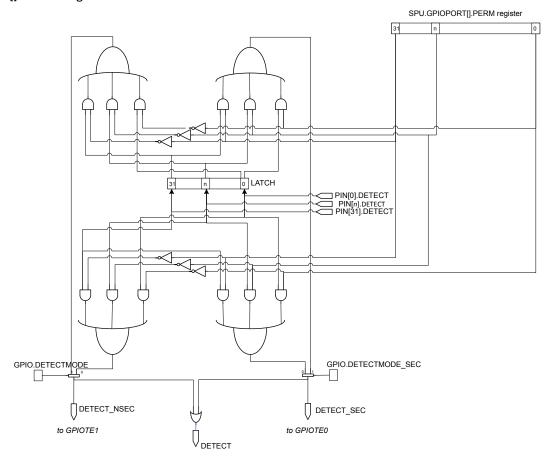

|   | 6.4 GPIO — General purpose input/output                                                                   |          |

|   | 6.4.1 Pin configuration                                                                                   | 99       |

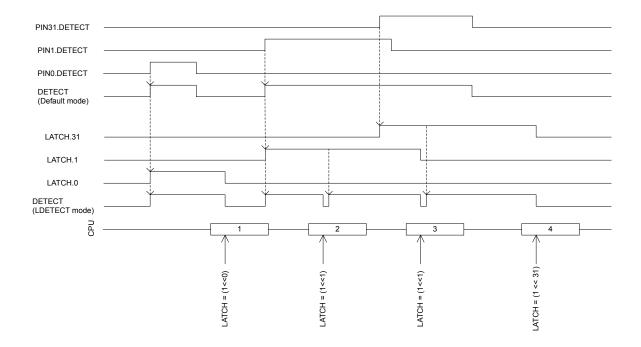

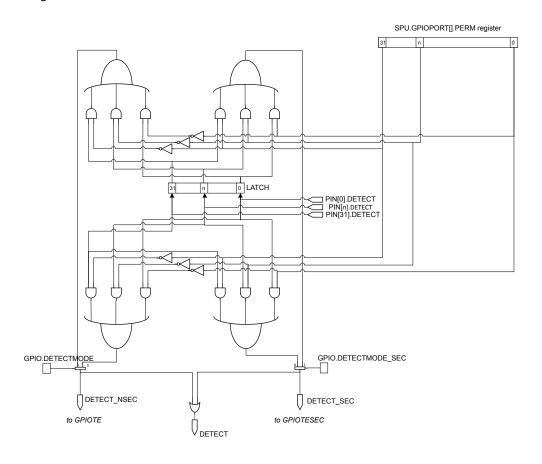

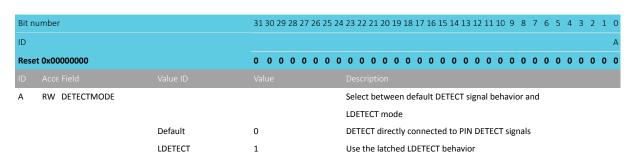

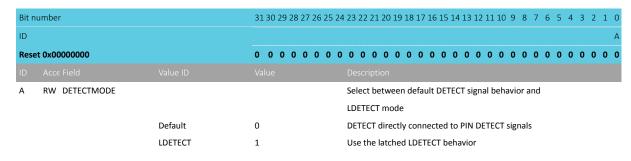

|   | 6.4.2 Pin sense mechanism                                                                                 | 100      |

|   | 6.4.3 GPIO security                                                                                       | 100      |

|   | 6.4.4 Registers                                                                                           | 101      |

|   | 6.4.5 Electrical specification                                                                            | 102      |

|   | 6.5 GPIOTE — GPIO tasks and events                                                                        | 107      |

|   | 6.5.1 Pin events and tasks                                                                                | 108      |

|   | 6.5.2 Port event                                                                                          | 100      |

|   | 6.5.3 Tasks and events pin configuration                                                                  | 109      |

|   | 6.5.4 Registers                                                                                           | 110      |

|   | 6.5.5 Electrical specification                                                                            | 116      |

|   |                                                                                                           |          |

4418\_1315 v1.2 iv

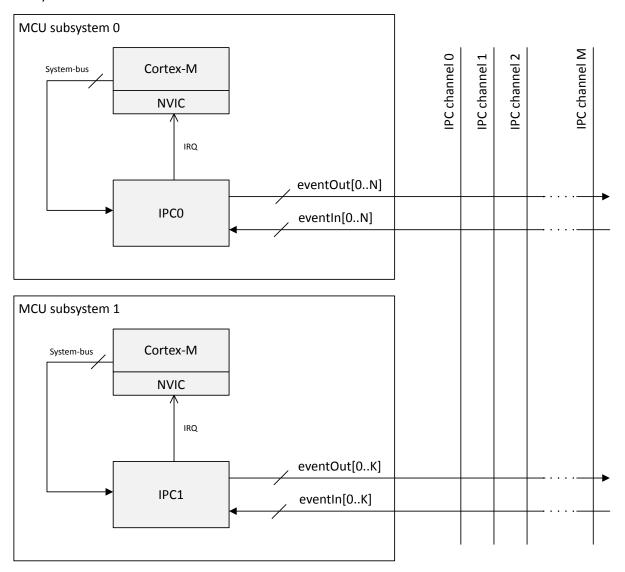

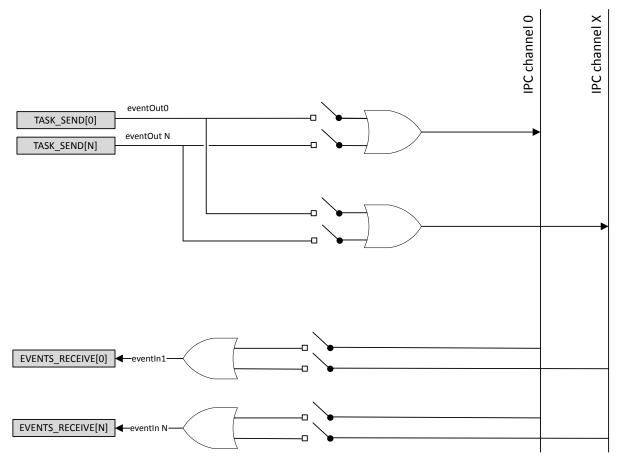

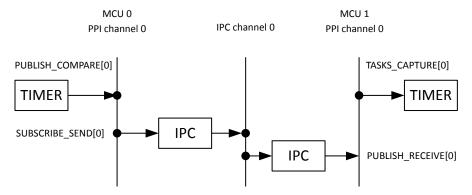

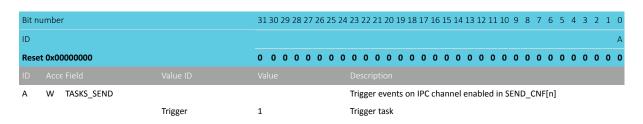

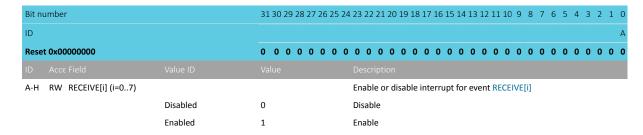

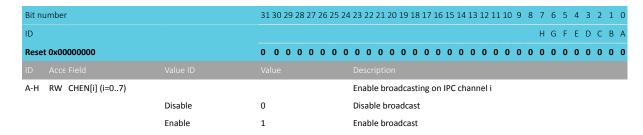

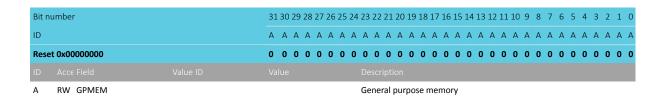

| 6.6 IPC — Interprocessor communication                            | 116 |

|-------------------------------------------------------------------|-----|

| 6.6.1 IPC and PPI connections                                     | 118 |

| 6.6.2 Registers                                                   | 118 |

| 6.6.3 Electrical specification                                    | 121 |

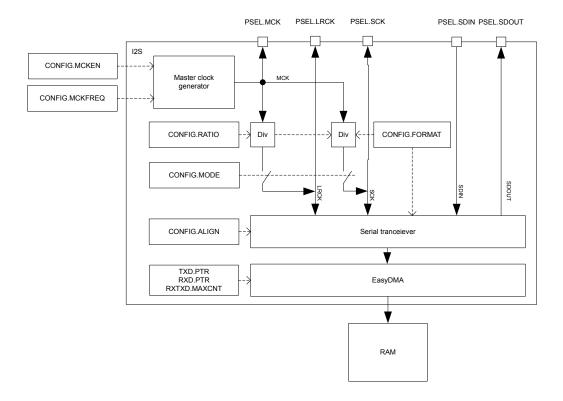

| 6.7 I <sup>2</sup> S — Inter-IC sound interface                   | 121 |

| 6.7.1 Mode                                                        | 122 |

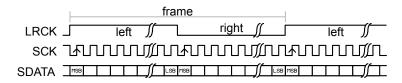

| 6.7.2 Transmitting and receiving                                  | 122 |

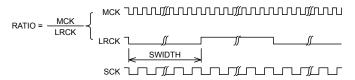

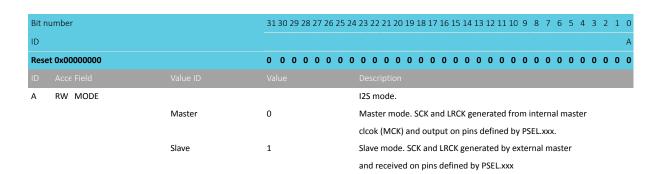

| 6.7.3 Left right clock (LRCK)                                     | 123 |

| 6.7.4 Serial clock (SCK)                                          | 123 |

| 6.7.5 Master clock (MCK)                                          | 124 |

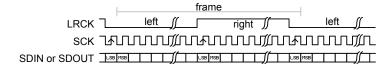

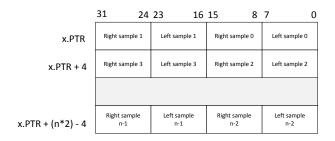

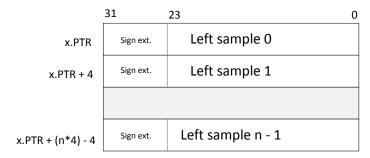

| 6.7.6 Width, alignment and format                                 | 125 |

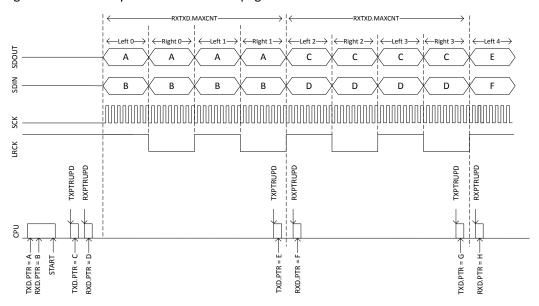

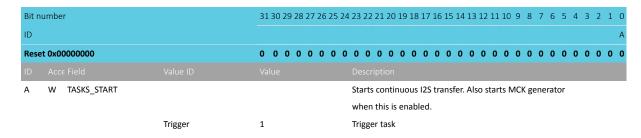

| 6.7.7 EasyDMA                                                     | 126 |

| 6.7.8 Module operation                                            | 128 |

| 6.7.9 Pin configuration                                           | 130 |

| 6.7.10 Registers                                                  | 131 |

| 6.7.11 Electrical specification                                   | 141 |

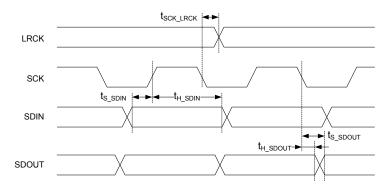

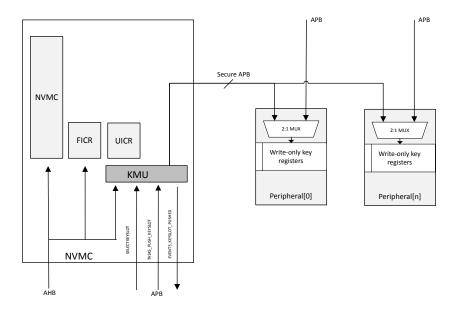

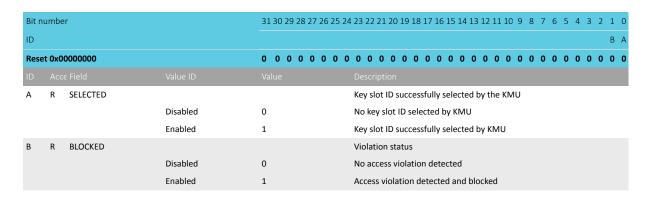

| 6.8 KMU — Key management unit                                     | 142 |

| 6.8.1 Functional view                                             | 142 |

| 6.8.2 Access control                                              | 143 |

| 6.8.3 Protecting the UICR content                                 | 143 |

| 6.8.4 Usage                                                       | 144 |

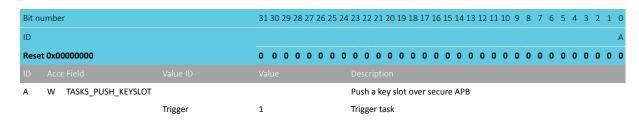

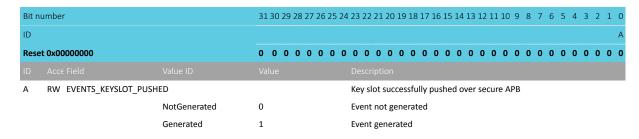

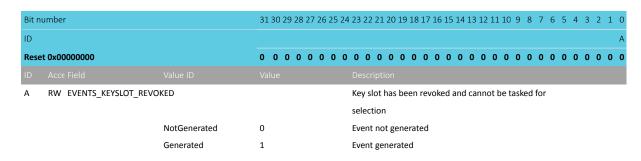

| 6.8.5 Registers                                                   | 148 |

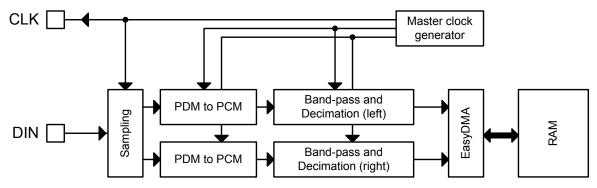

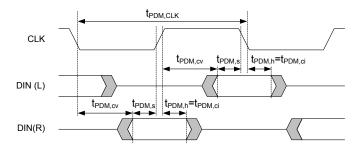

| 6.9 PDM — Pulse density modulation interface                      | 152 |

| 6.9.1 Master clock generator                                      | 152 |

| 6.9.2 Module operation                                            | 152 |

| 6.9.3 Decimation filter                                           | 153 |

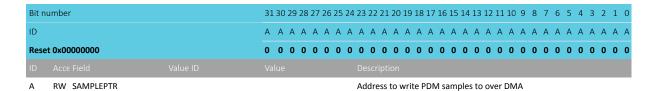

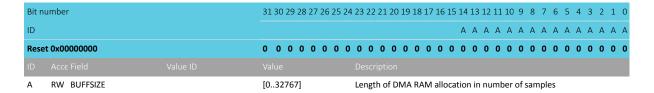

| 6.9.4 EasyDMA                                                     | 153 |

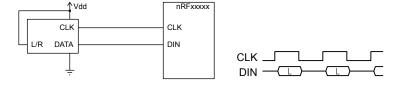

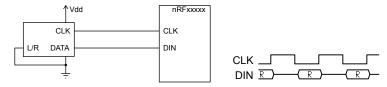

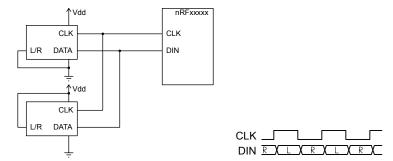

| 6.9.5 Hardware example                                            | 154 |

| 6.9.6 Pin configuration                                           | 155 |

|                                                                   | 155 |

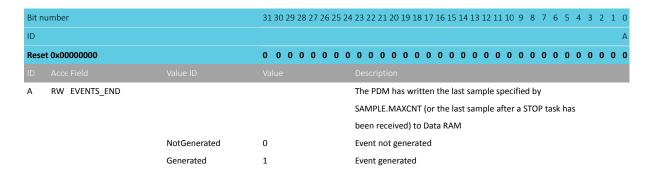

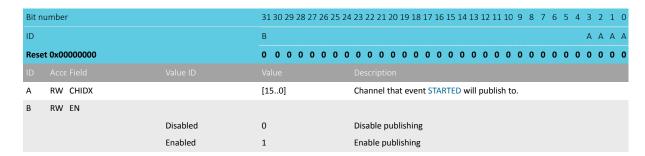

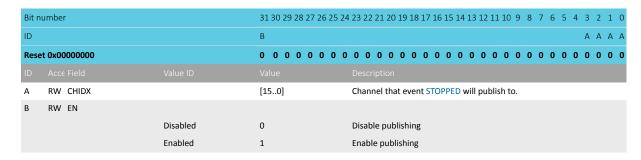

| 6.9.7 Registers                                                   | 163 |

| 6.9.8 Electrical specification                                    |     |

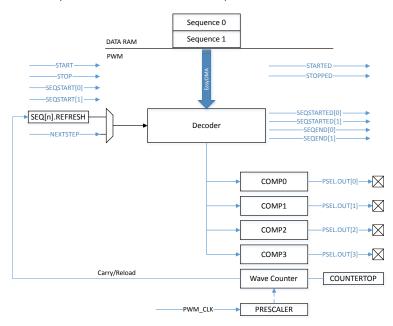

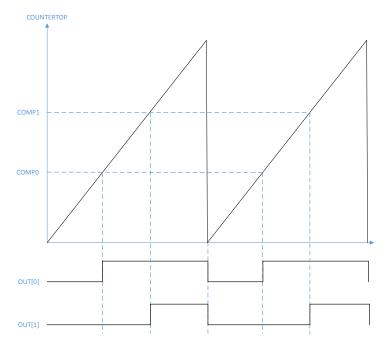

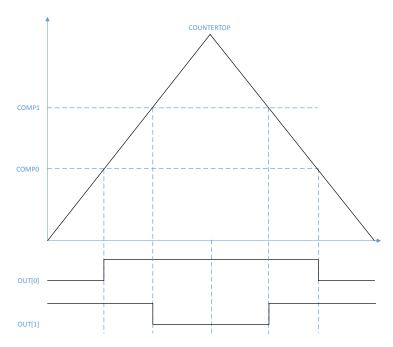

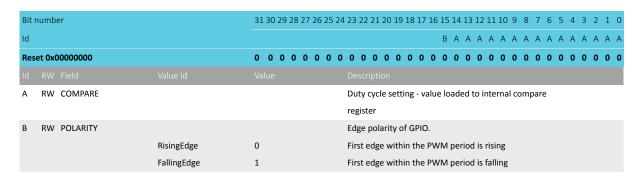

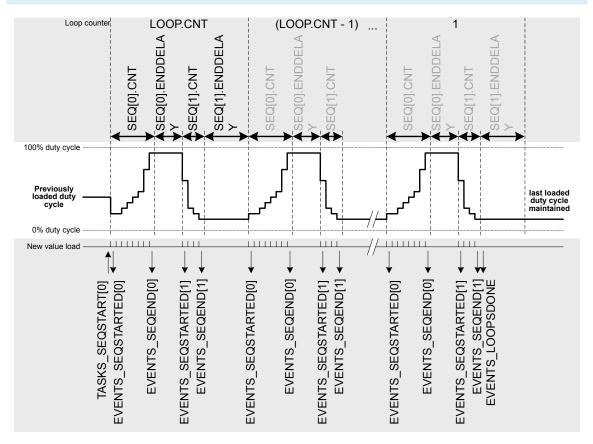

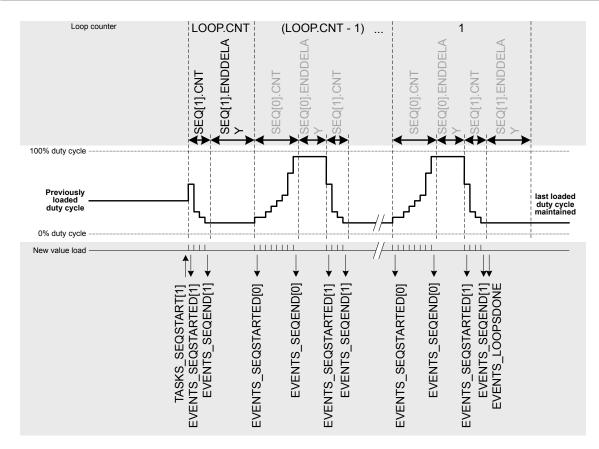

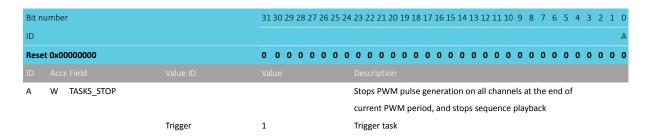

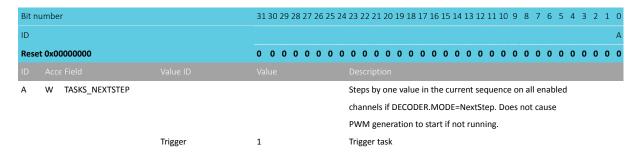

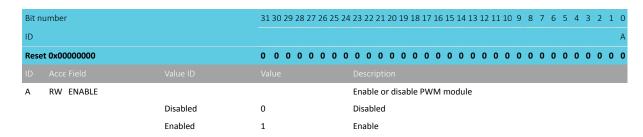

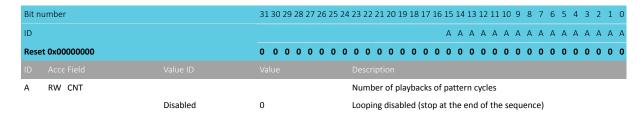

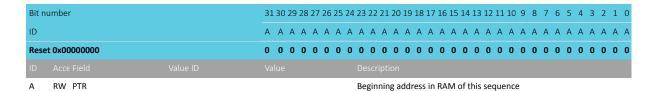

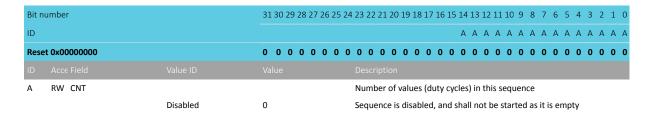

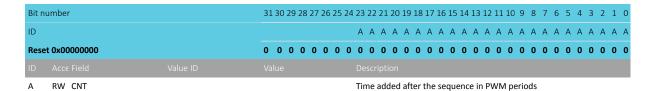

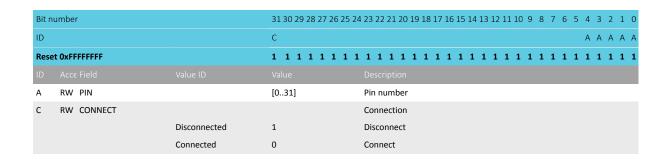

| 6.10 PWM — Pulse width modulation                                 | 164 |

| 6.10.1 Wave counter                                               |     |

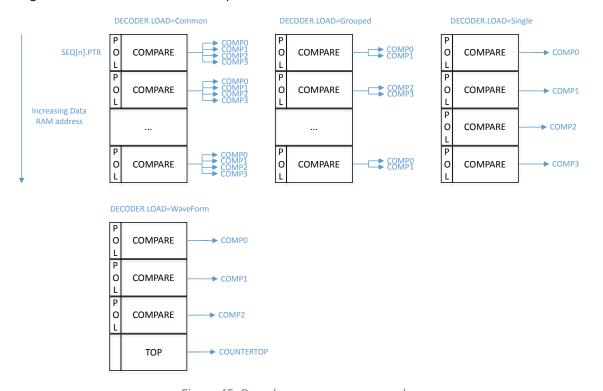

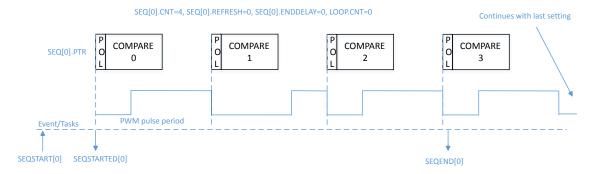

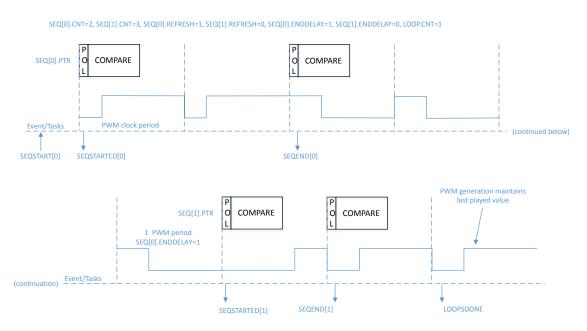

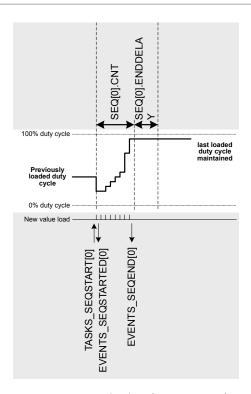

| 6.10.2 Decoder with EasyDMA                                       |     |

|                                                                   | 175 |

| 6.10.4 Pin configuration                                          | 175 |

| 6.10.5 Registers                                                  | 176 |

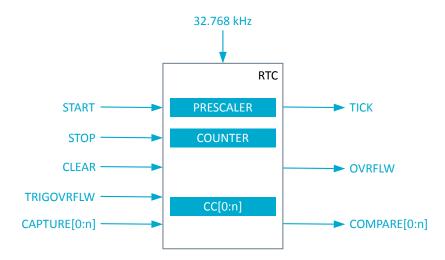

| 6.11 RTC — Real-time counter                                      | 187 |

| 6.11.1 Clock source                                               | 187 |

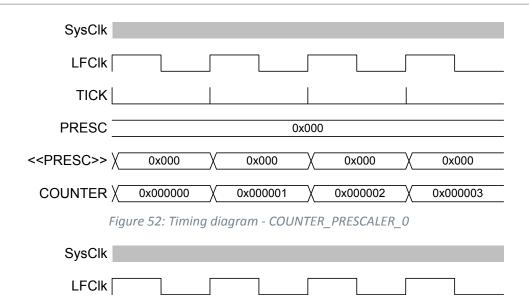

| 6.11.2 Resolution versus overflow and the prescaler               | 188 |

| 6.11.3 Counter register                                           | 188 |

| 6.11.4 Overflow                                                   | 189 |

| 6.11.5 Tick event                                                 | 189 |

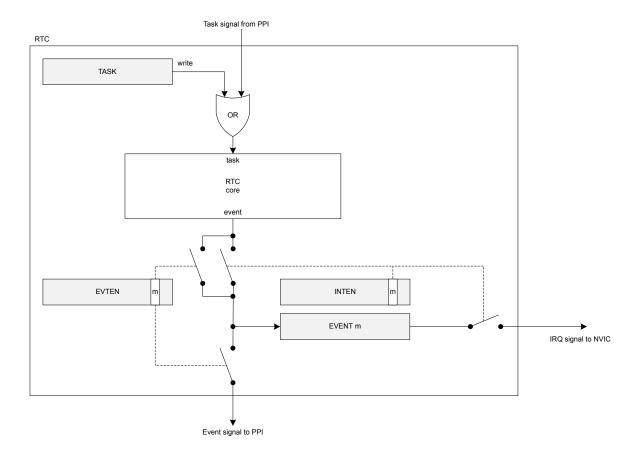

| 6.11.6 Event control                                              | 189 |

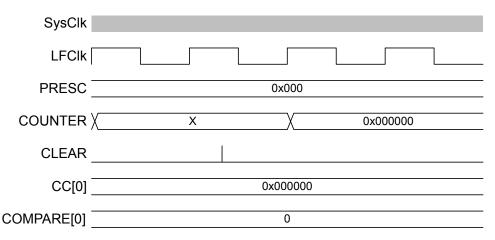

| 6.11.7 Compare                                                    | 190 |

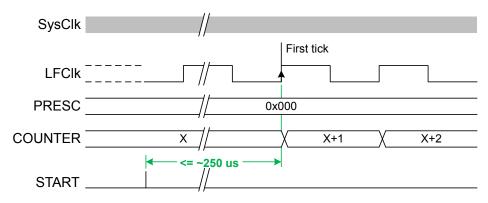

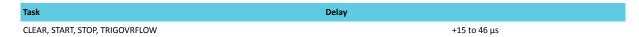

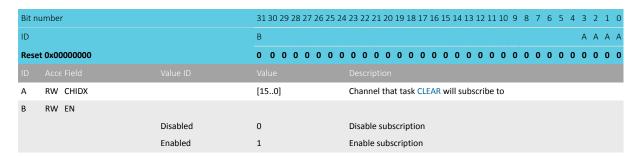

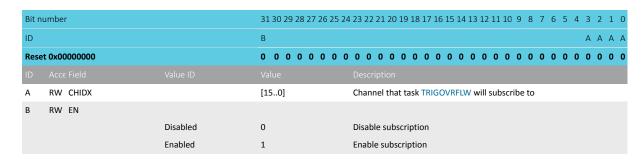

| 6.11.8 Task and event jitter/delay                                | 192 |

| 6.11.9 Reading the counter register                               | 194 |

| 6.11.10 Registers                                                 | 194 |

| 6.11.11 Electrical specification                                  | 202 |

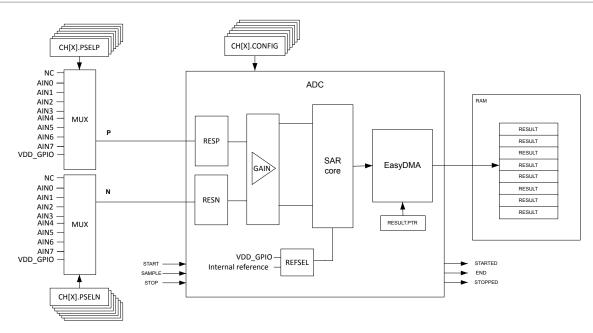

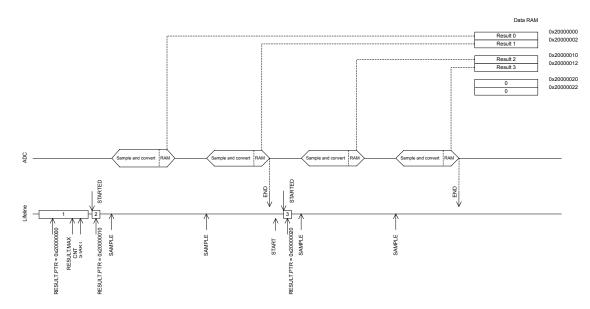

| 6.12 SAADC — Successive approximation analog-to-digital converter | 202 |

| 6.12.1 Overview                                                   | 202 |

| 6.12.2 Digital output                                             | 203 |

| 6.12.3 Analog inputs and channels                                 | 204 |

| 6.12.4 Operation modes                                            | 204 |

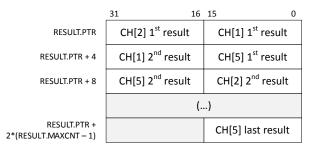

| 6.12.5 EasyDMA                                                                             |       |

|--------------------------------------------------------------------------------------------|-------|

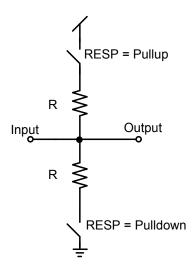

| 6.12.6 Resistor ladder                                                                     |       |

| 6.12.7 Reference                                                                           | . 208 |

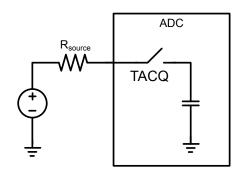

| 6.12.8 Acquisition time                                                                    | . 208 |

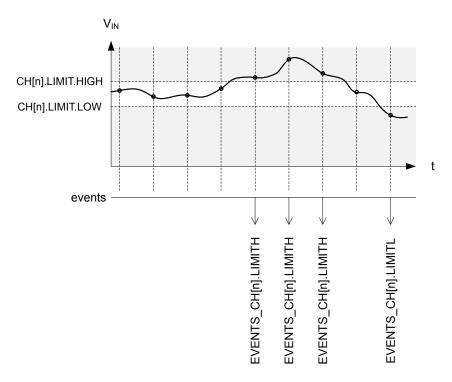

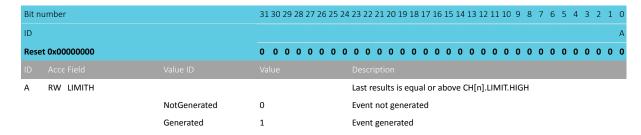

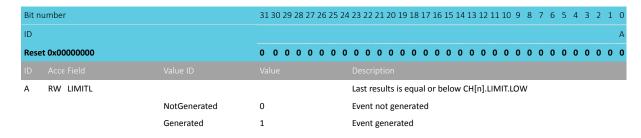

| 6.12.9 Limits event monitoring                                                             | . 209 |

| 6.12.10 Registers                                                                          | . 210 |

| 6.12.11 Electrical specification                                                           | . 228 |

| 6.12.12 Performance factors                                                                |       |

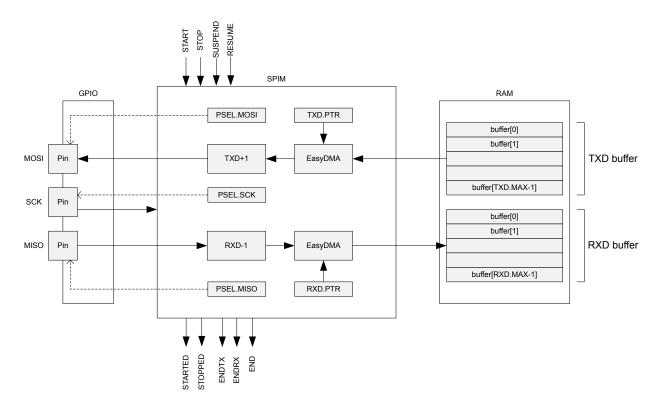

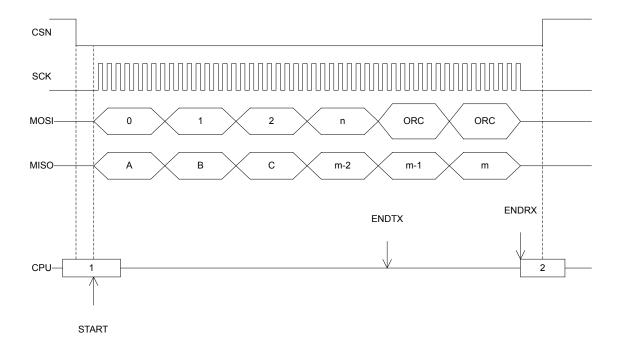

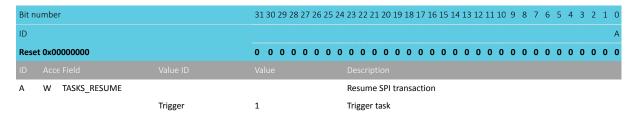

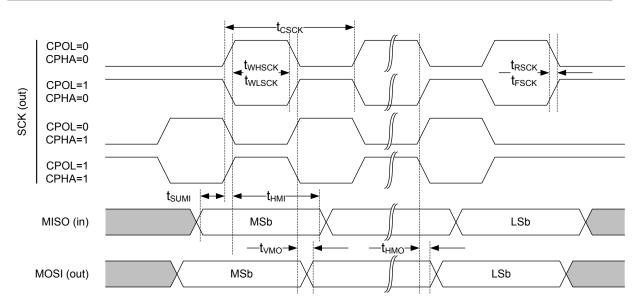

| 6.13 SPIM — Serial peripheral interface master with EasyDMA                                |       |

| 6.13.1 SPI master transaction sequence                                                     |       |

| 6.13.2 Master mode pin configuration                                                       |       |

| 6.13.3 Shared resources                                                                    |       |

| 6.13.4 EasyDMA                                                                             |       |

| 6.13.5 Low power                                                                           |       |

| 6.13.6 Registers                                                                           |       |

| 6.13.7 Electrical specification                                                            |       |

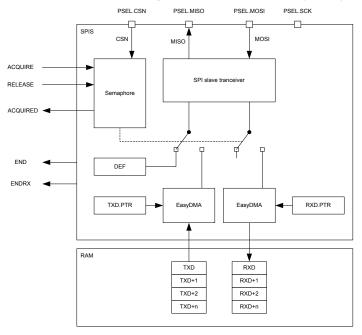

| 6.14 SPIS — Serial peripheral interface slave with EasyDMA                                 |       |

| 6.14.1 Shared resources                                                                    |       |

| 6.14.2 EasyDMA                                                                             |       |

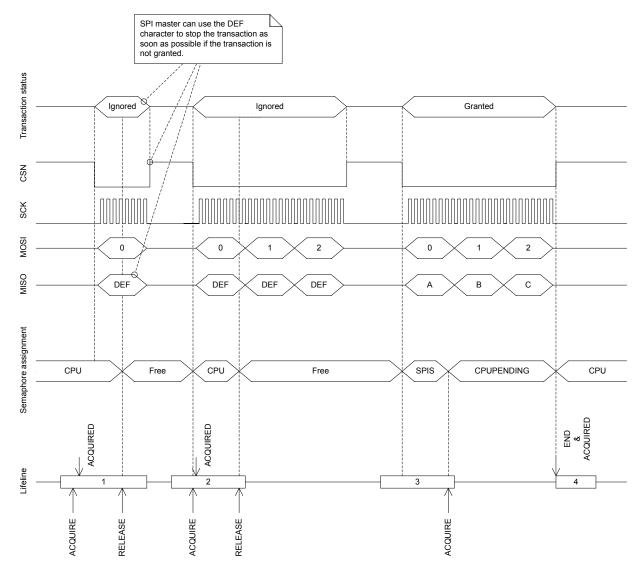

| 6.14.3 SPI slave operation                                                                 |       |

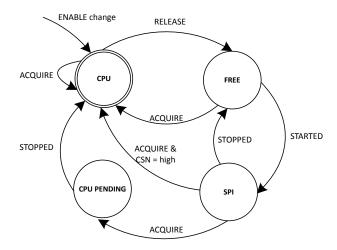

| 6.14.4 Semaphore operation                                                                 |       |

|                                                                                            |       |

| 6.14.5 Pin configuration                                                                   |       |

|                                                                                            |       |

| 6.14.7 Electrical specification                                                            |       |

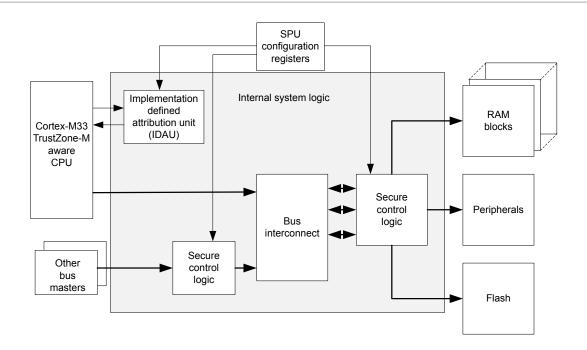

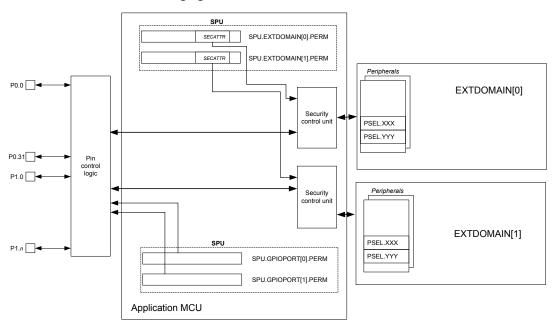

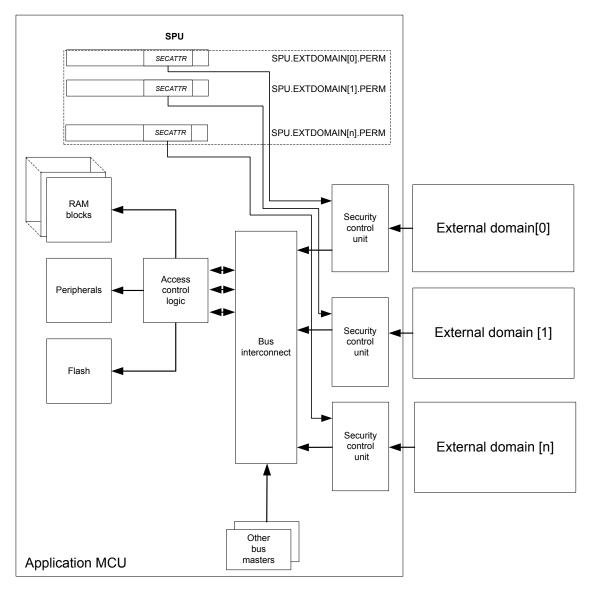

| 6.15 SPU - System protection unit                                                          |       |

| 6.15.1 General concepts                                                                    |       |

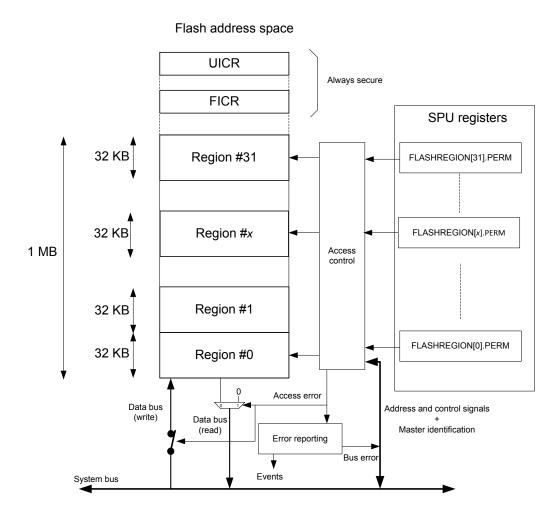

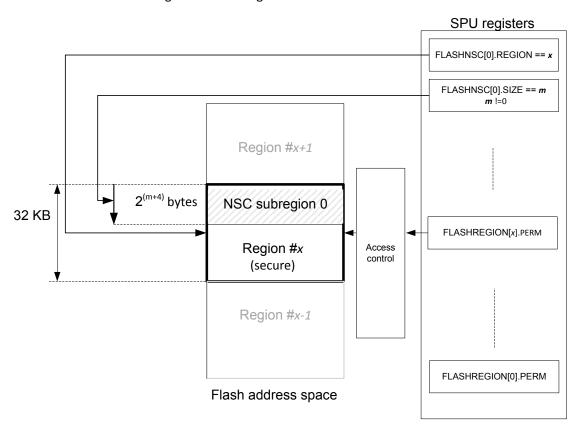

| 6.15.2 Flash access control                                                                |       |

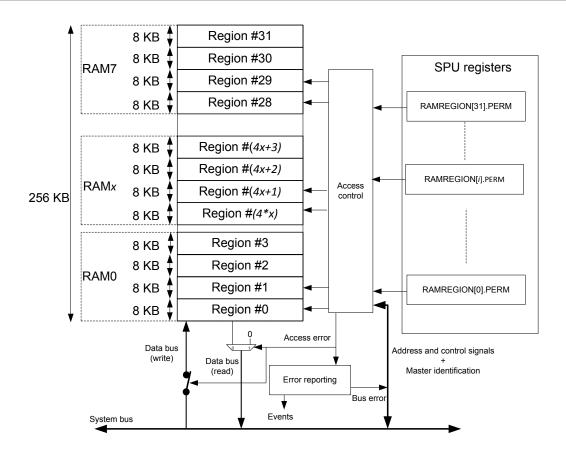

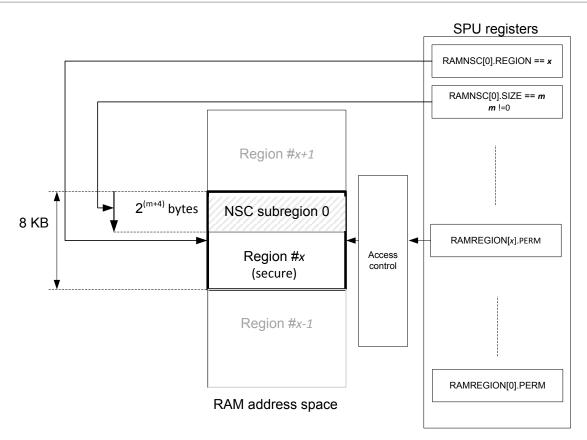

| 6.15.3 RAM access control                                                                  |       |

| 6.15.4 Peripheral access control                                                           |       |

| 6.15.5 Pin access control                                                                  |       |

| 6.15.6 DPPI access control                                                                 |       |

| 6.15.7 External domain access control                                                      |       |

| 6.15.8 TrustZone for Cortex-M ID allocation                                                |       |

| 6.15.9 Registers                                                                           |       |

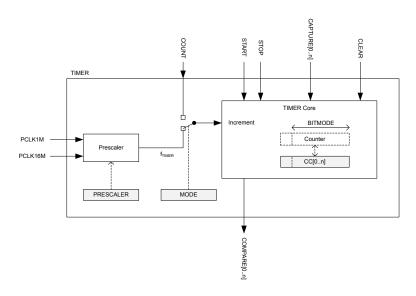

| 6.16 TIMER — Timer/counter                                                                 |       |

| 6.16.1 Capture                                                                             |       |

| 6.16.2 Compare                                                                             |       |

| 6.16.3 Task delays                                                                         |       |

| 6.16.4 Task priority                                                                       |       |

| 6.16.5 Registers                                                                           |       |

| 6.16.6 Electrical specification                                                            |       |

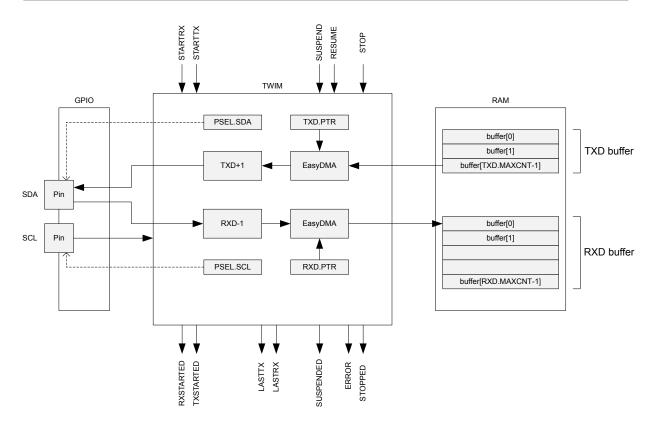

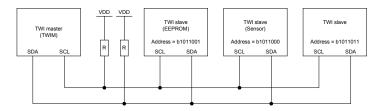

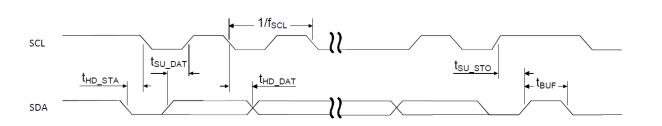

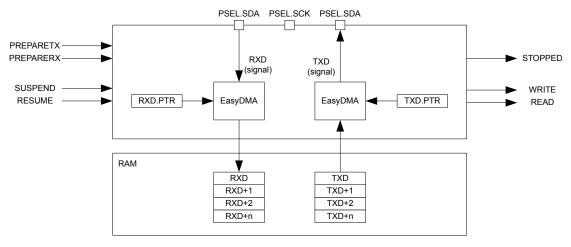

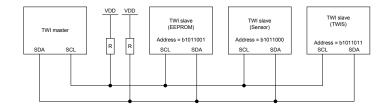

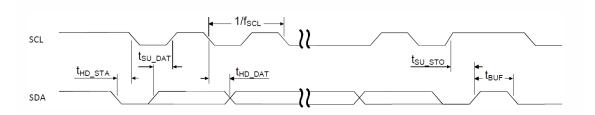

| $6.17 \text{ TWIM} - \text{I}^2\text{C}$ compatible two-wire interface master with EasyDMA | . 296 |

| 6.17.1 Shared resources                                                                    | . 298 |

| 6.17.2 EasyDMA                                                                             | . 298 |

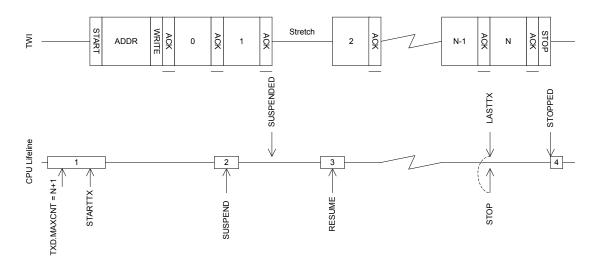

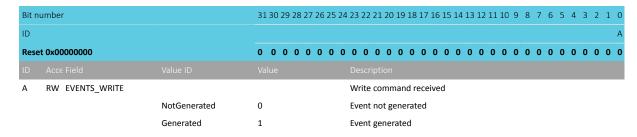

| 6.17.3 Master write sequence                                                               | . 298 |

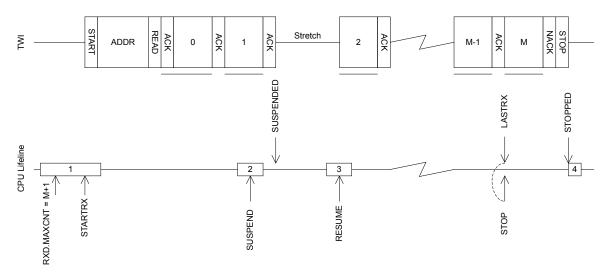

| 6.17.4 Master read sequence                                                                | . 299 |

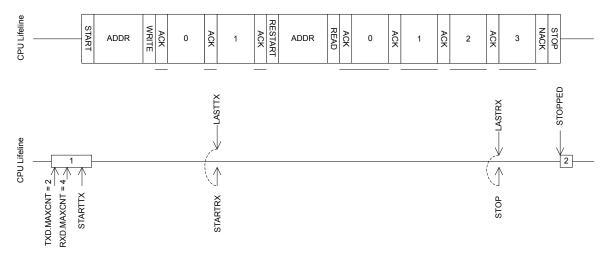

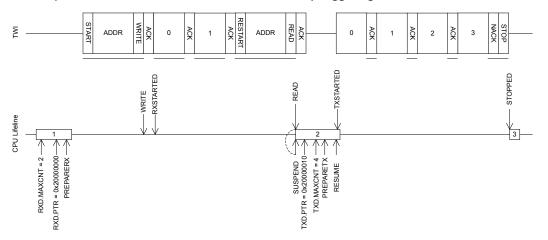

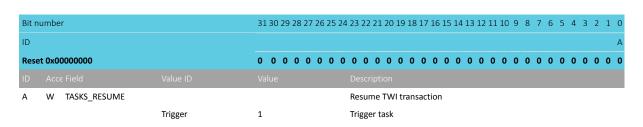

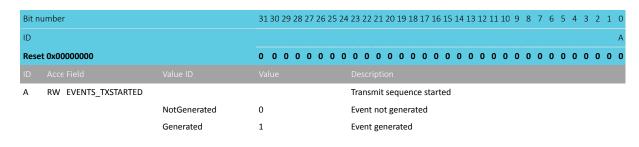

| 6.17.5 Master repeated start sequence                                                      | . 300 |

| 6.17.6 Low power                                                                           | . 301 |

| 6.17.7 Master mode pin configuration                                                       | . 301 |

| 6.17.8 Registers                                                                           | . 302 |

| 6.17.9 Electrical specification                                                            |       |

| 6.17.10 Pullup resistor                                                                    |       |

| 6.18 TWIS — $I^2C$ compatible two-wire interface slave with EasyDMA                        |       |

| 6.18.1 Shared resources                                                                    | . 319 |

4418\_1315 v1.2 vi

|   | 6.18.2 EasyDMA                                                        | . 319 |

|---|-----------------------------------------------------------------------|-------|

|   | 6.18.3 TWI slave responding to a read command                         | . 319 |

|   | 6.18.4 TWI slave responding to a write command                        | . 320 |

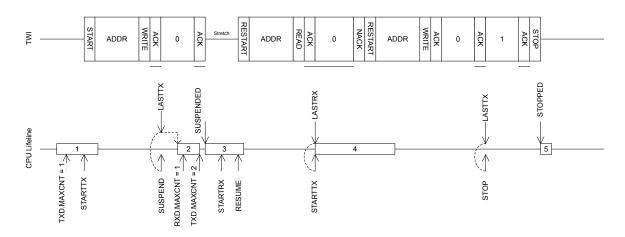

|   | 6.18.5 Master repeated start sequence                                 | . 322 |

|   | 6.18.6 Terminating an ongoing TWI transaction                         | . 322 |

|   | 6.18.7 Low power                                                      | . 322 |

|   | 6.18.8 Slave mode pin configuration                                   | . 322 |

|   | 6.18.9 Registers                                                      | . 323 |

|   | 6.18.10 Electrical specification                                      | . 336 |

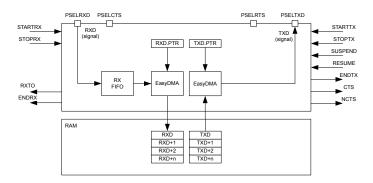

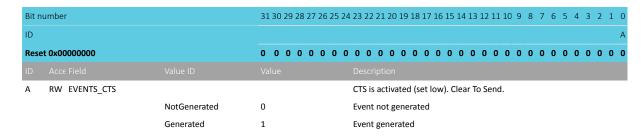

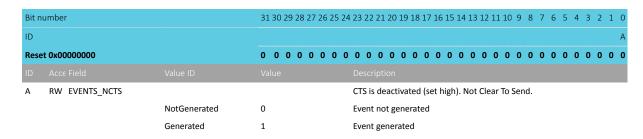

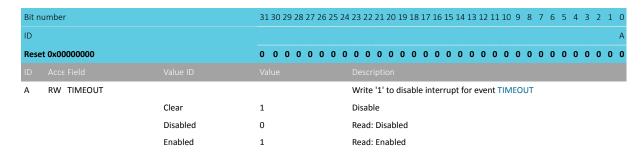

|   | 6.19 UARTE — Universal asynchronous receiver/transmitter with EasyDMA | . 337 |

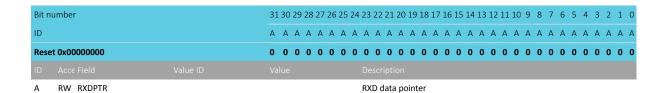

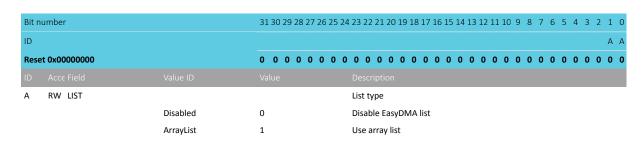

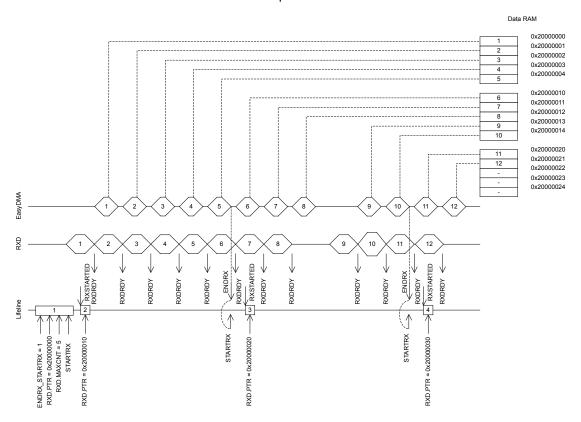

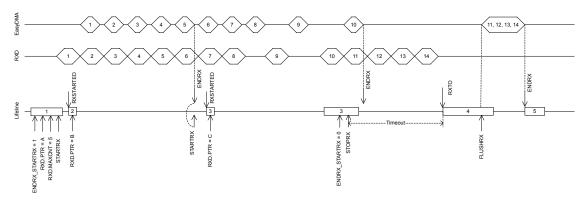

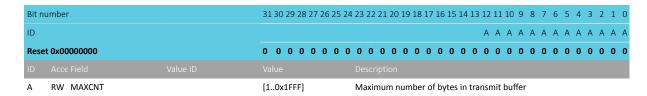

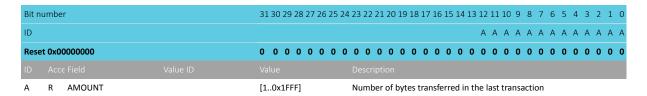

|   | 6.19.1 EasyDMA                                                        | . 338 |

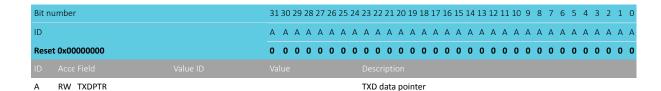

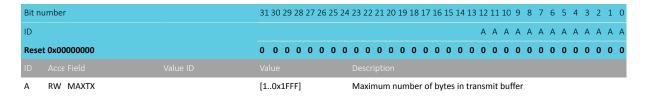

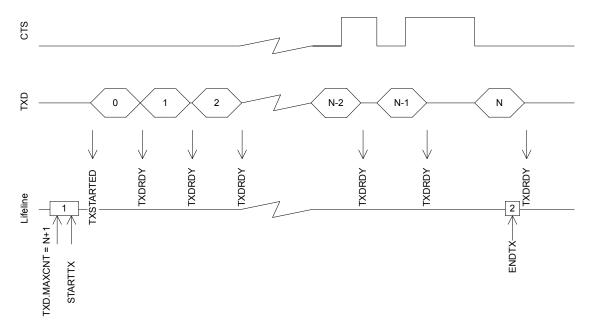

|   | 6.19.2 Transmission                                                   | . 338 |

|   | 6.19.3 Reception                                                      | 339   |

|   | 6.19.4 Error conditions                                               | . 340 |

|   | 6.19.5 Using the UARTE without flow control                           | 340   |

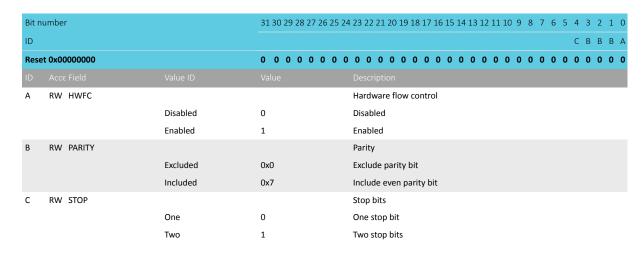

|   | 6.19.6 Parity and stop bit configuration                              | . 341 |

|   | 6.19.7 Low power                                                      | . 341 |

|   | 6.19.8 Pin configuration                                              | 341   |

|   | 6.19.9 Registers                                                      | . 342 |

|   | 6.19.10 Electrical specification                                      | . 359 |

|   | 6.20 WDT — Watchdog timer                                             | . 360 |

|   | 6.20.1 Reload criteria                                                |       |

|   | 6.20.2 Temporarily pausing the watchdog                               |       |

|   | 6.20.3 Watchdog reset                                                 |       |

|   | 6.20.4 Registers                                                      |       |

|   | 6.20.5 Electrical specification                                       |       |

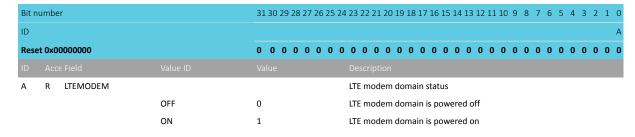

| 7 | LTE modem                                                             |       |

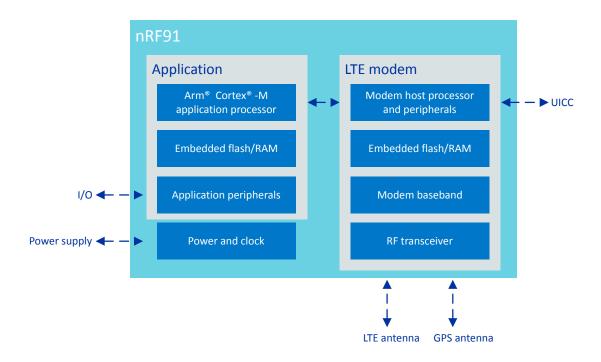

|   | 7.2 SIM card interface                                                | . 367 |

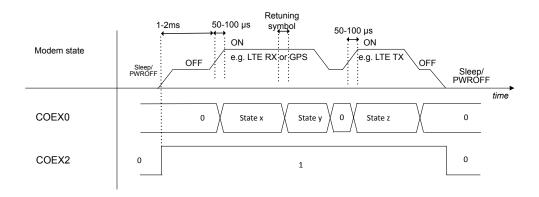

|   | 7.3 LTE modem coexistence interface                                   | . 368 |

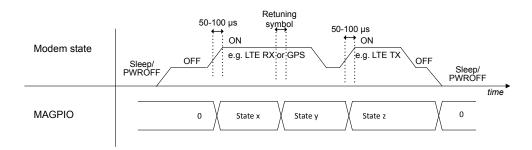

|   | 7.4 LTE modem RF control external interface                           | . 369 |

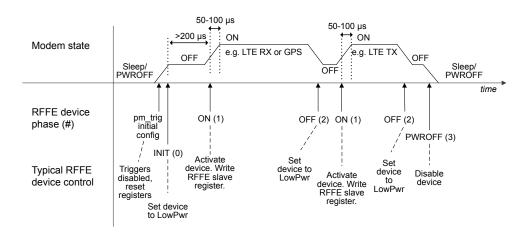

|   | 7.5 RF front-end interface                                            | 371   |

|   | 7.6 Electrical specification                                          | 371   |

|   | 7.6.1 Key RF parameters for Cat-M1                                    |       |

|   | 7.6.2 Key RF parameters for Cat-NB1 and Cat-NB2                       | 371   |

|   | 7.6.3 Receiver parameters for Cat-M1                                  | 372   |

|   | 7.6.4 Receiver parameters for Cat-NB1 and Cat-NB2                     | . 372 |

|   | 7.6.5 Transmitter parameters for Cat-M1                               | 373   |

|   | 7.6.6 Transmitter parameters for Cat-NB1 and Cat-NB2                  | 373   |

| 8 | GPS receiver.                                                         | 374   |

|   | 8.1 Electrical specification                                          | 374   |

|   | ·                                                                     |       |

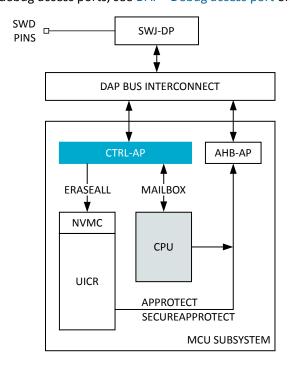

| 9 | Debug and trace.                                                      |       |

|   | 9.1 Overview                                                          |       |

|   | 9.1.1 Special consideration regarding debugger access                 |       |

|   | 9.1.2 DAP - Debug access port                                         | 377   |

|   | 9.1.3 Debug interface mode                                            | 377   |

|   | 9.1.4 Real-time debug                                                 |       |

|   | 9.1.5 Trace                                                           |       |

|   | 9.1.6 Registers                                                       |       |

|   | 9.1.7 Electrical specification                                        | . 379 |

4418\_1315 v1.2 vii

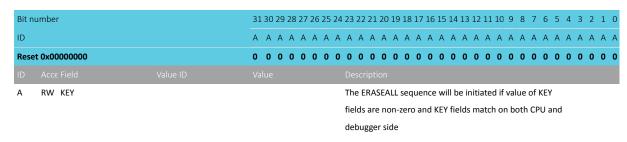

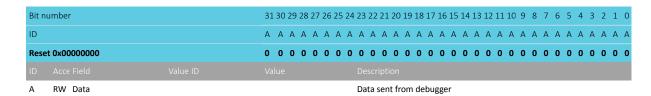

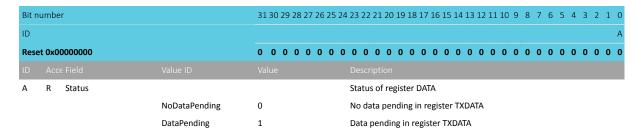

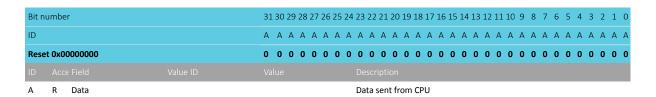

|    | 9.2 CTRL-AP - Control access port | 3/9 |

|----|-----------------------------------|-----|

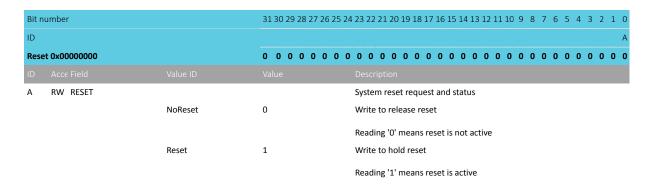

|    | 9.2.1 Reset request               | 380 |

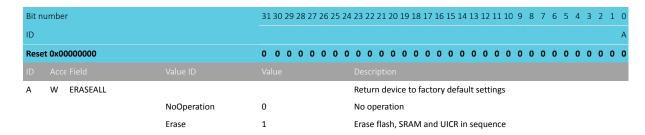

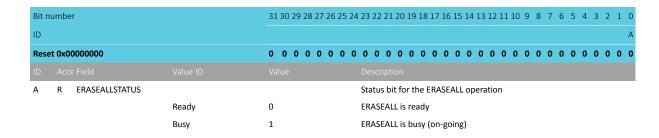

|    | 9.2.2 Erase all                   | 380 |

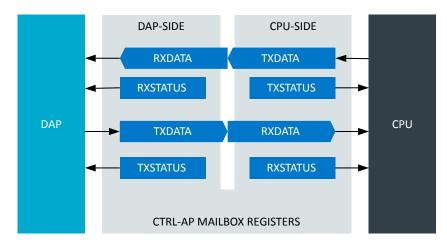

|    | 9.2.3 Mailbox interface           |     |

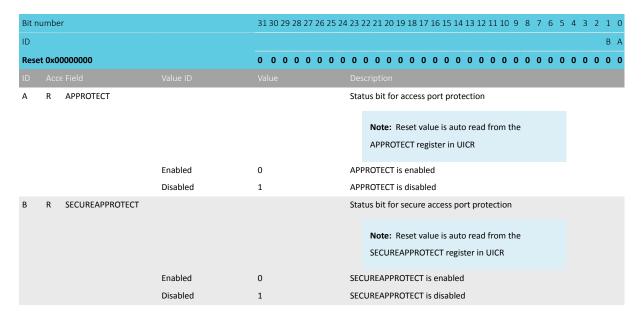

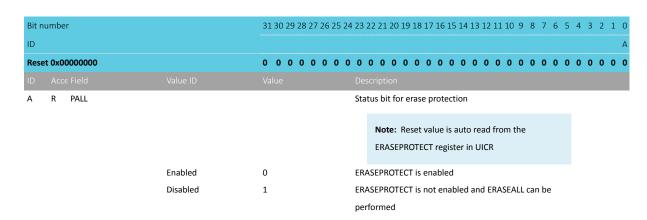

|    | 9.2.4 Disabling erase protection  |     |

|    | 9.2.5 Registers                   | 381 |

|    | 9.2.6 Registers                   | 385 |

|    | 9.3 TAD - Trace and debug control | 387 |

|    | 9.3.1 Registers                   | 387 |

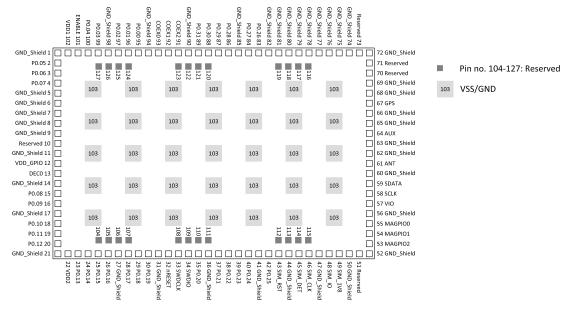

| 10 | Hardware and layout.              | 391 |

|    | 10.1 Pin assignments              | 391 |

|    | 10.1.1 Pin assignments            | 391 |

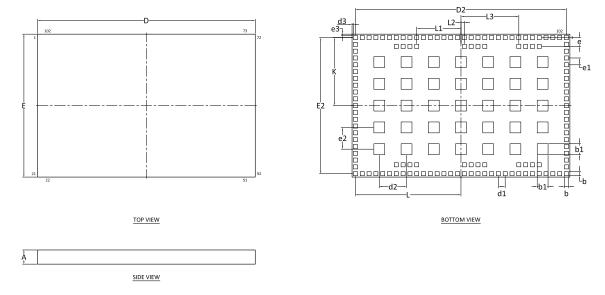

|    | 10.2 Mechanical specifications    | 394 |

|    | 10.2.1 16.00 x 10.50 mm package   | 394 |

|    | 10.3 Reference circuitry          | 394 |

|    | 10.3.1 Schematic SIxA LGA127      | 395 |

|    | 10.4 Reflow conditions            | 395 |

| 11 | Operating conditions.             | 396 |

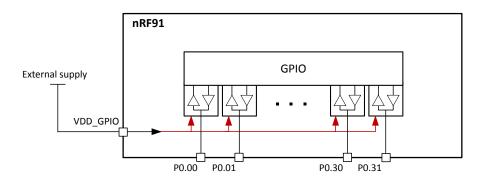

|    | 11.1 VDD GPIO considerations      |     |

|    | 11.1 VDB_GI TO CONSIDERATIONS     | 330 |

| 12 | Absolute maximum ratings.         | 397 |

| 13 | Ordering information.             | 398 |

|    |                                   |     |

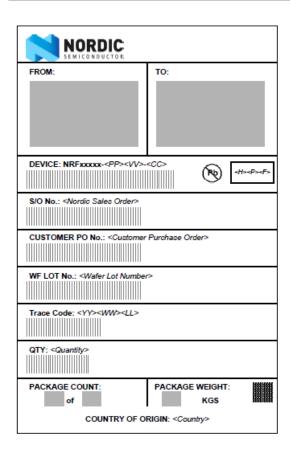

|    | 13.1 IC marking                   |     |

|    | 13.2 Box labels                   | 398 |

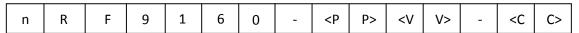

|    | 13.3 Order code                   | 400 |

|    | 13.4 Code ranges and values       | 400 |

|    | 13.3 Floudet options              | 401 |

| 14 | Regulatory information.           | 403 |

| 15 | Legal notices.                    | 404 |

4418\_1315 v1.2 viii

# 1 Revision history

| Date         | Version | Description                                                                                                      |  |

|--------------|---------|------------------------------------------------------------------------------------------------------------------|--|

| April 2020   | 1.2     | Updated the following:                                                                                           |  |

|              |         | Operating conditions on page 396 – updated with MAGPIO, COEX, MIPI<br>RFFE, SIMIF pins voltage supply references |  |

|              |         | Absolute maximum ratings on page 397:                                                                            |  |

|              |         | <ul> <li>Updated with GPS antenna input level and ATEX compliance information</li> </ul>                         |  |

|              |         | Decreased maximum storage temperature to 95 °C                                                                   |  |

|              |         | Power and clock management:                                                                                      |  |

|              |         | Updated ENABLE pin information                                                                                   |  |

|              |         | Added SYSTEM DISABLED mode information                                                                           |  |

|              |         | Updated Pin reset voltage level and pull-up information                                                          |  |

|              |         | Current consumption on page 57:                                                                                  |  |

|              |         | Updated peripherals consumption information                                                                      |  |

|              |         | Added SYSTEM DISABLED mode information                                                                           |  |

|              |         | Updated LTE modem Cat-M1 information                                                                             |  |

|              |         | Added Cat-NB1 information                                                                                        |  |

|              |         | Updated GPS receiver information                                                                                 |  |

|              |         | LTE modem:                                                                                                       |  |

|              |         | Added MAGPIO, COEX, and MIPI RFFE timing information                                                             |  |

|              |         | Added NB2 mode and COEX features availability information                                                        |  |

|              |         | <ul> <li>Added information on SIM card power down support during eDRX idle mode</li> </ul>                       |  |

|              |         | GPS receiver on page 374 - updated with performance information                                                  |  |

|              |         | Pin reset on page 55 - updated description and added schematic                                                   |  |

|              |         | Current consumption on page 57 - I GPS_SINGLE value increased due to                                             |  |

|              |         | design changes to improve performance in poor conditions                                                         |  |

|              |         | Added:                                                                                                           |  |

|              |         | Reflow conditions on page 395                                                                                    |  |

| October 2019 | 1.1     | Updated:                                                                                                         |  |

|              |         | Debug and trace Overview on page 376: Added debug access port.  Updated SDK version                              |  |

|              |         | Memory on page 20: Added a reference                                                                             |  |

|              |         | Pin assignments on page 391: Several updates                                                                     |  |

|              |         | Operating conditions on page 396: Changed chapter name. Updated                                                  |  |

|              |         | MAGPIO values. Updated VDD_GPIO restrictions.                                                                    |  |

|              |         | Ordering information on page 398: Updated Product options                                                        |  |

|              |         | Added:                                                                                                           |  |

|              |         | Reference circuitry on page 394                                                                                  |  |

| May 2019     | 1.0     | First release                                                                                                    |  |

# 2 About this document

This document is organized into chapters that are based on the modules and peripherals available in the IC.

## 2.1 Document status

The document status reflects the level of maturity of the document.

| Document name                         | Description                                                                                                                                                                                                                                                |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Objective Product Specification (OPS) | Applies to document versions up to 1.0.  This document contains target specifications for product development.                                                                                                                                             |  |

| Product Specification (PS)            | Applies to document versions 1.0 and higher.  This document contains final product specifications. Nordic Semiconductor ASA reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |  |

Table 1: Defined document names

# 2.2 Peripheral chapters

Every peripheral has a unique capitalized name or an abbreviation of its name, e.g. TIMER, used for identification and reference. This name is used in chapter headings and references, and it will appear in the ARM® Cortex® Microcontroller Software Interface Standard (CMSIS) hardware abstraction layer to identify the peripheral.

The peripheral instance name, which is different from the peripheral name, is constructed using the peripheral name followed by a numbered postfix, starting with 0, for example, TIMERO. A postfix is normally only used if a peripheral can be instantiated more than once. The peripheral instance name is also used in the CMSIS to identify the peripheral instance.

The chapters describing peripherals may include the following information:

- A detailed functional description of the peripheral

- · Register configuration for the peripheral

- Electrical specification tables, containing performance data which apply for the operating conditions described in Peripheral chapters on page 10.

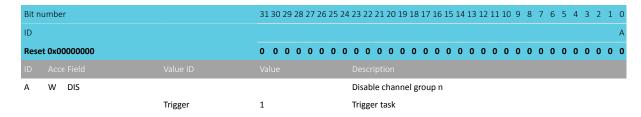

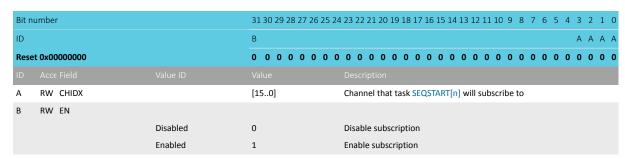

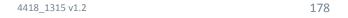

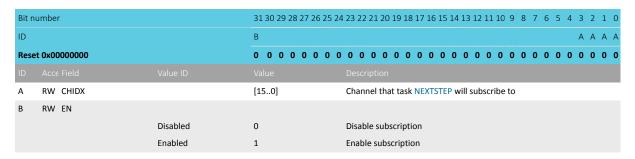

# 2.3 Register tables

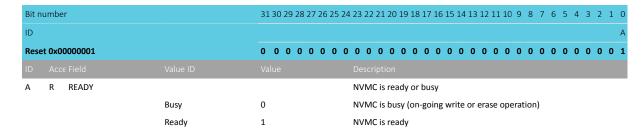

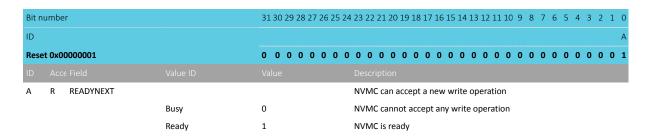

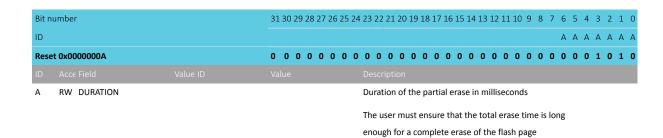

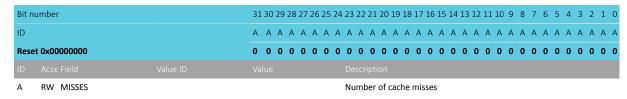

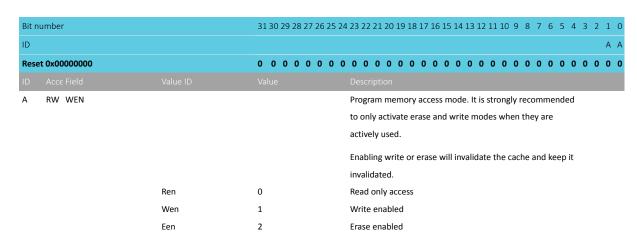

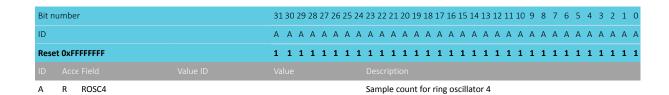

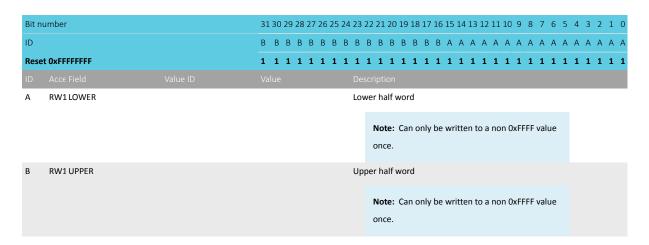

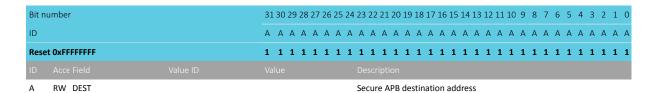

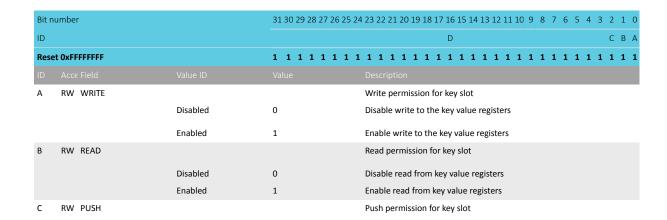

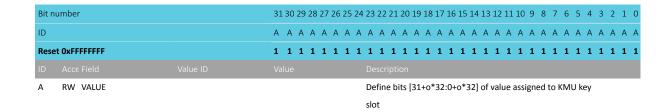

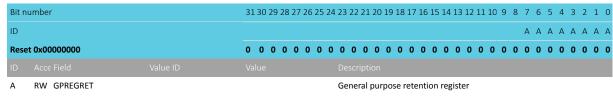

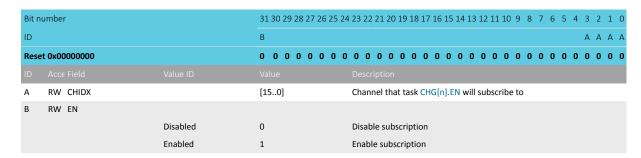

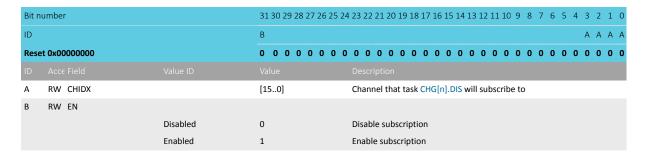

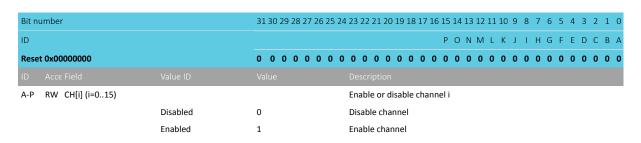

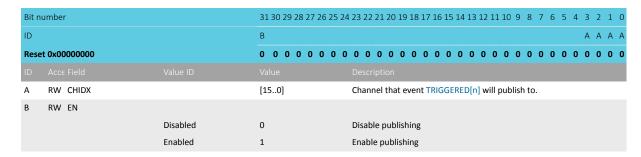

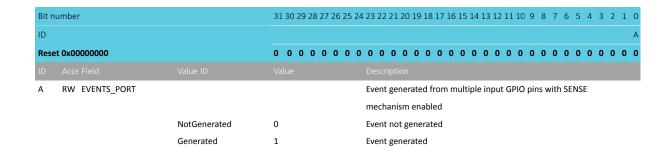

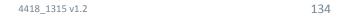

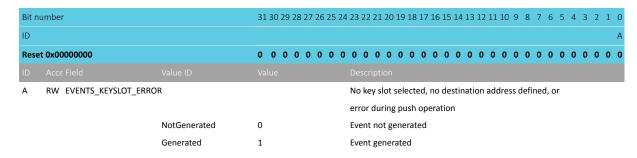

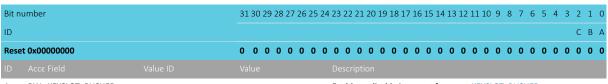

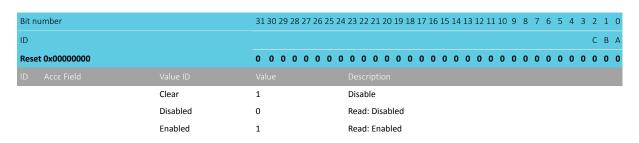

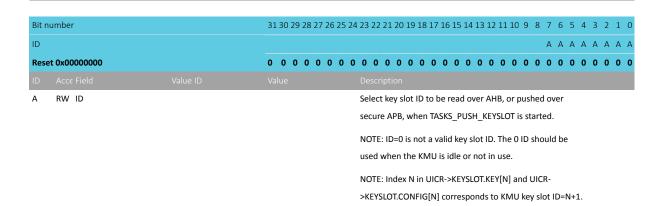

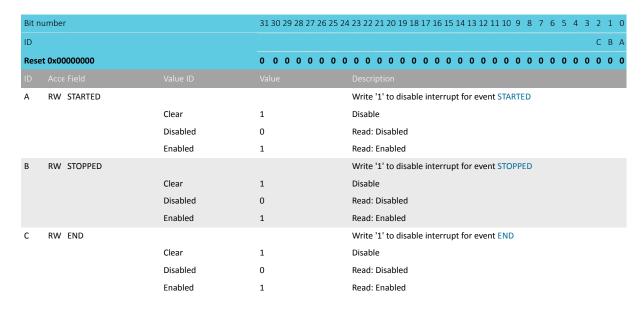

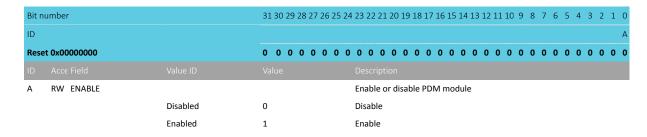

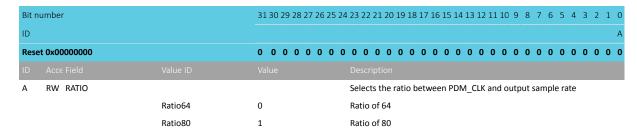

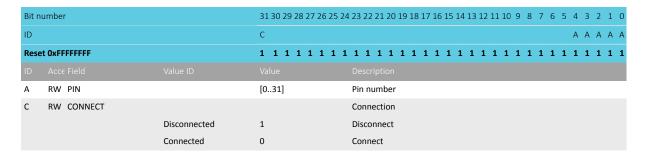

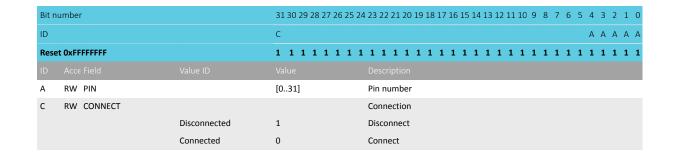

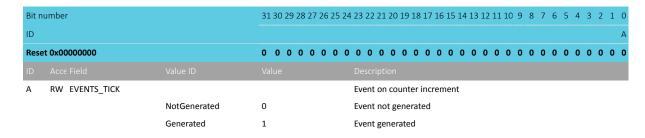

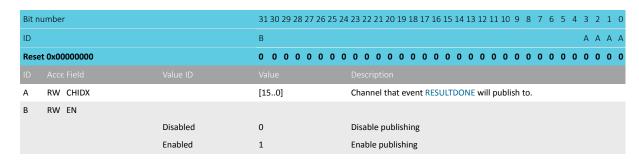

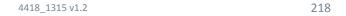

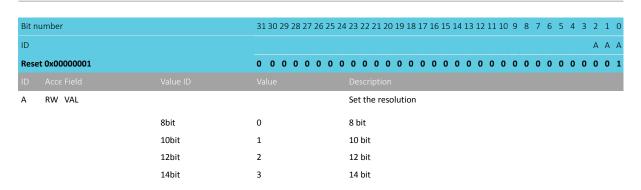

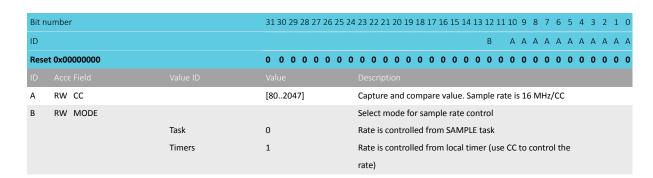

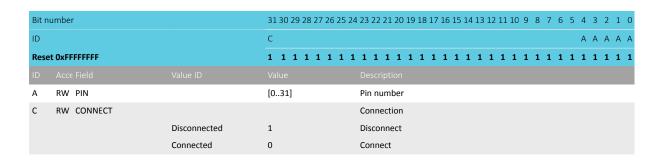

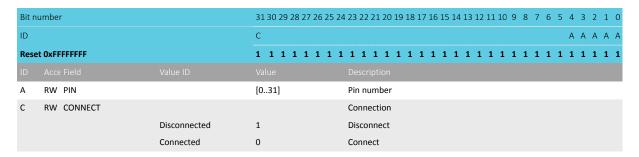

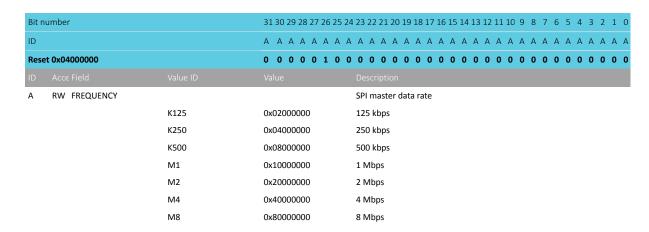

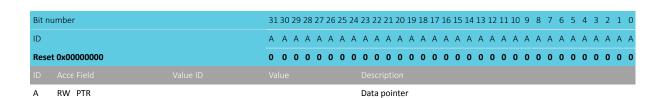

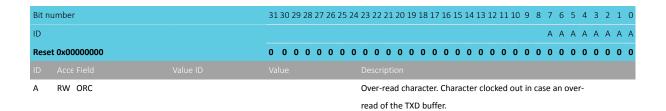

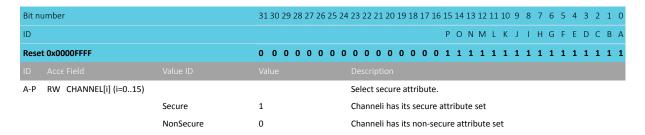

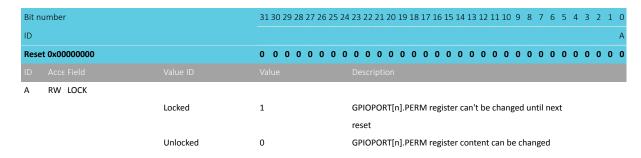

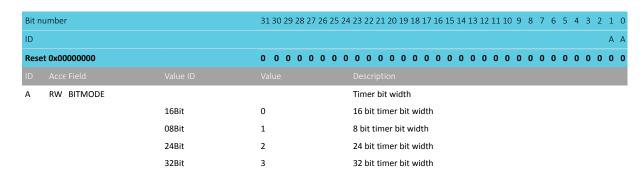

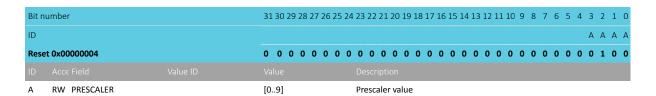

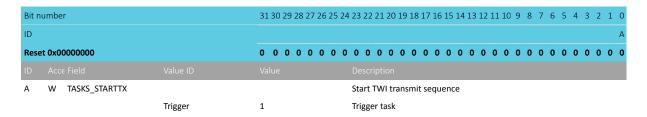

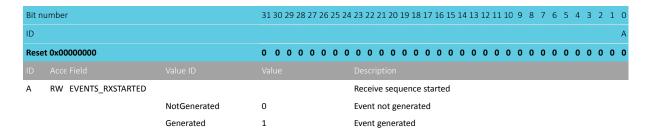

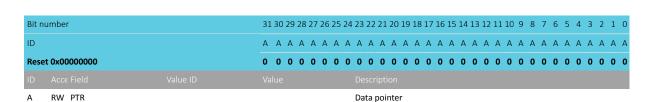

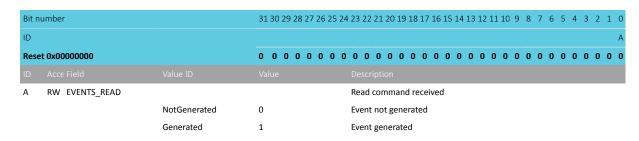

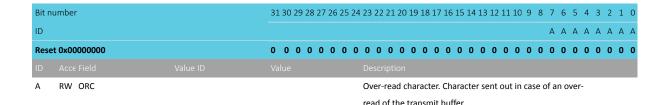

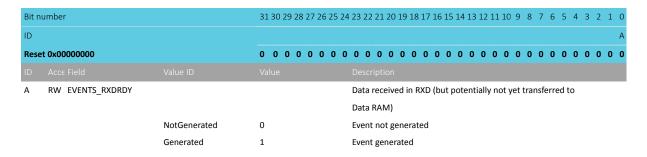

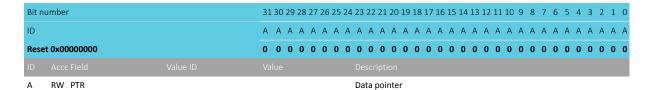

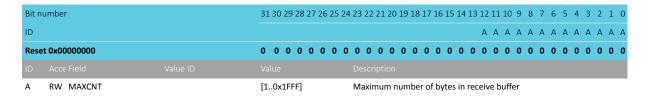

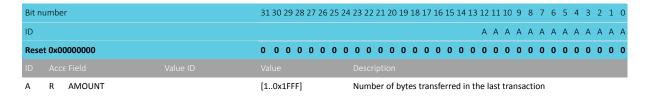

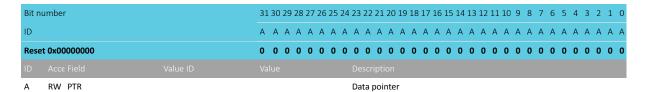

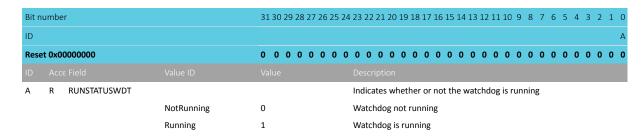

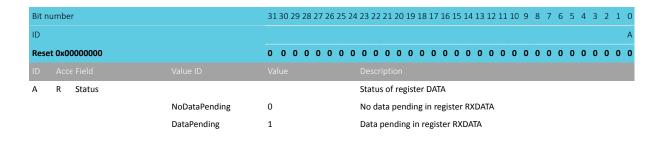

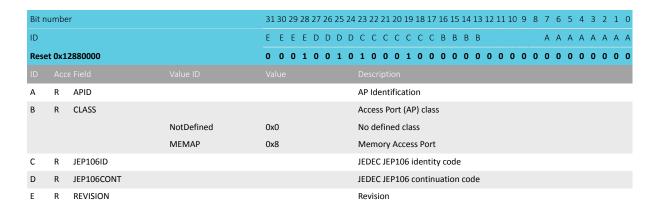

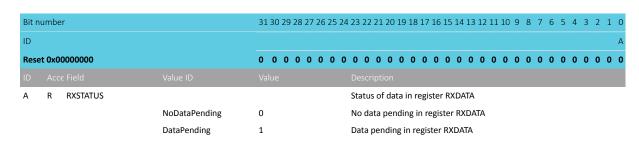

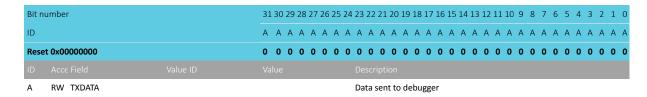

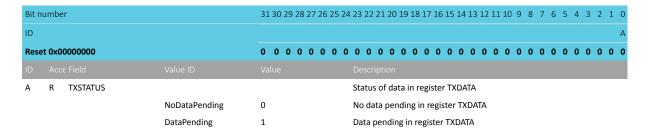

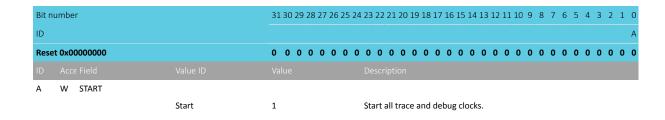

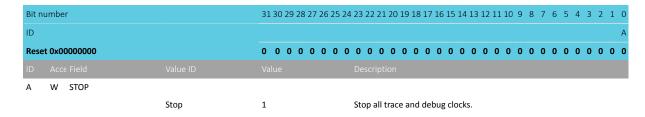

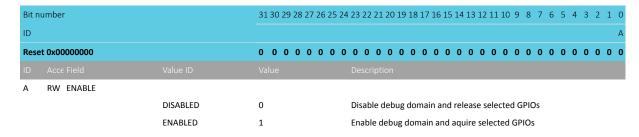

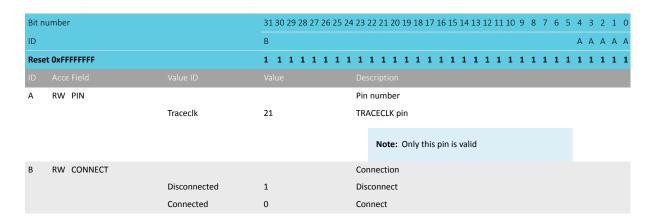

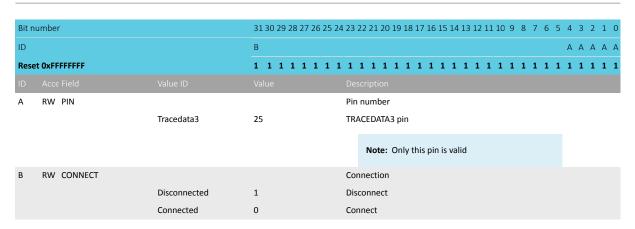

Individual registers are described using register tables. These tables are built up of two sections. The first three colored rows describe the position and size of the different fields in the register. The following rows describe the fields in more detail.

### 2.3.1 Fields and values

The **Id** (Field Id) row specifies the bits that belong to the different fields in the register. If a field has enumerated values, then every value will be identified with a unique value id in the **Value Id** column.

A blank space means that the field is reserved and read as undefined, and it also must be written as 0 to secure forward compatibility. If a register is divided into more than one field, a unique field name is specified for each field in the **Field** column. The **Value Id** may be omitted in the single-bit bit fields when values can be substituted with a Boolean type enumerator range, e.g. true/false, disable(d)/enable(d), on/off, and so on.

Values are usually provided as decimal or hexadecimal. Hexadecimal values have a 0x prefix, decimal values have no prefix.

The Value column can be populated in the following ways:

- Individual enumerated values, for example 1, 3, 9.

- Range of values, e.g. [0..4], indicating all values from and including 0 and 4.

- Implicit values. If no values are indicated in the **Value** column, all bit combinations are supported, or alternatively the field's translation and limitations are described in the text instead.

If two or more fields are closely related, the **Value Id**, **Value**, and **Description** may be omitted for all but the first field. Subsequent fields will indicate inheritance with '..'.

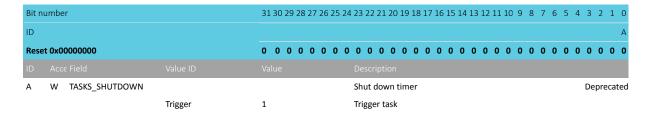

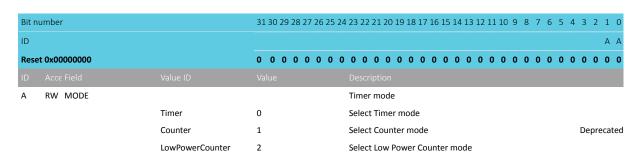

A feature marked **Deprecated** should not be used for new designs.

### 2.3.2 Permissions

Different fields in a register might have different access permissions enforced by hardware.

The access permission for each register field is documented in the Access column in the following ways:

| Access | Description     | Hardware behavior                                                                                                      |  |

|--------|-----------------|------------------------------------------------------------------------------------------------------------------------|--|

| RO     | Read-only       | Field can only be read. A write will be ignored.                                                                       |  |

| wo     | Write-only      | Field can only be written. A read will return an undefined value.                                                      |  |

| RW     | Read-write      | Field can be read and written multiple times.                                                                          |  |

| W1     | Write-once      | Field can only be written once per reset. Any subsequent write will be ignored. A read will return an undefined value. |  |

| RW1    | Read-write-once | Field can be read multiple times, but only written once per reset. Any subsequent write will be ignored.               |  |

Table 2: Register field permission schemes

# 2.4 Registers

| Register | Offset | Security | Description                                       |

|----------|--------|----------|---------------------------------------------------|

| DUMMY    | 0x514  |          | Example of a register controlling a dummy feature |

Table 3: Register overview

### 2.4.1 DUMMY

Address offset: 0x514

Example of a register controlling a dummy feature

| Bit r | number        |              | 31 30 29 28 27 26 2 | 5 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|---------------|--------------|---------------------|--------------------------------------------------------------------|

| ID    |               |              | D D [               | D CCC B A A                                                        |

| Rese  | et 0x00050002 |              | 0 0 0 0 0 0         | 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0                            |

| ID    |               |              |                     | Description                                                        |

| Α     | RW FIELD_A    |              |                     | Example of a read-write field with several enumerated              |

|       |               |              |                     | values                                                             |

|       |               | Disabled     | 0                   | The example feature is disabled                                    |

|       |               | NormalMode   | 1                   | The example feature is enabled in normal mode                      |

|       |               | ExtendedMode | 2                   | The example feature is enabled along with extra                    |

|       |               |              |                     | functionality                                                      |

| В     | RW FIELD_B    |              |                     | Example of a deprecated read-write field Deprecated                |

|       |               | Disabled     | 0                   | The override feature is disabled                                   |

|       |               | Enabled      | 1                   | The override feature is enabled                                    |

| С     | RW FIELD_C    |              |                     | Example of a read-write field with a valid range of values         |

|       |               | ValidRange   | [27]                | Example of allowed values for this field                           |

| D     | RW FIELD_D    |              |                     | Example of a read-write field with no restriction on the           |

|       |               |              |                     | values                                                             |

# 3 Product overview

## 3.1 Introduction

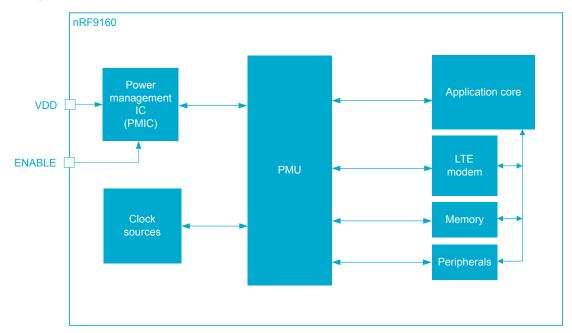

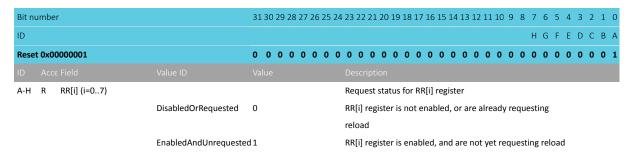

The nRF9160 is a low-power cellular IoT (Internet of Things) solution, integrating an ARM<sup>®</sup> Cortex<sup>®</sup>-M33 processor with advanced security features, a range of peripherals, as well as a complete LTE modem compliant with 3GPP LTE release 13 Cat-M1 and Cat-NB1, and 3GPP LTE release 14 Cat-NB1 and Cat-NB2 standards.

The ARM<sup>®</sup> Cortex-M33 processor is exclusively for user application software, and it offers 1 MB of flash and 256 kB of RAM dedicated to this use. The M33 application processor shares the power, clock and peripheral architecture with Nordic Semiconductor nRF51 and nRF52 Series of PAN/LAN SoCs, ensuring minimal porting efforts.

The peripheral set offers a variety of analog and digital functionality enabling single-chip implementation of a wide range of cellular IoT (Internet of Things) applications. ARM<sup>®</sup> TrustZone<sup>®</sup> technology, Cryptocell 310 and supporting blocks for system protection and key management, are embedded to enable advanced security needed for IoT applications.

The LTE modem integrates a very flexible transceiver that in hardware supports frequency range from 700 to 2200 MHz (through a single  $50~\Omega$  antenna pin), and a baseband processor handling LTE Cat-M1/NB1/NB2 protocol layers L1-L3 as well as IP upper layers offering secure socket API for the application. The modem is supported by pre-qualified software builds available for free from Nordic Semiconductor.

On specific nRF9160 device variants, the LTE modem supports A-GPS operation during sleep intervals in the LTE operation (RRC idle and PSM modes).

**Note:** Cat-NB2 is supported in LTE modem HW, but needs modem firmware support to get enabled. Please refer to *nRF9160 modem firmware release notes* found under nRF91 FW binaries downloads concerning availability of Cat-NB2 feature support".

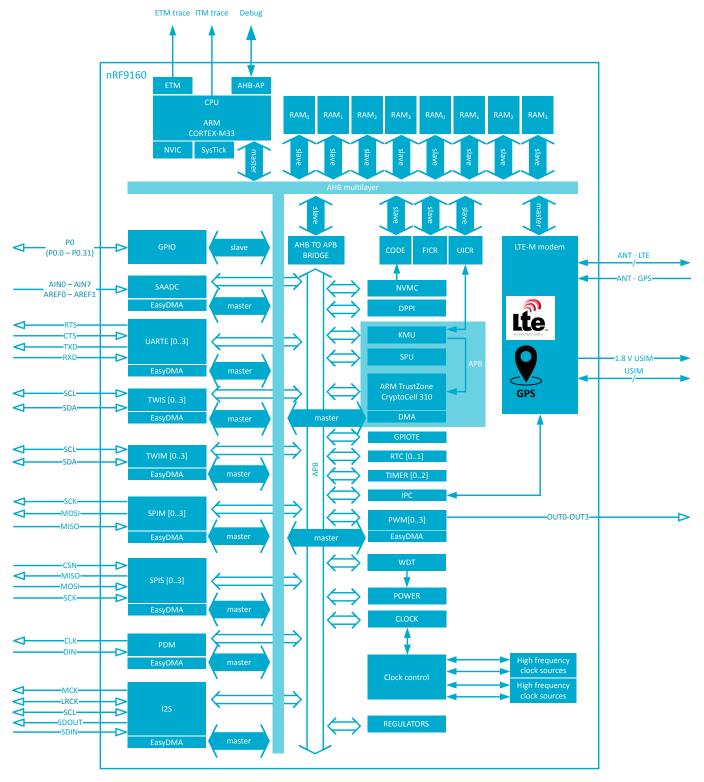

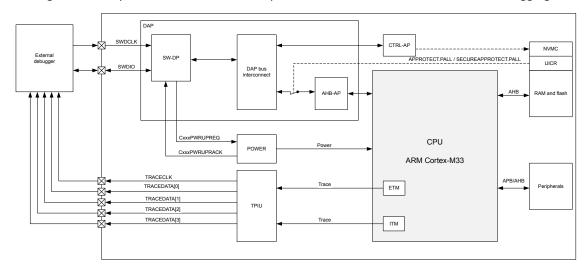

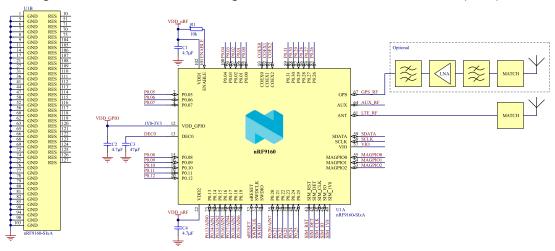

# 3.2 Block diagram

This block diagram illustrates the overall system. Arrows with white heads indicate signals that share physical pins with other signals.

Figure 1: Block diagram

# 3.3 Peripheral interface

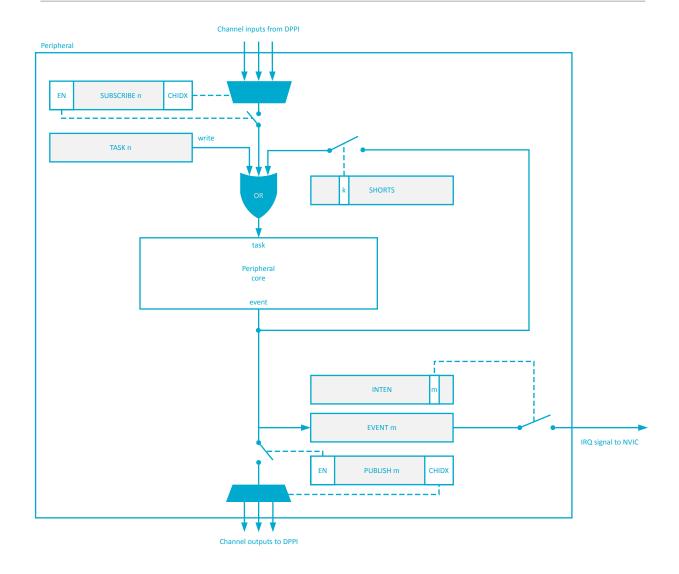

Peripherals are controlled by the CPU through configuration registers, as well as task and event registers. Task registers are inputs, enabling the CPU and other peripherals to initiate a functionality. Event registers are outputs, enabling a peripheral to trigger tasks in other peripherals and/or the CPU by tying events to CPU interrupts.

Figure 2: Tasks, events, shortcuts, publish, subscribe and interrupts

The distributed programmable peripheral interconnect (DPPI) feature enables peripherals to connect events to tasks without CPU intervention.

**Note:** For more information on DPPI and the DPPI channels, see DPPI - Distributed programmable peripheral interconnect on page 85.

## 3.3.1 Peripheral ID

Every peripheral is assigned a fixed block of 0x1000 bytes of address space, which is equal to 1024 x 32 bit registers.

See Instantiation on page 23 for more information about which peripherals are available and where they are located in the address map.

There is a direct relationship between peripheral ID and base address. For example, a peripheral with base address 0x40000000 is assigned ID=0, a peripheral with base address 0x40001000 is assigned ID=1, and a peripheral with base address 0x4001F000 is assigned ID=31.

Peripherals may share the same ID, which may impose one or more of the following limitations:

- Some peripherals share some registers or other common resources.

- Operation is mutually exclusive. Only one of the peripherals can be used at a time.

NORDIC

• Switching from one peripheral to another must follow a specific pattern (disable the first, then enable the second peripheral).

### 3.3.2 Peripherals with shared ID

In general (with the exception of ID 0), peripherals sharing an ID and base address may not be used simultaneously. The user can only enable one peripheral at the time on this specific ID.

When switching between two peripherals sharing an ID, the user should do the following to prevent unwanted behavior:

- Disable the previously used peripheral.

- Disable any publish/subscribe connection to the DPPI system for the peripheral that is being disabled.

- Clear all bits in the INTEN register, i.e. INTENCLR = 0xFFFFFFFF.

- Explicitly configure the peripheral that you are about to enable, and do not rely on configuration values that may be inherited from the peripheral that was disabled.

- Enable the now configured peripheral.

See which peripherals are sharing ID in Instantiation on page 23.

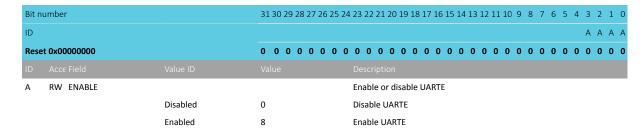

### 3.3.3 Peripheral registers

Most peripherals feature an ENABLE register. Unless otherwise is specified in the chapter, the peripheral registers must be configured before enabling the peripheral.

PSEL registers need to be set before a peripheral is enabled or started. Updating PSEL registers while the peripheral is running has no effect. In order to connect a peripheral to a different GPIO, the peripheral must be disabled, the PSEL register updated and the peripheral re-enabled. It takes four CPU cycles between the PSEL register update and the connection between a peripheral and a GPIO becoming effective.

Note that the peripheral must be enabled before tasks and events can be used.

Most of the register values are lost during System OFF or when a reset is triggered. Some registers will retain their values in System OFF or for some specific reset sources. These registers are marked as retained in the register description for a given peripheral. For more info on these retained registers' behavior, see chapter Reset on page 55.

### 3.3.4 Bit set and clear

Registers with multiple single-bit bit fields may implement the set-and-clear pattern. This pattern enables firmware to set and clear individual bits in a register without having to perform a read-modify-write operation on the main register.

This pattern is implemented using three consecutive addresses in the register map, where the main register is followed by dedicated SET and CLR registers (in that exact order).

The SET register is used to set individual bits in the main register, while the CLR register is used to clear individual bits in the main register. Writing 1 to a bit in SET or CLR register will set or clear the same bit in the main register respectively. Writing 0 to a bit in SET or CLR register has no effect. Reading the SET or CLR register returns the value of the main register.

**Note:** The main register may not be visible and hence not directly accessible in all cases.

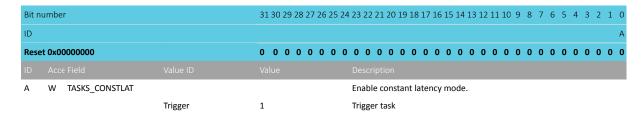

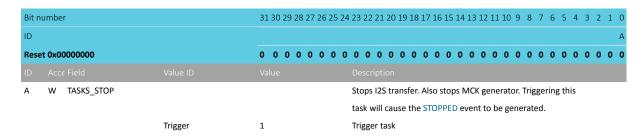

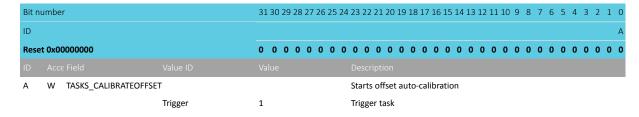

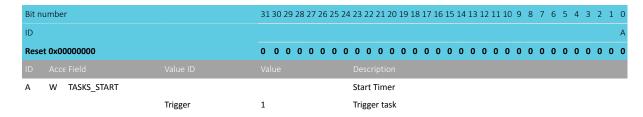

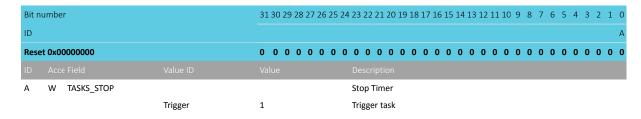

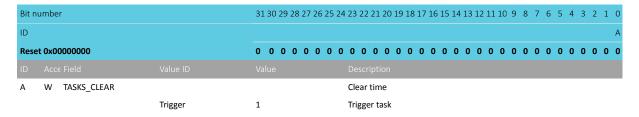

### 3.3.5 Tasks

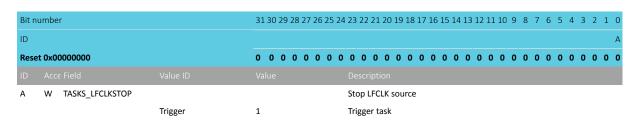

Tasks are used to trigger actions in a peripheral, for example to start a particular behavior. A peripheral can implement multiple tasks with each task having a separate register in that peripheral's task register group.

A task is triggered when firmware writes 1 to the task register, or when the peripheral itself or another peripheral toggles the corresponding task signal. See the figure Tasks, events, shortcuts, publish, subscribe and interrupts on page 15.

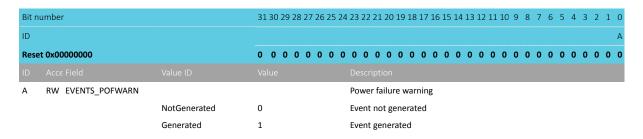

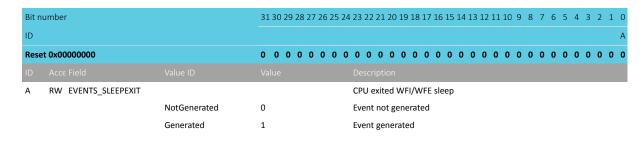

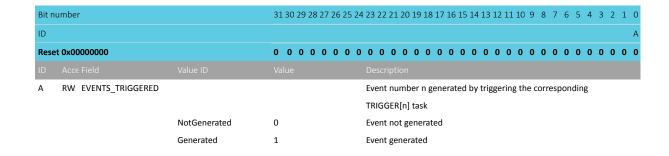

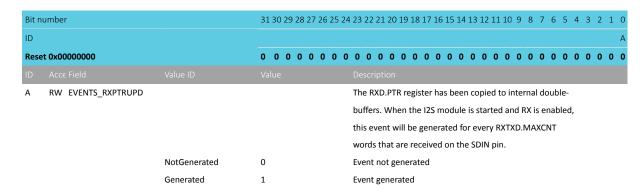

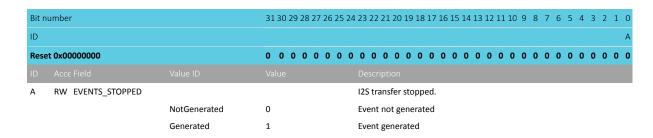

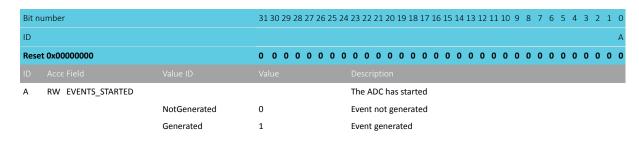

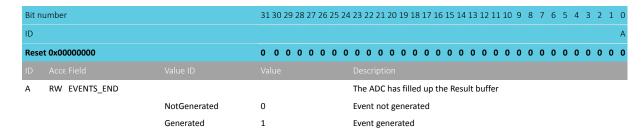

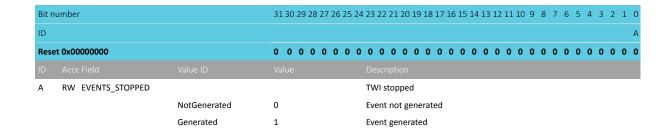

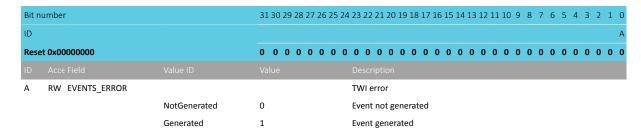

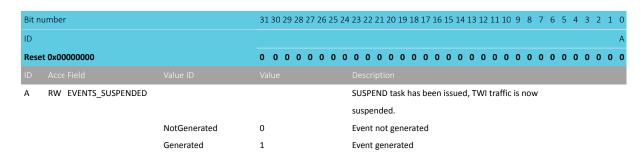

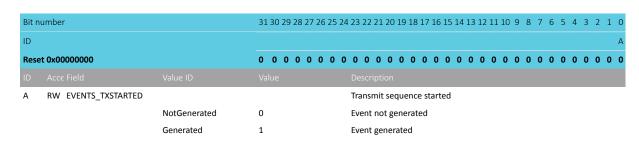

### 3.3.6 Events

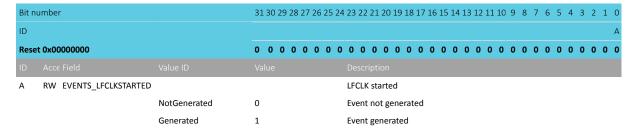

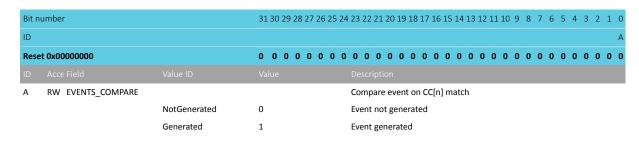

Events are used to notify peripherals and the CPU about events that have happened, for example a state change in a peripheral. A peripheral may generate multiple events, where each event has a separate register in that peripheral's event register group.

An event is generated when the peripheral itself toggles the corresponding event signal, and the event register is updated to reflect that the event has been generated (see figure Tasks, events, shortcuts, publish, subscribe and interrupts on page 15). An event register is only cleared when firmware writes 0 to it. Events can be generated by the peripheral even when the event register is set to 1.

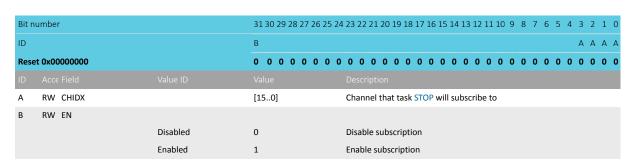

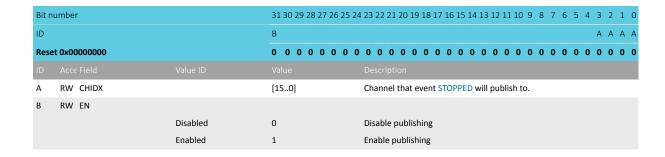

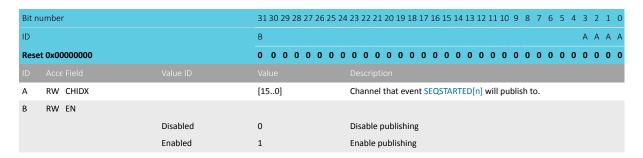

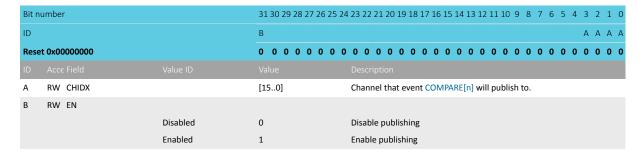

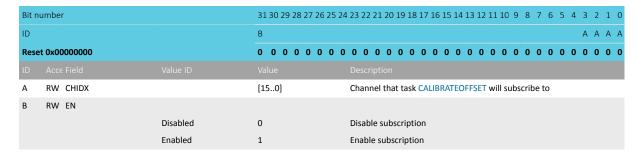

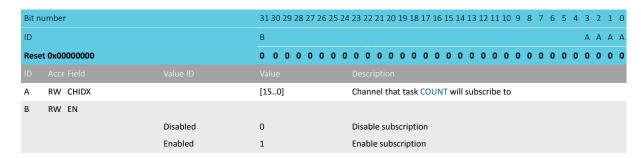

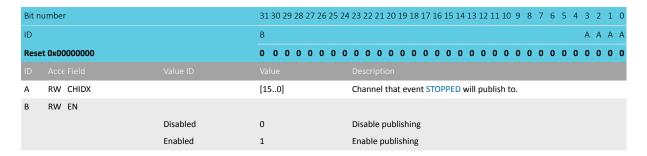

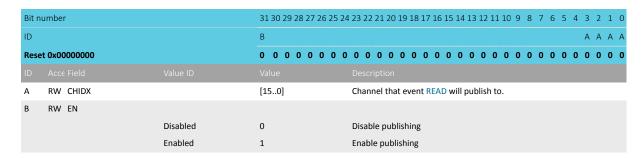

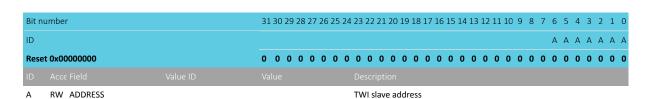

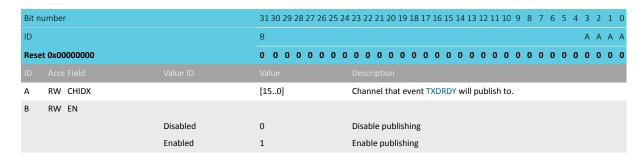

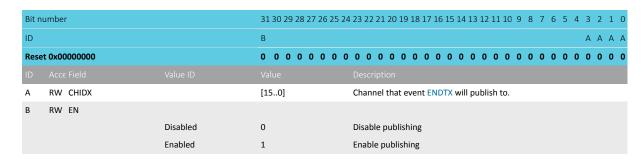

### 3.3.7 Publish / Subscribe

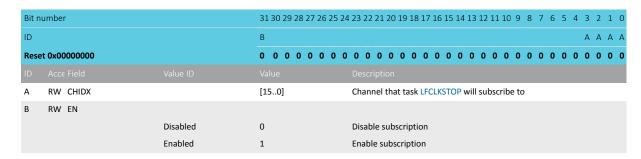

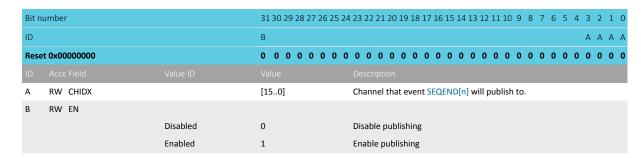

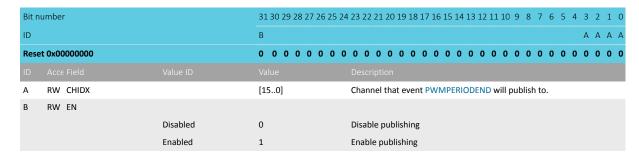

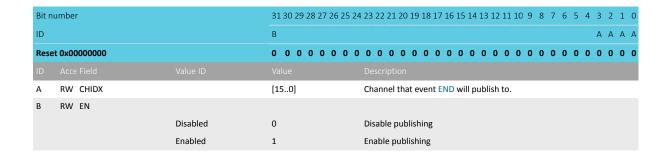

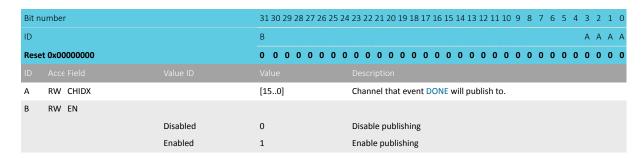

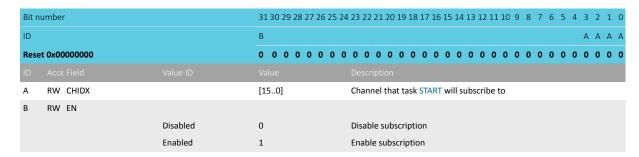

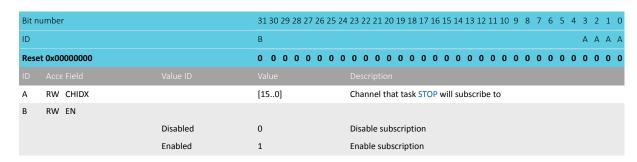

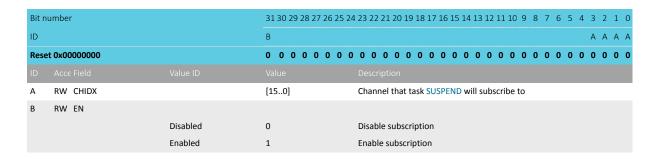

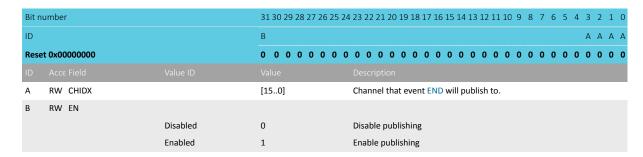

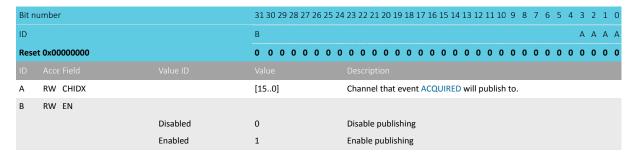

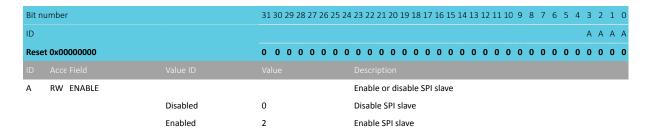

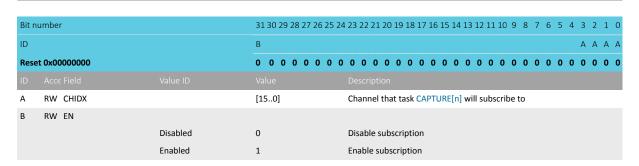

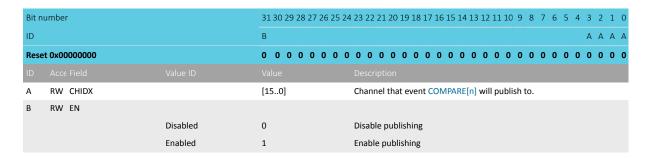

Events and tasks from different peripherals can be connected together through the DPPI. See Tasks, events, shortcuts, publish, subscribe and interrupts on page 15. This is done through publish / subscribe registers in each peripheral. An event can be published onto a DPPI channel by configuring the event's PUBLISH register. Similarly a task can subscribe to a DPPI channel by configuring the task's SUBSCRIBE register.

See DPPI - Distributed programmable peripheral interconnect on page 85 for details.

### 3.3.8 Shortcuts

A shortcut is a direct connection between an event and a task within the same peripheral. If a shortcut is enabled, the associated task is automatically triggered when its associated event is generated.

Using shortcuts is equivalent to making the connection outside the peripheral and through the DPPI. However, the propagation delay when using shortcuts is usually shorter than the propagation delay through the DPPI.

Shortcuts are predefined, which means that their connections cannot be configured by firmware. Each shortcut can be individually enabled or disabled through the shortcut register, one bit per shortcut, giving a maximum of 32 shortcuts for each peripheral.

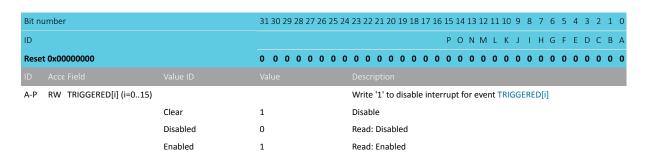

### 3.3.9 Interrupts

All peripherals support interrupts. Interrupts are generated by events.

A peripheral only occupies one interrupt, and the interrupt number follows the peripheral ID. For example, the peripheral with ID=4 is connected to interrupt number 4 in the nested vectored interrupt controller (NVIC).

Using registers INTEN, INTENSET, and INTENCLR, every event generated by a peripheral can be configured to generate that peripheral's interrupt. Multiple events can be enabled to generate interrupts simultaneously. To resolve the correct interrupt source, the event registers in the event group of peripheral registers will indicate the source.

Some peripherals implement only INTENSET and INTENCLR registers, and the INTEN register is not available on those peripherals. See the individual peripheral chapters for details. In all cases, reading back the INTENSET or INTENCLR register returns the same information as in INTEN.

Each event implemented in the peripheral is associated with a specific bit position in the INTEN, INTENSET and INTENCLR registers.

The relationship between tasks, events, shortcuts, and interrupts is illustrated in figure Tasks, events, shortcuts, publish, subscribe and interrupts on page 15.

### Interrupt clearing

Interrupts should always be cleared.

Clearing an interrupt by writing 0 to an event register, or disabling an interrupt using the INTENCLR register, may take a number of CPU clock cycles to take effect. This means that an interrupt may reoccur immediately, even if a new event has not come, if the program exits an interrupt handler after the interrupt is cleared or disabled but before it has taken effect.

**Note:** To avoid an interrupt reoccurring before a new event has come, the program should perform a read from one of the peripheral registers. For example, the event register that has been cleared, or the INTENCLR register that has been used to disable the interrupt.

Care should be taken to ensure that the compiler does not remove the read operation as an optimization.

# 3.3.10 Secure/non-secure peripherals

For some peripherals, the security configuration can change from secure to non-secure, or vice versa. Care must be taken when changing the security configuration of a peripheral, to prevent security information leakage and ensure correct operation.

The following sequence should be followed, where applicable, when configuring and changing the security settings of a peripheral in the SPU - System protection unit on page 263:

- **1.** Stop peripheral operation

- 2. Disable the peripheral

- 3. Remove pin connections

- 4. Disable DPPI connections

- 5. Clear sensitive registers (e.g. writing back default values)

- 6. Change peripheral security setting in the SPU System protection unit on page 263

- 7. Re-enable the peripheral

# 4 Application core

## 4.1 CPU

The ARM<sup>®</sup> Cortex-M33 processor has a 32-bit instruction set (Thumb<sup>®</sup>-2 technology) that implements a superset of 16 and 32-bit instructions to maximize code density and performance.

This processor implements several features that enable energy-efficient arithmetic and high-performance signal processing, including:

- Digital signal processing (DSP) instructions

- Single-cycle multiply and accumulate (MAC) instructions

- Hardware divide

- 8- and 16-bit single instruction, multiple data (SIMD) instructions

- Single-precision floating-point unit (FPU)

- Memory Protection Unit (MPU)

- ARM<sup>®</sup> TrustZone<sup>®</sup> for ARMv8-M

The ARM<sup>®</sup> Cortex Microcontroller Software Interface Standard (CMSIS) hardware abstraction layer for the ARM<sup>®</sup> Cortex processor series is implemented and available for the M33 CPU.

Real-time execution is highly deterministic in thread mode, to and from sleep modes, and when handling events at configurable priority levels via the nested vectored interrupt controller (NVIC).

Executing code from internal or external flash will have a wait state penalty. The instruction cache can be enabled to minimize flash wait states when fetching instructions. For more information on cache, see Cache on page 31. The section Electrical specification on page 20 shows CPU performance parameters including the wait states in different modes, CPU current and efficiency, and processing power and efficiency based on the CoreMark® benchmark.

# 4.1.1 CPU and support module configuration

The ARM® Cortex®-M33 processor has a number of CPU options and support modules implemented on the device.

| Option / Module    | Description                                               | Implemented                           |

|--------------------|-----------------------------------------------------------|---------------------------------------|

| Core options       |                                                           |                                       |

| NVIC               | Nested vectored interrupt controller                      |                                       |

| PRIORITIES         | Priority bits                                             | 3                                     |

| WIC                | Wake-up interrupt controller                              | NO                                    |

| Endianness         | Memory system endianness                                  | Little endian                         |

| DWT                | Data watchpoint and trace                                 | YES                                   |

| Modules            |                                                           |                                       |

| MPU_NS             | Number of non-secure memory protection unit (MPU) regions | 16                                    |

| MPU_S              | Number of secure MPU regions                              | 16                                    |

| SAU                | Number of security attribution unit (SAU) regions         | 0, see SPU for more information about |

|                    |                                                           | secure regions.                       |

| FPU                | Floating-point unit                                       | YES                                   |

| DSP                | Digital signal processing extension                       | YES                                   |

| ARMv8-M TrustZone® | ARMv8-M security extensions                               | YES                                   |

| CPIF               | Co-processor interface                                    | NO                                    |

| ETM                | Embedded trace macrocell                                  | YES                                   |

| ITM                | Instrumentation trace macrocell                           | YES                                   |

| МТВ                | Micro trace buffer                                        | NO                                    |

| СТІ                | Cross trigger interface                                   | YES                                   |

| BPU                | Breakpoint unit                                           | YES                                   |

| HTM                | AMBA <sup>™</sup> AHB trace macrocell                     | NO                                    |

# 4.1.2 Electrical specification

## 4.1.2.1 CPU performance

The CPU clock speed is 64 MHz. Current and efficiency data is taken when in System ON and the CPU is executing the CoreMark  $^{^{\text{TM}}}$  benchmark. It includes power regulator and clock base currents. All other blocks are IDLE.

| Symbol                  | Description                                               | Min. | Тур. | Max. | Units     |

|-------------------------|-----------------------------------------------------------|------|------|------|-----------|

| W <sub>FLASH</sub>      | CPU wait states, running from flash, cache disabled       | 0    |      | 4    |           |

| W <sub>FLASHCACHE</sub> | CPU wait states, running from flash, cache enabled        | 0    |      | 2    |           |

| $W_{RAM}$               | CPU wait states, running from RAM                         |      |      | 0    |           |

| CM <sub>FLASH</sub>     | CoreMark <sup>1</sup> , running from flash, cache enabled |      | 243  |      | Corel     |

| CM <sub>FLASH/MHz</sub> | CoreMark per MHz, running from flash, cache enabled       |      | 3.79 |      | CoreMark/ |

|                         |                                                           |      |      |      | MHz       |

| CM <sub>FLASH/mA</sub>  | CoreMark per mA, running from flash, cache enabled, DC/   |      | 84   |      | Corel     |

|                         | DC                                                        |      |      |      | mA        |

# 4.2 Memory

The application microcontroller has embedded 1024 kB flash and 256 kB RAM for application code and data storage.

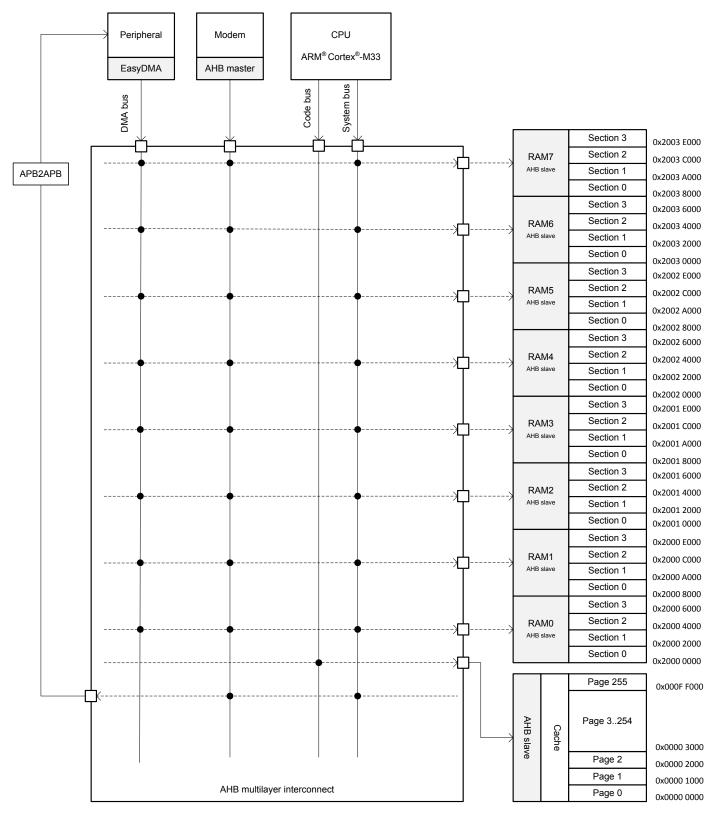

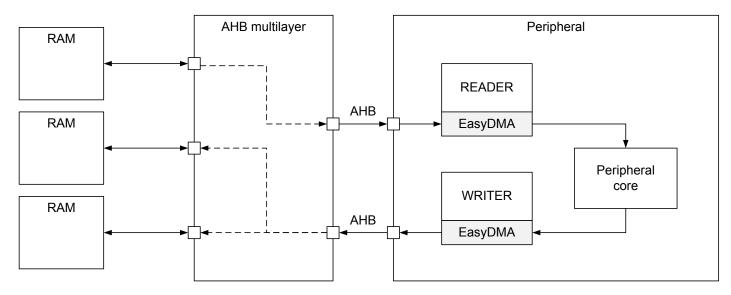

As illustrated in Memory layout on page 21, both CPU and EasyDMA are able to access RAM via the AHB multilayer interconnect. See AHB multilayer interconnect on page 47 and EasyDMA on page 44 for more information about AHB multilayer interconnect and EasyDMA respectively. The LTE modem can access all application MCU memory, but typically a small portion of RAM is dedicated to data exchange between application MCU and the modem baseband controller.

NORDIC\*

<sup>&</sup>lt;sup>1</sup> Using IAR compiler

Figure 3: Memory layout

### **RAM - Random access memory**

RAM can be read and written an unlimited number of times by the CPU and the EasyDMA.

Each RAM AHB slave is connected to one or more RAM sections. See Memory layout on page 21 for more information.

The RAM blocks power states and retention states in System ON and System OFF modes are controlled by the VMC.

### Flash - Non-volatile memory

Flash can be read an unlimited number of times by the CPU and is accessible via the AHB interface connected to the CPU, see Memory layout on page 21 for more information. There are restrictions on the number of times flash can be written and erased, and also on how it can be written. For more information, see Absolute maximum ratings on page 397. Writing to flash is managed by the non-volatile memory controller (NVMC).

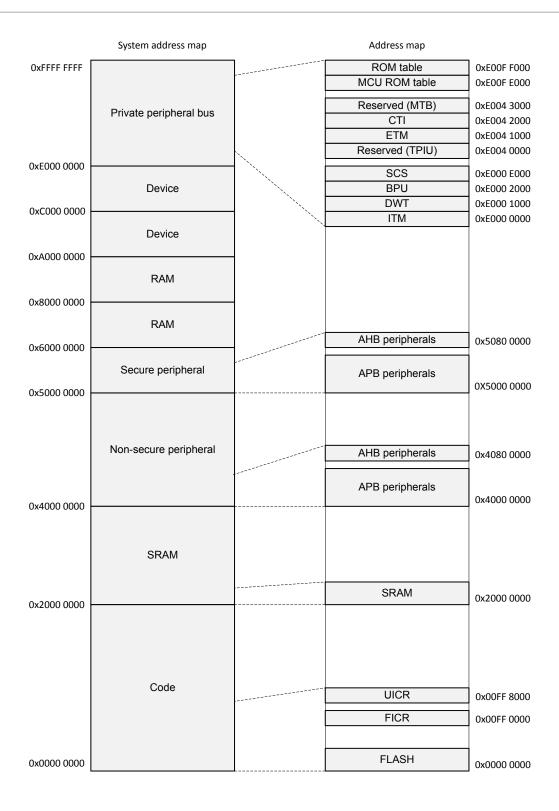

# 4.2.1 Memory map

All memory and registers are found in the same address space, as illustrated in the device memory map below.

Figure 4: Memory map

Some of the registers are retained (their values kept). Read more about retained registers in Retained registers on page 56 and Reset behavior on page 56.

### 4.2.2 Instantiation

| ID | Base address | Peripheral | Instance | Secure mapping | DMA security | Description            |

|----|--------------|------------|----------|----------------|--------------|------------------------|

| 3  | 0x50003000   | SPU        | SPU      | S              | NA           | System Protection Unit |

| Mathematical Regulations   REGULATIONS   REGULATIONS   NA   Regulation configuration   Regulations   NA   Regulation configuration   Regulations   NA   Regulation configuration   Regulations   NA   Regulation configuration   Regulations                                                                                                                                                                                                                                                                                                                                                                            | ID | Base address | Peripheral | Instance       | Secure mapping | DMA security | Description                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------|------------|----------------|----------------|--------------|------------------------------|

| Decided Control   Decide Control   CLOCK   CLOCK : S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4  | 0x50004000   | REGULATORS | REGULATORS : S | US             | NA           | Regulator configuration      |

| 5         Ox.000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7  |              | REGOLATORS |                |                | TV/          | negatation configuration     |

| 5         0x40005000         POWER         POWER: NS         US         NA         Power control           6         0x50000000         CFRLAPPERI         CFRLAPPERI         S         NA         CTRLAPPERI           0x50000000         SPIM         SPIM0 : NS         US         SA         SPI Invarier 0           0x50000000         SPIS         SPI90 : NS         US         SA         SPI Slave 0           0x50000000         TVIMIN DESTRUCTIONS         US         SA         Two-wire interface master 0           0x50000000         TVIMIN DESTRUCTIONS         US         SA         Two-wire interface slave 0           0x50000000         UARTE UARTED : S         US         SA         Two-wire interface slave 0           0x50000000         UARTE UARTED : S         US         SA         SPI slave 1           0x50000000         SPIM         SPIRIL : S         US         SA         SPI slave 1           0x50000000         TVIMIN : S         UARTED : S         US         SA         SPI slave 1           0x50000000         TVIMIN : S         UARTED : S         US         SA         Two-wire interface slave 1           0x50000000         TVIMIN : TWIMI : S         US         SA         Two-wire interface slave 1 <td>5</td> <td></td> <td>CLOCK</td> <td></td> <td>US</td> <td>NA</td> <td>Clock control</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5  |              | CLOCK      |                | US             | NA           | Clock control                |

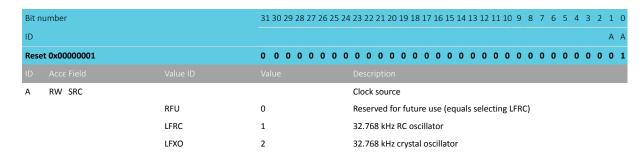

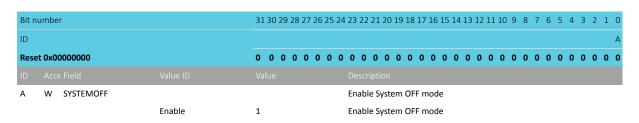

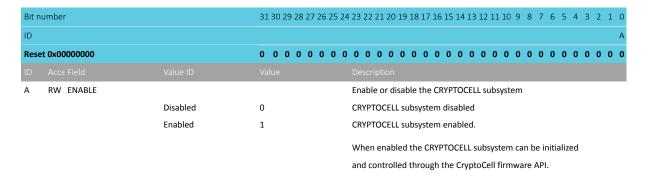

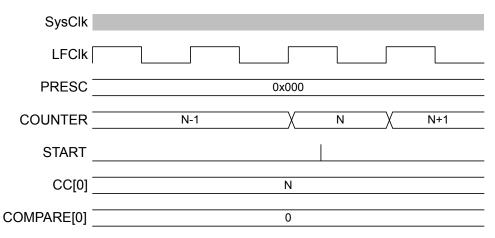

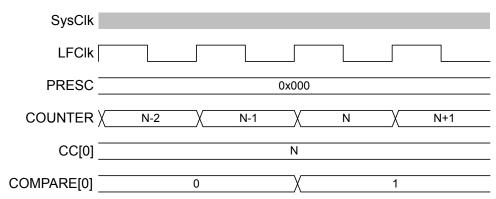

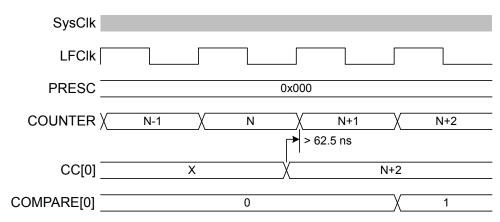

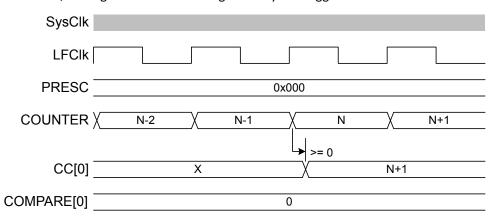

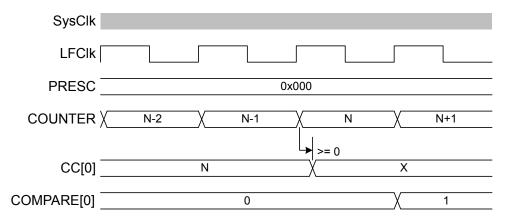

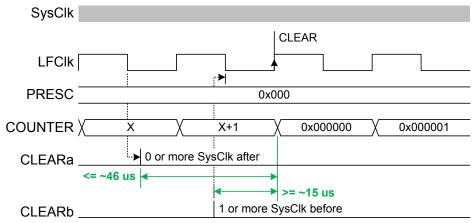

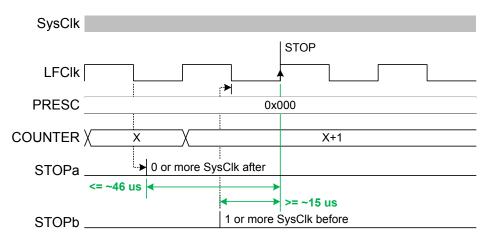

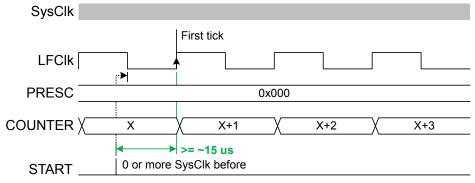

| 8         0x50000000 billion (NS)         SPIMO (S) billion (NS)         US         SA         SPI Insister O           8         0x50000000 billion (NS)         SPIS (SPIS) Signo (NS)         US         SA         SPI slave O           8         0x50000000 billion (NS)         TWIND (SS) Signo (NS)         US         SA         Two write interface moster O           8         0x50000000 billion (NS)         TWIND (NS) Signo (NS)         US         SA         Two write interface slave O           8         0x50000000 billion (NS) Signo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5  |              | POWER      |                | US             | NA           | Power control                |