# Impedance Matched Ultra Low Profile 0603 Balun For TI AFE7950 and ADC12DJ5200RF chipsets

#### **Description:**

The X4BD130LTI is an ultra-small low profile balanced to unbalanced transformer designed specifically for Texas Instruments AFE7950 and ADC12DJ5200RF chipsets. The X4BD130LTI is available on tape and reel for pick and place high volume manufacturing.

All of the Xinger components are constructed from ceramic filled PTFE composites, which possess excellent electrical and mechanical stability. All parts have been subjected to rigorous qualification testing and units are 100% RF tested. Produced in an ENIG final finish.

#### **Electrical Specifications\*\***

#### Features:

- 9200-16150 MHz

- 50 Ohm to 2 x50 Ohm

- 5G Applications

- Very Low Loss

- Tight Amplitude Balance

- Input to Output DC Isolation

- Production Friendly

- Tape and Reel

- Non-conductive Surface

- RoHS Compliant

- Halogen Free

| Frequency   | Port<br>Impedance        | Insertion<br>Loss | Return<br>Loss          | Amplitude<br>Balance |

|-------------|--------------------------|-------------------|-------------------------|----------------------|

| MHz         | Unbalanced :<br>Balanced | dB Max            | dB Min                  | dB Max               |

| 9200-14000  | 50:100                   | 0.7               | 18                      | ± 1.0                |

| 14000-16150 | 50:100                   | 1.0               | 16                      | ± 1.5                |

|             | Phase<br>Balance         | CMRR              | Power                   | Operating Temp.      |

|             | Degrees                  | dB Max            | Avg. CW<br>Watts @105°C | °C                   |

|             | ± 9                      | 20                | 1                       | -55 to +140          |

|             | ± 12                     | 16                | 1                       | -55 to +140          |

<sup>\*\*</sup>Specification based on performance of unit properly installed on a TTM test board with small signal applied.

\*Specifications subject to change without notice. Refer to parameter definitions for details.

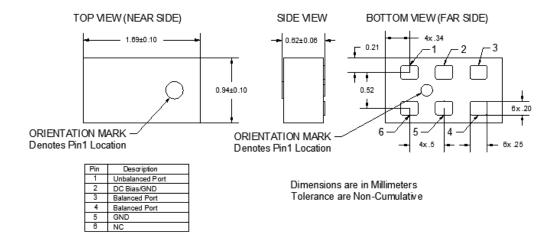

#### **Mechanical Outline:**

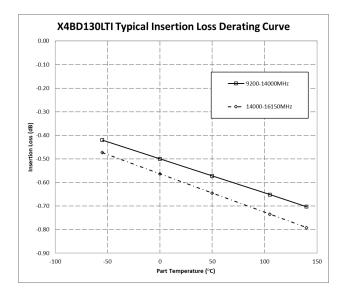

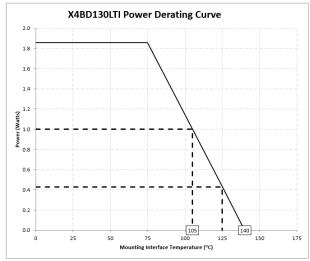

#### **Insertion Loss and Power Derating Curves:**

#### **Insertion Loss Derating:**

The insertion loss, at a given frequency, of a group of Balun is measured at 25°C and then averaged. The measurements are performed under small signal conditions (i.e. using a Vector Network Analyzer). The process is repeated at -55°C and 140°C. A best-fit line for the measured data is computed and then plotted from -55°C to 140°C.

### **Power Derating:**

The power handling and corresponding power derating plots are a function of the thermal resistance, mounting surface temperature (base plate temperature), maximum continuous operating temperature of the Balun, and the thermal insertion loss. The thermal insertion loss is defined in the Power Handling section of the data sheet.

As the mounting interface temperature approaches the maximum continuous operating temperature, the power handling decreases to zero.

If mounting temperature is greater than 105°C, Xinger Balun will perform reliably as long as the input power is derated to the curve above.

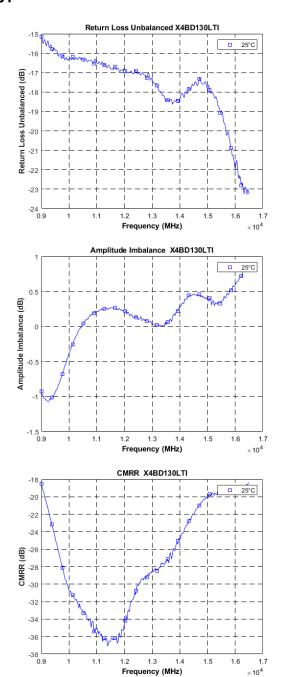

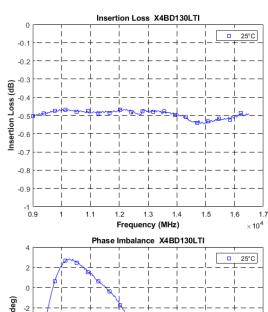

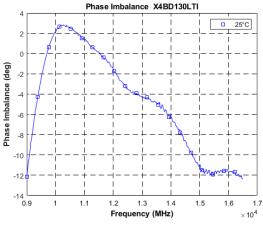

# Typical Performance: 9200 MHz to 16150 MHz

## **Definition of Measured Specifications:**

| Parameter                        | Definition                                                                           | Mathematical Representation                                 |  |

|----------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| Return Loss                      | The impedance match at the single ended port.                                        | $RL = 20Log_{10}(S_{11})$                                   |  |

| Differential Port<br>Return Loss | The impedance match at the differential port.                                        | $RLD = 20Log_{10} 0.5*(S_{22} - S_{23} - S_{32} + S_{33}) $ |  |

| Insertion Loss                   | Power loss from common mode to differential mode.                                    | $ILD = 20Log_{10}(0.707 * (S_{21} - S_{31}))$               |  |

| Phase Imbalance                  | The difference in phase angle between the two differential ports, offset by 180 deg. | $PB = (Phase(S_{21}) - Phase(S_{31})) - 180^{\circ}$        |  |

| Amplitude<br>Imbalance           | The ratio of the power at differential ports.                                        | $AB = 20 Log_{10} \left  \frac{S_{21}}{S_{31}} \right $     |  |

| Common Mode<br>Rejection Ratio   | The ratio of powers of the differential gain to the common-mode gain.                | $CMRR = \pm 20 Log_{10}(S_{21} + S_{31})/(S_{21} - S_{31})$ |  |

## **Peak Power Handling:**

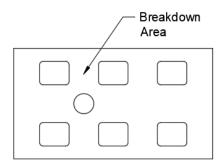

High-Pot testing of these components during the qualification procedure resulted in a minimum breakdown voltage of 1Kv (minimum recorded value). This voltage level corresponds to a breakdown resistance capable of handling at least 12dB peaks over average power levels, for very short durations. The breakdown location consistently occurred across the pads and the ground bar (see illustration below). The breakdown levels at these points will be affected by any contamination in the gap area around these pads. These areas must be kept clean for optimum performance. It is recommended that the user test for voltage breakdown under the maximum operating conditions and over worst case modulation induced power peaking. This evaluation should also include extreme environmental conditions (such as high humidity).