ETR0509\_017

## 1A Driver Transistor Built-In Step-Down DC/DC Converters

### ■ GENERAL DESCRIPTION

$\bigstar$  Green Operation Compatible

The XC9223/XC9224 series are synchronous step-down DC/DC converters with a  $0.21\Omega$  (TYP.) P-channel driver transistor and a synchronous  $0.23\Omega$  (TYP.) N-channel switching transistor built-in. A highly efficient and stable current can be supplied up to 1.0A by reducing ON resistance of the built-in transistor. With a high switching frequency of 1.0MHz or 2.0MHz, a small inductor is selectable; therefore, the XC9223/XC9224 series are ideally suited to applications with height limitation such as HDD or space-saving applications.

Current limit value can be chosen either 1.2A (MIN.) when the LIM pin is high level, or 0.6A (MIN.) when the LIM pin is low level for using the power supply which current limit value differs such as USB or AC adapter. With the MODE/SYNC pin, the XC9223/XC9224 series provide mode selection of the fixed PWM control or automatically switching current limit PFM/PWM control. As for preventing unwanted switching noise, the XC9223/XC9224 series can be synchronized with an external clock signal within the range of ± 25% toward an internal clock signal via the MODE/SYNC pin. For protection against heat damage of the ICs, the XC9223/XC9224 series build in three protection functions: integral latch protection, thermal shutdown, and short-circuit protection. With the built-in UVLO (Under Voltage Lock Out) function, the internal P-channel driver transistor is forced OFF when input voltage becomes 1.8V or lower. The XC9223/KC9224 series' detector function monitors the discretional voltage by external resistors.

### APPLICATIONS

- Magnetic disk drive

- Note PCs / Tablet PCs

- OCD-R / RW, DVD

- Mobile devices / terminals

- Digital still cameras / Camcorders

- Multi-function power supplies

## ■FEATURES

| Input Voltage Range      | : 2.5V ~ 6.0V                        |

|--------------------------|--------------------------------------|

| Output Voltage Range     | $: 0.9V \sim V_{IN}$ (set by FB pin) |

| Oscillation Frequency    | : 1MHz, 2MHz (+15% accuracy)         |

|                          |                                      |

| Output Current           | : 1.0A                               |

| Maximum Current          | : 0.6A (MIN.) ~ 0.9A (MAX)           |

| Limit                    | with LIM pin='L'                     |

|                          | : 1.2A (MIN.) ~ 2.0A (MAX.)          |

|                          | with LIM pin='H'                     |

| Controls                 | : PWM/PFM or PWM by MODE pin         |

| Protection Circuits      | : Thermal shutdown                   |

|                          | Integral latch method                |

|                          | 0                                    |

|                          | Short-circuit protection             |

| Soft-Start Time          | : 1ms (TYP.) internally set          |

| Voltage Detector         | : 0.712V Detection,                  |

|                          | N-channel open drain                 |

| Built-in P-channel       | : 0.21Ω                              |

| MOSFET                   |                                      |

| Built-in Synchronous     | : 0.23Ω                              |

| N-channel MOSFET         | (No Schottky Barrier Diode Required) |

| High Efficiency          | : 95% (VIN=5.0V, VOUT=3.3V)          |

| Synchronized with an E   |                                      |

| Ceramic Capacitor Com    |                                      |

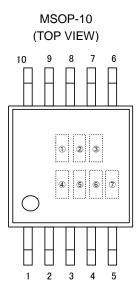

| Packages                 | : MSOP-10, USP-10B                   |

|                          |                                      |

| Environmentally Friendly | : EU RoHS Compliant, Pb Free         |

|                          |                                      |

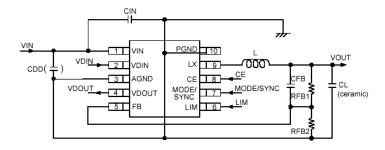

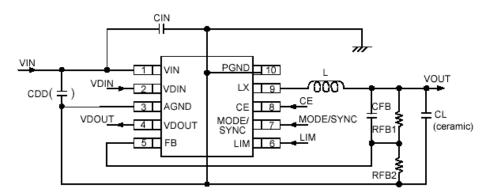

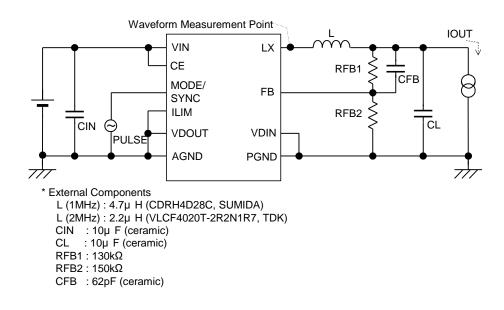

## ■TYPICAL APPLICATION CIRCUIT

(\*1) A capacitor of 2200pF~0.1  $\mu$  F is recommended to place at the  $C_{\text{DD}}$  between the AGND pin and the  $V_{\text{IM}}$  pin.

Please refer to the page showing INSTRUCTION ON PATTERN LAYOUT for more detail.

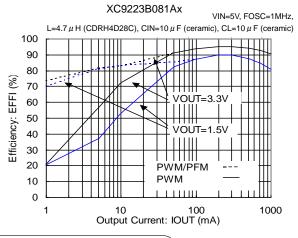

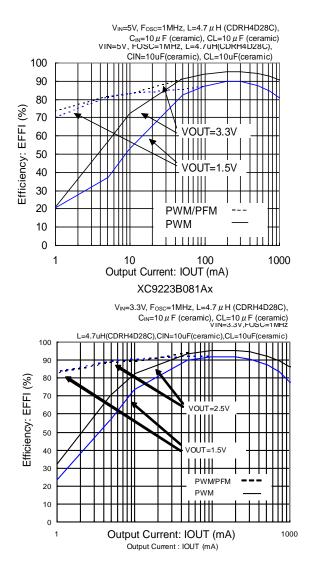

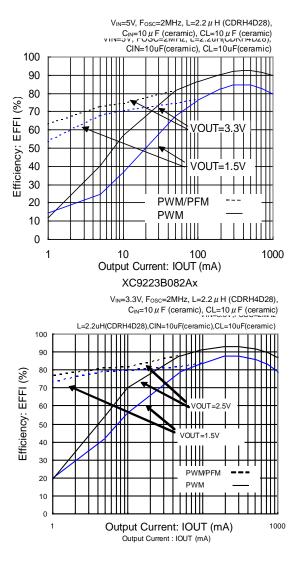

## TYPICAL PERFORMANCE CHARACTERISTICS

•Efficiency vs. Output Current

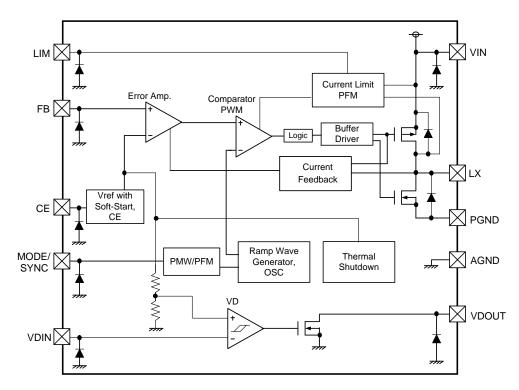

## BLOCK DIAGRAM

•XC9223B/XC9224B Series

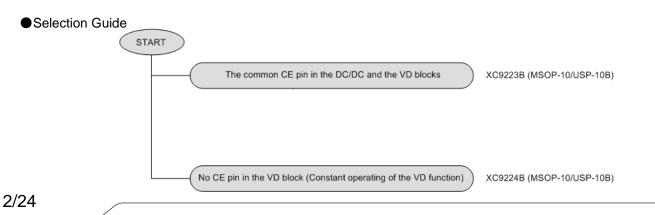

## PRODUCT CLASSIFICATION

Ordering Information

$\frac{XC9223(1)(2)(3)(4)(5)(6)-7)}{XC9224(1)(2)(3)(4)(5)(6)-7)}$  <The common CE pin in the DC/DC block and the voltage detector block.> <br/> <br/

| DESIGNATOR      | ITEM                        | SYMBOL | DESCRIPTION                                                                                 |

|-----------------|-----------------------------|--------|---------------------------------------------------------------------------------------------|

| 1               | Туре                        | В      | Transistor built-in,<br>Output voltage freely set (FB voltage),<br>Current Limit: 0.6A/1.2A |

| 23              | Reference Voltage           | 08     | Fixed reference voltage<br>②=0, ③=8                                                         |

| (4)             | DC/DC Oscillation Frequency | 1      | 1.0MHz                                                                                      |

| (4)             | DC/DC Oscillation Frequency | 2      | 2.0MHz                                                                                      |

|                 |                             | AR     | MSOP-10 (1,000pcs/Reel)                                                                     |

| 56-7            | Packages                    | AR-G   | MSOP-10 (1,000pcs/Reel)                                                                     |

|                 | (Order Unit)                | DR     | USP-10B (3,000pcs/Reel)                                                                     |

| (*1) TI ( 01) ( |                             | DR-G   | USP-10B (3,000pcs/Reel)                                                                     |

(\*1) The "-G" suffix denotes Halogen and Antimony free as well as being fully EU RoHS compliant.

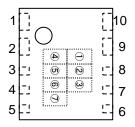

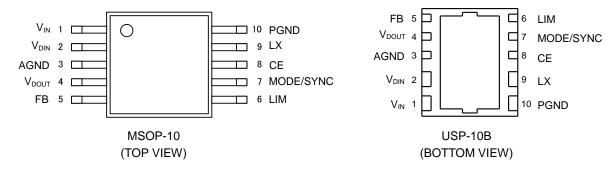

## ■ PIN CONFIGURATION

\* For mounting intensity and heat dissipation, please refer to recommended mounting pattern and recommended metal mask when soldering the pad of USP-10B. Mounting should be connected to the GND (No.3,10) pin.

| PIN NU    | JMBER     |                 | FUNCTION                           |  |  |

|-----------|-----------|-----------------|------------------------------------|--|--|

| MSOP-10 * | USP-10B * | PIN NAME        | FUNCTION                           |  |  |

| 1         | 1         | V <sub>IN</sub> | Input                              |  |  |

| 2         | 2         | Vdin            | Voltage Detector Input             |  |  |

| 3         | 3         | Agnd            | Analog Ground                      |  |  |

| 4         | 4         | Vdout           | VD Output                          |  |  |

| 5         | 5         | FB              | Output Voltage Monitor             |  |  |

| 6         | 6         | LIM             | Over Current Limit Setting         |  |  |

| 7         | 7         | MODE/SYNC       | Mode Switch / External Clock Input |  |  |

| 8         | 8         | CE              | Chip Enable                        |  |  |

| 9         | 9         | Lx              | Output of Internal Power Switch    |  |  |

| 10        | 10        | Pgnd            | Power Ground                       |  |  |

### ■ PIN ASSIGNMENT

\* For MSOP-10 and USP-10B packages, please short the GND pins (pin #3 and 10)

## ■ FUNCTION CHART

1. CE

| CE PIN | OPERATIONAL STATE |

|--------|-------------------|

| Н      | ON                |

| L      | OFF *1            |

(\*1) Except for a voltage detector block in the XC9224 series.

#### 2. MODE

| MODE PIN | FUNCTION                  |

|----------|---------------------------|

| Н        | PWM Control               |

| L        | PWM/PFM Automatic Control |

#### 3. LIM

| LIM PIN | FUNCTION                     |

|---------|------------------------------|

| Н       | Maximum Output Current: 1.0A |

| L       | Maximum Output Current: 0.4A |

## ■ABSOLUTE MAXIMUM RATINGS

| PARAME                      | TER           | SYMBOL                 | RATINGS                                           | UNITS |

|-----------------------------|---------------|------------------------|---------------------------------------------------|-------|

| V <sub>IN</sub> Pin Voltage |               | V <sub>IN</sub>        | -0.3 ~ 6.5                                        | V     |

| V <sub>DIN</sub> Pin V      | oltage        | Vdin                   | -0.3 ~ 6.5                                        | V     |

| V <sub>DOUT</sub> Pin \     | /oltage       | V <sub>DOUT</sub>      | -0.3 ~ 6.5                                        | V     |

| VDOUT Pin C                 | Current       | Idout                  | 10                                                | mA    |

| FB Pin Vo                   | oltage        | V <sub>FB</sub>        | -0.3 ~ 6.5                                        | V     |

| LIM Pin Vo                  | oltage        | VLIM                   | -0.3 ~ 6.5                                        | V     |

| MODE/SYNC Pin Voltage       |               | V <sub>MODE/SYNC</sub> | -0.3 ~ 6.5                                        | V     |

| CE Pin Vo                   | oltage        | VCE                    | -0.3 ~ 6.5                                        | V     |

| Lx Pin Vo                   | Itage         | V <sub>Lx</sub>        | -0.3 ~ V <sub>IN</sub> + 0.3                      | V     |

| Lx Pin Cu                   | irrent        | I <sub>Lx</sub>        | 2000                                              | mA    |

| Deven Dissingtion           | MSOP-10       |                        | 500 (40mm x 40mm Standard board) <sup>(*1)</sup>  |       |

| Power Dissipation           |               | Pd                     | 150                                               | mW    |

| (Ta=25°C)                   | USP-10B       |                        | 1000 (40mm x 40mm Standard board) <sup>(*1)</sup> |       |

| Operating Ambien            | t Temperature | Topr                   | -40 ~ 85                                          | °C    |

| Storage Tem                 | perature      | Tstg                   | -55 ~125                                          | °C    |

All voltages are described based on the GND (AGND and PGND) pin.

(\*1) The power dissipation figure shown is PCB mounted and is for reference only. The mounting condition is please refer to PACKAGING INFORMATION.

## ■ ELECTRICAL CHARACTERISTICS

#### XC9223/XC9224 Series

| PARAMETER                                       | SYMBOL                  | CONDITIONS                                                                                                              | MIN.                 | TYP.      | MAX.            | UNIT | CIRCU |

|-------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------|-----------|-----------------|------|-------|

| Input Voltage                                   | V <sub>IN</sub>         |                                                                                                                         | 2.5                  | -         | 6.0             | V    | -     |

| FB Voltage                                      | V <sub>FB</sub>         |                                                                                                                         | 0.784                | 0.800     | 0.816           | V    | 1     |

| Output Voltage Setting Range                    | V <sub>OUTSET</sub>     |                                                                                                                         | 0.9                  | -         | V <sub>IN</sub> | V    | 3     |

| Maximum Output Current 1 (*1)                   | I <sub>OUTMAX1</sub>    |                                                                                                                         | 0.4                  | -         | -               | А    | 3     |

| Maximum Output Current 2 <sup>(*1)</sup>        | I <sub>OUTMAX2</sub>    | ED // y 0.0 // Voltage which I y pip                                                                                    | 1.0                  | -         | -               | А    | 3     |

| U.V.L.O. Voltage                                | V <sub>UVLO</sub>       | $FB=V_{FB} \times 0.9$ , $V_{IN}$ Voltage which Lx pin voltage holding 'L' level ( <sup>*8)</sup>                       | 1.55                 | 1.80      | 2.00            | V    | 1     |

| Supply Current 1                                | I <sub>DD1</sub>        | FB=V <sub>FB</sub> x 0.9, MODE/SYNC=0V                                                                                  |                      | D1-1 (*2) |                 | μA   | 2     |

| Supply Current 2                                | I <sub>DD2</sub>        | FB=V <sub>FB</sub> x 1.1 (Oscillation stops),<br>MODE/SYNC=0V                                                           | D1-2 <sup>(*2)</sup> |           | μA              | 2    |       |

| Stand-by Current                                | I <sub>STB</sub>        | CE=0V                                                                                                                   |                      | D1-6 (*2) |                 | μA   | 2     |

| Oscillation Frequency                           | fosc                    | Connected to external components,<br>I <sub>OUT</sub> =10mA                                                             |                      | D1-3 (*2) |                 | MHz  | 3     |

| External Clock Signal<br>Synchronized Frequency | SYNCOSC                 | Connected to external components,<br>IOUT=10mA, apply an external clock<br>signal to the MODE/SYNC                      | D1-4 (*2)            |           |                 | MHz  | 4     |

| External Clock Signal Cycle                     | SYNCDTY                 |                                                                                                                         | 25                   | -         | 75              | %    | 4     |

| Maximum Duty Cycle                              | MAXDTY                  | FB=V <sub>FB</sub> x 0.9                                                                                                | 100                  | -         | -               | %    | 1     |

| Minimum Duty Cycle                              | MINDTY                  | FB=V <sub>FB</sub> x 1.1                                                                                                | -                    | -         | 0               | %    | 1     |

| PFM Switch Current                              | I <sub>PFM</sub>        | Connected to external components,<br>MODE/SYNC=0V, IOUT=10mA                                                            | -                    | 200       | 250             | mA   | 3     |

| Efficiency (*3)                                 | EFFI                    | Connected to external components, V <sub>IN</sub> =5.0V, V <sub>OUT</sub> =3.3V, I <sub>OUT</sub> =200mA                | -                    | 95        | -               | %    | 3     |

| Lx SW 'H' On Resistance (*4)                    | R <sub>LxH</sub>        | FB=V <sub>FB</sub> x 0.9, ILx=VI <sub>N</sub> -0.05V                                                                    | -                    | 0.21      | 0.3 (*7)        | Ω    | 1     |

| Lx SW 'L' On Resistance                         | R <sub>LxL</sub>        |                                                                                                                         | -                    | 0.23      | 0.3 (*7)        | Ω    | -     |

| Current Limit 1                                 | I <sub>LIM1</sub>       | LIM=0V                                                                                                                  | 0.6                  | -         | 0.9             | A    | 1     |

| Current Limit 2                                 | I <sub>LIM2</sub>       | LIM=V <sub>IN</sub>                                                                                                     | 1.2                  | -         | 2.0             | A    | 1     |

| Integral Latch Time (*5)                        | T <sub>LAT</sub>        | FB=V <sub>FB</sub> x 0.9, Short Lx by $1\Omega$ resistance                                                              |                      | D1-5 (*2) |                 | ms   | 1     |

| Short Detect Voltage                            | V <sub>SHORT</sub>      | FB Voltage which Lx becomes 'L' ("8)                                                                                    | 0.3                  | 0.4       | 0.5             | V    | 1     |

| Soft-Start Time                                 | T <sub>SS</sub>         | CE=0V→V <sub>IN</sub> , I <sub>OUT</sub> =1mA                                                                           | 0.5                  | 1.0       | 2.0             | ms   | 1     |

| hermal Shutdown Temperature                     | T <sub>TSD</sub>        |                                                                                                                         | -                    | 150       | -               | °C   | -     |

| Hysteresis Width                                | T <sub>HYS</sub>        |                                                                                                                         | -                    | 20        | -               | °C   | -     |

| CE "H" Voltage                                  | V <sub>CEH</sub>        | $FB=V_{FB} \times 0.9$ , Voltage which Lx becomes<br>'H' after CE voltage changed from 0.4V to<br>$1.2V^{(78)}$         | 1.2                  | -         | 6.0             | V    | 1     |

| CE "L" Voltage                                  | V <sub>CEL</sub>        | $FB=V_{FB} \times 0.9$ , Voltage which Lx becomes<br>'L' after CE voltage changed from 1.2V to<br>0.4V ( <sup>'8)</sup> | AGND                 | -         | 0.4             | V    | 1     |

| MODE/SYNC "H" Voltage                           | V <sub>MODE/SYNCH</sub> |                                                                                                                         | 1.2                  | -         | 6.0             | V    | 3     |

| MODE/SYNC "L" Voltage                           | V <sub>MODE/SYNCL</sub> |                                                                                                                         | AGND                 | -         | 0.4             | V    | 3     |

| LIM "H" Voltage                                 | V <sub>LIMH</sub>       |                                                                                                                         | 1.2                  | -         | 6.0             | V    | 1     |

| LIM "L" Voltage                                 | V <sub>LIML</sub>       | $I_{OUT}=I_{LIM1} \times 1.1$ , Check LIM voltage which<br>Lx oscillated after CE voltage changed<br>from 1.2V to 0.4V  | AGND                 | -         | 0.4             | V    | 1     |

| CE "H" Current                                  | I <sub>CEH</sub>        | V <sub>IN</sub> =CE=6.0V                                                                                                | -                    | -         | 0.1             | μA   | (5)   |

| CE "L" Current                                  | I <sub>CEL</sub>        | V <sub>IN</sub> =6.0V, CE=0V                                                                                            | - 0.1                | -         | -               | μA   | 5     |

| MODE/SYNC "H" Current                           |                         | V <sub>IN</sub> =6.0V                                                                                                   | -                    | -         | 0.1             | μA   | 5     |

| MODE/SYNC "L" Current                           |                         | V <sub>IN</sub> =6.0V, MODE/SYNC=0V                                                                                     | - 0.1                |           |                 | -    | 5     |

|                                                 | MODE/SYNCL              |                                                                                                                         | - 0.1                | -         | -               | μA   |       |

| LIM "H" Current                                 | I <sub>LIMH</sub>       | V <sub>IN</sub> =LIM=6.0V                                                                                               | -                    | -         | 0.1             | μA   | 5     |

| LIM "L" Current                                 | I <sub>LIML</sub>       | V <sub>IN</sub> =6.0V, LIM=0V                                                                                           | - 0.1                | -         | -               | μA   | 5     |

| FB "H" Current                                  | I <sub>FBH</sub>        | V <sub>IN</sub> =FB=6.0V                                                                                                | -                    | -         | 0.1             | μA   | 5     |

| FB "L" Current                                  | I <sub>FBL</sub>        | V <sub>IN</sub> =6.0V, FB=0V                                                                                            | - 0.1                | -         | -               | μA   | 5     |

| Lx SW "H" Leak Current                          | I <sub>LeakH</sub>      | V <sub>IN</sub> =Lx=6.0V, CE=0V                                                                                         | -                    | -         | 1.0             | μA   | 6     |

| Lx SW "L" Leak Current (*6)                     | LeakL                   | V <sub>IN</sub> =6.0V, Lx=CE=0V                                                                                         | - 3.0                | -         | -               | μA   | 6     |

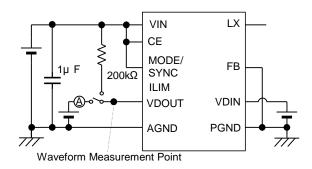

## ELECTRICAL CHARACTERISTICS (Continued)

XC9223/XC9224 Series (Continued), Voltage Detector Block

| XC9223/XC9224 Series (Contin  | C9223/XC9224 Series (Continued), Voltage Detector Block Ta=25°C |                                                                                                        |       |       |       |      |            |  |  |  |

|-------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------|-------|-------|------|------------|--|--|--|

| PARAMETER                     | SYMBOL                                                          | CONDITIONS                                                                                             | MIN.  | TYP.  | MAX.  | UNIT | CIRCUIT    |  |  |  |

| Detect Voltage                | V <sub>DF</sub>                                                 | $V_{\text{DIN}}$ Voltage which $V_{\text{DOUT}}$ becomes<br>'H' to 'L', Pull-up resistor 200k $\Omega$ | 0.676 | 0.712 | 0.744 | V    | Ī          |  |  |  |

| Release Voltage               | V <sub>DR</sub>                                                 | V <sub>DIN</sub> Voltage which V <sub>DOUT</sub> becomes<br>'L' to 'H', Pull-up resistor 200kΩ         | 0.716 | 0.752 | 0.784 | V    | Ø          |  |  |  |

| Hysteresis Width              | V <sub>HYS</sub>                                                | $V_{HYS}=(V_{DR}-V_{DF}) / V_{DF} x 100$                                                               | -     | 5     | -     | %    | -          |  |  |  |

| Output Current                | I <sub>DOUT</sub>                                               | $V_{\text{DIN}}{=}V_{\text{DF}} \ x \ 0.9, \ \text{apply} \ 0.25 V \ \text{to} \ V_{\text{DOUT}}$      | 2.5   | 4.0   | -     | mA   | $\bigcirc$ |  |  |  |

| Delay Time                    | T <sub>DLY</sub>                                                | Time until $V_{DOUT}$ becomes 'L' to 'H' after $V_{DIN}$ changed from 0V to 1.0V                       | 0.5   | 2.0   | 8.0   | ms   | Ø          |  |  |  |

| V <sub>DIN</sub> "H" Current  | I <sub>VDINH</sub>                                              | V <sub>IN</sub> =V <sub>DIN</sub> =6.0V                                                                | -     | -     | 0.1   | μA   | 5          |  |  |  |

| V <sub>DIN</sub> "L" Current  | I <sub>VDINL</sub>                                              | V <sub>IN</sub> =6.0V, V <sub>DIN</sub> =0V                                                            | - 0.1 | -     | -     | μA   | 5          |  |  |  |

| V <sub>DOUT</sub> "H" Current | I <sub>VDOUTH</sub>                                             | $V_{IN}=V_{DIN}=V_{DOUT}=6.0V$                                                                         | -     | -     | 1.0   | μA   | 5          |  |  |  |

| V <sub>DOUT</sub> "L" Current | I <sub>VDOUTL</sub>                                             | $V_{IN}=V_{DIN}=6.0V$ , $V_{DOUT}=0V$                                                                  | - 1.0 | -     | -     | μA   | 5          |  |  |  |

05°C

Test Condition: Unless otherwise stated,  $V_{IN}$ =3.6V, CE= $V_{IN}$ , MODE/SYNC= $VI_N$  NOTE:

<sup>(\*1)</sup> When the difference between the input and the output is small, some cycles may be skipped completely before current maximizes. If current is further pulled from this state, output voltage will decrease because of P-ch driver ON resistance.

(\*2) Refer to the chart below.

- (\*3) EFFI = { ( output voltage x output current ) / ( input voltage x input current) } x 100

- $^{(^*\!4)}$  On resistance (Ω)= (V\_{IN-} Lx pin measurement voltage) / 100mA

- <sup>('5)</sup> Time until it short-circuits Lx with GND through 1Ω of resistance from a state of operation and is set to Lx=Low from current limit pulse generating.

- $^{(^*\!6)}$  When temperature is high, a current of approximately 100  $\mu$  A may leak.

(\*7) Designed value.

$^{("8)}$  Whether the Lx pin is high level or low level is judged at the condition of "H">V<sub>IN</sub>-0.1V and "L"<0.05V.

| No.  | PARAMETER                                 | SYMBOL           | 1MHz |      |      | 2MHz |      |      |

|------|-------------------------------------------|------------------|------|------|------|------|------|------|

| INU. | FARAIVIETER                               | STINDUL          | MIN. | TYP. | MAX. | MIN. | TYP. | MAX. |

| D1-1 | Supply Current 1                          | I <sub>DD1</sub> | -    | 380  | 700  | -    | 440  | 800  |

| D1-2 | Supply Current 2                          | IDD2             | -    | 30   | 60   | -    | 45   | 80   |

| D1-3 | Oscillation Frequency                     | Fosc             | 0.85 | 1.00 | 1.15 | 1.7  | 2.0  | 2.3  |

| D1-4 | External Clock<br>Synchronous Oscillation | SYNCOSC          | 0.75 | -    | 1.25 | 1.5  | -    | 2.5  |

| D1-5 | 01-5 Integral Latch Time                  |                  | -    | 6.0  | 15.0 | -    | 3.0  | 15.0 |

#### Electrical Characteristics Standard Values

| No. PARAMETER |                  | SYMBOL -         | XC9223 SERIES |      |      | XC9224 SERIES |      |      |

|---------------|------------------|------------------|---------------|------|------|---------------|------|------|

| INO.          | NO. PARAMETER    |                  | MIN.          | TYP. | MAX. | MIN.          | TYP. | MAX. |

| D1-6          | Stand-by Current | I <sub>STB</sub> | -             | 0.1  | 2.0  | -             | 7.0  | 15.0 |

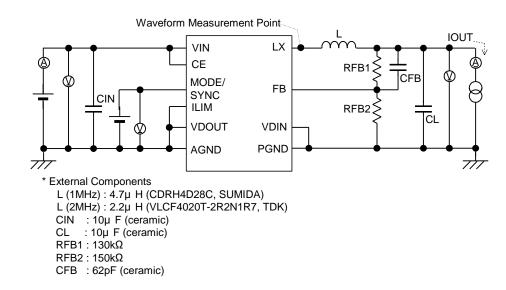

## ■ TYPICAL APPLICATION CIRCUIT

$^{(1)}$  A capacitor of 2200pF~0.1µF is recommended to place at the C<sub>DD</sub> between the AGND pin and the V<sub>IN</sub> pin. Please refer to the page showing INSTRUCTION ON PATTERN LAYOUT for more detail.

<Output Voltage Setting>

Output voltage can be set by adding external split resistors. Output voltage is determined by the following equation, based on the values of  $R_{FB1}$  and  $R_{FB2}$ . The sum of  $R_{FB1}$  and  $R_{FB2}$  should normally be 1M $\Omega$  or less.

$V_{OUT} = 0.8 x (R_{FB1} + R_{FB2}) / R_{FB2}$

The value of CFB, speed-up capacitor for phase compensation, should be  $fzfb = 1 / (2 \times \pi \times C_{FB1} \times R_{FB1})$  which is equal to 20kHz. Adjustments are required from 1kHz to 50kHz depending on the application, value of inductance (L), and value of load capacity (C<sub>L</sub>).

[Example of calculation]

When  $R_{FB1}$ =470k $\Omega$ ,  $R_{FB2}$ =150k $\Omega$ ,  $V_{OUT1} = 0.8 \times (470k + 150k) / 150k = 3.3V$

| V <sub>OUT (V)</sub> | $R_{FB1}$ (k $\Omega$ ) | $R_{FB2}\left(k\Omega ight)$ | C <sub>FB</sub> (pF) | V <sub>OUT</sub> (V) | $R_{FB1}(k\Omega)$ | $R_{FB2}\left(k\Omega ight)$ | C <sub>FB</sub> (pF) |

|----------------------|-------------------------|------------------------------|----------------------|----------------------|--------------------|------------------------------|----------------------|

| 1.0                  | 75                      | 300                          | 110                  | 2.5                  | 510                | 240                          | 15                   |

| 1.2                  | 150                     | 300                          | 51                   | 3.0                  | 330                | 120                          | 24                   |

| 1.5                  | 130                     | 150                          | 62                   | 3.3                  | 470                | 150                          | 18                   |

| 1.8                  | 300                     | 240                          | 27                   | 5.0                  | 430                | 82                           | 18                   |

\* When fzfb = 20kHz

[External components] 1MHz: L: 4.7  $\mu$  H (CDRH4D28C, SUMIDA) CL: 10  $\mu$  F (ceramic) CIN: 10  $\mu$  F (ceramic)

2MHz:

L: 2.2  $\mu$  H (CDRH4D28, SUMIDA) 2.2  $\mu$  H (VLCF4020T-2R2N1R7, TDK) C<sub>L</sub>: 10  $\mu$  F (ceramic) C<sub>IN</sub>: 10  $\mu$  F (ceramic)

\* As for C<sub>IN</sub> and C<sub>L</sub>, use output capacitors of 10  $\mu$  F or more. (Ceramic capacitor compatible)

\* High ESR (Equivalent Series Resistance) that comes by using a tantalum or an electrolytic capacitor causes high ripple voltage.

Furthermore, it can cause an unstable operation. Use the IC after you fully confirm with an actual device.

## ■OPERATIONAL EXPLANATION

Each unit of the XC9223/XC9224 series consists of a reference voltage source, a ramp wave circuit, error amplifier, PWM comparator, phase compensation circuit, output voltage adjustment resistors, P-channel MOS driver transistor, N-channel MOS synchronous rectification switching transistor, current limiter circuit, U.V.L.O. circuit and others. The series compares, using the error amplifier, the internal reference voltage to the V<sub>OUT</sub> pin with the voltage feedback via resistors R<sub>FB1</sub> and R<sub>FB2</sub>. Phase compensation is performed on the resulting error amplifier output, to input a signal to the PWM comparator to determine the turn-on time during PWM operation. The PWM comparator compares, in terms of voltage level, the signal from the error amplifier with the ramp wave from the ramp wave circuit, and delivers the resulting output to the buffer driver circuit to cause the Lx pin to output a switching duty cycle. This process is continuously performed to ensure stable output voltage. The current feedback circuit monitors the P-channel MOS driver transistor current for each switching operation, and modulates the error amplifier output signal to provide multiple feedback signals. This enables a stable feedback loop even when a low ESR capacitor, such as a ceramic capacitor, is used, ensuring stable output voltage.

#### <Reference Voltage Source>

The reference voltage source provides the reference voltage to ensure stable output voltage of the DC/DC converter.

#### <Ramp Wave Circuit>

The ramp wave circuit determines switching frequency. The frequency is fixed internally and can be selected from 1.0MHz and 2.0MHz. Clock pulses generated in this circuit are used to produce ramp waveforms needed for PWM operation, and to synchronize all the internal circuits.

#### <Error Amplifier>

The error amplifier is designed to monitor output voltage. The amplifier compares the reference voltage with the feedback voltage divided by the internal resistors ( $R_{FB1}$  and  $R_{FB2}$ ). When a voltage lower than the reference voltage is fed back, the output voltage of the error amplifier increases. The gain and frequency characteristics of the error amplifier output are fixed internally to deliver an optimized signal to the mixer.

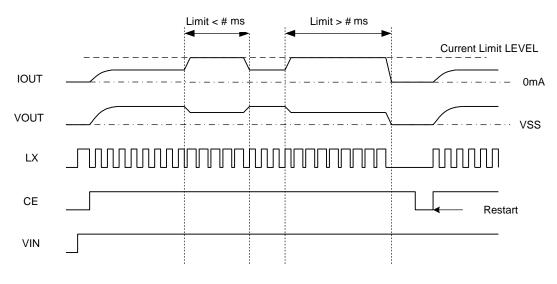

#### <Current Limit>

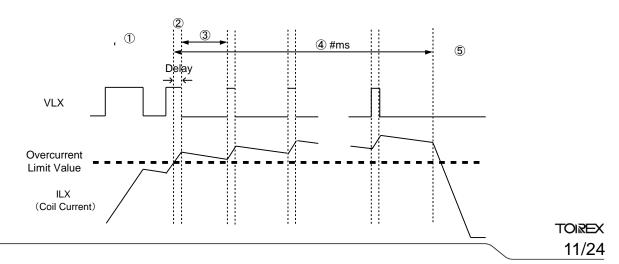

The current limiter circuit of the XC9223/XC9224 series monitors the current flowing through the P-channel MOS driver transistor connected to the Lx pin, and features a combination of the constant-current type current limit mode and the operation suspension mode. For the current limit values, please select the values either from 1.2A (MIN.) when the LIM pin is high level or 0.6A (MIN.) when the LIM pin is low level.

<sup>①</sup>When the driver current is greater than a specific level, the constant-current type current limit function operates to turn off the pulses from the Lx pin at any given time.

When the driver transistor is turned off, the limiter circuit is then released from the current limit detection state.

- ③At the next pulse, the driver transistor is turned on. However, the transistor is immediately turned off in the case of an over current state.

- <sup>④</sup> When the over current state is eliminated, the IC resumes its normal operation.

The IC waits for the over current state to end by repeating the steps ① through ③. If an over current state continues for several msec and the above three steps are repeatedly performed, the IC performs the function of latching the OFF state of the driver transistor, and goes into operation suspension mode. After being put into suspension mode, the IC can resume operation by turning itself off once and then starting it up using the CE pin, or by restoring power to the V<sub>IN</sub> pin. Integral latch time may be released from a current limit detection state because of the noise. Depending on the state of a substrate, it may result in the case where the latch time may become longer or the operation may not be latched. Please locate an input capacitor as close as possible.

## OPERATIONAL EXPLANATION (Continued)

#### <Thermal Shutdown>

For protection against heat damage of the ICs, thermal shutdown function monitors chip temperature. The thermal shutdown circuit starts operating and the driver transistor will be turned off when the chip's temperature reaches 150°C. When the temperature drops to 130°C or less after shutting of the current flow, the IC performs the soft start function to initiate output startup operation.

#### <Short-Circuit Protection>

The short-circuit protection circuit monitors FB voltage. In case where output is accidentally shorted to the Ground and when the FB voltage decreases less than half of the FB voltage, the short-circuit protection operates to turn off and to latch the driver transistor. In latch mode, the operation can be resumed by either turning the IC off and on via the CE pin, or by restoring power supply to the  $V_{IN}$  pin.

#### <Voltage Detector>

The detector block of the XC9223/9224 series detects a signal inputted from the  $V_{DIN}$  pin by the  $V_{DOUT}$  pin (N-ch open-drain).

#### <U.V.L.O. Circuit>

When the  $V_{IN}$  pin voltage becomes 1.8V (TYP.) or lower, the driver transistor is forced OFF to prevent false pulse output caused by unstable operation of the internal circuitry. When the  $V_{IN}$  pin voltage becomes 2.0V (TYP.) or higher, switching operation takes place. By releasing the U.V.L.O. function, the IC performs the soft-start function to initiate output startup operation. The U.V.L.O. function operates even when the  $V_{IN}$  pin voltage falls below the U.V.L.O. operating voltage for tens of ns.

#### <MODE/SYNC>

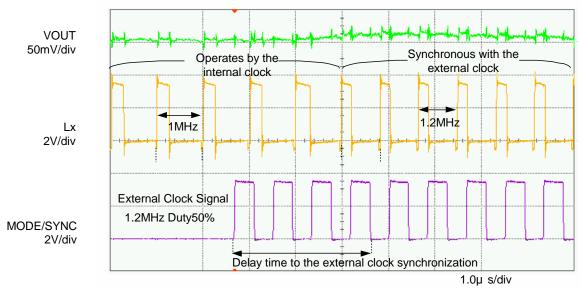

A MODE/SYNC pin has two functions, a MODE switch and an input of external clock signal. The MODE/SYNC pin operates as the PWM mode when applying high level of direct current and the PFM/PWM automatic switching mode by applying low level of direct current, which is the same function as the normal MODE pin. By applying the external clock signal ( $\pm 25\%$  of the internal clock signal, ON duty 25% to 75%), the MODE/SYNC pin switches to the internal clock signal. Also the circuit will synchronize with the falling edge of external clock signal. While synchronizing with the external clock signal, the MODE/SYNC pin becomes the PWM mode automatically. If the MODE/SYNC pin holds high or low level of the external clock signal for several  $\mu$  s, the MODE/SYNC pin stops synchronizing with the external clock and switches to the internal clock operation. (Refer to the chart below.)

External Clock Synchronization Function

\* When an input of MODE/SYNC is changed from "L" voltage into a clock signal of 1.2MHz and 50% duty.

## OPERATIONAL EXPLANATION (Continued)

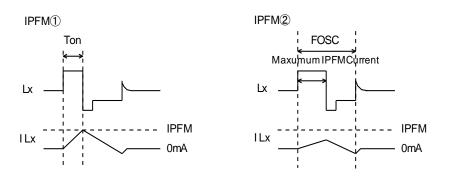

#### <PFM Switch Current>

In PFM control operation, until coil current reaches to a specified level (I<sub>PFM</sub>), the IC keeps the P-ch MOSFET on. In this case, time that the P-ch MOSFET is kept on (TON) can be given by the following formula.

$T_{ON} = L \times I_{PFM} / (V_{IN} - V_{OUT}) \rightarrow I_{PFM}$

<Maximum IPFM Limit>

In PFM control operation, the maximum duty cycle (MAXPFM) is set to 50% (TYP.). Therefore, under the condition that the duty increases (e.g. the condition that the step-down ratio is small), it's possible for P-ch MOSFET to be turned off even when coil current doesn't reach to  $I_{PFM}$ .  $\rightarrow I_{PFM}$

## ■NOTES ON USE

- 1. The XC9223/XC9224 series is designed for use with ceramic output capacitors. If, however, the potential difference between dropout voltage, a ceramic capacitor may fail to absorb the resulting high switching energy and oscillation could occur on the output. In this case, use a larger capacitor etc. to compensate for insufficient capacitance.

- 2. Spike noise and ripple voltage arise in a switching regulator as with a DC/DC converter. These are greatly influenced by external component selection, such as the coil inductance, capacitance values, and board layout of external components. Once the design has been completed, verification with actual components should be done.

- In PWM control, very narrow pulses will be outputted, and there is the possibility that some cycles may be skipped completely. This may happens while synchronizing with an external clock.

- 4. When the difference between V<sub>IN</sub> and V<sub>OUT</sub> is small, and the load current is heavy, very wide pulses will be outputted and there is the possibility that some cycles may be skipped completely.

- 5. With the IC, the peak current of the coil is controlled by the current limit circuit. Since the peak current increases when dropout voltage or load current is high, current limit starts operating, and this can lead to instability. When peak current becomes high, please adjust the coil inductance value and fully check the circuit operation. In addition, please calculate the peak current according to the following formula:

$lpk = (V_{IN} - V_{OUT}) \times OnDuty / (2 \times L \times f_{osc}) + I_{DOUT}$ L: Coil Inductance Value fosc: Oscillation Frequency

- 6. When the peak current, which exceeds limit current, flows within the specified time, the built-in P-ch driver transistor is turned off (an integral latch circuit). During the time until it detects limit current and before the built-in transistor can be turned off, the current for limit current flows; therefore, care must be taken when selecting the rating for the coil.

- 7. The voltage drops because of ON resistance of a driver transistor or in-series resistance of a coil. For this, the current limit may not be attained to the limit current value, when input voltage is low.

- 8. Malfunction may occur in the U.V.L.O. circuit because of the noise when pulling current at the minimum operation voltage.

- 9. This IC and the external components should be used within the stated absolute maximum ratings in order to prevent damage to the device.

- 10. Depending on the state of the PC Board, latch time may become longer and latch operation may not work. The board should be laid out so that capacitors are placed as close to the chip as possible.

- 11. In heavy load, the noise of DC/DC may influence and the delay time of the voltage detector may be prolonged.

- 12. Output voltage may become unstable when synchronizing high internal frequency with the external clock. In such a case, please use a larger output capacitor etc. to compensate for insufficient capacitance.

- When a voltage lower than minimum operating voltage is applied, the output voltage may fall before reaching the over current limit.

- 14. When the IC is used in high temperature, output voltage may increase up to input voltage level at light load (less than 100 μ A) because of the leak current of the driver transistor.

- 15. The current limit is set to LIM=H: 2000mA (MAX.). However, the current of 2000mA or more may flow. In case that the current limit functions while the V<sub>OUT</sub> pin is shorted to the GND pin, when P-ch MOSFET is ON, the potential difference for input voltage will occur at both ends of a coil. For this, the time rate of coil current becomes large. By contrast, when N-ch MOSFET is ON, there is almost no potential difference at both ends of the coil since the V<sub>OUT</sub> pin is shorted to the GND pin. Consequently, the time rate of coil current becomes quite small. According to the repetition of this operation, and the delay time of the circuit, coil current will be converged on a certain current value, exceeding the amount of current, which is supposed to be limited originally. The short protection does not operate during the soft-start time. The short protection starts to operate and the circuit will be disabled after the soft-start time. Current larger than over current limit may flow because of a delay time of the IC when step-down ratio is large. A coil should be used within the stated absolute maximum rating in order to prevent damage to the device.

①Current flows into P-ch MOSFET to reach the current limit (ILIM).

- ②The current of ILIM (2000mA, MAX.) or more flows since the delay time of the circuit occurs during from the detection of the current limit to OFF of P-ch MOSFET.

- ③Because of no potential difference at both ends of the coil, the time rate of coil current becomes quite small.

- (4) Lx oscillates very narrow pulses by the current limit for several msec.

(5) The short protection operates, stopping its operation.

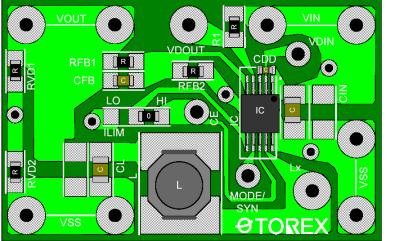

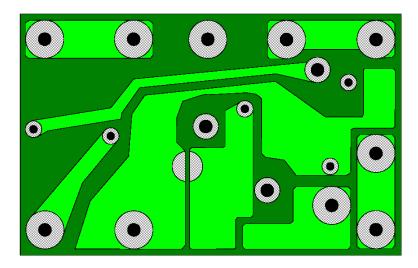

## **INSTRUCTION ON PATTERN LAYOUT**

- 1. In order to stabilize VIN's voltage level, we recommend that a by-pass capacitor (CIN) be connected as close as possible to the VIN & Vss pins.

- 2. Please mount each external component, especially CIN, as close to the IC as possible.

- 3. Wire external components as close to the IC as possible and use thick, short connecting traces to reduce the circuit impedance.

- 4. Make sure that the PCB GND traces are as thick as possible, as variations in ground potential caused by high ground currents at the time of switching may result in instability of the IC.

- 5. Unstable operation may occur at the heavy load because of a spike noise. 2200pF~0.1 µ F of a capacitor, CDD, is recommended to use between the AGND pin and the VIN pin for reducing noise.

- TOP VIEW

BOTTOM VIEW

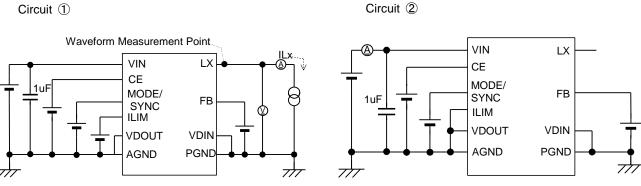

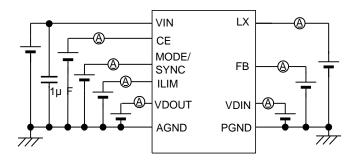

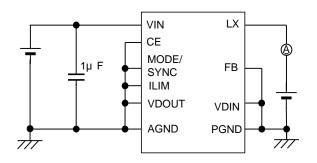

## ■TEST CIRCUITS

Circuit ①

Circuit ③

Circuit ④

TOIREX 13/24

## ■TEST CIRCUITS (Continued)

Circuit (5)

Circuit (6)

Circuit ⑦

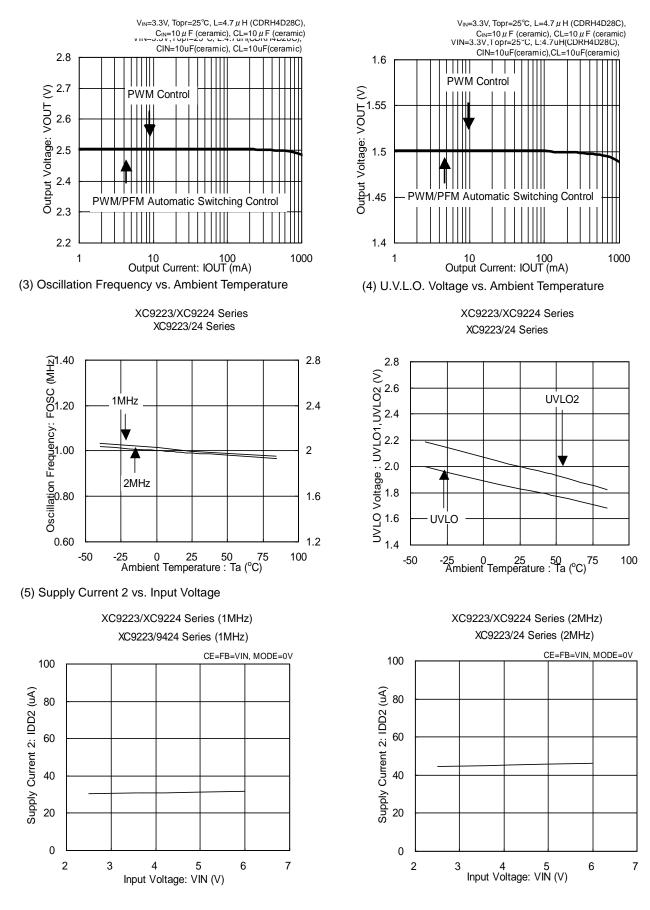

## ■ TYPICAL PERFORMANCE CHARACTERISTICS

(1) Efficiency vs. Output Current

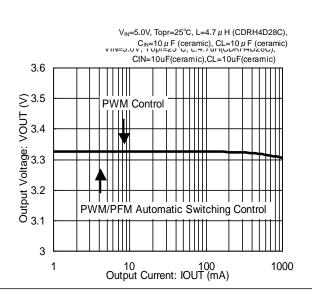

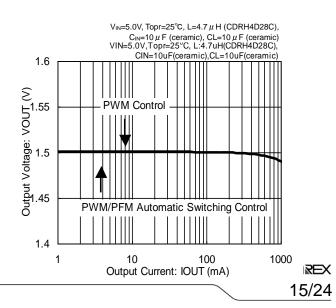

(2) Output Voltage vs. Output Current

(2) Output Voltage vs. Output Current (Continued)

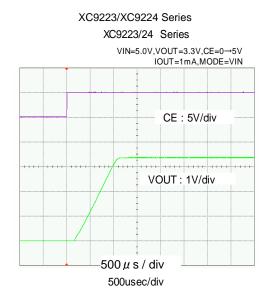

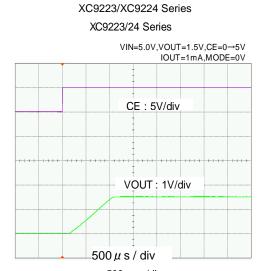

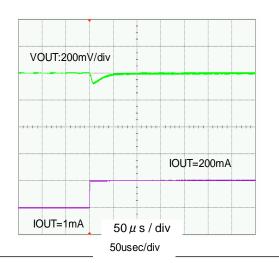

#### (6) Soft Start Time

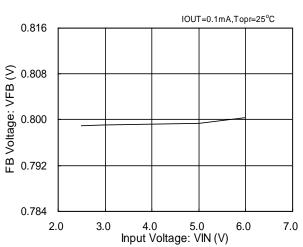

(7) FB Voltage vs. Supply Voltage

XC9223/XC9224 Series XC9223/9424 Series

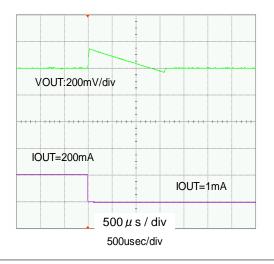

500usec/div

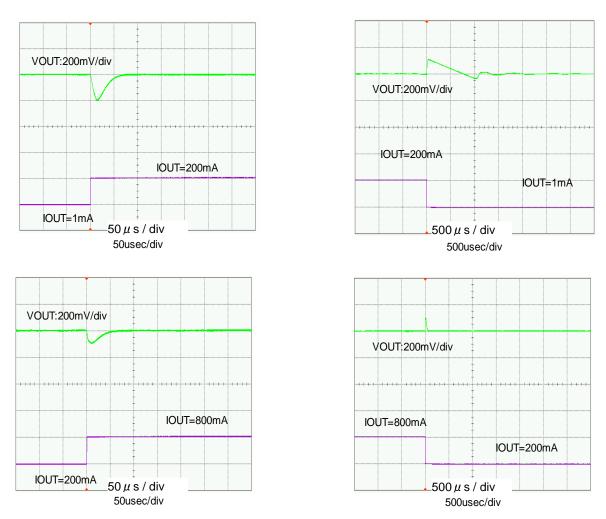

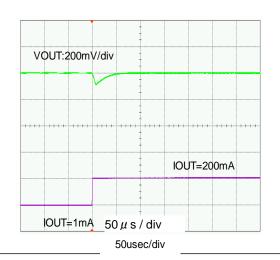

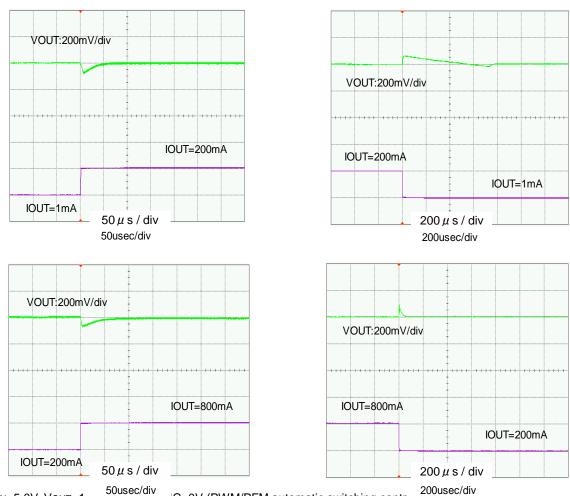

(8) Load Transient Response

XC9223B081Ax <1MHz>

VIN=5.0V, VOUT=3.3V, MODE/SYNC=VIN (PWM control) L=4.7  $\mu$  H (CDRH4D28C), CIN=10  $\mu$  F (ceramic), CL=10  $\mu$  F (ceramic), Topr=25°C

VIN=5.0V, VOUT=3.3V, MODE/SYNC=0V (PWM/PFM automatic switching control) L=4.7  $\mu$  H (CDRH4D28C), CIN=10  $\mu$  F (ceramic), CL=10  $\mu$  F (ceramic), Topr=25°C

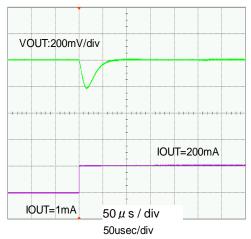

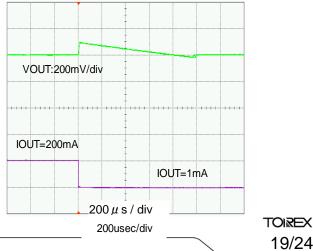

(8) Load Transient Response (Continued)

XC9223B081Ax <1MHz> (Continued)

VIN=5.0V, VOUT=1.5V, MODE/SYNC=VIN (PWM control) L=4.7 µ H (CDRH4D28C), CIN=10 µ F (ceramic), CL=10 µ F (ceramic), Topr=25°C

VIN=5.0V, VOUT=1.5 C=0V (PWM/PFM automatic switching contr L=4.7 µ H (CDRH4D28C), CIN=10 µ F (ceramic), CL=10 µ F (ceramic), Topr=25°C

19/24

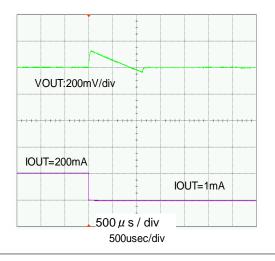

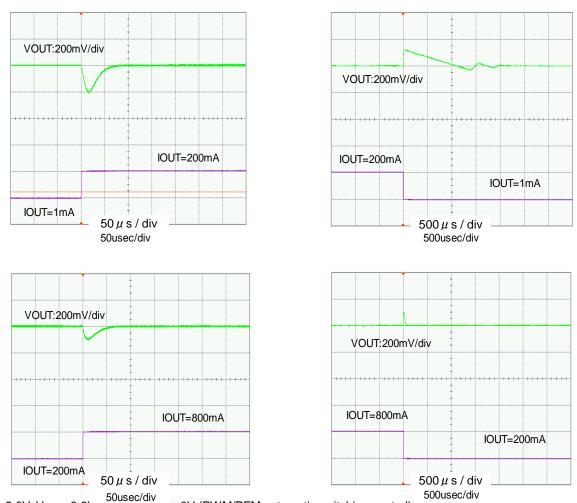

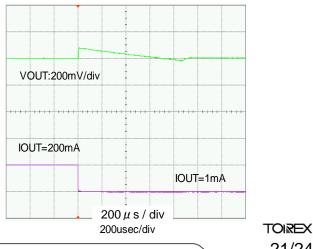

(8) Load Transient Response (Continued)

XC9223B082Ax <2MHz>

VIN=5.0V, VOUT=3.3V, MODE/SYNC=VIN (PWM control) L=2.2  $\mu$  H (CDRH4D28), CIN=10  $\mu$  F (ceramic), CL=10  $\mu$  F (ceramic), Topr=25°C

VIN=5.0V, VOUT=3.3' =0V (PWM/PFM automatic switching control) L=2.2  $\mu$  H (CDRH4D28C), CIN=10  $\mu$  F (ceramic), CL=10  $\mu$  F (ceramic), Topr=25°C

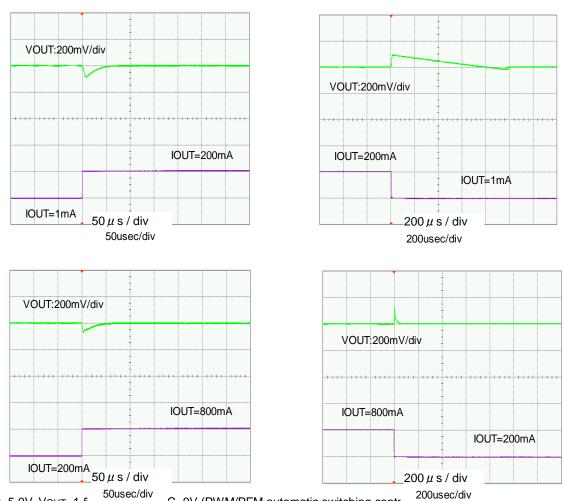

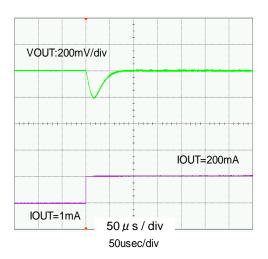

(8) Load Transient Response (Continued)

XC9223B082Ax <2MHz> (Continued)

VIN=5.0V, VOUT=1.5V, MODE/SYNC=VIN (PWM control) L=2.2 µ H (CDRH4D28), CIN=10 µ F (ceramic), CL=10 µ F (ceramic), Topr=25°C

C=0V (PWM/PFM automatic switching contr VIN=5.0V, VOUT=1. L=2.2  $\mu$  H (CDRH4D28C), CIN=10  $\mu$  F (ceramic), CL=10  $\mu$  F (ceramic), Topr=25°C

21/24

## ■ PACKAGING INFORMATION

For the latest package information go to, www.torexsemi.com/technical-support/packages

| PACKAGE | OUTLINE / LAND PATTERN | THERMAL CHARACTERISTICS   |

|---------|------------------------|---------------------------|

| MSOP-10 | MSOP-10 PKG            | MSOP-10 Power Dissipation |

| USP-10B | USP-10B PKG            | USP-10B Power Dissipation |

## ■MARKING RULE

#### ●MSOP-10

① represents products series

| MARK | PRODUCT SERIES |

|------|----------------|

| 0    | XC9223xxxxAx   |

| A    | XC9224xxxxAx   |

2 represents type of DC/DC converters

| MARK | PRODUCT SERIES    |

|------|-------------------|

| В    | XC9223/9224BxxxAx |

3 (4) represents reference voltage

| MARK |   | PRODUCT SERIES    |

|------|---|-------------------|

| 3    | 4 | FRODUCT SERIES    |

| 0    | 8 | XC9223/9224x08xAx |

5 represents oscillation frequency

| MARK | OSCILLATION FREQUENCY | PRODUCT SERIES    |

|------|-----------------------|-------------------|

| 1    | 1.0MHz                | XC9223/9224xxx1Ax |

| 2    | 2.0MHz                | XC9223/9224xxx2Ax |

67 represents production lot number

01 to 09, 0A to 0Z, 10 to 19, 1A~ in order. (G, I, J, O, Q, W excluded)Note: No character inversion used.

x. e)

| MARKING |                          | PRODUCTION |

|---------|--------------------------|------------|

| 6       | $\overline{\mathcal{O}}$ | LOT NUMBER |

| 0       | 3                        | 03         |

| 1       | А                        | 1A         |

USP-10B (BOTTOM VIEW)