#### Bittiviare a molex company

# UltraScale+ PCIe board with integrated HBM2 memory

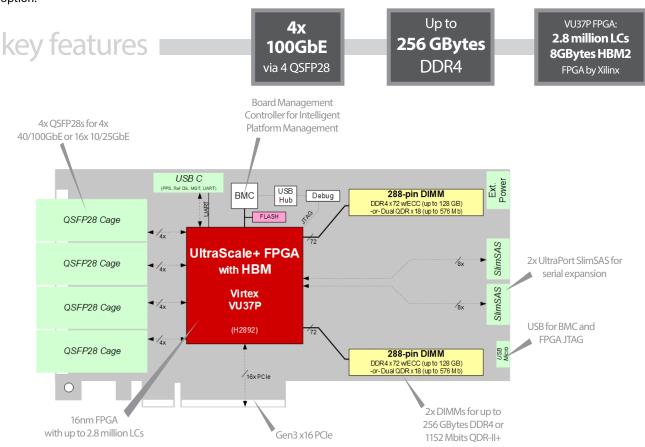

BittWare's XUP-VVH is an UltraScale+ VU37P FPGA-based PCIe card ideal for high-density datacenter applications that demand high memory bandwidth. The UltraScale+ FPGA helps these demanding applications avoid I/O bottlenecks with integrated High Bandwidth Memory (HBM2) tiles on the FPGA that support up to 8 GBytes of memory at 460 GBytes/sec.

Along with the integrated memory, the UltraScale+ VU37P offers up to 2.8 million logic elements, which gives designers incredible performance potential — yet with a power density that makes thermal management difficult. The XUP-VVH meets this challenge with BittWare's Viper platform, supporting large FPGA loads, up to 256 GBytes DDR4, and 4x 100 Gbps Ethernet.

BittWare's Viper platform uses advanced computer flow simulation to drive the physical board design in a thermals first approach, including the use of heat pipes, airflow channels, and arranging components to maximize the limited available airflow in a server. Viper boards are passive by default, with active cooling as an option.

# **E** XILINX.

Xilinx VU37P FPGA: lidless package is used by BittWare's Viper thermal management for enhanced cooling performance

## **Additional Services**

Take advantage of BittWare's range of design, integration, and support options

Customization Additional specification options or accessory boards to meet your exact needs.

### Server Integration Available pre-integrated in our <u>TeraBox servers</u> in a range of configurations.

| Application<br>Benchmark<br>Report | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EPGA Acceleration of Lattice Bo    | Participan and an end of the second second second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                    | Han, Yuo Milan Ago Kulo Si Marchi Yu. Milayi an<br>apalasan hani ati anan ananan haribiyi an<br>anathri ang nan nanani harutayi. Yarannin<br>mantifa berunga sanahasi Kulo amala<br>mathri<br>anathri.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                    | (abo)<br>(intercent out-part of profile to divert diverting<br>encoders and part of profile to diverting any<br>intercent and part of a second or diverting any<br>intercent of the second or diverting and profile diverting<br>of the data state data diverting<br>of the data state data diverting<br>of the data state of the second of the second<br>of the data state of the second of the<br>second of the data data and the<br>second of the second of the second of the<br>second of the second of the second of the<br>second of the second of the<br>second of the second of th |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                    | NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Application Optimization Ask about our services to help you port, optimize, and benchmark

your application.

Service and Support BittWare Developer Site

BittWare Developer Site provides online documentation and issue tracking.

#### **Board Specifications**

| FPGA              | <ul> <li>Virtex UltraScale+</li> <li>VU37P</li> <li>8 GBytes of HBM2 high-bandwidth DRAM</li> <li>Core speed grade - 2</li> <li>Contact BittWare for other FPGA options</li> </ul>                              |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-board Flash    | Flash memory for booting FPGA                                                                                                                                                                                   |

| External memory   | <ul> <li>2 DIMM sites, each supporting:</li> <li>Up to 128 GBytes DDR4 x72 with ECC</li> <li>Up to 576 Mbits dual QDR-II+ x18 (2 independent 288 Mbit banks)</li> </ul>                                         |

| Host interface    | x16 Gen3 interface direct to FPGA                                                                                                                                                                               |

| USB port          | Micro USB: access to BMC and FPGA JTAG                                                                                                                                                                          |

| Utility           | <ul> <li>Connects to a breakout board for UART, 1 PPS<br/>input, and 10MHz clock input</li> </ul>                                                                                                               |

| UltraPort SlimSAS | <ul> <li>2 UltraPort SlimSAS on rear edge connected to<br/>FPGA via 16x GTY transceivers</li> <li>Can support an additional x16 or x8 PCle interface<br/>(requires soft IP core and additional slot)</li> </ul> |

| QSFP cages        | <ul> <li>4 QSFP28 (zQSFP) cages on front panel connected directly to FPGA via 16 transceivers</li> <li>Each supports 100GbE, 40GbE, 4x 25GbE, or 4x 10GbE and can be combined for 400GbE</li> </ul>             |

| Board<br>Management<br>Controller | <ul> <li>Voltage, current, temperature monitoring</li> <li>Power sequencing and reset</li> <li>Field upgrades</li> <li>FPGA configuration and control</li> <li>Clock configuration</li> <li>I<sup>2</sup>C bus access</li> <li>USB 2.0</li> <li>Voltage overrides</li> </ul> |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cooling                           | Standard: double-width passive heatsink                                                                                                                                                                                                                                      |

| Electrical                        | <ul> <li>On-board power derived from 12V PCIe slot &amp; an AUX connector (8-pin)</li> <li>Power dissipation is application dependent</li> </ul>                                                                                                                             |

| Environmental                     | <ul> <li>Operating temperature 5°C to 35°C</li> </ul>                                                                                                                                                                                                                        |

| Size                              | <ul> <li>¾-length, standard-height PCIe dual-slot board</li> <li>10 x 4.37 inches (254 x 111.15 mm)</li> </ul>                                                                                                                                                               |

#### **Development Tools**

| System<br>development | BittWorks II Toolkit - host, command, and debug tools for BittWare hardware                                         |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| FPGA development      | <ul> <li>FPGA Examples - example Vivado projects</li> <li>Xilinx Tools - Vivado<sup>®</sup> Design Suite</li> </ul> |

## To learn more, visit www.BittWare.com

Rev 2020.02.11 | February 2020

© BittWare 2020

UltraScale, Virtex, and Vivado are registered trademarks of Xilinx Corp. All other products are the trademarks or registered trademarks of their respective holders.