# Z8FS021 ZMOTION™ Intrusion Detection

**Product Specification**

PS028804-1011

ii

<u>\</u>

Warning: DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2011 Zilog, Inc All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

ZMOTION and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. (An IXYS Company). All other product or service names are the property of their respective owners.

PS028804-1011 Life Support Policy

iii

# **Revision History**

Each instance in the following revision history table reflects a change to this document from its previous version. For more details, refer to the corresponding pages or appropriate links provided in the table.

| Date        | Revision<br>Level | Description                                                                                       | Page<br>Number    |

|-------------|-------------------|---------------------------------------------------------------------------------------------------|-------------------|

| Oct<br>2011 | 04                | Corrected error in ePIR_SC1 description, Table 9; modified Packaging section.                     | <u>29, 46</u>     |

| Jul<br>2011 | 03                | Corrections to ePIR_SC1, ePIR_Process_Rate and ePIR_Signal_DC registers                           | <u>29, 40, 44</u> |

| Apr<br>2011 | 02                | Corrections to PIR Noise Sensitivity Level Register and PIR Transient Sensitivity Level Register. | <u>42</u>         |

| Feb<br>2011 | 01                | Original issue.                                                                                   | All               |

PS028804-1011 Revision History

# **Table of Contents**

| Revision Historyiii                                                                           |

|-----------------------------------------------------------------------------------------------|

| List of Figures                                                                               |

| List of Tables                                                                                |

| Overview1ZMOTION Intrusion Detection Features1Z8FS021 MCU Features2Z8FS021 MCU Block Diagram3 |

| MCU Part Selection Guide                                                                      |

| Pin Configuration                                                                             |

| Signal Descriptions                                                                           |

| Flash Memory Map                                                                              |

| RAM Memory Map                                                                                |

| Peripherals                                                                                   |

| Hardware Connection Requirements                                                              |

| White Light Detection                                                                         |

| PIR Engine and API                                                                            |

| Standard API Register Set                                                                     |

| Advanced API Register Set                                                                     |

| Packaging                                                                                     |

| Ordering Information                                                                          |

| Related Documents                                                                             |

| Appendix A. Example Application Schematics                                                    |

PS028804-1011 **Table of Contents**

# ZMOTION<sup>™</sup> Intrusion Detection Product Specification

| Z8FS021xHJ20EG (28-Pin)                                      | . 55 |

|--------------------------------------------------------------|------|

| Appendix B. PIR Engine Initialization and Control            | 58   |

| Appendix C. Software Support Files and Project Configuration |      |

| Appendix D. Lens Specifications                              | 63   |

| Customer Support                                             | 64   |

PS028804-1011 Table of Contents

# **List of Figures**

| Figure 1.  | Z8FS021 MCU Block Diagram                                                                                    | 3  |

|------------|--------------------------------------------------------------------------------------------------------------|----|

| Figure 2.  | 8-Pin SOIC Package Diagram – Z8FS021xSB20EG                                                                  | 5  |

| Figure 3.  | 20-Pin SSOP Package Diagram – Z8FS021xHH20EG                                                                 | 6  |

| Figure 4.  | 28-Pin SSOP Package Pin-Out, Z8FS021xHJ20EG                                                                  | 7  |

| Figure 5.  | Z8FS021 MCU Program Memory Map                                                                               | 10 |

| Figure 6.  | Z8FS021 MCU RAM Memory Map                                                                                   | 11 |

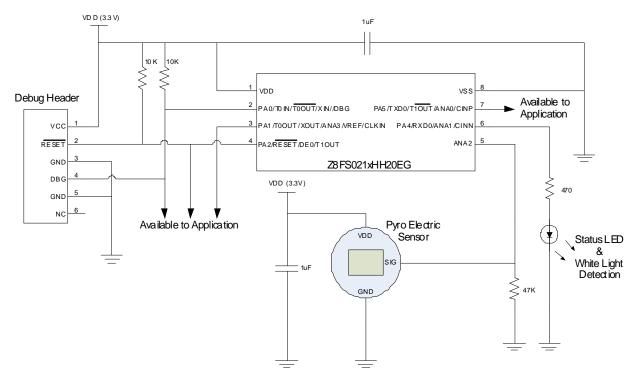

| Figure 7.  | Example Circuit with the Z8FS021xSB20EG (8-Pin) ZMOTION Intrusion Detection MCU                              | 52 |

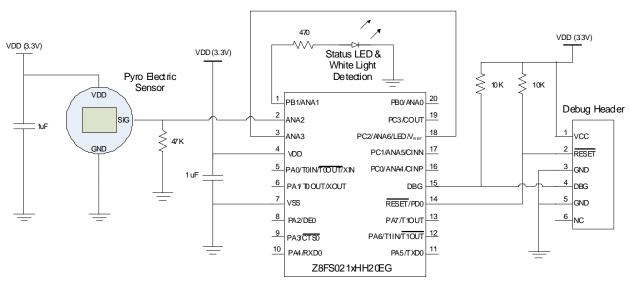

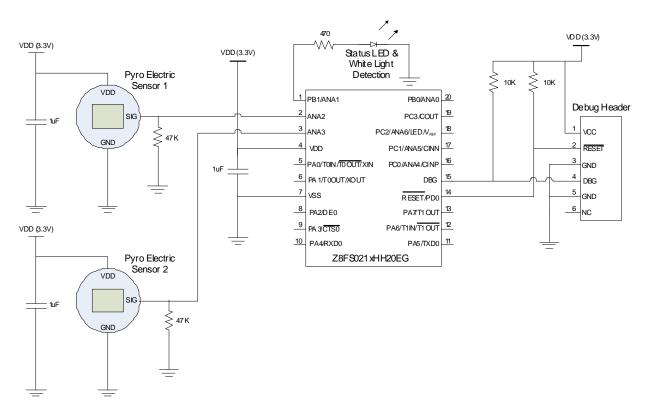

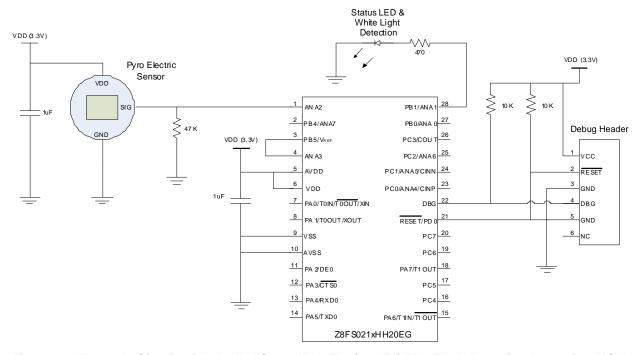

| Figure 8.  | Example Circuit with the Z8FS021xHH20EG (20-Pin) ZMOTION Intrusion Detection MCU, Single Pyro Mode           | 53 |

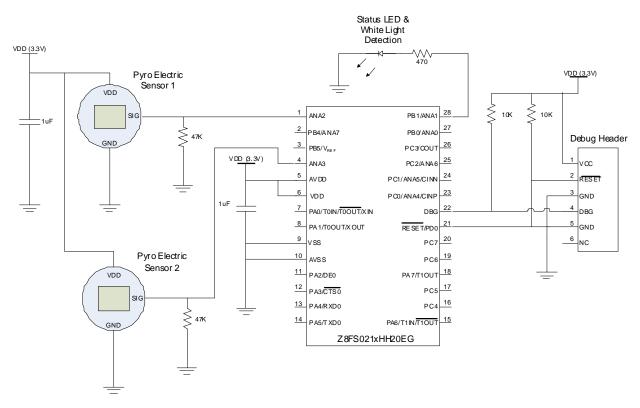

| Figure 9.  | Example Circuit with the Z8FS021xHH20EG (20-Pin) ZMOTION Intrusion Detection MCU, Dual Pyro Mode             | 54 |

| Figure 10. | Example Circuit with the Z8FS021xHJ20EG (28-Pin) ZMOTION Intrusion Detection MCU, Single Pyro Mode           | 56 |

| Figure 11. | Required Circuit Connections for the Z8FS021xHJ20EG (28-Pin) ZMOTION Intrusion Detection MCU, Dual Pyro Mode | 57 |

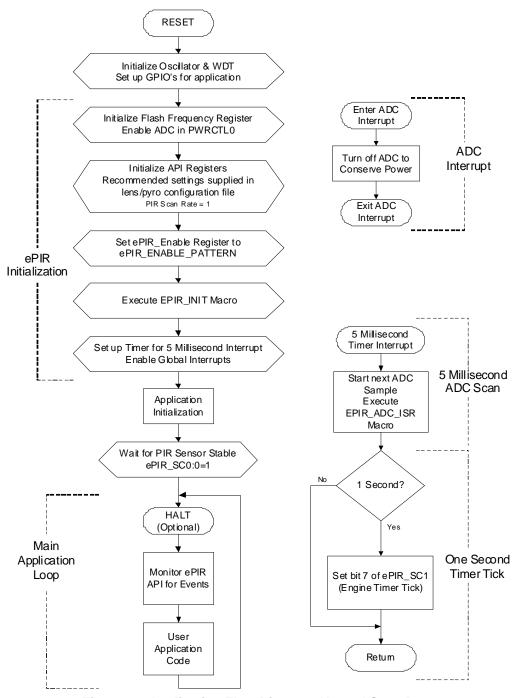

| Figure 12. | Application Flow Diagram, Normal Scan Rate                                                                   | 59 |

| Figure 13. | Application Flow Diagram, Normal Scan Rate                                                                   | 60 |

List of Figures PS028804-1011

# ZMOTION<sup>™</sup> Intrusion Detection Product Specification

# **List of Tables**

| Table 1.  | Z8FS021 ZMOTION Intrusion Detection MCU Part Selection Guide | 4  |

|-----------|--------------------------------------------------------------|----|

| Table 2.  | Z8FS021 MCU Signal Descriptions                              | 8  |

| Table 3.  | Peripheral Availability                                      | 12 |

| Table 4.  | PIR Engine Standard API Registers                            | 23 |

| Table 5.  | PIR Engine Enable Register                                   | 24 |

| Table 6.  | PIR Software Enable Patterns                                 | 24 |

| Table 7.  | PIR Sensitivity Register                                     | 25 |

| Table 8.  | PIR Status/Control Register 0                                | 26 |

| Table 9.  | PIR Status/Control Register 1                                | 29 |

| Table 10. | PIR Status/Control Register 2                                | 31 |

| Table 11. | PIR Status/Control Register 3, 20-Pin SSOP                   | 32 |

| Table 12. | PIR Status/Control Register 3, 28-Pin SSOP                   | 32 |

| Table 13. | PIR Status/Control Register 3, 8-Pin SOIC                    | 33 |

| Table 14. | PIR ADC Result Value                                         | 34 |

| Table 15. | PIR Version                                                  | 34 |

| Table 16. | PIR Engine API Advanced Registers                            | 35 |

| Table 17. | PIR Advanced Status/Control Register 0                       | 36 |

| Table 18. | PIR Advanced Status/Control Register 1                       | 38 |

| Table 19. | PIR Advanced Status/Control Register 2                       | 39 |

| Table 20. | PIR Sample Size Register                                     | 40 |

| Table 21. | PIR Process Rate                                             | 40 |

| Table 22. | PIR Debounce Batch Size Register                             | 41 |

| Table 23. | PIR Debounce Timeout Register                                | 41 |

| Table 24. | PIR Noise Sensitivity Level Register                         | 42 |

| Table 25. | PIR Transient Sensitivity Level Register                     | 42 |

| Table 26. | Maximum Noise Sensitivity Values                             | 43 |

| Table 27. | PIR Signal                                                   | 43 |

| Table 28. | PIR Extended Detection Sensitivity Level                     | 44 |

| Table 29. | PIR DC Signal Level                                          | 44 |

PS028804-1011 List of Tables

## ZMOTION<sup>™</sup> Intrusion Detection Product Specification

|    |   |   | ٠ |

|----|---|---|---|

| \/ | ı | ı | ı |

| v  | ı | ı | ı |

| Table 30. | PIR Extended Detection Debounce Timeout                                 |

|-----------|-------------------------------------------------------------------------|

| Table 31. | Z8FS021 ZMOTION Intrusion Detection Series Part Selection Guide 47      |

| Table 32. | PIR Engine Revision Identifiers                                         |

| Table 33. | ZMOTION Intrusion Detection Device Number Schema                        |

| Table 34. | Device Number Description, Positions 1–4: Product Family Selector 48    |

| Table 35. | Device Number Description, Positions 5–8: MCU and Package Selector . 48 |

| Table 36. | Device Number Description, Positions 9–12: Lens and PIR Sensor Selector |

| Table 37. | Device Number Description, Position 13: Environmental Flow Selector 49  |

| Table 38. | ZMOTION Intrusion Detection Device Number Example                       |

| Table 39. | Lens Selection Guide                                                    |

PS028804-1011 List of Tables

#### 1

#### **Overview**

The ZMOTION Intrusion Detection device is an integrated and flexible solution for Passive Infrared (PIR)-based motion detection applications. The ZMOTION family includes a series of high-performance microcontrollers with integrated motion-detection algorithms and a selection of lenses and PIR sensors to fit a wide range of intrusion detection and security applications. Zilog's ZMOTION Intrusion Detection Solution provides a dramatic improvement in both sensitivity and stability over traditional security-related motion detection designs with integrated functions such as White Light detection and Pet Immunity. As a result, it is the ideal solution for security applications in which intrusion detection capability is vital.

The ZMOTION Intrusion Detection Solution, based on Zilog's Z8FS021 MCU, combines the programmability and rich peripheral set of our Z8 Encore! XP family of In-Circuit Programmable Flash MCUs with built-in motion detection software algorithms to provide the functions necessary for PIR motion detection applications. These algorithms comprise the PIR Engine and run in the background while control and status of the Engine is accessed through a software Application Programmer Interface (API). These APIs allow designers to create their own application-specific software while taking advantage of Zilog's ZMOTION Motion Detection Technology. Additional API settings are provided to match PIR Engine operation to each lens and pyroelectric sensor combination.

The Flash in-circuit programming capability of the Z8FS021 MCU allows for faster development time, more flexible manufacturing and firmware changes in the field.

As with all of Zilog's ZMOTION products, the ZMOTION Intrusion Detection MCU provides optimized configuration parameters for each lens/sensor combination to ensure the best possible performance while significantly reducing development risk and minimizing time to market.

#### **ZMOTION Intrusion Detection Features**

- Software-based Motion Detection (PIR) Engine controlled and monitored via software API registers

- Select from an assortment of lenses and pyroelectric sensors to best fit your application

- API settings provided for each lens and pyroelectric sensor combination

- Sensitivity control, range control and directionality detection

- Accurate frequency discrimination and programmable pet immunity

- No temperature compensation required

- White light detection using status LED reduces system cost (eliminates CDS photocell)

- White Light Anti-Jam feature and programmable sensitivity to support a wide range of LED and light pipe configurations

PS028804-1011 Overview

Programmable transient and noise detection

#### **Z8FS021 MCU Features**

- High-performance eZ8® CPU core

- 2KB in-circuit programmable Flash available for application code

- Single-pin debug with unlimited breakpoints

- Flexible clocking scheme

- Internal precision oscillator running at 5.53MHz

- External oscillator operating up to 20MHz

- Sigma Delta ADC

- Up to 6 single-ended channels or 3 differential channels available

- On-chip analog comparator with independent programmable reference voltage

- Full-duplex UART with dedicated BRG

- Two 16-bit timers with input capture, output compare and PWM capability (11 modes

- Watchdog timer (WDT) with dedicated internal oscillator

- Up to 20 vectored interrupts

- 6 to 25 I/O pins depending upon package

- 2.7 V to 3.6 V operating voltage with extended operating temperature range –40°C to +105°C

- Low power modes

PS028804-1011 Overview

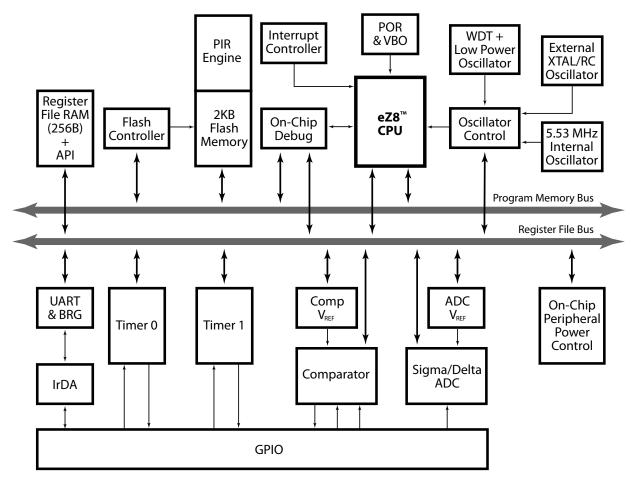

# **Z8FS021 MCU Block Diagram**

Figure 1 displays a block diagram of the Z8FS021 MCU.

Figure 1. Z8FS021 MCU Block Diagram

PS028804-1011 Overview

#### **MCU Part Selection Guide**

Table 1 displays the basic features and package styles available for each device within the Z8FS021 ZMOTION Intrusion Detection MCU devices. Select the package type that is most suitable to your application based on required General Purpose I/Os and ADC channels. The table suggests references to the pin configuration diagrams for the peripheral functions available on each I/O pin.

See the <u>Ordering Information</u> section on page 47 for a list of all ZMOTION Intrusion Detection part numbers.

Table 1. Z8FS021 ZMOTION Intrusion Detection MCU Part Selection Guide

| ZMOTION MCU<br>Part Number                                                  | Z8 Encore! XP<br>Base Part Number | Flash<br>Memory | GPIO | ADC<br>Channels | Package     | Pin<br>Configuration<br>Diagram |  |

|-----------------------------------------------------------------------------|-----------------------------------|-----------------|------|-----------------|-------------|---------------------------------|--|

| Z8FS021xSB20EG                                                              | Z8F082ASB020EG                    | 2KB             | 5    | 3               | 8-pin SOIC  | Figure 2                        |  |

| Z8FS021xHH20EG                                                              | Z8F082AHH020EG                    | 2KB             | 16   | 4               | 20-pin SSOP | Figure 3                        |  |

| Z8FS021xHJ20EG                                                              | Z8F082AHJ020EG                    | 2KB             | 22   | 6               | 28-pin SSOP | Figure 4                        |  |

| Note: $x = PIR$ Engine Revision Identifier (see <u>Table 4</u> on page 23.) |                                   |                 |      |                 |             |                                 |  |

# **Pin Configuration**

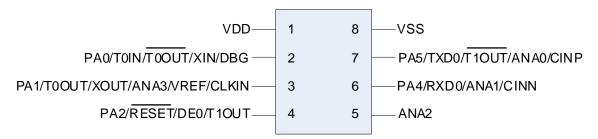

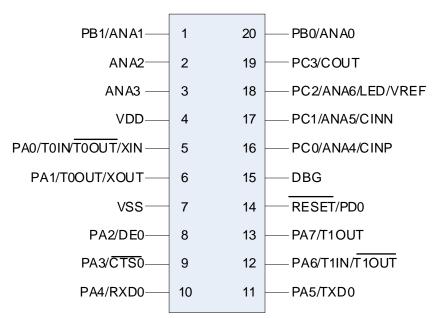

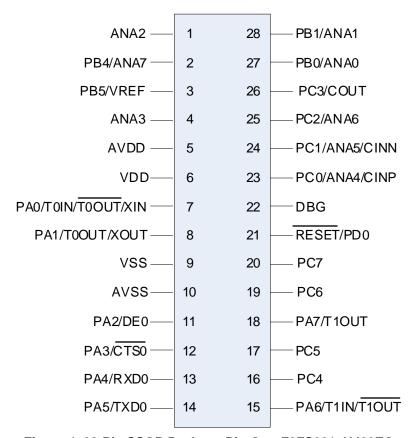

The Z8FS021 MCU is available in a variety of package styles and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information about the physical package specifications, see the <u>Packaging</u> section on page 46.

Figures 2 through 4 display the pin configurations of all the packages available for the ZMOTION MCU Series. For a description of the signals, see <u>Tables 6 through 8</u> on pages 24 through 26.

At reset, all port pins are set to GPIO input state except /RESET/DE0/T1OUT (8-pin) which is configured to /RESET, PA0/T0IN/T0OUT/XIN/DBG (8-pin), which is configured to DBG and RESET/PD0 (20- and 28-pin) which are configured to /RESET.

Figure 2. 8-Pin SOIC Package Diagram - Z8FS021xSB20EG

PS028804-1011 Pin Configuration

Figure 3. 20-Pin SSOP Package Diagram - Z8FS021xHH20EG

PS028804-1011 Pin Configuration

Figure 4. 28-Pin SSOP Package Pin-Out, Z8FS021xHJ20EG

PS028804-1011 Pin Configuration

# **Signal Descriptions**

Table 2 describes the Z8FS021 MCU signals. Signal availability is package dependent. See the Pin Configuration section on page 5 for signal availability multiplexing.

Table 2. Z8FS021 MCU Signal Descriptions

| Signal<br>Mnemonic            | I/O | Description                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| General-Purpose I/O Ports A–D |     |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| PA[7:0]                       | I/O | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                |  |  |  |  |  |

| PB[5:0]                       | I/O | Port B. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                |  |  |  |  |  |

| PC[7:0]                       | I/O | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                |  |  |  |  |  |

| PD[0]                         | 0   | Port D. This pin is used for general-purpose output only.                                                                                                                                                                                                                                           |  |  |  |  |  |

| UART Controllers              |     |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TXD0                          | 0   | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                           |  |  |  |  |  |

| RXD0                          | I   | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                               |  |  |  |  |  |

| CTS0                          | I   | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                  |  |  |  |  |  |

| DE                            | 0   | Driver Enable. This signal allows automatic control of external RS-485 drivers. It is approximately the inverse of the Transmit Empty (TXE) bit in the UART Status 0 Register. The DE signal can be used to ensure that the external RS-485 driver is enabled when data is transmitted by the UART. |  |  |  |  |  |

| Timers                        |     |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| T0OUT/T1OUT                   | 0   | Timer Output 0–1. These signals are outputs from the timers.                                                                                                                                                                                                                                        |  |  |  |  |  |

| T0OUT/T1OUT                   | 0   | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                      |  |  |  |  |  |

| TOIN/T1IN                     | 1   | Timer Input 0–1. These signals are used as the capture, gating and counter inputs.                                                                                                                                                                                                                  |  |  |  |  |  |

| Comparator                    |     |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| CINP/CINN                     | I   | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                            |  |  |  |  |  |

| COUT                          | 0   | Comparator Output.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Analog                        |     |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| ANA[7:0]                      | I   | Analog Port. These signals are used as inputs to the analog-to-digital converter (ADC).                                                                                                                                                                                                             |  |  |  |  |  |

| V <sub>REF</sub>              | I/O | Analog-to-digital converter reference voltage input, or buffered output for internal reference.                                                                                                                                                                                                     |  |  |  |  |  |

PS028804-1011 Signal Descriptions

Table 2. Z8FS021 MCU Signal Descriptions (Continued)

| Signal<br>Mnemonic                                                                   | I/O | Description                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillators                                                                          |     |                                                                                                                                                                                                                                                                            |

| crystal can be connected between it a<br>oscillator. In addition, this pin is used w |     | External Crystal Input. This pin is the input pin to the crystal oscillator. A crystal can be connected between it and the XOUT pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| XOUT                                                                                 | 0   | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the XIN pin to form the oscillator.                                                                                                                   |

| Clock Input                                                                          |     |                                                                                                                                                                                                                                                                            |

| CLKIN                                                                                | I   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                       |

| LED Drivers                                                                          |     |                                                                                                                                                                                                                                                                            |

| LED                                                                                  | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                                                                                |

| On-Chip Debugger                                                                     |     |                                                                                                                                                                                                                                                                            |

| DBG                                                                                  | I/O | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                              |

| The                                                                                  |     | The DBG pin is open-drain and requires a pull-up resistor to ensure proper operation.                                                                                                                                                                                      |

| Reset                                                                                |     |                                                                                                                                                                                                                                                                            |

| RESET                                                                                | I/O | RESET. Generates a Reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor.                                                      |

| Power Supply                                                                         |     |                                                                                                                                                                                                                                                                            |

| $\overline{V_{DD}}$                                                                  | I   | Digital Power Supply.                                                                                                                                                                                                                                                      |

| AV <sub>DD</sub>                                                                     | I   | Analog Power Supply.                                                                                                                                                                                                                                                       |

| V <sub>SS</sub>                                                                      | I   | Digital Ground.                                                                                                                                                                                                                                                            |

| AV <sub>SS</sub>                                                                     | I   | Analog Ground.                                                                                                                                                                                                                                                             |

|                                                                                      |     |                                                                                                                                                                                                                                                                            |

Signal Descriptions PS028804-1011

# Flash Memory Map

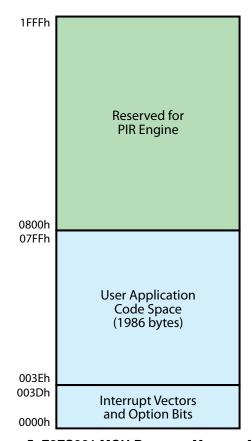

The Z8FS021 MCU is based on Zilog's Z8F082A device, which contains a total of 8KB Flash memory. Zilog's PIR technology is located in the 6KB address range 0800h–1FFFh, a code space that is locked and cannot be erased by the user or by the Zilog Debug Interface (ZDI) mass erase or page erase commands. The remaining 2 KB of this Flash memory space, in the address range 0000h–07FFh, is available for user application code.

A memory map of the Z8FS021 MCU's Flash code space is illustrated in Figure 5.

Figure 5. Z8FS021 MCU Program Memory Map

PS028804-1011 Flash Memory Map

## **RAM Memory Map**

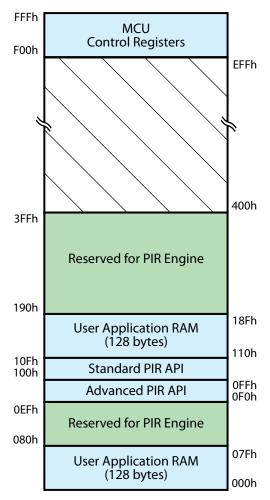

There is a total of 1 KB of RAM available on the base Z8F082A device. Some of this RAM (from 080h to 0EFh and from 190h to 3FFh) is used by Zilog's PIR technology. The remainder of the RAM, from 000h to 07Fh and from 110h to 18Fh (256 bytes) is available to the application. The MCU Control Registers are located at the top of memory, from F00h to FFFh, and are also available to the application. The area from 400h to EFFh contains no device memory. See Figure 6.

The ZMOTION Motion Detection API is a series of registers located in the RAM memory space in the address range 0F0h-10Fh. It is through these memory locations that configuration and status are passed between the PIR Engine and the user application. Advanced API registers are located in the range 0F0h-0FFh. See the <u>PIR Engine and API</u> section on page 21 for details about these API registers and to set up the project memory environment.

Figure 6. Z8FS021 MCU RAM Memory Map

PS028804-1011 RAM Memory Map

# **Peripherals**

The following sections describe the differences, changes or limitations placed on any of the Z8FS021 peripherals or other functions from the base Z8F082A device. For more information about the operation of each peripheral, please refer to the appropriate section of the Z8 Encore! XP F082A Series Product Specification (PS0228).

#### **Peripheral Availability**

Table 3 shows how the Z8FS021 MCU peripherals are used by Zilog's PIR technology and how these peripherals differ from their counterparts on the base Z8F082A device. The peripherals used by the PIR Engine should not be used by the application unless the Engine is disabled through the <u>PIR Engine Enable Register</u>.

**Table 3. Peripheral Availability**

|                  |                                                                                         | Device                                                                               |                                                                 |

|------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                  | Z8FS021xSB20EG                                                                          | Z8FS021xHH20EG                                                                       | Z8FS021xHJ20EG                                                  |

| Base MCU Device  | Z8F082ASB020EG                                                                          | Z8F082AHH020EG                                                                       | Z8F082AHJ020EG                                                  |

| Pins/Package     | 8-pin SOIC                                                                              | 20-pin SSOP                                                                          | 28-pin SSOP                                                     |

| ADC              | ANA1 is used for White<br>Light Detection when<br>enabled.                              | ANA1 is used for White Light Detection when enabled.                                 | ANA1 is used for White Light Detection when enabled.            |

|                  | ANA2 is used for PIR sensor input.                                                      | ANA2 is used for PIR sensor input.                                                   | ANA2 is used for PIR sensor input.                              |

|                  | ANA3 is used for a second sensor input in                                               | ANA3 is connected to ANA6/V <sub>REF</sub> .                                         | ANA3 is connected to V <sub>REF</sub> .                         |

|                  | Dual Pyro Mode.                                                                         | ANA3 is used for a second sensor input and ANA6 becomes available in Dual Pyro Mode. | ANA3 is used for a second sensor in Dual Pyro Mode.             |

| V <sub>REF</sub> | Internal V <sub>REF</sub> used by the PIR Engine and set to 1V.                         | Internal V <sub>REF</sub> used by the PIR Engine and set to 1V.                      | Internal V <sub>REF</sub> used by the PIR Engine and set to 1V. |

| Timer 0          | Available to application.                                                               | Available to application.                                                            | Available to application.                                       |

| Timer 1          | Available to application.                                                               | Available to application.                                                            | Available to application.                                       |

| GP I/O           | PA3/PA1 are multiplexed with ANA2/ANA3 and                                              | PB2, PB3 & PC2 are used for PIR functions.                                           | PB2, PB3 & PB5 are used for PIR functions.                      |

|                  | used for PIR sensor input (ANA2 for single pyro mode and ANA2/ANA3 for dual pyro mode). | In dual pyro mode, PC2 becomes available.                                            | In dual pyro mode, PB5 becomes available.                       |

**Table 3. Peripheral Availability (Continued)**

| Low Power Op Amp   | Not Available                      | Not Available             | Not Available             |

|--------------------|------------------------------------|---------------------------|---------------------------|

| Comparator         | Available to application.          | Available to application. | Available to application. |

| UART               | Available to application – No CTS. | Available to application. | Available to application. |

| Temperature Sensor | Not available.                     | Not available.            | Not available.            |

| LED Drive          | _                                  | Available to application. | Available to application. |

| WDT                | Available to application.          | Available to application. | Available to application. |

The remainder of this section further describes the differences in application availability between the 8-pin, 20-pin and 28-pin peripheral sets.

#### **Analog to Digital Signal Conversion**

Zilog's PIR technology requires exclusive access to the ADC peripheral to detect motion. However, ADC conversions can be requested by the application via the API (PIR Status/Control Register 3). If it is necessary for the user application to utilize the ADC peripheral directly, the PIR Engine must first be disabled via the PIR Engine Enable Register in the API. Motion detection is not possible while the PIR Engine is disabled. When the user application is finished with the ADC peripheral, it must reenable the PIR Engine.

**8-Pin Device.** PA3 (ANA2) is reserved as the analog ADC input from the pyroelectric sensor. Therefore, ANA2 is not available for user applications. Additionally, ANA3 is used for a second sensor input in Dual Pyro Mode. All other channels are available to the user application.

| ADC Channel | Available to Application             |

|-------------|--------------------------------------|

| 0           | Yes                                  |

| 1           | Yes – used for White Light detection |

| 2           | No                                   |

| 3           | Only in Single Pyro Mode             |

**20-Pin Device.** PB2 (ANA2) is reserved as the analog ADC input from the pyroelectric sensor. Therefore, ANA2 is not available for user applications. Additionally, ANA3 and ANA6 are not available because PB3 (ANA3) must be tied directly to PC2 (ANA6/ $V_{REF}$ ). PC2 is configured as  $V_{REF}$  output by the PIR Engine. In Dual Pyro Mode, ANA3 is used for a second sensor input rather than being tied to  $V_{REF}$ ; ANA6/ $V_{REF}$  therefore becomes available. All other channels are available to the user application.

| ADC Channel | Available to Application             |

|-------------|--------------------------------------|

| 0           | Yes                                  |

| 1           | Yes – used for White Light detection |

| 2           | No                                   |

| 3           | No                                   |

| 4           | Yes                                  |

| 5           | Yes                                  |

| 6           | Only in Dual Pyro Mode               |

**28-Pin Device.** PB2 (ANA2) is reserved as the analog ADC input from the pyroelectric sensor. Therefore, ANA2 is not available for user applications. Also, ANA3 is not available because it is tied directly to PB5/ $V_{REF}$ . PB5 will be configured as  $V_{REF}$  output by the PIR Engine. In Dual Pyro Mode, ANA3 is used for a second sensor input rather than being tied to  $V_{REF}$ ; PB5 therefore becomes available. All other channels are available to the user application.

| ADC Channel | Available to Application             |

|-------------|--------------------------------------|

| 0           | Yes                                  |

| 1           | Yes – used for White Light detection |

| 2           | No                                   |

| 3           | No                                   |

| 4           | Yes                                  |

| 5           | Yes                                  |

| 6           | Yes                                  |

| 7           | Yes                                  |

#### **Timers**

The Z8FS021 MCU offers two independent and identical 16-bit multi-function timers, Timer 0 and Timer 1; both are available to the user application.

| Timer 0      |                                                                                                                                                                                   |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 8-Pin Device | TOOUT is not available in Dual Pyro Mode; it is configured as ANA3 to support a second sensor input. All other external Timer 0 functions are available for the user application. |  |  |

| 20-Pin Device | All external Timer 0 functions are available for the user application. |

|---------------|------------------------------------------------------------------------|

| 28-Pin Device | All external Timer 0 functions are available for the user application. |

|               | Timer 1                                                                                                                                                                      |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 8-Pin Device  | T1IN is configured as ANA2 to support the signal input from the pyroelectric sensor and is not available to the user application. All other Timer 1 functions are available. |  |  |  |  |

| 20-Pin Device | All external Timer 1 functions are available for the user application.                                                                                                       |  |  |  |  |

| 28-Pin Device | All external Timer 1 functions are available for the user application.                                                                                                       |  |  |  |  |

# **Watchdog Timer**

No changes or limitations are placed on WDT functions by the PIR Engine; the WDT is available to the user application.

# Comparator

| 8-Pin Device  | The external pin that carries COUT is configured as ANA2 to support the signal input from the Pyroelectric sensor. However, the Comparator is still able to generate an interrupt internally without COUT. |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-Pin Device | All external Comparator functions are available for the user application.                                                                                                                                  |

| 28-Pin Device | All external Comparator functions are available for the user application.                                                                                                                                  |

#### **UART**

| 8-Pin Device  | /CTS0 is configured as ANA2 to support the signal input from the Pyroelectric sensor. It is therefore not available to the user application. The UART is still able to function correctly without /CTS when CTSE in the U0CTL0 Register is set to 0. |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-Pin Device | All external UART functions are available for the user application.                                                                                                                                                                                  |

| 28-Pin Device | All external UART functions are available for the user application.                                                                                                                                                                                  |

#### **Oscillator Control**

All devices can be operated with the internal 5.54MHz IPO. For applications that require more processing power or a more accurate time base, an external crystal oscillator or ceramic resonator can be used.

When using the 8-pin device, external oscillator support is limited to Single Pyro Mode only, because ANA3 (the ADC input for a second pyro sensor) is multiplexed with  $X_{OUT}$ . The 20- and 28-pin devices can be operated with an external oscillator in both Single and Dual Pyro modes.

**Caution:** Do not operate at frequencies lower than the IPO frequency while the PIR Engine is enabled or motion detection performance will be degraded.

No other changes or limitations are placed on oscillator control functions by the PIR Engine.

#### **Flash Memory**

The control registers associated with Flash memory are all available to the application. The PIR Engine uses the value programmed into the Flash Frequency registers (FFREQ) to determine the required sample rate of the ADC and other functions. The Flash Frequency High (FFREQH) and Flash Frequency Low Byte (FFREQL) registers must be programmed prior to initializing the PIR Engine. These two registers combine to form a 16-bit value, FFREQ. This value is the System Clock Frequency in KHz and is calculated using the following equation.

#### **Interrupt Controller**

No changes or limitations are placed on the interrupt controller functions by the PIR Engine.

#### **Temperature Sensor**

The temperature sensor is not tested or calibrated (trim bits are not available). Therefore, this peripheral is not available on any of the Z8FS021 devices.

#### **Low-Power Operational Amplifier**

The AMPINP signal is multiplexed with ANA2 which is used for the pyro sensor input. Therefore, this peripheral is not available on any of the Z8FS021 devices.

#### Non-Volatile Data Storage

There is no dedicated non-volatile data storage on the Z8FS021 devices.

#### Pin Availability

Although most pins on the ZMOTION MCU Series are available to the application, some pins are dedicated to supporting the functions of the PIR Engine. This section describes which pins are reserved and which are available to the application. The pins used by the PIR Engine are automatically configured when the Engine is initialized.

#### **General-Purpose Input/Output**

All of the General Purpose I/Os are available except for those used for the PIR circuit. See <u>Appendix A. Example Application Schematics</u> on page 51 for more information.

| 8-Pin Device | Pin 5 (ANA2) is reserved as the analog ADC input from the pyroelectric sensor. Any other |

|--------------|------------------------------------------------------------------------------------------|

|              | functions multiplexed with Pin 5 (PA3//CTS0, COUT and T1IN) are not available for user   |

|              | applications.                                                                            |

|              | In Dual Dura Mode, in which the application uses 2 pyraelectric concern Din 2 (ANA2) is  |

In Dual Pyro Mode, in which the application uses 2 pyroelectric sensors, Pin 3 (ANA3) is used as an analog ADC input for a second sensor and is therefore not available for other functions (T0OUT/V<sub>RFF</sub>/CLKIN).

20-Pin Device

Pin 2 (ANA2) is reserved as the analog ADC input from the pyroelectric sensor. In Single Pyro Mode, Pin 3 (ANA3) must be externally tied to V<sub>REF</sub> on Pin 18 (PC2/ANA6/LED/V<sub>REF</sub>). PC2 will be configured as the V<sub>REF</sub> output by the PIR Engine when it is enabled. In Dual Pyro Mode (supporting 2 pyroelectric sensors), Pin 3 (ANA3) is used for the second sensor. In this mode the Pin 18 V<sub>REF</sub> signal is not connected externally to any other ADC inputs and is therefore available to the application (PC2/ANA6/LED/V<sub>REF</sub>).

28-Pin Device

Pin 1 (ANA2) is reserved as the analog ADC input from the pyroelectric sensor. In Single Pyro Mode, Pin 4 (ANA3) must be externally tied to  $V_{REF}$  on Pin 3 (PB5/ $V_{REF}$ ). PB5 will be configured as  $V_{REF}$  output by the PIR Engine when it is enabled.

In Dual Pyro Mode, which supports 2 pyroelectric sensors, Pin 4 (ANA3) is used for the second sensor. In this mode the Pin 3  $V_{REF}$  signal is not connected externally to any other ADC inputs and is therefore available to the application (PB5/ $V_{REF}$ ).

# **Hardware Connection Requirements**

This section describes the required external hardware connection for the ZMOTION MCU Series. See <u>Appendix A. Example Application Schematics</u> on page 51 for example schematic diagrams showing these connections.

Pins are automatically configured to their required function when the PIR Engine is initialized via the EPIR\_INIT macro. The device can be operated in Single Pyro Mode when supporting one pyroelectric sensor or in Dual Pyro Mode when supporting two pyroelectric sensors. Both of these modes can be operated in Normal or Low Scan Rate modes.

Depending on the application, there can be up to four connection requirements supporting these modes: one for each of two PIR sensors, one for the ADC and one for the White Light Detection and Status LED. A description of each of these elements follows in this section. For a broader description of the White Light Detection component, see the White Light Detection section on page 19.

#### Pyroelectric PIR Sensor #1

The signal from the PIR sensor is connected directly to the ANA2 input of the ADC. The ADC is configured for differential buffered mode by Zilog's PIR technology. The sensor signal should be connected directly to the ADC input with no additional signal conditioning circuitry unless specified by the pyroelectric sensor manufacturer.

#### ADC V<sub>REF</sub>

The on-chip  $V_{REF}$  is configured for 1V of nominal voltage. The PIR Sensor signal is connected to the positive (+) differential input of the ADC (ANA2), and the  $V_{REF}$  signal is connected to the negative (–) differential input (ANA3). The 8-pin device provides an internal connection from  $V_{REF}$  to ANA3 to support this configuration; therefore, no external hardware connection is required. The 20- and 28-pin devices require an external connection from the  $V_{REF}$  output signal to the ADC negative (–) (ANA3) input.

#### Pyroelectric PIR Sensor #2

In Dual Pyro Mode, the ADC is still used in differential buffered mode (i.e., as is true for Single Pyro Mode). The signal from the second PIR sensor is connected to ANA3. The

$V_{REF}$  signal is no longer connected to ANA3 negative (–) ADC input. The fist PIR sensor is connected to the positive (+) ADC input (ANA2) as it is in Single Pyro Mode. The  $V_{REF}$  signal is still used internally for the ADC, but the external pin is unused in Dual Pyro Mode.

#### White Light Detection and Status LED

When enabled via the White Light Threshold field in the <u>PIR Status/Control Register 2</u>, the PIR Engine automatically performs ADC conversions on the ANA1 input. The signal on this input should be proportional to the amount of white light to which the PIR sensor is being subjected. Typically, this pin would be connected to a high-efficiency (status) LED which generates a small voltage in the presence of white light. The PIR Engine configures the pin to a (single-ended) analog input, perform the necessary ADC conversion and reconfigure it to a digital output. See the following White Light Detection section for more information about the operation of this mode.

# **White Light Detection**

Due to the nature of the pyroelectric sensor, sudden large changes in white light will cause a DC shift in the signal output, which could potentially generate a false motion event. Sources such as car headlights have been known to cause this issue. The PIR Engine can monitor this occurrence and be configured to ignore the event.

When light hits the pyroelectric sensor, its energy is converted into a signal output. If the pattern and intensity of the light is optimal, then the signal can appear exactly like a motion event. However, the PIR Engine can determine when the sensor is being exposed to light and use this information to filter out an invalid motion event.

When enabled via the White Light Threshold (WLT) bits in the ePIR\_SC2 Register (see Table 10 on page 31), the PIR Engine automatically performs ADC conversions on ANA1, which should be connected to a high-efficiency LED (typically a status LED). When light shines on an LED, it generates a small voltage which the PIR Engine can measure. The PIR Engine reconfigures the pin to an analog input and performs the necessary ADC conversion. The system should be configured such that if light is shining on the LED, it is also shining on the PIR sensor. As a result, it is advisable to avoid placing the LED behind a lens with white light filtering.

When the Engine detects a sudden change in voltage on ANA1 greater than the value set in the White Light Threshold field of ePIR\_SC2, the motion detection algorithms automatically compensate for the associated signal level shift from the pyroelectric sensor (caused by the light simultaneously shining on the LED and the pyroelectric sensor). This compensation allows the PIR Engine to suppress false motion events caused by White Light while still detecting real motion events. However, sensitivity is reduced during this period. The White Light Detected bit of the ePIR\_ASC0 Register is set to indicate the

detection of White Light and stays set until cleared by the application. No other action is required by the application.

Additionally, an Anti-Jam feature is available via bit 5 of the ePIR\_ASC0 Register to prevent intentional jamming of the detector. When Anti-Jam is on, the Engine looks for continuous white light events occurring within a short time span (for example, a malicious intruder continuously flashing a bright light onto the detector). After 12 white light events within a short time period, the Engine automatically begins ignoring the white light events and returns to normal motion detection. The Engine begins responding to white light events after a period without white light events.

When White Light Detection Mode is enabled by programming the White Light Threshold bits in PIR Status/Control Register 2 (ePIR\_SC2), the application is not required to perform any other functions. The PIR Engine performs all required tasks related to White Light immunity. The White Light Detected bit in <a href="PIR Status/Control Register 1">PIR Status/Control Register 1</a> simply provides the application with an indication that a white light event has occurred.

#### **LED Requirements**

The PIR Engine uses the voltage generated by the LED connected to ANA1 to determine the level of white light to which the system is being subjected. While most high-efficiency LEDs will perform correctly for this function, there are certain requirements placed on the specifications of the LED that is used in the system.

These requirements are:

- Do not place the LED behind any white light filtering material. If it is behind a lens or a light pipe, these materials should be transparent to white light.

- Ensure that the light source for the LED is originating from the same general direction as the PIR sensor. It is important that the PIR sensor and the LED receive the light at the same time.

- LEDs are available with a large range of electrical specifications. The White Light

Threshold Detection bits in the ePIR\_SC02 Register allow the PIR Engine the flexibility to work with many LED types, but generally LEDs that are more efficient at generating a voltage from a light source perform better as white light detectors.

- Most high-efficiency LEDs in red, yellow or green with a forward voltage drop less than 2V @2mA are well suited for white light detection.

## PIR Engine and API

The ZMOTION MCU Series is developed upon the Z8 Encore! XP-based Z8F082A MCU with the added functionality of a motion detection (PIR) Engine. The PIR Engine is located in the upper 4KB area of the 8KB device, leaving 4KB of code space to the user application. The PIR Engine operates in the background and is controlled and monitored via an Application Programmer Interface (API). The API is a series of reserved registers in memory.

There are two sections to the API: Standard API Registers and Advanced API Registers, as described below.

**Standard API Registers.** These registers include all of the status and control functions required by most applications. These include sensitivity control, motion detection/direction status and operational modes.

**Advanced API Registers.** These registers provide additional control over the PIR Engine operation and allows it to be configured to support the pyroelectric sensor and lens being used in the application.

#### **PIR Engine Timer Tick**

Bit 7 of <u>PIR Status/Control Register 1</u> provides a one-second time base for the PIR Engine to perform housekeeping operations. This bit must be set to 1, once per second by the user application. The bit is checked and cleared during the EPIR\_ADC\_ISR routine.

#### **PIR Engine Entry Points**

There are two entry points to the PIR Engine that are accessed via two predefined macros – one is an initialization macro that is used to start the Engine and the other is executed upon every ADC interrupt. Both macros save and initialize the Register Pointer, perform a call to the PIR Engine entry point and then restore the Register Pointer before returning control to the application. It is the responsibility of the application software to execute these macros at the appropriate time.

**ePIR\_INIT Macro.** This macro is executed to initialize the PIR Engine after reset. It is normally only executed once and is used in conjunction with the <u>PIR Engine Enable Register</u> in the Standard API section. The application should initialize all API registers, write the PIR Enable Pattern to the PIR Engine Enable Register, then execute this macro. ADC conversions are started by this macro.

EPIR\_INIT Macro:

PUSHX RP

LDX RP, #%E0

CALL %1FFD

POPX RP

PS028804-1011 PIR Engine and API

S Company 22

CPU Cycles: 261

Peripherals initialized: ADC and GPIO, depending on API-selected options. The ADC IRQ is set for medium priority.

**ePIR\_ADC\_ISR Macro.** This macro is executed for each ADC conversion. The application handles the ADC interrupt and executes this macro. All motion detection processing is performed by this macro.

EPIR\_ADC\_ISR Macro:

PUSHX RP

LDX RP, #%E0 CALL %1000 POPX RP

The CPU cycles used by the **EPIR\_ADC\_ISR** macro vary depending on Engine state and configuration.

#### PIR Engine CPU Stack Usage

The PIR Engine shares the processor stack with the user application. There are no special requirements on the placement of the stack in memory, but it is essential that the user provide enough stack space for both the user application and the PIR Engine.

The PIR Engine requires a maximum 6 bytes of stack.

PS028804-1011 PIR Engine and API

# **Standard API Register Set**

The Standard API Register set, shown in Table 4, is a series of registers implemented in the Z8FS021 MCU RAM that allows the user code to configure and communicate with the PIR Engine. The default values are loaded only when the PIR Engine is enabled via the PIR Enable Register.

Table 4. PIR Engine Standard API Registers

| API Register Name                                     | Address   | Mnemonic         | Description                            |

|-------------------------------------------------------|-----------|------------------|----------------------------------------|

| PIR Engine Enable Register (ePIR_Enable)              | 100h      | ePIR_Enable      | Enable PIR Engine.                     |

| PIR Sensitivity Register (ePIR_Sensitivity)           | 101h      | ePIR_Sensitivity | Motion Sensitivity.                    |

| PIR Status/Control Register 0 (ePIR_SC0)              | 102h      | ePIR_SC0         | Motion Status and Engine Mode Control. |

| PIR Status/Control Register 1 (ePIR_SC1)              | 103h      | ePIR_SC1         | Engine Status and Control.             |

| PIR Status/Control Register 2 (ePIR_SC2)              | 104h      | ePIR_SC2         | Range Control.                         |

| PIR Status/Control Register 3 (ePIR_SC3), 28-pin SSOP | 105h      | ePIR_SC3         | ADC Scan Request.                      |

| PIR ADC Result Value (ePIR_ADC_Result)                | 10Ah/10Bh | ePIR_ADC_Result  | ADC Scan Result.                       |

| PIR Version (ePIR_Version)                            | 10Ch      | ePIR_Version     | PIR Engine Software Version.           |

Tables 5 through 15 describe each of the standard API registers listed in Table 4.

# Table 5. PIR Engine Enable Register (ePIR\_Enable)

| Bit     | 7 | 6                          | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---|----------------------------|---|---|---|---|---|---|

| Field   |   | PIR Enable/Disable Pattern |   |   |   |   |   |   |

| Control |   | Read/Write                 |   |   |   |   |   |   |

| Address |   | 100H                       |   |   |   |   |   |   |

#### PIR Enable/Disable Pattern (Bits 7-0)

PIR Enable/Disable Register; controlled by the application.

- The PIR Enable Register controls the overall operation of the PIR Engine. As an added level of

protection, there are specific 8-bit enable and disable values; all other values are reserved. Reading this

register returns the last value written. Once enabled, the PIR Engine reads the application-controlled

Status/Control Register values and sets the Engine-controlled values to their default states.

- To enable the PIR Engine, first write the ePIR\_ENABLE\_PATTERN to the PIR Enable Register, then execute the EPIR\_INIT macro. See Table 6.

#### **Table 6. PIR Software Enable Patterns**

| Pattern | Name                 | Description                                                                                                                                                                                                                   |

|---------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h     | ePIR_DISABLE_PATTERN | Disables all PIR Engine functions, including motion detection. Used to temporarily or permanently shut down the Engine.                                                                                                       |

| 11h     | ePIR_ENABLE_PATTERN  | Enables the PIR Engine. All primary Engine functions, as configured in Engine Status/Control Registers, are enabled. Confirmation of enabled status is provided through the Engine Disabled bit in Status/Control Register 0. |

# Table 7. PIR Sensitivity Register (ePIR\_Sensitivity)

| Bit     | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-------------|---|---|---|---|---|---|---|--|--|

| Field   | Sensitivity |   |   |   |   |   |   |   |  |  |

| Default | U           | U | U | U | U | U | U | U |  |  |

| Control | Read/Write  |   |   |   |   |   |   |   |  |  |

| Address | 101H        |   |   |   |   |   |   |   |  |  |

#### Sensitivity (Bits 7)

PIR Sensitivity Setting; controlled by the application.

The PIR Sensitivity Register is used to adjust the sensitivity of the PIR Engine to target motion. Lower

values produce higher sensitivity to motion with 00h being the most sensitive and FFh being the least

sensitive. The user application should load this register with the appropriate value to provide the

appropriate sensitivity.

#### Notes:

- 1. The setting of this register also affects the range of detection. Lower values increase range and higher values decrease range.

- 2. Depending on the lens and pyroelectric sensor used, values above 3Fh can result in very limited detection.

# Table 8. PIR Status/Control Register 0 (ePIR\_SC0)

| Bit     | 7                  | 6 | 5                  | 4             | 3                              | 2                   | 1                  | 0          |  |  |

|---------|--------------------|---|--------------------|---------------|--------------------------------|---------------------|--------------------|------------|--|--|

| Field   | Extended Detection |   | Engine<br>Disabled | MD<br>Suspend | Motion<br>Direction<br>Control | Motion<br>Direction | Motion<br>Detected | PIR Stable |  |  |

| Control | R/W                |   | R                  | R/W           | R/W                            | R                   | R/W                | R          |  |  |

| Address | 102H               |   |                    |               |                                |                     |                    |            |  |  |

#### Extended Detection Level (Bits 7-6)

Sets the sensitivity level of the extended detector; controlled by the application.

- These two bits enhance the motion detection algorithms to detect slower, faster and/or more subtle

motion. The Extended Detection level is selected to provide a balance between additional sensitivity

while maintaining stability (no false detections). In certain applications such as lighting control, the

Extended Detection level can be increased when normal motion has been detected. Extended

detection is dependent on the lens pattern used. Smaller lens beams tend to provide more subtle

motion detection.

- The Extended Detection level affects user control over the range provided in ePIR\_SC2. As the Extended Detection level is increased, the Range setting becomes less effective.

- 00 = Extended Detection Level 0 Minimum (least sensitive).

- 01 = Extended Detection Level 1.

- 10 = Extended Detection Level 2.

- 11 = Extended Detection Level 3 High (most sensitive).

#### **Engine Disabled (Bit 5)**

PIR Engine Disable/Suspend Acknowledged; controlled by the PIR Engine.

- This bit indicates the operational status of and is controlled by the PIR Engine. When the Engine is initialized and enabled by loading the PIR Enable Register with the ePIR\_ENABLE\_PATTERN value, this bit is cleared to indicate that the Engine is ready. When the Engine is disabled by loading the PIR Enable Register with the ePIR\_DISABLE\_PATTERN, it will respond by setting this bit to 1 and perform no further operations until reenabled. For the Engine to detect that it has been disabled, the user must allow the Engine ADC interrupt to run at least once after loading the PIR Enable Register with the ePIR\_DISABLE\_PATTERN.

- 0 = Engine is enabled and operational.

- 1 = Engine is disabled and not operational.

#### MD Suspend (Bit 4)

Motion Detection Suspend; controlled by the application.

- Temporarily suspends the PIR Engine from running and places it in a very low processing overhead state and can be used when the application requires significant CPU processing power. While suspended, motion detection is disabled; however, to ensure fast recovery from this mode, ADC interrupts still occur and samples continue to be buffered. When the application clears this bit, suspend mode is exited upon the next ADC interrupt.

- 0 = Normal Motion Detection.

- 1 = Suspended Motion Detection.

#### **Motion Direction Control (Bit 3)**

Motion Direction Control Enable; controlled by the application.

- This bit enables directional motion detection. The relative direction of the detected motion is indicated in bit 2 (Motion Direction) of this same register. When configured as a directional detector (bit 3 set to 1), direction is indicated in bit 2 as a positive or negative relative to the PIR sensor.

- 0 = Standard Motion Detection Mode. Motion is detected in any direction; the Motion Direction status bit (Bit 2) is not valid.

- 1 = Directional Motion Detection Mode. Motion is detected in any direction; relative direction is indicated via the Motion Direction status bit (Bit 2).

- The directional polarity of PIR sensors is arbitrary at the time of manufacturing. Therefore, it is necessary for the user application to calibrate to each individual PIR sensor using a controlled target (i.e. moving in a known direction) and internally recording the polarity to identify which polarity represents that direction.

#### **Motion Direction (Bit 2)**

Relative Direction of Last Motion Detected; controlled by the PIR Engine.

When directional motion detection is enabled, this bit indicates the relative direction of the last motion detected. When the PIR Engine sets the Motion Detected bit in PIR Status Register 0, this bit is set or cleared to indicate the direction of the motion. The status is latched until the user application clears the Motion Detected bit.

- 0 = Last detected motion was negative.

- 1 = Last detected motion was positive.

This status bit is undefined when Motion Direction Control is disabled.

#### **Motion Detected (Bit 1)**

Motion Detected on PIR Sensor

Set by the PIR Engine; cleared by the application.

This bit indicates that the Engine has detected a motion event. The user application should routinely check this bit to determine if motion has been detected. This bit is set by the Engine and must be cleared by the user application.

- 0 = No motion detected by the Engine.

- 1 = Motion has been detected by the Engine.

#### PIR Stable (Bit 0)

Passive Infrared (PIR) sensor signal stabilized bit; controlled by the PIR Engine.

After periods of non-use, the PIR sensor will take some time to stabilize before it can be used reliably. The amount of time is dependent on the PIR Sensor being used as well as environmental conditions; it can range from a few seconds to as much as one minute. To relieve the application software from having to assume a worst-case stabilization time, the PIR Engine automatically monitors the DC offset of the PIR sensor and sets this bit when it determines that it has become stable. This bit indicates that the PIR sensor has stabilized after one of the following conditions:

- · After initial power on (cold start).

- After re-enabling the Engine via PIR Enable Register.

- · After returning from sleep mode.

- 0 = PIR sensor signal is not stable; motion detected events are not valid.

- 1 = PIR sensor signal is stable; motion detected events are valid.

## Table 9. PIR Status/Control Register 1 (ePIR\_SC1)

| Bit     | 7                    | 6 | 5                  | 4      | 3  | 2   | 1               | 0                   |

|---------|----------------------|---|--------------------|--------|----|-----|-----------------|---------------------|

| Field   | Engine<br>Timer Tick |   | Frequency Response |        |    |     | 2-Pulse<br>Mode | Dual Pyro<br>Enable |

| Control | R/W                  |   | Read               | /Write |    | R/W | R/W             | R/W                 |

| Address |                      |   |                    | 10     | 3H |     |                 | •                   |

#### **Engine Timer Tick (Bit 7)**

PIR One-Second Timer Tick

Set by the application; cleared by the PIR Engine.

- This bit must be set to 1 one time per second by the user application to provide the Engine with a onesecond tick to perform housekeeping operations relating to motion detection. The Engine will routinely poll this bit to obtain a one-second tick. This bit is cleared by the Engine.

- 0 = Cleared by the PIR Engine.

- 1 = A one-second interval has occurred.

#### Frequency Response (Bits 6-3)

Frequency Response of PIR Engine; controlled by application

Frequency response: 0h-Fh

- This value determines the frequency response of the motion detection system. Higher values allow lower frequencies to be accepted by the PIR Engine. Lower values cause the Engine to ignore targets that generate lower frequencies. These targets typically include horizontally oriented objects such as pets.

- The frequency of the signal that is presented to the PIR Engine is largely dependent on the structure

of the PIR lens being used (number and dispersion of beams). A lens with several evenly distributed

beams provides better frequency response performance than a lens with an uneven beam

distribution.

Note: Lower programmed values also have the effect of reducing the relative range of detection.

#### PIR Scan Rate (Bit 2)

PIR ADC conversion rate for the Pyroelectric Sensor; controlled by the application.

- The PIR Engine performs the necessary ADC conversions on the PIR sensor input. Each conversion

generates an interrupt that is processed by the PIR Engine from the EPIR\_ADC\_ISR macro. The PIR

Scan Rate bit determines the rate at which the ADC conversions are generated.

- In Normal Scan Rate Mode (PIR Scan Rate set to 0), the Z8FS021 ADC peripheral is set to

continuous conversion mode which causes a conversion to be carried out automatically every 256

system clocks. In this mode, the application is only required to execute the EPIR\_ADC\_ISR macro

for each ADC interrupt. The ADC continually runs and continuously generates interrupts.

- When Low Scan Rate Mode is selected by setting this bit to a 1, continuous conversion mode is

disabled and the ADC is operated in single-shot mode such that each conversion takes 5129 system

clocks to complete. In this mode, the application software must initiate the ADC conversion request