# Z8S180/Z8L180

ENHANCED Z180 MICROPROCESSOR OFFERS FASTER EXECUTION, POWER-SAVER MODE, LOW EMI

#### **FEATURES**

- Code Compatible with ZiLOG Z80<sup>®</sup> CPU

- Extended Instructions

- Two Chain-Linked DMA Channels

- Low Power-Down Modes

- On-Chip Interrupt Controllers

- Three On-Chip Wait-State Generators

- On-Chip Oscillator/Generator

- Expanded MMU Addressing (Up to 1 MB)

- Clocked Serial I/O Port

- Two 16-Bit Counter/Timers

- Two Enhanced UARTs (up to 512 Kbps)

- Clock Speeds: 10, 20, 33 MHz

- Operating Range: 5V (3.3V@ 20 MHz)

- Operating Temperature Range: 0°C to +70°C

- -40°C to +85°C Extended Temperature Range

- Three Packaging Styles

- 68-Pin PLCC

- 64-Pin DIP

- 80-Pin QFP

#### **GENERAL DESCRIPTION**

The enhanced Z8S180/Z8L180<sup>TM</sup> significantly improves on previous Z80180 models, while still providing full backward compatibility with existing ZiLOG Z80 devices. The Z8S180/Z8L180 now offers faster execution speeds, power-saving modes, and EMI noise reduction.

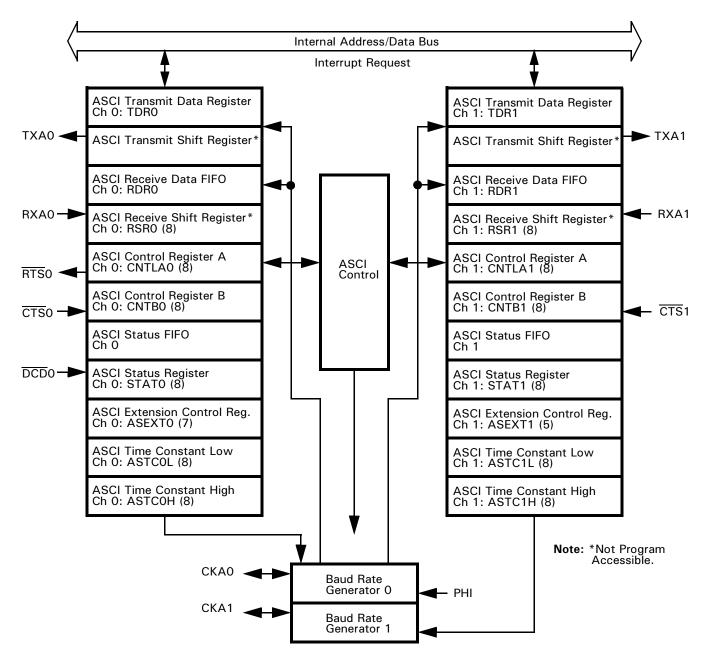

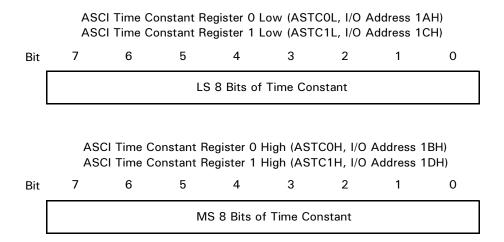

This enhanced Z180<sup>™</sup> design also incorporates additional feature enhancements to the ASCIs, DMAs, and STANDBY mode power consumption. With the addition of ESCC-like Baud Rate Generators (BRGs), the two ASCIs offer the flexibility and capability to transfer data asynchronously at rates of up to 512 Kbps. In addition, the ASCI receiver features a 4-byte first in/first out (FIFO) buffer which reduces the likelihood of overrun errors. The DMAs have been modified to allow for chain-linking of the two DMA channels when set to take their DMA requests from the same peripherals device. This feature allows for nonstop DMA operation between the two DMA channels.

Not only does the Z8S180/Z8L180 consume less power during normal operations than the previous model, it offers

three modes intended to further reduce power consumption. Power consumption during STANDBY Mode is reduced to  $10~\mu\text{A}$  by stopping the external oscillators and internal clock. The SLEEP mode reduces power by placing the CPU into a stopped state, consuming less current while the onchip I/O devices still operate. The SYSTEM STOP mode places both the CPU and the on-chip peripherals into a stopped mode, reducing power consumption even further.

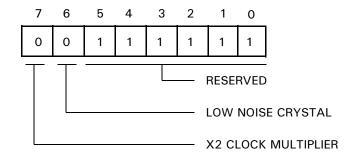

A new clock-doubler feature in the Z8S180/Z8L180 allows the internal clock speed to be twice the external clock speed. As a result, system cost is reduced by allowing the use of lower-cost, lower-frequency crystals.

The Enhanced Z180 is housed in 80-pin QFP, 68-pin PLCC, and 64-pin DIP packages.

**Note:** All Signals with an overline are active Low. For example:  $B/\overline{W}$ , in which WORD is active Low; or  $\overline{B}/W$ , in which BYTE is active Low.

DS006002-ZMP0200 1

#### **GENERAL DESCRIPTION** (Continued)

Power connections follow the conventional descriptions below:

| Connection | Circuit         | Device          |  |

|------------|-----------------|-----------------|--|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |  |

| Ground     | GND             | V <sub>SS</sub> |  |

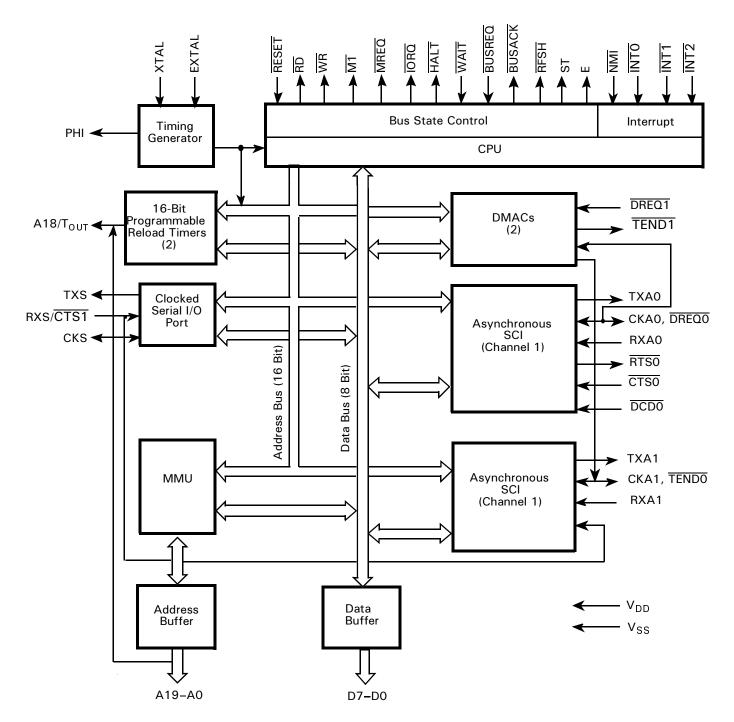

Figure 1. Z8S180/Z8L180 Functional Block Diagram

#### PIN IDENTIFICATION

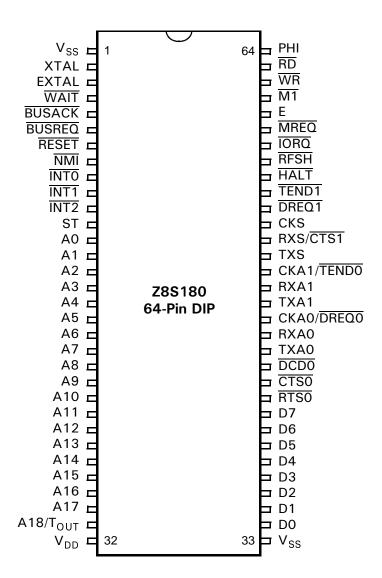

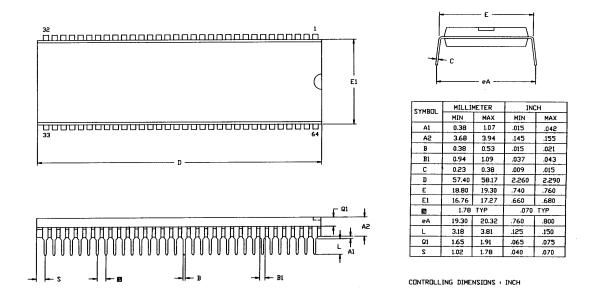

Figure 2. Z8S180 64-Pin DIP Pin Configuration

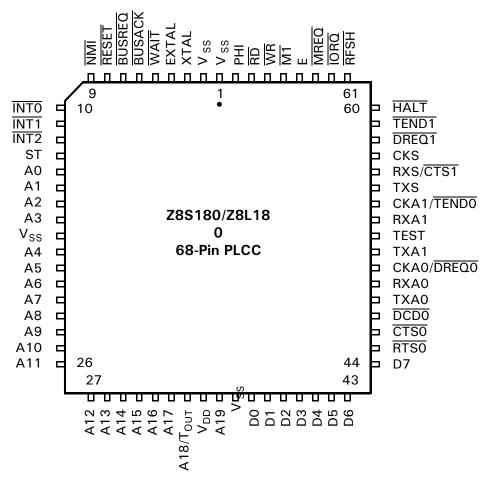

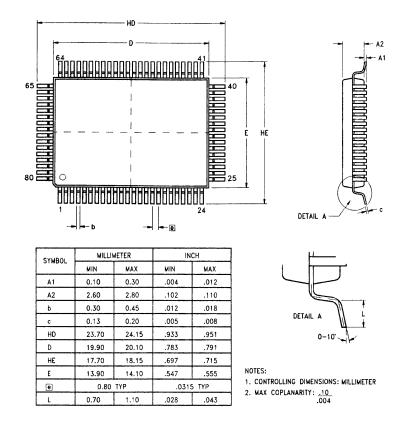

Figure 3. Z8S180/Z8L180 68-Pin PLCC Pin Configuration

5

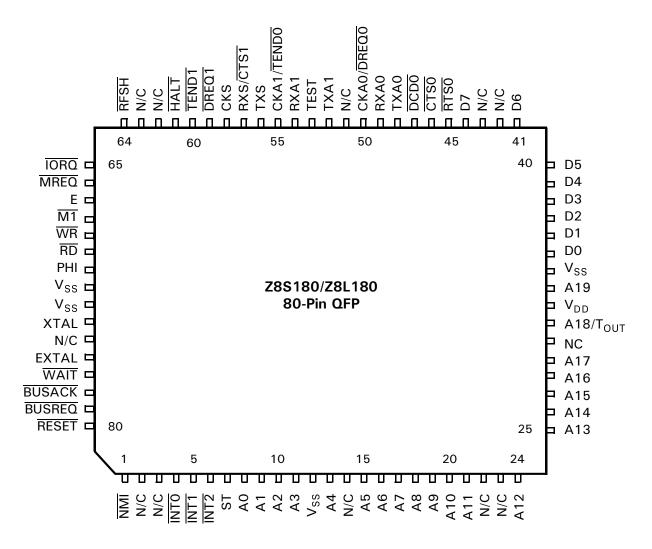

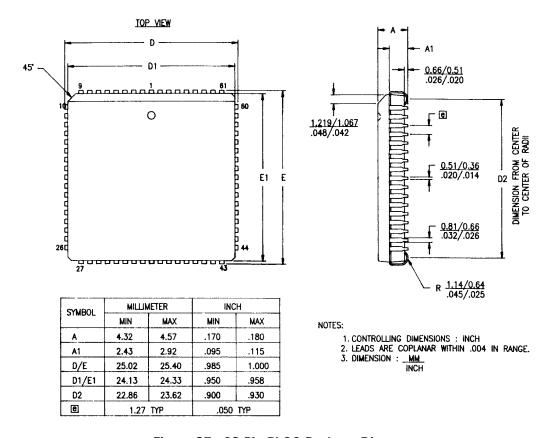

Figure 4. Z8S180/Z8L180 80-Pin QFP Pin Configuration

Table 1. Z8S180/Z8L180 Pin Identification

| Pin Num | ber and Packa | ge Type | Default  | Secondary |         |

|---------|---------------|---------|----------|-----------|---------|

| QFP     | PLCC          | DIP     | Function | Function  | Control |

| 1       | 9             | 8       | NMI      |           |         |

| 2       |               |         | NC       |           |         |

| 3       |               |         | NC       |           |         |

| 4       | 10            | 9       | ĪNT0     |           |         |

| 5       | 11            | 10      | ĪNT1     |           |         |

| 6       | 12            | 11      | ĪNT2     |           |         |

| 7       | 13            | 12      | ST       |           |         |

| 8       | 14            | 13      | Α0       |           |         |

| 9       | 15            | 14      | A1       |           |         |

| 10      | 16            | 15      | A2       |           |         |

| 11      | 17            | 16      | А3       |           |         |

| 12      | 18            |         | $V_{SS}$ |           |         |

Table 1. Z8S180/Z8L180 Pin Identification (Continued)

| Pin Numb | Pin Number and Package Type |     | Default         | Secondary        |                         |

|----------|-----------------------------|-----|-----------------|------------------|-------------------------|

| QFP      | PLCC                        | DIP | Function        | Function         | Control                 |

| 13       | 19                          | 17  | A4              |                  |                         |

| 14       |                             |     | NC              |                  |                         |

| 15       | 20                          | 18  | A5              |                  |                         |

| 16       | 21                          | 19  | A6              |                  |                         |

| 17       | 22                          | 20  | Α7              |                  |                         |

| 18       | 23                          | 21  | A8              |                  |                         |

| 19       | 24                          | 22  | A9              |                  |                         |

| 20       | 25                          | 23  | A10             |                  |                         |

| 21       | 26                          | 24  | A11             |                  |                         |

| 22       |                             |     | NC              |                  |                         |

| 23       |                             |     | NC              |                  |                         |

| 24       | 27                          | 25  | A12             |                  |                         |

| 25       | 28                          | 26  | A13             |                  |                         |

| 26       | 29                          | 27  | A14             |                  |                         |

| 27       | 30                          | 28  | A15             |                  |                         |

| 28       | 31                          | 29  | A16             |                  |                         |

| 29       | 32                          | 30  | A17             |                  |                         |

| 30       |                             |     | NC              |                  |                         |

| 31       | 33                          | 31  | A18             | T <sub>OUT</sub> | Bit 2 or Bit 3 of TCR   |

| 32       | 34                          | 32  | $V_{DD}$        |                  |                         |

| 33       | 35                          |     | A19             |                  |                         |

| 34       | 36                          | 33  | V <sub>SS</sub> |                  |                         |

| 35       | 37                          | 34  | D0              |                  |                         |

| 36       | 38                          | 35  | D1              |                  |                         |

| 37       | 39                          | 36  | D2              |                  |                         |

| 38       | 40                          | 37  | D3              |                  |                         |

| 39       | 41                          | 38  | D4              |                  |                         |

| 40       | 42                          | 39  | D5              |                  |                         |

| 41       | 43                          | 40  | D6              |                  |                         |

| 42       |                             |     | NC              |                  |                         |

| 43       |                             |     | NC              |                  |                         |

| 44       | 44                          | 41  | D7              |                  |                         |

| 45       | 45                          | 42  | RTS0            |                  |                         |

| 46       | 46                          | 43  | CTS0            |                  |                         |

| 47       | 47                          | 44  | DCD0            |                  |                         |

| 48       | 48                          | 45  | TXA0            |                  |                         |

| 49       | 49                          | 46  | RXA0            |                  |                         |

| 50       | 50                          | 47  | CKA0            | DREQ0            | Bit 3 or Bit 5 of DMODE |

| 51       |                             |     | NC              |                  |                         |

| 52       | 51                          | 48  | TXA1            |                  |                         |

Table 1. Z8S180/Z8L180 Pin Identification (Continued)

| Pin Num | ber and Packa | age Type | Default         | Secondary |                 |

|---------|---------------|----------|-----------------|-----------|-----------------|

| QFP     | PLCC          | DIP      | Function        | Function  | Control         |

| 53      | 52            |          | TEST            |           |                 |

| 54      | 53            | 49       | RXA1            |           |                 |

| 55      | 54            | 50       | CKA1            | TEND0     | Bit 4 of CNTLA1 |

| 56      | 55            | 51       | TXS             |           |                 |

| 57      | 56            | 52       | RXS             | CTS1      | Bit 2 of STAT1  |

| 58      | 57            | 53       | CKS             |           |                 |

| 59      | 58            | 54       | DREQ1           |           |                 |

| 60      | 59            | 55       | TEND1           |           |                 |

| 61      | 60            | 56       | HALT            |           |                 |

| 62      |               |          | NC              |           |                 |

| 63      |               |          | NC              |           |                 |

| 64      | 61            | 57       | RFSH            |           |                 |

| 65      | 62            | 58       | ĪORQ            |           |                 |

| 66      | 63            | 59       | MREQ            |           |                 |

| 67      | 64            | 60       | E               |           |                 |

| 68      | 65            | 61       | M1              |           |                 |

| 69      | 66            | 62       | WR              |           |                 |

| 70      | 67            | 63       | RD              |           |                 |

| 71      | 68            | 64       | PHI             |           |                 |

| 72      | 1             | 1        | $V_{SS}$        |           |                 |

| 73      | 2             |          | V <sub>SS</sub> |           |                 |

| 74      | 3             | 2        | XTAL            |           |                 |

| 75      |               |          | NC              |           |                 |

| 76      | 4             | 3        | EXTAL           |           |                 |

| 77      | 5             | 4        | WAIT            |           |                 |

| 78      | 6             | 5        | BUSACK          |           |                 |

| 79      | 7             | 6        | BUSREQ          |           |                 |

| 80      | 8             | 7        | RESET           |           |                 |

|         |               |          |                 |           |                 |

Table 2. Pin Status During RESET, BUSACK, and SLEEP Modes

| Pin Num  | ber and Packa | age Type |                     |                       |                 | Pin Status      |                 |

|----------|---------------|----------|---------------------|-----------------------|-----------------|-----------------|-----------------|

| QFP      | PLCC          | DIP      | Default<br>Function | Secondary<br>Function | RESET           | BUSACK          | SLEEP           |

|          |               |          | NMI                 | runction              |                 |                 |                 |

| 1        | 9             | 8        |                     |                       | IN              | IN              | IN              |

| 3        |               |          | NC                  |                       |                 |                 |                 |

|          | 10            | 9        | NC<br>INTO          |                       | INI             | INI             | INI             |

| 4        |               | 10       | INTO<br>INT1        |                       | IN              | IN              | IN              |

| 5        | 11<br>12      | 11       | INT 1               |                       | IN<br>IN        | IN<br>IN        | IN<br>IN        |

| 6<br>7   | 13            | 12       | ST                  |                       |                 |                 |                 |

|          | 14            |          |                     |                       | High            | High            | High            |

| 9        | 15            | 13<br>14 | A0                  |                       | 3T<br>3T        | 3T<br>3T        | High            |

| 10       | 16            | 15       | A1                  |                       | 3T              |                 | High            |

|          | 17            | 16       | A2<br>A3            |                       | 3T              | 3T<br>3T        | High            |

| 11       | 17            | 10       |                     |                       |                 |                 | High            |

|          |               | 47       | V <sub>SS</sub>     |                       | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> |

| 13       | 19            | 17       | A4                  |                       | 3T              | 3T              | High            |

| 14       | 00            | 40       | NC                  |                       | 0.7             | 0.7             |                 |

| 15       | 20            | 18       | A5                  |                       | 3T              | 3T              | High            |

| 16       | 21            | 19       | A6                  |                       | 3T              | 3T              | High            |

| 17       | 22            | 20       | A7                  |                       | 3T              | 3T              | High            |

| 18       | 23            | 21       | A8                  |                       | 3T              | 3T              | High            |

| 19       | 24            | 22       | A9                  |                       | 3T              | 3T              | High            |

| 20       | 25            | 23       | A10                 |                       | 3T              | 3T              | High            |

| 21       | 26            | 24       | A11                 |                       | 3T              | 3T              | High            |

| 22       |               |          | NC                  |                       |                 |                 |                 |

| 23       | 0.7           | 0.5      | NC<br>A 1 2         |                       | 0.7             | O.T.            | 11.1            |

| 24       | 27            | 25       | A12                 |                       | 3T              | 3T              | High            |

| 25       | 28            | 26       | A13                 |                       | 3T              | 3T              | High            |

| 26<br>27 | 29<br>30      | 27       | A14                 |                       | 3T<br>3T        | 3T              | High            |

| 28       | 30            | 28<br>29 | A15<br>A16          |                       | 31<br>3T        | 3T<br>3T        | High<br>High    |

| 29       | 31            | 30       | A16                 |                       | 31<br>3T        | 3T              | High            |

| 30       | ٥٧            | 30       | NC                  |                       | <b>ا</b> ا      | 31              | піуп            |

| 31       | 33            | 31       | A18                 |                       | 3T              | 3T              | High            |

| JI       | JJ            | JI       |                     |                       | N/A             | OUT             | OUT             |

| 22       | 2.4           | 20       | T <sub>OUT</sub>    |                       |                 |                 |                 |

| 32       | 34            | 32       | V <sub>DD</sub>     |                       | V <sub>DD</sub> | V <sub>DD</sub> | V <sub>DD</sub> |

| 33       | 35            |          | A19                 |                       | 3T              | 3T              | High            |

| 34       | 36            | 33       | V <sub>SS</sub>     |                       | $V_{SS}$        | V <sub>SS</sub> | V <sub>SS</sub> |

| 35       | 37            | 34       | D0                  |                       | 3T              | 3T              | 3T              |

| 36       | 38            | 35       | D1                  |                       | 3T              | 3T              | 3T              |

| 37       | 39            | 36       | D2                  |                       | 3T              | 3T              | 3T              |

| 38       | 40            | 37       | D3                  |                       | 3T              | 3T              | 3T              |

Table 2. Pin Status During RESET, BUSACK, and SLEEP Modes (Continued)

| Pin Num | ber and Packa | age Type     | Pin Status          |                       |       |        |       |

|---------|---------------|--------------|---------------------|-----------------------|-------|--------|-------|

| QFP     | PLCC          | DIP          | Default<br>Function | Secondary<br>Function | RESET | BUSACK | SLEEF |

| 39      | 41            | 38           | D4                  |                       | 3T    | 3T     | 3T    |

| 40      | 42            | 39           | D5                  |                       | 3T    | 3T     | 3T    |

| 41      | 43            | 40           | D6                  |                       | 3T    | 3T     | 3T    |

| 42      |               |              | NC                  |                       |       |        |       |

| 43      |               |              | NC                  |                       |       |        |       |

| 44      | 44            | 41           | D7                  |                       | 3T    | 3T     | 3T    |

| 45      | 45            | 42           | RTS0                |                       | High  | OUT    | High  |

| 46      | 46            | 43           | CTS0                |                       | IN    | OUT    | IN    |

| 47      | 47            | 44           | DCD0                |                       | IN    | IN     | IN    |

| 48      | 48            | 45           | TXA0                |                       | High  | OUT    | OUT   |

| 49      | 49            | 46           | RXA0                |                       | IN    | IN     | IN    |

| 50      | 50            | 47           | CKA0                |                       | 3T    | I/O    | I/O   |

|         |               |              | DREQ0               |                       | N/A   | IN     | IN    |

| 51      |               |              | NC                  |                       |       |        |       |

| 52      | 51            | 48           | TXA1                |                       | High  | OUT    | OUT   |

| 53      | 52            |              | TEST                |                       |       |        |       |

| 54      | 53            | 49           | RXA1                |                       | IN    | IN     | IN    |

| 55      | 54            | 50           | CKA1                |                       | 3T    | I/O    | I/O   |

|         |               |              | TEND0               |                       | N/A   | High   | High  |

| 56      | 55            | 51           | TXS                 |                       | High  | OUT    | OUT   |

| 57      | 56            | 52           | RXS                 |                       | IN    | IN     | IN    |

|         |               |              | CTS1                |                       | N/A   | IN     | IN    |

| 58      | 57            | 53           | CKS                 |                       | 3T    | I/O    | I/O   |

| 59      | 58            | 54           | DREQ1               |                       | IN    | 3T     | IN    |

| 60      | 59            | 55           | TEND1               |                       | High  | OUT    | High  |

| 61      | 60            | 56           | HALT                |                       | High  | High   | Low   |

| 62      |               |              | NC                  |                       |       |        |       |

| 63      |               |              | NC                  |                       |       |        |       |

| 64      | 61            | 57           | RFSH                |                       | High  | OUT    | High  |

| 65      | 62            | 58           | ĪORQ                |                       | High  | 3T     | High  |

| 66      | 63            | 59           | MREQ                |                       | High  | 3T     | High  |

| 67      | 64            | 60           | Е                   |                       | Low   | OUT    | OUT   |

| 68      | 65            | 61           | M1                  |                       | High  | High   | High  |

| 69      | 66            | 62           | WR                  |                       | High  | 3T     | High  |

| 70      | 67            | 63           | RD                  |                       | High  | 3T     | High  |

| 71      | 68            | 64           | PHI                 |                       | OUT   | OUT    | OUT   |

| 72      | 1             | 1            | V <sub>SS</sub>     |                       | GND   | GND    | GND   |

| 73      | 2             |              | V <sub>SS</sub>     |                       | GND   | GND    | GND   |

| 74      | 3             | 2            | XTAL                |                       | OUT   | OUT    | OUT   |

| 75      | <del>-</del>  | <del>-</del> | NC                  |                       |       |        |       |

Table 2. Pin Status During RESET, BUSACK, and SLEEP Modes (Continued)

| Pin Num | ber and Packa | ige Type | Pin Status          |                       |       |        |       |

|---------|---------------|----------|---------------------|-----------------------|-------|--------|-------|

| QFP     | PLCC          | DIP      | Default<br>Function | Secondary<br>Function | RESET | BUSACK | SLEEP |

| 76      | 4             | 3        | EXTAL               |                       | IN    | IN     | IN    |

| 77      | 5             | 4        | WAIT                |                       | IN    | IN     | IN    |

| 78      | 6             | 5        | BUSACK              |                       | High  | OUT    | OUT   |

| 79      | 7             | 6        | BUSREQ              |                       | IN    | IN     | IN    |

| 80      | 8             | 7        | RESET               |                       | IN    | IN     | IN    |

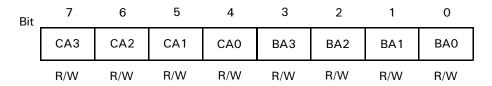

#### PIN DESCRIPTIONS

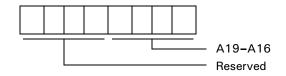

**A0–A19** Address Bus (Output, 3-state). A0–A19 form a 20-bit address bus. The Address Bus provides the address for memory data bus exchanges (up to 1 MB) and I/O data bus exchanges (up to 64 KB). The address bus enters a high–impedance state during reset and external bus acknowledge cycles. Address line A18 is multiplexed with the output of PRT channel 1 (T<sub>OUT</sub>, selected as address output on reset), and address line A19 is not available in DIP versions of the Z8S180.

**BUSACK**. Bus Acknowledge (Output, active Low). BUSACK indicates that the requesting device, the MPU address and data bus, and some control signals enter their high-impedance state.

**BUSREQ.** Bus Request (Input, active Low). This input is used by external devices (such as DMA controllers) to request access to the system bus. This request demands a higher priority than  $\overline{\text{NMI}}$  and is always recognized at the end of the current machine cycle. This signal stops the CPU from executing further instructions, places addresses, data buses, and other control signals into the high-impedance state.

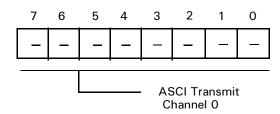

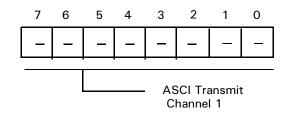

**CKAO**, **CKA1**. Asynchronous Clock 0 and 1 (bidirectional). When in output mode, these pins are the transmit and receive clock outputs from the ASCI baud rate generators. When in input mode, these pins serve as the external clock inputs for the ASCI baud rate generators. CKAO is multiplexed with  $\overline{\text{DREQO}}$ , and CKA1 is multiplexed with  $\overline{\text{TENDO}}$ .

**CKS.** Serial Clock (bidirectional). This line is the clock for the CSI/O channel.

**CTS0**-**CTS1**. Clear to send 0 and 1 (Inputs, active Low). These lines are modem control signals for the ASCI channels. CTS1 is multiplexed with RXS.

**D0–D7.** Data Bus = (bidirectional, 3-state). D0–D7 constitute an 8-bit bidirectional data bus, used for the transfer of information to and from I/O and memory devices. The data bus enters the high-impedance state during reset and external bus acknowledge cycles.

**DCDO.** Data Carrier Detect 0 (Input, active Low); a programmable modem control signal for ASCI channel 0.

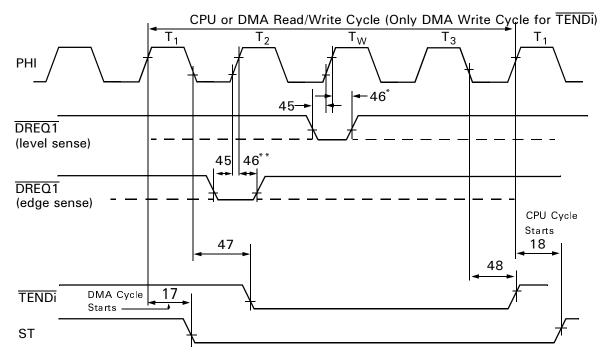

DREQO, DREQT. DMA Request 0 and 1 (Input, active Low). DREQ is used to request a DMA transfer from one of the on-chip DMA channels. The DMA channels monitor these inputs to determine when an external device is ready for a READ or WRITE operation. These inputs can be programmed to be either level or edge sensed. DREQO is multiplexed with CKAO.

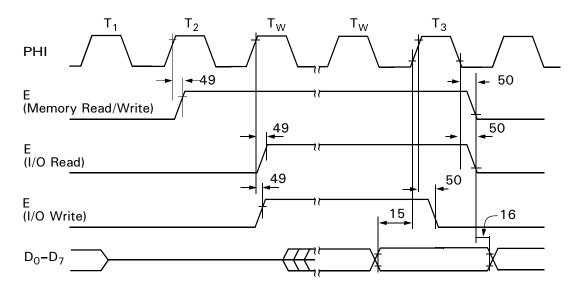

**E.** Enable Clock (Output). This pin functions as a synchronous, machine-cycle clock output during bus transactions.

**EXTAL.** External Clock Crystal (Input). Crystal oscillator connections. An external clock can be input to the Z8S180/Z8L180 on this pin when a crystal is not used. This input is Schmitt triggered.

HALT. HALT/SLEEP (Output, active Low). This output is asserted after the CPU executes either the HALT or SLEEP instruction and is waiting for either a nonmaskable or a maskable interrupt before operation can resume. It is also used with the M1 and ST signals to decode the status of the CPU machine cycle.

**INTO.** Maskable Interrupt Request 0 (Input, active Low). This signal is generated by external I/O devices. The CPU honors these requests at the end of the current instruction cycle as long as the NMI and BUSREQ signals are inactive. The CPU acknowledges this interrupt request with an interrupt acknowledge cycle. During this cycle, both the M1 and  $\overline{IORQ}$  signals become active.

**INT1**, **INT2**. Maskable Interrupt Request 1 and 2 (Inputs, active Low). This signal is generated by external I/O devices. The CPU honors these requests at the end of the current instruction cycle as long as the NMI, BUSREQ, and INTO signals are inactive. The CPU acknowledges these requests with an interrupt acknowledge cycle. Unlike the acknowledgment for INTO, neither the MT or IORQ signals become active during this cycle.

$\overline{\text{IORQ}}$ . I/O Request (Output, active Low, 3-state).  $\overline{\text{IORQ}}$  indicates that the address bus contains a valid I/O address for an I/O READ or I/O WRITE operation.  $\overline{\text{IORQ}}$  is also generated, along with  $\overline{\text{M1}}$ , during the acknowledgment of the  $\overline{\text{INTO}}$  input signal to indicate that an interrupt response vector can be place onto the data bus. This signal is analogous to the  $\overline{\text{IOE}}$  signal of the Z64180.

M1. Machine Cycle 1 (Output, active Low). Together with MREQ, M1 indicates that the current cycle is the opcodefetch cycle of instruction execution. Together with IORQ, M1 indicates that the current cycle is for interrupt acknowledgment. It is also used with the HALT and ST signal to decode the status of the CPU machine cycle. This signal is analogous to the LIR signal of the Z64180.

MREQ. Memory Request (Output, active Low, 3-state). MREQ indicates that the address bus holds a valid address for a memory READ or memory WRITE operation. This signal is analogous to the ME signal of Z64180.

**NMI.** Nonmaskable Interrupt (Input, negative edge triggered). NMI demands a higher priority than INT and is al-

#### PIN DESCRIPTIONS (Continued)

ways recognized at the end of an instruction, regardless of the state of the interrupt-enable flip-flops. This signal forces CPU execution to continue at location 0066H.

**PHI.** System Clock (Output). The output is used as a reference clock for the MPU and the external system. The frequency of this output may be one-half, equal to, or twice the crystal or input clock frequency.

RD. Read (Output, active Low, 3-state). RD indicates that the CPU wants to read data from either memory or an I/O device. The addressed I/O or memory device should use this signal to gate data onto the CPU data bus.

RFSH. Refresh (Output, active Low). Together with MREQ, RFSH indicates that the current CPU machine cycle and the contents of the address bus should be used for refresh of dynamic memories. The low-order 8 bits of the address bus (A7–A0) contain the refresh address. *This signal is analogous to the REF signal of the Z64180*.

**RTSO**. Request to Send 0 (Output, active Low); a programmable MODEM control signal for ASCI channel 0.

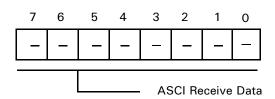

**RXA0**, **RXA1**. Receive Data 0 and 1 (Input). These signals are the receive data for the ASCI channels.

**RXS.** Clocked Serial Receive Data (Input). This line is the receive data for the CSI/O channel. RXS is multiplexed with the CTS1 signal for ASCI channel 1.

**ST.** Status (Output). This signal is used with the  $\overline{M1}$  and  $\overline{HALT}$  output to decode the status of the CPU machine cycle. See Table 3.

Table 3. Status Summary

| ST | HALT | M1 | Operation                                       |

|----|------|----|-------------------------------------------------|

| 0  | 1    | 0  | CPU Operation (1st Opcode Fetch)                |

| 1  | 1    | 0  | CPU Operation (2nd Opcode and 3rd Opcode Fetch) |

| 1  | 1    | 1  | CPU Operation (MC Except Opcode Fetch)          |

| 0  | Χ    | 1  | DMA Operation                                   |

| 0  | 0    | 0  | HALT Mode                                       |

| 1  | 0    | 1  | SLEEP Mode (Including SYSTEM STOP Mode)         |

Notes:

X = Do not care.

MC = Machine Cycle.

**TENDO**, **TEND1**. Transfer End 0 and 1 (Outputs, active Low). This output is asserted active during the most recent WRITE cycle of a DMA operation. It is used to indicate the end of the block transfer. **TENDO** is multiplexed with CKA1.

**TEST.** Test (Output, not in DIP version). This pin is for test and should be left open.

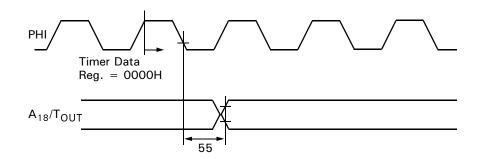

$T_{OUT}$ . Timer Out (Output).  $T_{OUT}$  is the output from PRT channel 1. This line is multiplexed with A18 of the address bus.

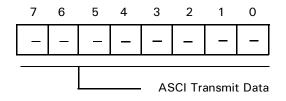

**TXA0.** TXA1. Transmit Data 0 and 1 (Outputs). These signals are the transmitted data from the ASCI channels. Transmitted data changes are with respect to the falling edge of the transmit clock.

**TXS.** Clocked Serial Transmit Data (Output). This line is the transmitted data from the CSI/O channel.

WAIT. Wait (Input, active Low). WAIT indicates to the MPU that the addressed memory or I/O devices are not ready for data transfer. This input is sampled on the falling edge of T2 (and subsequent WAIT states). If the input is sampled Low, then the additional WAIT states are inserted until the WAIT input is sampled High, at which time execution continues.

WR. WRITE (Output, active Low, 3-state). WR indicates that the CPU data bus holds valid data to be stored at the addressed I/O or memory location.

**XTAL.** Crystal Oscillator Connection (Input). This pin should be left open if an external clock is used instead of a crystal. The oscillator input is not a TTL level (see <u>DC Characteristics</u>).

Several pins are used for different conditions, depending on the circumstance.

|            | Table 4. Multiplexed Pin Descriptions                                                                                                                                                                                                         |  |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| A18/TOUT   | During RESET, this pin is initialized as A18. If either the TOC1 or the TOC0 bit of the Timer Control register (TCR) is set to 1, the T <sub>OUT</sub> function is selected. If TOC1 and TOC0 are cleared to 0, the A18 function is selected. |  |  |  |  |  |  |

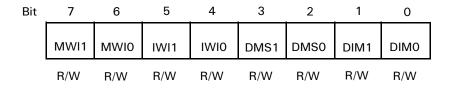

| CKA0/DREQ0 | During RESET, this pin is initialized as CKAO. If either DM1 or SM1 in the DMA Mode register (DMODE) is set to 1, the DREQO function is selected.                                                                                             |  |  |  |  |  |  |

| CKA1/TENDO | During RESET, this pin is initialized as CKA1. If the CKA1D bit in ASCI control register ch1 (CNTLA1) is set to 1, the $\overline{\text{TENDO}}$ function is selected. If the CKA1D bit is set to 0, the CKA1 function is selected.           |  |  |  |  |  |  |

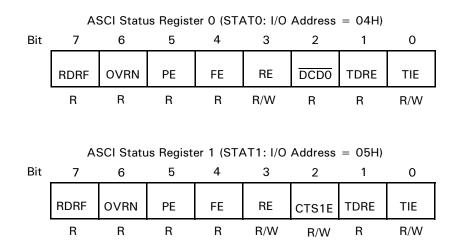

| RXS/CTS1   | During RESET, this pin is initialized as RXS. If the CTS1E bit in the ASCI status register ch1 (STAT1) is set to 1, the $\overline{\text{CTS1}}$ function is selected. If the CTS1E bit is set to 0, the RXS function is selected.            |  |  |  |  |  |  |

#### **ARCHITECTURE**

The Z180 combines a high-performance CPU core with a variety of system and I/O resources useful in a broad range of applications. The CPU core consists of five functional blocks: clock generator, bus state controller, Interrupt controller, memory management unit (MMU), and the central processing unit (CPU). The integrated I/O resources make up the remaining four functional blocks: direct memory access (DMA) control (2 channels), asynchronous serial communication interface (ASCI, 2 channels) programmable reload timers (PRT, 2 channels), and a clock serial I/O (CSI/O) channel.

**Clock Generator.** This logic generates a system clock from an external crystal or clock input. The external clock is divided by 2 or 1 and provides the timing for both internal and external devices.

**Bus State Controller.** This logic performs all of the status and bus-control activity associated with the CPU and some on-chip peripherals. Also includes wait-state timing, reset cycles, DRAM refresh, and DMA bus exchanges.

**Interrupt Controller.** This logic monitors and prioritizes the variety of internal and external interrupts and traps to provide the correct responses from the CPU. To maintain compatibility with the Z80 CPU, three different interrupts modes are supported.

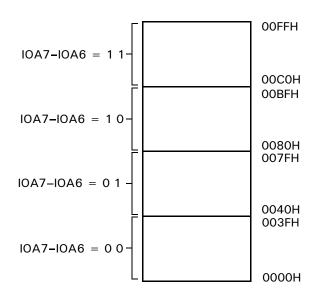

Memory Management Unit. The MMU allows the user to map the memory used by the CPU (logically only 64KB) into the 1-MB addressing range supported by the Z8S180/Z8L180. The organization of the MMU object

code maintains compatibility with the Z80 CPU, while offering access to an extended memory space. Accomplished by using an effective common-area/banked-area scheme.

Central Processing Unit. The CPU is microcoded to provide a core that is object-code compatible with the Z80 CPU. It also provides a superset of the Z80 instruction set, including 8-bit multiplication. The core is modified to allow many of the instructions to execute in fewer clock cycles.

**DMA Controller.** The DMA controller provides high-speed transfers between memory and I/O devices. Transfer operations supported are memory-to-memory, memory to/from I/O, and I/O-to-I/O. Transfer modes supported are request, burst, and cycle steal. DMA transfers can access the full 1-MB address range with a block length up to 64 KB, and can cross over 64K boundaries.

#### Asynchronous Serial Communication Interface (ASCI).

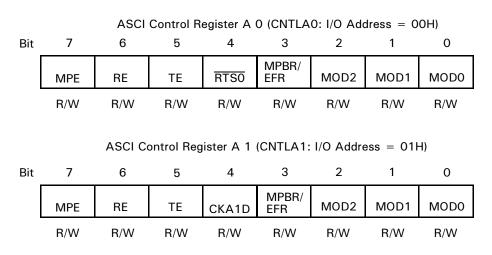

The ASCI logic provides two individual full-duplex UARTs. Each channel includes a programmable baud rate generator and modem control signals. The ASCI channels can also support a multiprocessor communication format as well as break detection and generation

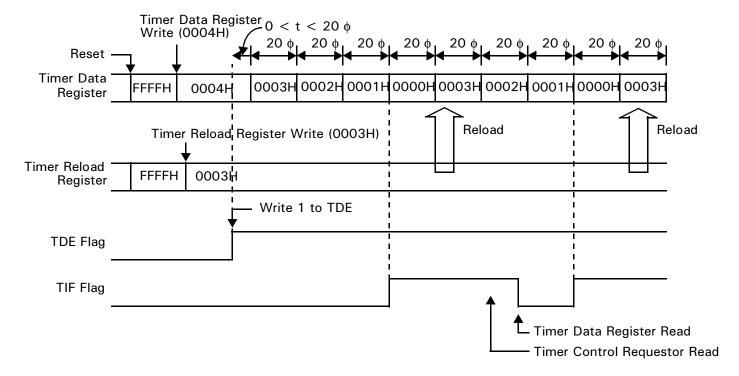

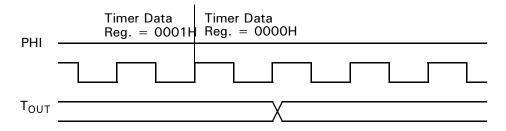

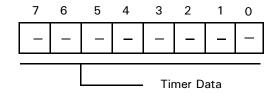

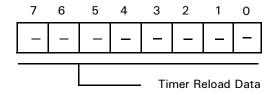

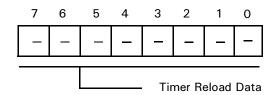

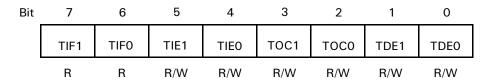

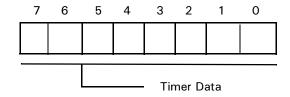

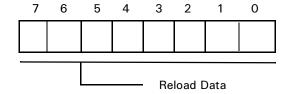

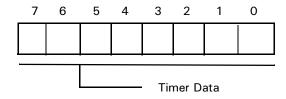

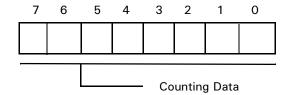

Programmable Reload Timers (PRT). This logic consists of two separate channels, each containing a 16-bit counter (timer) and count reload register. The time base for the counters is derived from the system clock (divided by 20) before reaching the counter. PRT channel 1 provides an optional output to allow for waveform generation.

Figure 5. Timer Initialization, Count Down, and Reload Timing

Figure 6. Timer Output Timing

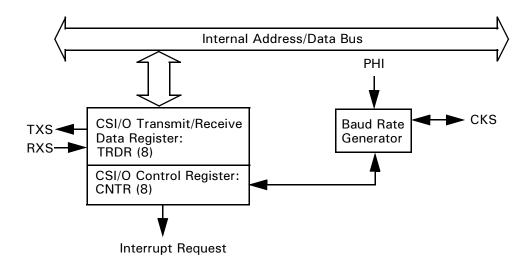

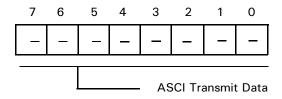

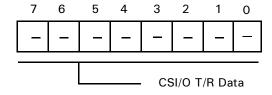

Clocked Serial I/O (CSI/O). The CSI/O channel provides a half-duplex serial transmitter and receiver. This channel can be used for simple high-speed data connection to another microprocessor or microcomputer. TRDR is used for both CSI/O transmission and reception. Thus, the system design must ensure that the constraints of half-duplex operation are met (Transmit and Receive operation cannot occur simultaneously). For example, if a CSI/O transmission is attempted while the CSI/O is receiving data, a CSI/O does not work.

**Note:** TRDR is not buffered. Performing a CSI/O transmit while the previous transmission is still in progress causes the data to be immediately updated and corrupts the transmit operation. Similarly, reading TRDR while a transmit or receive is in progress should be avoided.

### **ARCHITECTURE** (Continued)

Figure 7. CSI/O Block Diagram

#### **OPERATION MODES**

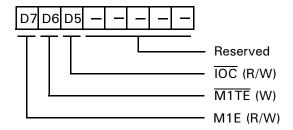

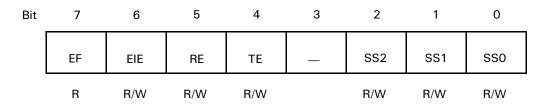

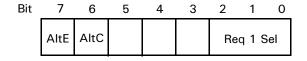

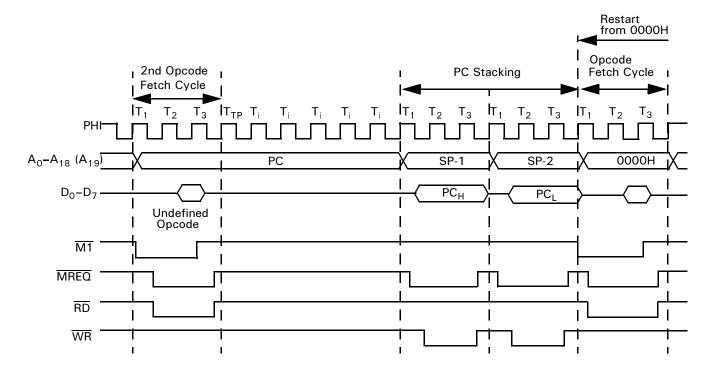

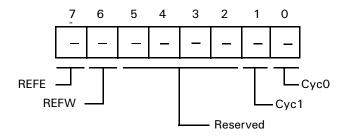

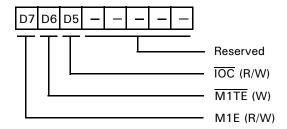

**Z80** versus **64180** Compatibility. The Z8S180/Z8L180 is descended from two different "ancestor" processors, ZiLOG's original Z80 and the Hitachi 64180. The Operating Mode Control Register (OMCR), illustrated in Figure 8, can be programmed to select between certain Z80 and 64180 differences.

Figure 8. Operating Control Register (OMCR: I/O Address = 3EH)

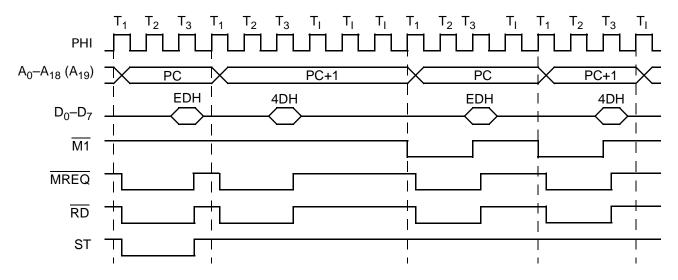

M1E ( $\overline{M1}$  Enable). This bit controls the  $\overline{M1}$  output and is set to a 1 during RESET.

When M1E = 1, the  $\overline{\text{M1}}$  output is asserted Low during opcode fetch cycles, Interrupt Acknowledge cycles, and the first machine cycle of an  $\overline{\text{NMI}}$  acknowledge.

On the Z8S180/Z8L180, this choice makes the processor fetch a RETI instruction one time. When fetching a RETI from a zero-wait-state memory location, the processor uses three clock bus cycles. These bus cycles are not fully Z80-timing compatible.

When M1E = 0, the processor does not drive  $\overline{\text{M1}}$  Low during the instruction fetch cycles. After fetching a RETI instruction with normal timing, the processor goes back and refetches the instruction using fully Z80-compatible cycles that include driving  $\overline{\text{M1}}$  Low. This option may be required by some external Z80 peripherals to properly decode the RETI instruction. Figure 9 and Table 5 show the RETI sequence when M1E is 0.

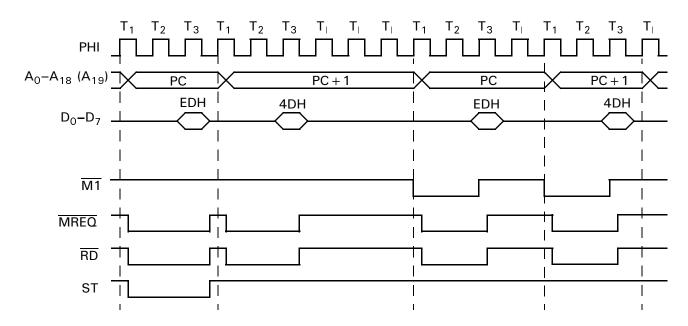

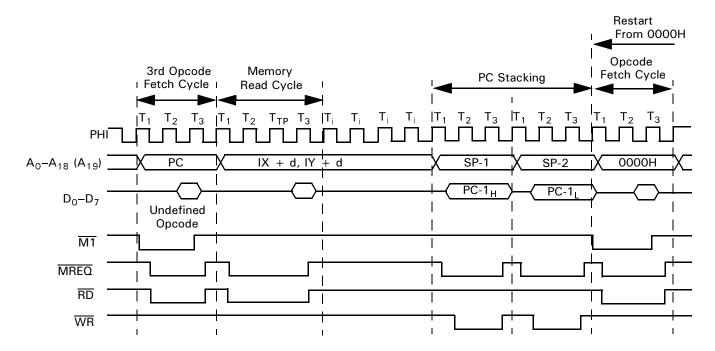

Figure 9. RETI Instruction Sequence with M1E = 0

#### **OPERATION MODES** (Continued)

| Table 5. RETI Control S | Signal | States |

|-------------------------|--------|--------|

|-------------------------|--------|--------|

| Machine<br>Cycle | States | Address    | Data    | RD | WR | MREQ | ĪΟRQ | M1<br>M1E=<br>1 | M1<br>M1E =<br>0 | HALT | ST |

|------------------|--------|------------|---------|----|----|------|------|-----------------|------------------|------|----|

| 1                | T1-T3  | 1st Opcode | EDH     | 0  | 1  | 0    | 1    | 0               | 1                | 1    | 0  |

| 2                | T1-T3  | 2nd Opcode | 4DH     | 0  | 1  | 0    | 1    | 0               | 1                | 1    | 0  |

|                  | Ti     | NA         | 3-state | 1  | 1  | 1    | 1    | 1               | 1                | 1    | 1  |

|                  | Ti     | NA         | 3-state | 1  | 1  | 1    | 1    | 1               | 1                | 1    | 1  |

|                  | Ti     | NA         | 3-state | 1  | 1  | 1    | 1    | 1               | 1                | 1    | 1  |

| 3                | T1-T3  | 1st Opcode | EDH     | 0  | 1  | 0    | 1    | 0               | 0                | 1    | 1  |

|                  | Ti     | NA         | 3-state | 1  | 1  | 1    | 1    | 1               | 1                | 1    | 1  |

| 4                | T1-T3  | 2nd Opcode | 4DH     | 0  | 1  | 0    | 1    | 0               | 1                | 1    | 1  |

| 5                | T1-T3  | SP         | Data    | 0  | 1  | 0    | 1    | 1               | 1                | 1    | 1  |

| 6                | T1-T3  | SP + 1     | Data    | 0  | 1  | 0    | 1    | 1               | 1                | 1    | 1  |

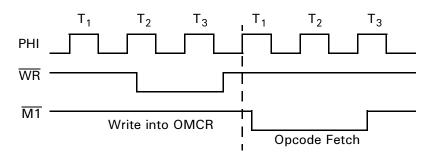

$\overline{\text{M1TE}}$  ( $\overline{\text{M1}}$  Temporary Enable). This bit controls the temporary assertion of the  $\overline{\text{M1}}$  signal. It is always read back as a 1 and is set to 1 during RESET.

When M1E is set to 0 to accommodate certain external Z80 peripheral(s), those same device(s) may require a pulse on M1 after programming certain of their registers to complete the function being programmed.

For example, when a control word is written to the Z80 PIO to enable interrupts, no enable actually takes place until the PIO sees an active  $\overline{\text{M1}}$  signal. When  $\overline{\text{M1TE}} = 1$ , there is no change in the operation of the  $\overline{\text{M1}}$  signal, and M1E controls its function. When  $\overline{\text{M1TE}} = 0$ , the  $\overline{\text{M1}}$  output is asserted during the next opcode fetch cycle regardless of the state programmed into the M1E bit. This condition is only momentary (one time) and it is not necessary to preprogram a 1 to disable the function (see Figure 10).

Figure 10. M1 Temporary Enable Timing

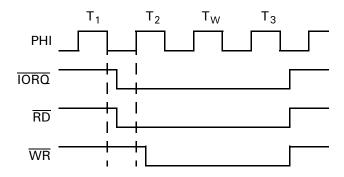

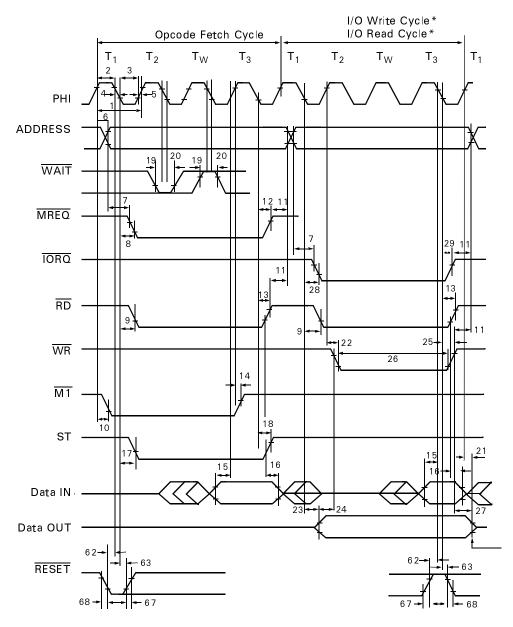

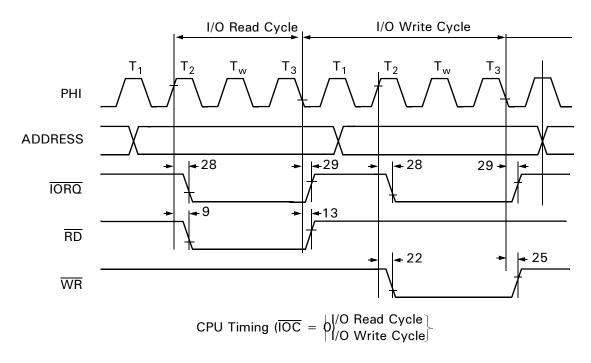

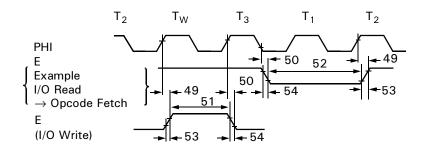

IOC (I/O Compatibility). This bit controls the timing of the  $\overline{\text{IORO}}$  and  $\overline{\text{RD}}$  signals. The bit is set to 1 by RESET.

When  $\overline{\mathsf{IOC}} = 1$ , the  $\overline{\mathsf{IORQ}}$  and  $\overline{\mathsf{RD}}$  signals function the same as the Z64180 (Figure 11).

Figure 11. I/O Read and Write Cycles with  $\overline{IOC} = 1$

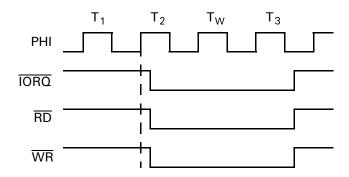

When  $\overline{\text{IOC}} = 0$ , the timing of the  $\overline{\text{IORQ}}$  and  $\overline{\text{RD}}$  signals match the timing of the Z80. The  $\overline{\text{IORQ}}$  and  $\overline{\text{RD}}$  signals go active as a result of the rising edge of T2. (Figure 12.)

Figure 12. I/O Read and Write Cycles with  $\overline{IOC} = 0$

#### **HALT and Low-Power Operating Modes.** The

Z8S180/Z8L180 can operate in seven modes with respect to activity and power consumption:

- Normal Operation

- HALT Mode

- IOSTOP Mode

- SLEEP Mode

- SYSTEM STOP Mode

- IDLE Mode

- STANDBY Mode (with or without QUICK RECOVERY)

**Normal Operation.** In this state, the Z8S180/Z8L180 processor is fetching and running a program. All enabled functions and portions of the device are active, and the HALT pin is High.

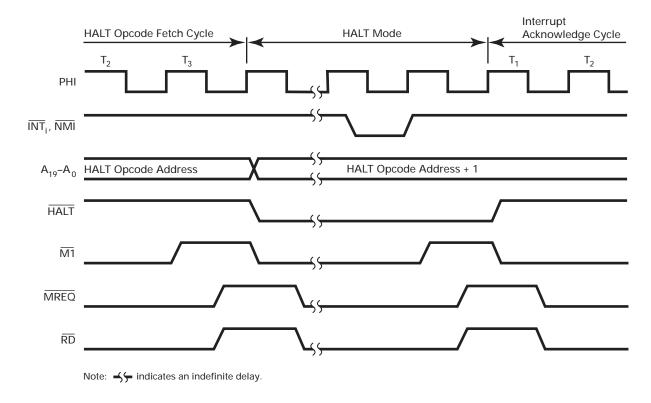

**HALT Mode.** This mode is entered by the HALT instruction. Thereafter, the Z8S180/Z8L180 processor continually fetches the following opcode but does not execute it and drives the  $\overline{\text{HALT}}$ , ST and  $\overline{\text{M1}}$  pins all Low. The oscillator and PHI pin remain Active. Interrupts and bus granting to external Masters, and DRAM refresh can occur, and all onchip I/O devices continue to operate including the DMA channels.

#### **OPERATION MODES** (Continued)

The Z8S180/Z8L180 leaves HALT mode in response to:

- Low on RESET

- Interrupt from an enabled on-chip source

- External request on NMI

- Enabled external request on INTO, INT1, or INT2

In case of an interrupt, the return address is the instruction following the HALT instruction. The program can either branch back to the HALT instruction to wait for another interrupt or can examine the new state of the system/application and respond appropriately.

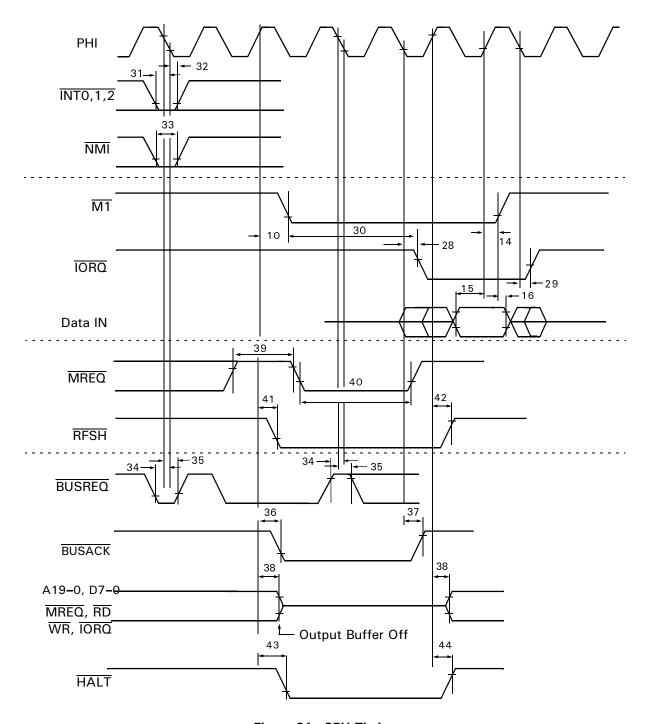

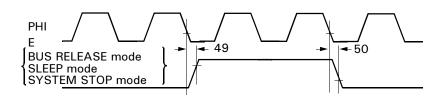

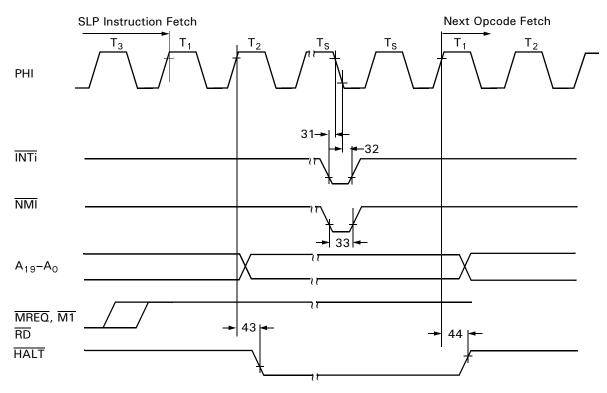

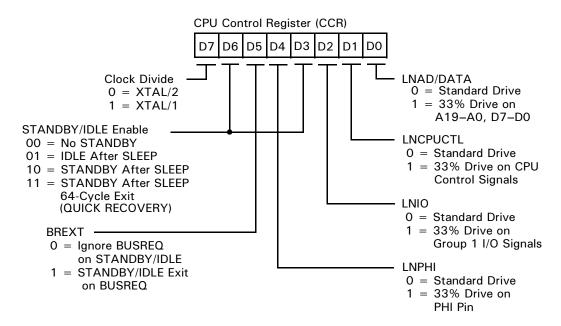

Figure 13. HALT Timing

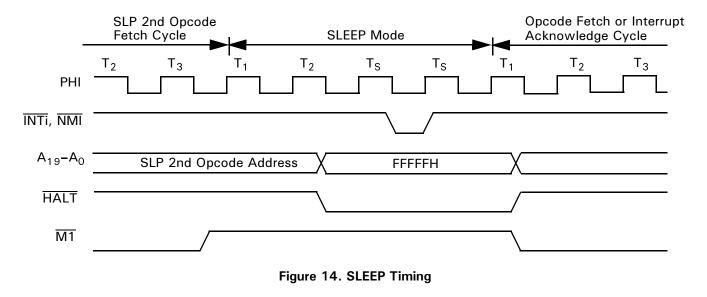

SLEEP Mode. This mode is entered by keeping the IOSTOP bit (ICR5) and bits 3 and 6 of the CPU Control Register (CCR3, CCR6) all zero and executing the SLP instruction. The oscillator and PHI output continue operating, but are blocked from the CPU core and DMA channels to reduce power consumption. DRAM refresh stops, but interrupts and granting to an external Master can occur. Except when the bus is granted to an external Master, A19–0 and all control signals except HALT are maintained High. HALT is Low. I/O operations continue as before the SLP instruction, except for the DMA channels.

The Z8S180/Z8L180 leaves SLEEP mode in response to a Low on RESET, an interrupt request from an on-chip source,

an external request on  $\overline{\text{NMI}}$ , or an external request on  $\overline{\text{INTO}}$ ,  $\overline{\text{INT1}}$ , or  $\overline{\text{INT2}}$ .

If an interrupt source is individually disabled, it cannot bring the Z8S180/Z8L180 out of SLEEP mode. If an interrupt source is individually enabled, and the IEF bit is 1 so that interrupts are globally enabled (by an EI instruction), the highest priority active interrupt occurs with the return address being the instruction after the SLP instruction. If an interrupt source is individually enabled, but the IEF bit is 0 so that interrupts are globally disabled (by a DI instruction), the Z8S180/Z8L180 leaves SLEEP mode by simply executing the following instruction(s).

This condition provides a technique for synchronization with high-speed external events without incurring the latency imposed by an interrupt-response sequence. Figure 14 depicts the timing for exiting SLEEP mode due to an interrupt request.

**Note:** The Z8S180/Z8L180 takes about 1.5 clock ticks to restart.

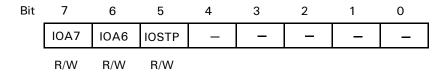

**IOSTOP Mode.** IOSTOP mode is entered by setting the IOSTOP bit of the I/O Control Register (ICR) to 1. In this case, on-chip I/O (ASCI, CSI/O, PRT) stops operating. However, the CPU continues to operate. Recovery from IOSTOP mode is performed by resetting the IOSTOP bit in ICR to 0.

**SYSTEM STOP Mode.** SYSTEM STOP mode is the combination of SLEEP and IOSTOP modes. SYSTEM STOP mode is entered by setting the IOSTOP bit in ICR to 1 followed by execution of the SLP instruction. In this mode, onchip I/O and CPU stop operating, reducing power consumption, but the PHI output continues to operate. Recovery from SYSTEM STOP mode is the same as recovery from SLEEP mode except that internal I/O sources (disabled by IOSTOP) cannot generate a recovery interrupt.

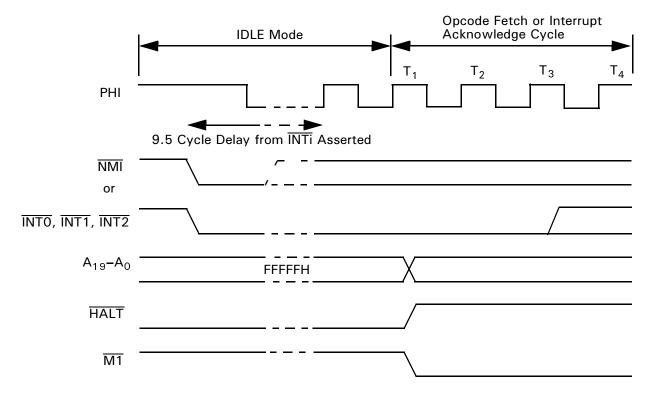

**IDLE Mode.** Software puts the Z8S180/Z8L180 into this mode by performing the following actions:

- Set the IOSTOP bit (ICR5) to 1

- Set CCR6 to 0

- Set CCR3 to 1

- Execute the SLP instruction

The oscillator keeps operating but its output is blocked to all circuitry including the PHI pin. DRAM refresh and all

internal devices stop, but external interrupts can occur. Bus granting to external Masters can occur if the BREST bit in the CPU control Register (CCR5) was set to 1 before IDLE mode was entered.

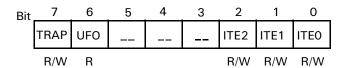

The Z8S180/Z8L180 leaves IDLE mode in response to a Low on  $\overline{\text{RESET}}$ , an external interrupt request on  $\overline{\text{NMI}}$ , or an external interrupt request on  $\overline{\text{INT0}}$ ,  $\overline{\text{INT1}}$  or  $\overline{\text{INT2}}$  that is enabled in the INT/TRAP Control Register. As previously described for SLEEP mode, when the Z8S180/Z8L180 leaves IDLE mode due to an  $\overline{\text{NMI}}$ , or due to an enabled external interrupt request when the  $\overline{\text{IEF}}$  flag is 1 due to an EI instruction, the device starts by performing the interrupt with the return address of the instruction after the SLP instruction.

If an external interrupt enables the INT/TRAP control register while the IEF1 bit is 0, Z8S180/Z8L180 leaves IDLE mode; specifically, the processor restarts by executing the instructions following the SLP instruction.

Figure 15 indicates the timing for exiting IDLE mode due to an interrupt request.

**Note:** The Z8S180/Z8L180 takes about 9.5 clocks to restart.

#### **OPERATION MODES** (Continued)

Figure 15. Z8S180/Z8L180 IDLE Mode Exit Due To External Interrupt

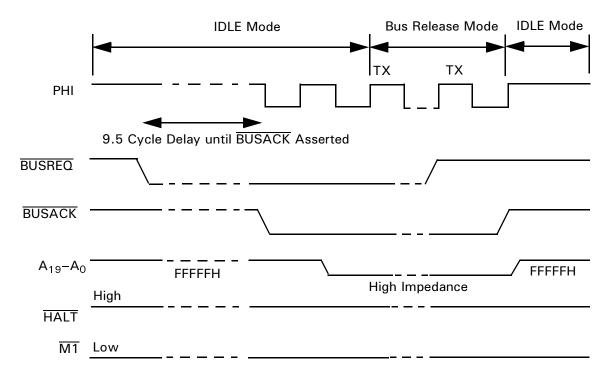

While the Z8S180/Z8L180 is in IDLE mode, it grants the bus to an external Master if the BREXT bit (CCR5) is 1. Figure 16 depicts the timing for this sequence.

After the external Master negates the Bus Request, the Z8S180/Z8L180 disables the PHI clock and remains in IDLE mode.

**Note:** A response to a bus request takes 8 clock cycles longer than in normal operation.

Figure 16. Bus Granting to External Master in IDLE Mode

#### STANDBY Mode (With or Without QUICK RECOVERY).

Software can put the Z8S180/Z8L180 into this mode by setting the IOSTOP bit (ICR5) to 1, CCR6 to 1, and executing the SLP instruction. This mode stops the on-chip oscillator and thus draws the least power of any mode, less than  $10\mu A$ .

As with IDLE mode, the Z8S180/Z8L180 leaves STANDBY mode in response to a Low on  $\overline{\text{RESET}}$ , on  $\overline{\text{NMI}}$ , or a Low on  $\overline{\text{INTO-2}}$  that is enabled by a 1 in the corresponding bit in the INT/TRAP Control Register. This action grants the bus to an external Master if the BREXT bit in the CPU Control Register (CCR5) is 1. The time required for all of these operations is greatly increased by the necessity for restarting the on-chip oscillator, and ensuring that it stabilizes to square-wave operation.

When an external clock is connected to the EXTAL pin rather than a crystal to the XTAL and EXTAL pins and the external clock runs continuously, there is little necessity to use STANDBY mode because no time is required to restart the oscillator, and other modes restart faster. However, if external logic stops the clock during STANDBY mode (for example, by decoding HALT Low and M1 High for several clock cycles), then STANDBY mode can be useful to allow the external clock source to stabilize after it is re-enabled.

When external logic drives RESET Low to bring the device out of STANDBY mode, and a crystal is in use or an external clock source is stopped, the external logic must hold RESET Low until the on-chip oscillator or external clock source is restarted and stabilized.

The clock-stability requirements of the Z8S180/Z8L180 are much less in the divide-by-two mode that is selected by a RESET sequence and controlled by the Clock Divide bit in the CPU Control Register (CCR7). As a result, software performs the following actions:

- 1. Sets CCR7 to 0 for divide-by-two mode before an SLP instruction and STANDBY mode.

- Delays setting CCR7 back to 1 for divide-by-one mode as long as possible to allow additional clock stabilization time after a RESET, interrupt, or in-line RESTART after an SLP 01 instruction.

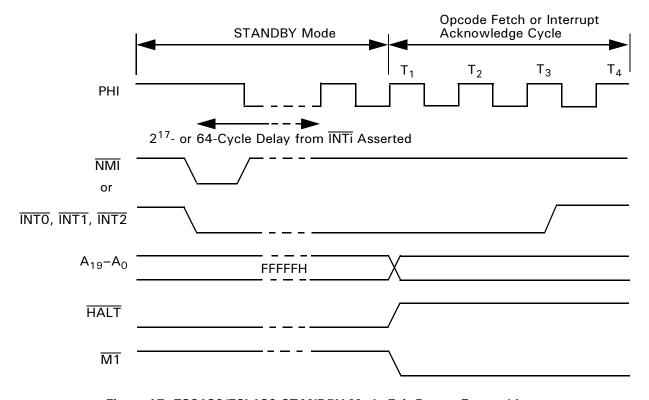

If CCR6 is set to 1 before the SLP instruction places the MPU in STANDBY mode, the value of the CCR3 bit determines the length of the delay before the oscillator restarts and stabilizes when it leaves STANDBY mode due to an external interrupt request. When CCR3 is 0, the Z8S180/Z8L180 waits 2<sup>17</sup> (131,072) clock cycles. When CCR3 is 1, it waits 64 clock cycles. This state is called QUICK RECOVERY mode. The same delay applies to grant-

ing the bus to an external Master during STANDBY mode, when the BREXT bit in the CPU Control Register (CCR5) is 1.

As described previously for SLEEP and IDLE modes, when the MPU leaves STANDBY mode due to NMI Low or an enabled INTO-INT2 Low when the IEF, flag is 1 due to an IE instruction, it starts by performing the interrupt with the return address being that of the instruction following the SLP instruction. If the Z8S180/Z8L180 leaves STANDBY mode due to an external interrupt request that's enabled in the INT/TRAP Control Register, but the IEF, bit is 0 due to

a DI instruction, the processor restarts by executing the instruction(s) following the SLP instruction. If INTO, or INT1 or INT2 goes inactive before the end of the clock stabilization delay, the Z8S180/Z8L180 stays in STANDBY mode.

Figure 17 indicates the timing for leaving STANDBY mode due to an interrupt request.

**Note:** The Z8S180/Z8L180 takes either 64 or 2<sup>17</sup> (131,072) clocks to restart, depending on the CCR3 bit.

Figure 17. Z8S180/Z8L180 STANDBY Mode Exit Due to External Interrupt

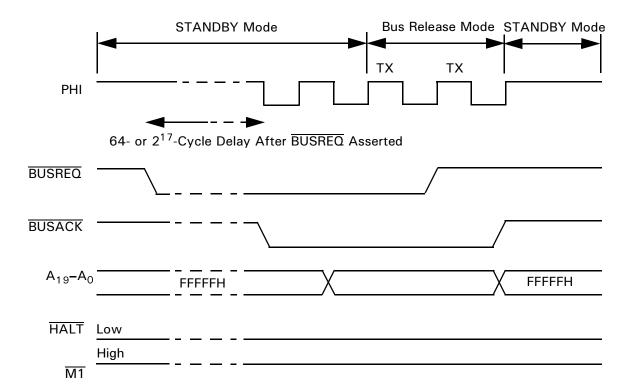

While the Z8S180/Z8L180 is in STANDBY mode, it grants the bus to an external Master if the BREXT bit (CCR5) is 1. Figure 18 indicates the timing of this sequence. The device takes 64 or  $2^{17}$  (131,072) clock cycles to grant the bus de-

pending on the CCR3 bit. The latter (not the QUICK RE-COVERY) case may be prohibitive for many demand-driven external Masters. If so, QUICK RECOVERY or IDLE mode can be used.

Figure 18. Bus Granting to External Master During STANDBY Mode

#### STANDARD TEST CONDITIONS

The following standard test conditions apply to  $\underline{DC}$  Characteristics, unless otherwise noted. All voltages are referenced to  $V_{SS}$  (0V). Positive current flows into the referenced pin.

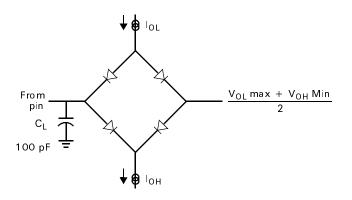

All AC parameters assume a load capacitance of 100 pF. Add a 10-ns delay for each 50-pF increase in load up to a maximum of 200 pF for the data bus and 100 pF for the address and control lines. AC timing measurements are referenced to  $V_{OL}$  MAX or  $V_{OL}$  MIN as indicated in Figures 20 through 30 (except for CLOCK, which is referenced to the 10% and 90% points). Ordering Information lists temperature ranges and product numbers. Find package drawings in Package Information.

Figure 19. AC Parameter Test Circuit

#### ABSOLUTE MAXIMUM RATINGS

| Item                  | Symbol           | Value                    | Unit |

|-----------------------|------------------|--------------------------|------|

| Supply Voltage        | $V_{DD}$         | -0.3 ~ +7.0              | V    |

| Input Voltage         | $V_{ N}$         | $-0.3 \sim V_{cc} + 0.3$ | V    |

| Operating Temperature | T <sub>OPR</sub> | 0 ~ 70                   | °C   |

| Extended Temperature  | T <sub>EXT</sub> | <b>−</b> 40 ~ 85         | °C   |

| Storage Temperature   | T <sub>STG</sub> | −55 ~ +150               | °C   |

**Note:** Permanent damage may occur if maximum ratings are exceeded. Normal operation should be under recommended operating conditions. If these conditions are exceeded, it could affect reliability.

#### DC CHARACTERISTICS—Z8S180

Table 6. Z8S180 DC Characteristics  $V_{DD} = 5V \pm 10\%$ ;  $V_{SS} = 0V$

| Symbol                       | Item                                                      | Condition                                   | Min                  | Тур | Max                     | Unit |

|------------------------------|-----------------------------------------------------------|---------------------------------------------|----------------------|-----|-------------------------|------|

| V <sub>IH1</sub>             | Input H Voltage<br>RESET, EXTAL, NMI                      |                                             | V <sub>DD</sub> -0.6 | _   | V <sub>DD</sub><br>+0.3 | V    |

| V <sub>IH2</sub>             | Input H Voltage<br>Except RESET, EXTAL, NMI               |                                             | 2.0                  | -   | V <sub>DD</sub><br>+0.3 | V    |

| V <sub>IH3</sub>             | Input H Voltage<br>CKS, CKA0, CKA1                        |                                             | 2.4                  | _   | V <sub>DD</sub><br>+0.3 | V    |

| V <sub>IL1</sub>             | Input L Voltage<br>RESET, EXTAL, NMI                      |                                             | -0.3                 | _   | 0.6                     | V    |

| V <sub>IL2</sub>             | Input L Voltage<br>Except RESET, EXTAL, NMI               |                                             | -0.3                 | _   | 0.8                     | V    |

| V <sub>OH</sub>              | Outputs H Voltage<br>All outputs                          | $I_{OH} = -200 \mu A$                       | 2.4                  | _   | _                       | V    |

|                              |                                                           | $I_{OH} = -20 \mu\text{A}$                  | V <sub>DD</sub> -1.2 | _   | _                       |      |

| V <sub>OL</sub>              | Outputs L Voltage<br>All outputs                          | $I_{OL} = 2.2 \text{ mA}$                   | _                    | _   | 0.45                    | V    |

| I <sub>IL</sub>              | Input Leakage<br>Current All Inputs<br>Except XTAL, EXTAL | $V_{IN} = 0.5 \sim V_{DD} - 0.5$            | _                    | _   | 1.0                     | μΑ   |

| I <sub>TL</sub>              | Three State Leakage<br>Current                            | $V_{IN} = 0.5 \sim V_{DD} - 0.5$            | _                    | _   | 1.0                     | μΑ   |

| I <sub>DD</sub> <sup>1</sup> | Power Dissipation                                         | F = 10 MHz                                  | _                    | 25  | 60                      | mA   |

| 00                           | (Normal Operation)                                        | 20                                          |                      | 30  | 50                      |      |

|                              |                                                           | 33                                          |                      | 60  | 100                     |      |

|                              | Power Dissipation                                         | F = 10 MHz                                  |                      | 2   | 5                       |      |

|                              | (SYSTEM STOP mode)                                        | 20                                          |                      | 3   | 6                       |      |

|                              |                                                           | 33                                          |                      | 5   | 9                       |      |

| C <sub>P</sub>               | Pin Capacitance                                           | $V_{ N} = O_V$ , f = 1 MHz<br>$T_A = 25$ °C | _                    | _   | 12                      | pF   |

#### Note:

<sup>1.</sup>  $V_{IHmin} = V_{DD}$ -1.0V,  $V_{ILmax} = 0.8V$  (All output terminals are at NO LOAD.)  $V_{DD} = 5.0V$ .

Table 7. Z8L180 DC Characteristics  $V_{DD} = 3.3V \pm 10\%; V_{SS} = 0V$

| Symbol           | Item                                                      | Condition                                     | Min                  | Тур | Max                     | Unit |

|------------------|-----------------------------------------------------------|-----------------------------------------------|----------------------|-----|-------------------------|------|

| V <sub>IH1</sub> | Input H Voltage<br>RESET, EXTAL, NMI                      |                                               | V <sub>DD</sub> -0.6 |     | V <sub>DD</sub><br>+0.3 | V    |

| V <sub>IH2</sub> | Input H Voltage<br>Except RESET, EXTAL, NMI               |                                               | 2.0                  |     | V <sub>DD</sub><br>+0.3 | V    |

| V <sub>IL1</sub> | Input L Voltage<br>RESET, EXTAL, NMI                      |                                               | -0.3                 |     | 0.6                     | V    |

| V <sub>IL2</sub> | Input L Voltage<br>Except RESET, EXTAL, NMI               |                                               | -0.3                 |     | 0.8                     | V    |

| V <sub>OH</sub>  | Outputs H Voltage                                         | $I_{OH} = -200  \mu A$                        | 2.15                 |     |                         | V    |

|                  | All outputs                                               | $I_{OH} = -20 \mu A$                          | V <sub>DD</sub> -0.6 |     |                         | V    |

| V <sub>OL</sub>  | Outputs L Voltage<br>All Outputs                          | $I_{OL} = 4 \text{ mA}$                       |                      |     | 0.4                     | V    |

| I <sub>IL</sub>  | Input Leakage<br>Current All Inputs<br>Except XTAL, EXTAL | $V_{IN} = 0.5 \sim V_{DD} - 0.5$              |                      |     | 1.0                     | μΑ   |

| I <sub>TL</sub>  | Three State Leakage<br>Current                            | $V_{ N} = 0.5 \sim V_{DD} - 0.5$              |                      |     | 1.0                     | μΑ   |

| I <sub>DD1</sub> | Power Dissipation                                         | F = 20  MHz                                   |                      | 30  | 60                      | mA   |

|                  | (Normal Operation)                                        | 4 MHz                                         |                      | 4   | 10                      |      |

|                  | Power Dissipation (SYSTEM STOP mode)                      | F = 20 MHz                                    |                      | 5   | 10                      |      |

|                  |                                                           | 4 MHz                                         |                      | 2   | 5                       |      |

| C <sub>P</sub>   | Pin Capacitance                                           | $V_{IN} = 0V$ , $f = 1 MHz$<br>$T_A = 25$ ° C |                      |     | 12                      | pF   |

| Note:            |                                                           |                                               |                      |     |                         |      |

<sup>1.</sup>  $V_{IHmin} = V_{DD}$  –1.0V,  $V_{ILmax} = 0.6V$  (All output terminals are at NO LOAD.)  $V_{DD} = 3.0V$ .

## **AC CHARACTERISTICS—Z8S180**

Table 8. Z8S180 AC Characteristics  $V_{DD}=5V~\pm10\%$  or  $V_{DD}=3.3V~\pm10\%$ ; 33-MHz Characteristics Apply Only to 5V Operation

|        |                   |                                                                             | Z8S180-20 MHz Z8S180-33 MHz |     |          |     |      |

|--------|-------------------|-----------------------------------------------------------------------------|-----------------------------|-----|----------|-----|------|

| Number | Symbol            | Item                                                                        | Min                         | Max | Min      | Max | Unit |

| 1      | t <sub>CYC</sub>  | Clock Cycle Time                                                            | 50                          | DC  | 30       | DC  | ns   |

| 2      | t <sub>CHW</sub>  | Clock "H" Pulse Width                                                       | 15                          | _   | 10       | _   | ns   |

| 3      | t <sub>CLW</sub>  | Clock "L" Pulse Width                                                       | 15                          | _   | 10       | _   | ns   |

| 4      | t <sub>CF</sub>   | Clock Fall Time                                                             | _                           | 10  | _        | 5   | ns   |

| 5      | t <sub>CR</sub>   | Clock Rise Time                                                             | _                           | 10  | _        | 5   | ns   |

| 6      | t <sub>AD</sub>   | PHI Rise to Address Valid Delay                                             | _                           | 30  | _        | 15  | ns   |

| 7      | t <sub>AS</sub>   | Address Valid to MREQ Fall or IORQ Fall)                                    | 5                           | _   | 5        | _   | ns   |

| 8      | t <sub>MED1</sub> | PHI Fall to MREQ Fall Delay                                                 | _                           | 25  | _        | 15  | ns   |

| 9      | t <sub>RDD1</sub> | PHI Fall to $\overline{RD}$ Fall Delay $\overline{IOC} = 1$                 | _                           | 25  | _        | 15  | ns   |

|        |                   | PHI Rise to $\overline{RD}$ Rise Delay $\overline{IOC} = 0$                 | _                           | 25  | _        | 15  |      |

| 10     | t <sub>M1D1</sub> | PHI Rise to M1 Fall Delay                                                   | _                           | 35  | _        | 15  | ns   |

| 11     | t <sub>AH</sub>   | Address Hold Time from MREQ, IOREQ, RD, WR High                             | 5                           | _   | 5        | _   | ns   |

| 12     | t <sub>MED2</sub> | PHI Fall to MREQ Rise Delay                                                 | _                           | 25  | _        | 15  | ns   |

| 13     | t <sub>RDD2</sub> | PHI Fall to RD Rise Delay                                                   | _                           | 25  | _        | 15  | ns   |

| 14     | t <sub>M1D2</sub> | PHI Rise to M1 Rise Delay                                                   | _                           | 40  | _        | 15  | ns   |

| 15     | t <sub>DRS</sub>  | Data Read Set-up Time                                                       | 10                          | _   | 5        | _   | ns   |

| 16     | t <sub>DRH</sub>  | Data Read Hold Time                                                         | 0                           | _   | 0        | _   | ns   |

| 17     | t <sub>STD1</sub> | PHI Fall to ST Fall Delay                                                   | _                           | 30  | _        | 15  | ns   |

| 18     | t <sub>STD2</sub> | PHI Fall to ST Rise Delay                                                   | _                           | 30  | _        | 15  | ns   |

| 19     | t <sub>WS</sub>   | WAIT Set-up Time to PHI Fall                                                | 15                          | _   | 10       | _   | ns   |

| 20     | t <sub>WH</sub>   | WAIT Hold Time from PHI Fall                                                | 10                          | _   | 5        | _   | ns   |

| 21     | t <sub>WDZ</sub>  | PHI Rise to Data Float Delay                                                | _                           | 35  | _        | 20  | ns   |

| 22     | t <sub>WRD1</sub> | PHI Rise to WR Fall Delay                                                   | _                           | 25  | _        | 15  | ns   |

| 23     | t <sub>WDD</sub>  | PHI Fall to Write Data Delay Time                                           | _                           | 25  | _        | 15  | ns   |

| 24     | t <sub>WDS</sub>  | Write Data Set-up Time to WR Fall                                           | 10                          | _   | 10       | _   | ns   |

| 25     | t <sub>WRD2</sub> | PHI Fall to WR Rise Delay                                                   | _                           | 25  | _        | 15  | ns   |

| 26     | t <sub>WRP</sub>  | WR Pulse Width (Memory Write Cycle)                                         | 80                          | _   | 45       | _   | ns   |

| 26a    |                   | WR Pulse Width (I/O Write Cycle)                                            | 150                         | _   | 70       | _   | ns   |

| 27     | t <sub>WDH</sub>  | Write Data Hold Time from WR Rise                                           | 10                          | _   | 5        | _   | ns   |

| 28     | t <sub>IOD1</sub> | PHI Fall to $\overline{IORQ}$ Fall Delay $\overline{IOC} = 1$               | _                           | 25  | _        | 15  | ns   |

|        |                   | PHI Rise to $\overline{\text{IORQ}}$ Fall Delay $\overline{\text{IOC}} = 0$ | _                           | 25  | _        | 15  |      |

| 29     | t <sub>IOD2</sub> | PHI Fall to IORQ Rise Delay                                                 | <u> </u>                    | 25  | <u> </u> | 15  | ns   |

| 30     | t <sub>IOD3</sub> | M1 Fall to IORQ Fall Delay                                                  | 125                         | _   | 80       | _   | ns   |

| 31     | t <sub>INTS</sub> | INT Set-up Time to PHI Fall                                                 | 20                          |     | 15       | _   | ns   |

# AC CHARACTERISTICS—Z8S180 (Continued)

Table 8. Z8S180 AC Characteristics (Continued)  $V_{DD}=5V\pm10\%$  or  $V_{DD}=3.3V\pm10\%$ ; 33-MHz Characteristics Apply Only to 5V Operation

|        |                   |                                                           | Z8S180 | _20 MHz                     | Z8S180-33 MHz |                            |      |

|--------|-------------------|-----------------------------------------------------------|--------|-----------------------------|---------------|----------------------------|------|

| Number | Symbol            | Item                                                      | Min    | Max                         | Min           | Max                        | Unit |

| 32     | t <sub>INTH</sub> | INT Hold Time from PHI Fall                               | 10     | _                           | 10            | _                          | ns   |

| 33     | t <sub>NMIW</sub> | NMI Pulse Width                                           | 35     | _                           | 25            | _                          | ns   |

| 34     | t <sub>BRS</sub>  | BUSREQ Set-up Time to PHI Fall                            | 10     | _                           | 10            | _                          | ns   |

| 35     | t <sub>BRH</sub>  | BUSREQ Hold Time from PHI Fall                            | 10     | _                           | 10            |                            | ns   |

| 36     | t <sub>BAD1</sub> | PHI Rise to BUSACK Fall Delay                             | _      | 25                          | _             | 15                         | ns   |

| 37     | t <sub>BAD2</sub> | PHI Fall to BUSACK Rise Delay                             | _      | 25                          | _             | 15                         | ns   |

| 38     | t <sub>BZD</sub>  | PHI Rise to Bus Floating Delay Time                       | _      | 40                          | _             | 30                         | ns   |

| 39     | t <sub>MEWH</sub> | MREQ Pulse Width (High)                                   | 35     | _                           | 25            | _                          | ns   |

| 40     | t <sub>MEWL</sub> | MREQ Pulse Width (Low)                                    | 35     | _                           | 25            | _                          | ns   |

| 41     | t <sub>RFD1</sub> | PHI Rise to RFSH Fall Delay                               |        | 20                          | _             | 15                         | ns   |

| 42     | t <sub>RFD2</sub> | PHI Rise to RFSH Rise Delay                               | _      | 20                          | _             | 15                         | ns   |

| 43     | t <sub>HAD1</sub> | PHI Rise to HALT Fall Delay                               | _      | 15                          | _             | 15                         | ns   |

| 44     | t <sub>HAD2</sub> | PHI Rise to HALT Rise Delay                               | _      | 15                          | _             | 15                         | ns   |

| 45     | t <sub>DRQS</sub> | DREQ1 Set-up Time to PHI Rise                             | 20     | _                           | 15            | _                          | ns   |

| 46     | t <sub>DRQH</sub> | DREQ1 Hold Time from PHI Rise                             | 20     | _                           | 15            | _                          | ns   |

| 47     | t <sub>TED1</sub> | PHI Fall to TENDi Fall Delay                              | _      | 25                          | _             | 15                         | ns   |

| 48     | t <sub>TED2</sub> | PHI Fall to TENDi Rise Delay                              | _      | 25                          | _             | 15                         | ns   |

| 49     | t <sub>ED1</sub>  | PHI Rise to E Rise Delay                                  | _      | 30                          | _             | 15                         | ns   |

| 50     | t <sub>ED2</sub>  | PHI Fall or Rise to E Fall Delay                          | _      | 30                          | _             | 15                         | ns   |

| 51     | P <sub>WEH</sub>  | E Pulse Width (High)                                      | 25     | _                           | 20            | _                          | ns   |

| 52     | P <sub>WEL</sub>  | E Pulse Width (Low)                                       | 50     | _                           | 40            | _                          | ns   |

| 53     | t <sub>Er</sub>   | Enable Rise Time                                          | _      | 10                          | _             | 10                         | ns   |

| 54     | t <sub>Ef</sub>   | Enable Fall Time                                          | _      | 10                          | _             | 10                         | ns   |

| 55     | t <sub>TOD</sub>  | PHI Fall to Timer Output Delay                            | _      | 75                          | _             | 50                         | ns   |

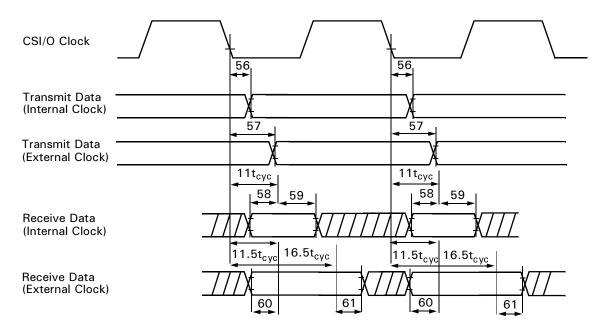

| 56     | t <sub>STDI</sub> | CSI/O Transmit Data Delay Time (Internal Clock Operation) | _      | 2                           | _             | 2                          | tcyc |

| 57     | t <sub>STDE</sub> | CSI/O Transmit Data Delay Time (External Clock Operation) | _      | 7.5 t <sub>CYC</sub><br>+75 | _             | 75 t <sub>CYC</sub><br>+60 | ns   |

| 58     | t <sub>SRSI</sub> | CSI/O Receive Data Set-up Time (Internal Clock Operation) | 1      | _                           | 1             | _                          | tcyc |

| 59     | t <sub>SRHI</sub> | CSI/O Receive Data Hold Time (Internal Clock Operation)   | 1      | _                           | 1             | _                          | tcyc |

| 60     | t <sub>SRSE</sub> | CSI/O Receive Data Set-up Time (External Clock Operation) | 1      | _                           | 1             | _                          | tcyc |

| 61     | t <sub>SRHE</sub> | CSI/O Receive Data Hold Time (External Clock Operation)   | 1      | _                           | 1             | _                          | tcyc |

| 62     | t <sub>RES</sub>  | RESET Set-up Time to PHI Fall                             | 40     | _                           | 25            | _                          | ns   |

# Table 8. Z8S180 AC Characteristics (Continued) $V_{DD}=5V\pm10\%$ or $V_{DD}=3.3V\pm10\%$ ; 33-MHz Characteristics Apply Only to 5V Operation

|        |                  |                                       | Z8S180-20 MHz Z8S180-33 MHz |     |     | _   |      |

|--------|------------------|---------------------------------------|-----------------------------|-----|-----|-----|------|

| Number | Symbol           | Item                                  | Min                         | Max | Min | Max | Unit |

| 63     | t <sub>REH</sub> | RESET Hold Time from PHI Fall         | 25                          | _   | 15  | _   | ns   |

| 64     | t <sub>OSC</sub> | Oscillator Stabilization Time         | _                           | 20  | _   | 20  | ns   |

| 65     | t <sub>EXR</sub> | External Clock Rise Time (EXTAL)      | _                           | 5   | _   | 5   | ns   |

| 66     | t <sub>EXF</sub> | External Clock Fall Time (EXTAL)      | _                           | 5   | _   | 5   | ns   |

| 67     | t <sub>RR</sub>  | RESET Rise Time                       | _                           | 50  | _   | 50  | ms   |

| 68     | t <sub>RF</sub>  | RESET Fall Time                       | _                           | 50  | _   | 50  | ms   |

| 69     | t <sub>IR</sub>  | Input Rise Time (except EXTAL, RESET) | _                           | 50  | _   | 50  | ns   |