Short Form Data Sheet

### Features

- Fully compliant SEC (G.813) and EEC (G.8262) flexible rate conversion digital phase locked loop (DPLL)

- Two programmable DPLLs/Numerically Controlled Oscillators (NCOs) synchronize to any clock rate from 1 Hz to 750 MHz

- Four programmable synthesizers generate any clock rate from 1 Hz to 750 MHz with maximum jitter below 0.62 ps RMS

- Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates

- DPLLs filter jitter from 0.1 mHz up to 1 kHz

- Automatic hitless reference switching and digital holdover on reference fail

- Nine input references configurable as single ended or differential and two single ended input references

- Any input reference can be fed with sync (frame pulse) or clock

| Ordering I | nformation |

|------------|------------|

|------------|------------|

ZL30163GDG2 144 Pin LBGA Trays

Pb Free Tin/Silver/Copper -40°C to +85°C Package Size: 13 x 13 mm

- Programmable DPLLs can synchronize to sync pulse and sync pulse/clock pair

- · Eight LVPECL outputs and eight LVCMOS outputs

- Operates from a single crystal resonator or clock

oscillator

- Field programmable via the SPI/I<sup>2</sup>C interface

#### Applications

- SyncE/SONET/SDH Timing Cards

- Synchronous Ethernet, 10 GBASE-R and 10 GBASE-W

- SONET/SDH, Fibre Channel, XAUI

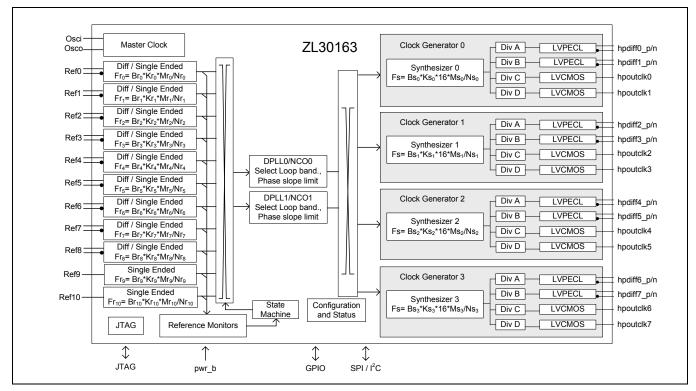

#### Figure 1 - Functional Block Diagram

ZL30163

# 1.0 Pin Diagram

TOP VIEW

| $\Lambda$ | 1             | 2              | 3          | 4           | 5           | 6           | 7           | 8           | 9           | 10         | 11             | 12             |

|-----------|---------------|----------------|------------|-------------|-------------|-------------|-------------|-------------|-------------|------------|----------------|----------------|

| A         | <br>hpdiff0_p | O<br>VDD0      | O<br>NC    | O<br>VDD1   | Osco_1V8    | O<br>VDD2   | Osco_3V3    | Osci_3V3    | O<br>VDD3   | O<br>NC    | O<br>VDD4      | hpdiff2_p      |

| В         | <br>hpdiff0_n | ⊖<br>vss       |            | O<br>vss    | Osci_1V8    | ⊖<br>vss    | )<br>XOin   | O<br>VCORE0 | ⊖<br>vss    |            | O<br>VSS       | D<br>hpdiff2_n |

| С         | <br>hpdiff1_p | Dhpdiff1_n     | VDD5       | Vss         | VSS         | O<br>VCORE1 | O<br>VSS    | O<br>vss    | O<br>VSS    | VDD6       | O<br>hpdiff3_n | hpdiff3_p      |

| D         | O<br>VDD7     | O<br>vss       | hpoutclk0  | hpoutclk1   | O<br>vss    | ⊖<br>vss    | O<br>VSS    | O<br>vss    | hpoutclk3   | hpoutclk2  | O<br>VSS       | O<br>VDD8      |

| E         | NC            | UDD9           | O<br>VDD10 | VSS         | ⊖<br>vss    | ⊖<br>vss    | O<br>VSS    | O<br>vss    | O<br>VSS    | O<br>VDD11 | O<br>IC1       | O<br>NC        |

| F         | O<br>NC       | ⊖<br>trst_b    | hpoutclk4  | hpoutclk5   | O<br>VSS    | O<br>vss    | O<br>VSS    | O<br>VSS    | hpoutclk6   | hpoutclk7  | pwr_b          | O<br>NC        |

| G         | tdi           | ⊖<br>tdo       | )<br>tms   | O<br>VSS    | O<br>VSS    | O<br>vss    | O<br>VSS    | O<br>VSS    | O<br>VDD12  | <br>gpio1  | <br>gpio0      | O<br>IC2       |

| Н         | <br>hpdiff4_p | O<br>hpdiff4_n | C<br>tck   | ⊖<br>vss    | ⊖<br>vss    | ⊖<br>vss    | ⊖<br>vss    | O<br>VSS    | O<br>VCORE2 | gpio2      | hpdiff6_n      | hpdiff6_p      |

| J         | O<br>VDD13    | ⊖<br>vss       | O<br>gpio4 | ⊖<br>vss    | O<br>VSS    | ⊖<br>vss    | ⊖<br>vss    | ⊖<br>vss    | O<br>VCORE3 | O<br>gpio3 | O<br>VSS       | O<br>VDD14     |

| к         | <br>hpdiff5_p | Dhpdiff5_n     | O<br>gpio5 | O<br>gpio6  | ⊖<br>vss    | O<br>VCORE4 | Cs_b_asel0  | Sck_scl     | ⊖<br>si_sda | So_asel1   | hpdiff7_n      | hpdiff7_p      |

| L         | O<br>VDD15    | O<br>VSS       | Cref1_p    | O<br>ref1_n | Cref3_p     | O<br>ref3_n | Cref5_p     | Cref5_n     | Cref6_n     | Cref8_p    | Cref8_n        | Cref10         |

| м         |               | O<br>vss       | Cref0_p    | Cref0_n     | C<br>ref2_p | C<br>ref2_n | C<br>ref4_p | C<br>ref4_n | ref6_p      | Cref7_p    | oref7_n        | ref9           |

- A1 corner is identified by metallized markings.

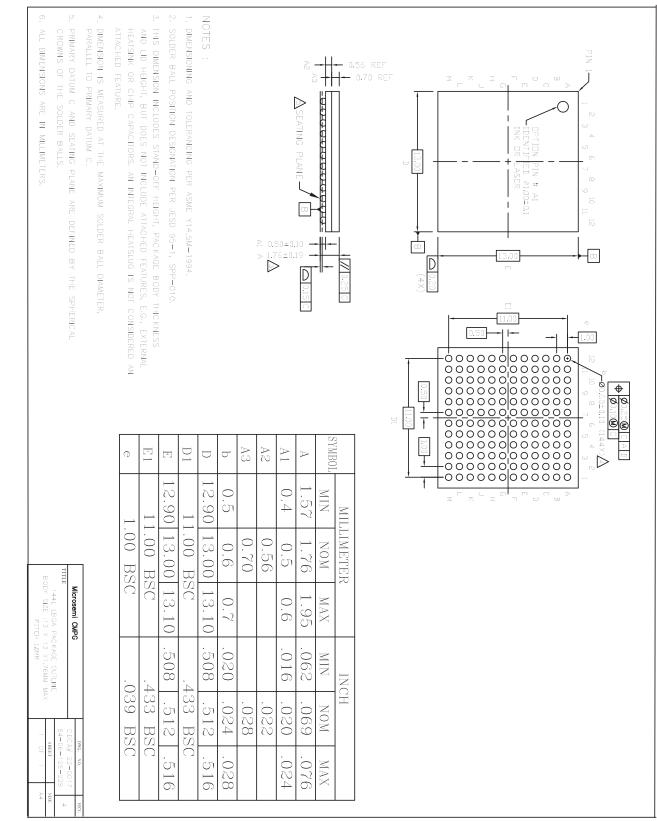

### Figure 2 - Package Description

# 2.0 Pin Description

All device inputs and outputs are LVCMOS unless it is specifically stated to be differential. For the I/O column, there are digital inputs (I), digital outputs (O), analog inputs (A-I) and analog outputs (A-O).

| Ball #                                                                                                       | Name                                                                                                                                                                                       | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Ref                                                                                                    | erence                                                                                                                                                                                     |     |                                                                                                                                                                                                                                                                                                                                                                                                  |

| M3<br>M4<br>L3<br>L4<br>M5<br>M6<br>L5<br>L6<br>M7<br>M8<br>L7<br>L8<br>M9<br>L9<br>M10<br>M11<br>L10<br>L11 | ref0_p<br>ref0_n<br>ref1_p<br>ref1_n<br>ref2_p<br>ref2_n<br>ref3_p<br>ref3_n<br>ref4_p<br>ref4_n<br>ref5_p<br>ref5_n<br>ref6_n<br>ref6_n<br>ref6_n<br>ref7_p<br>ref7_n<br>ref8_p<br>ref8_n | Ι   | Input References 0 to 8. Input reference sources used for<br>synchronization. The positive and negative pair of these inputs accepts a<br>differential input signal. The refx_p input terminal accepts a CMOS input<br>reference. These inputs can be used as an external feedback input.<br>Maximum frequency limit on single ended inputs is 177.5 MHz, and<br>750 MHz on differential inputs. |

| M12<br>L12                                                                                                   | ref9<br>ref10                                                                                                                                                                              | I   | Input References 9 and 10. Input reference sources used for synchronization. These inputs are the same as inputs 0 to 8, but only single ended. These inputs can be used as an external feedback input. Maximum frequency limit is 177.5 MHz.                                                                                                                                                    |

| Output C                                                                                                     | locks                                                                                                                                                                                      |     |                                                                                                                                                                                                                                                                                                                                                                                                  |

| D3<br>D4<br>D10<br>D9<br>F3<br>F4<br>F9<br>F10                                                               | hpoutclk0<br>hpoutclk1<br>hpoutclk2<br>hpoutclk3<br>hpoutclk4<br>hpoutclk5<br>hpoutclk6<br>hpoutclk7                                                                                       | 0   | <ul> <li>High Performance Output Clocks 0 to 7. These outputs can be configured to provide any one of the single ended high performance clock outputs.</li> <li>Maximum frequency limit on single ended LVCMOS outputs is 177.5 MHz.</li> </ul>                                                                                                                                                  |

Table 1 - Pin Description

| Ball #                                                                                               | Name                                                                                                                                                                                            | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1<br>B1<br>C1<br>C2<br>A12<br>B12<br>C12<br>C11<br>H1<br>H2<br>K1<br>K2<br>H12<br>H11<br>K12<br>K11 | hpdiff0_p<br>hpdiff0_n<br>hpdiff1_p<br>hpdiff1_n<br>hpdiff2_p<br>hpdiff2_n<br>hpdiff3_n<br>hpdiff4_p<br>hpdiff4_n<br>hpdiff5_p<br>hpdiff5_n<br>hpdiff5_n<br>hpdiff6_p<br>hpdiff6_n<br>hpdiff7_n | 0   | <ul> <li>High Performance Differential Output Clocks 0 to 7 (LVPECL). These outputs can be configured to provide any one of the available high performance differential output clocks.</li> <li>Maximum frequency limit on differential outputs is 750 MHz.</li> </ul>                                                                                                                                                                                     |

| Control a                                                                                            | ind Status                                                                                                                                                                                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| F11                                                                                                  | pwr_b                                                                                                                                                                                           | I   | <b>Power-on Reset.</b> A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. The <b>pwr_b</b> pin should be held low for 2 ms after all power supplies are stabilized. This pin is internally pulled-up to $V_{DD}$ . User can access device registers either 125 ms after <b>pwr_b</b> goes high, or after bit 7 in register at address 0x000 goes high (which can be determined by polling). |

Table 1 - Pin Description (continued)

| Ball #                                     | Name                                                        | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------|-------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G11<br>G10<br>H10<br>J10<br>J3<br>K3<br>K4 | gpio0<br>gpio1<br>gpio2<br>gpio3<br>gpio4<br>gpio5<br>gpio6 | 1/0   | <b>General Purpose Input and Output pins.</b> These are general purpose I/O pins.<br>Example GPIO functions include:<br>• DPLL lock indicators<br>• DPLL holdover indicators<br>• Reference fail indicators<br>• Reference select control or monitor<br>• Differential output clock enable<br>• High performance LVCMOS outputs enable<br>• Host Interrupt Output to flag status changes<br>All GPIO functions are listed in 5.2, "GPIO Configuration".<br>Pins 5:0 are internally pulled down to GND and pin 6 is internally pulled<br>up to V <sub>DD</sub> .<br>Unused GPIO pins can be left unconnected.<br>After power on reset, device GPIO[0,1,3] configure basic device function.<br>GPIO3 sets I <sup>2</sup> C or SPI control mode, GPIO[1,0] sets master clock rate<br>selection. The GPIO[0,1,3] pins must be either pulled low or high with an<br>external 1 k $\Omega$ resistor for their assigned functions at reset; or they must<br>be driven low or high for 125 ms after reset, and released and then used<br>for normal GPIO functions.<br>The GPIO4 pin must be either pulled low with an external 1 k $\Omega$ resistor;<br>or it must be driven low for 125 ms after reset, and then released and<br>used for normal GPIO functions. |

| Host Inter<br>K8                           | face<br>sck_scl                                             | I/O   | GPIO[5,6] are not used during power up.<br><b>Clock for Serial Interface.</b> Provides clock for serial micro-port interface.<br>This pin is also the serial clock line (SCL) when the host interface is<br>configured for I <sup>2</sup> C mode. As an input this pin is internally pulled up to<br>Var                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| K9                                         | si_sda                                                      | I/O   | $V_{DD}$ .<br><b>Serial Interface Input.</b> The input serial data stream holds the access command, the address and the write data bits. This pin is also the serial data line (SDA) when the host interface is configured for I <sup>2</sup> C mode. This pin is internally pulled up to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| K10                                        | so_asel1                                                    | I/O   | <b>Serial Interface Output.</b> As an output, the serial stream holds the read data bits. This pin is also a part of the $I^2C$ address select when the host interface is configured for $I^2C$ mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| K7                                         | cs_b_asel0                                                  | I     | <b>Chip Select for Serial Interface.</b> As serial interface chip select, this is an active low signal. This pin is also a part of the $I^2C$ address select when the host interface is configured for $I^2C$ mode. This pin is internally pulled up to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| JTAG (IEE                                  | E 1149.1) and Test                                          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| G12                                        | IC2                                                         | I     | Internal Connection. Connect this pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| E11                                        | IC1                                                         | A-I/O | Internal Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### Table 1 - Pin Description (continued)

| Ball # | Name   | I/O | Description                                                                                                                                                                                                                                                                                                                                      |

|--------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G2     | tdo    | 0   | <b>Test Serial Data Out.</b> JTAG serial data is output on this pin on the falling edge of tck. This pin is held in high impedance state when JTAG scan is not enabled.                                                                                                                                                                          |

| G1     | tdi    | 1   | <b>Test Serial Data In.</b> JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be left unconnected.                                                                                                                                        |

| F2     | trst_b | I   | <b>Test Reset.</b> Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be held low or pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be connected to GND. |

| H3     | tck    | I   | <b>Test Clock.</b> Provides the clock for the JTAG test logic. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be connected to GND.                                                                                                                                                                        |

| G3     | tms    | I   | <b>Test Mode Select.</b> JTAG signal that controls the state transitions of the TAP controller. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be left unconnected.                                                                                                                                       |

|    | . ,      |     |                                                                                                                                                                                                                                                                                                                                            |

|----|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A7 | osco_3V3 | A-0 | <b>3.3V Crystal Master Clock Output.</b> For the alternative connection method for a crystal, the crystal is connected from this pin to <b>osci_3V3</b> . Not suitable for driving other devices. For clock oscillator operation or the use of a crystal between <b>osci_1V8</b> and <b>osco_1V8</b> , this pin should be lef unconnected. |

| A8 | osci_3V3 | I   | <b>3.3V Crystal Master Clock Input.</b> For the alternative connection method for a crystal, the crystal is connected from this pin to <b>osco_3V3</b> . For clock oscillator operation or the use of a crystal between <b>osci_1V8</b> and <b>osco_1V8</b> , this pin should be grounded.                                                 |

| A5 | osco_1V8 | A-0 | <b>1.8V Crystal Master Clock Output.</b> For the primary connection method for a crystal, the crystal is connected from this pin to <b>osci_1V8</b> . Not suitable for driving other devices. For clock oscillator operation or the use of a crystal between <b>osci_3V3</b> and <b>osco_3V3</b> , this pin should be left unconnected.    |

| В5 | osci_1V8 | I   | <b>1.8V Crystal Master Clock Input.</b> For the primary connection method for a crystal, the crystal is connected from this pin to <b>osco_1V8</b> . For clock oscillator operation or the use of a crystal between <b>osci_3V3</b> and <b>osco_3V3</b> , this pin should be grounded.                                                     |

| B7 | XOin     | Ι   | <b>XO Master Clock Output.</b> For clock oscillator operation, this pin is connected to the output of the oscillator. For crystal operation using either method, this pin should be grounded.                                                                                                                                              |

#### Power and Ground

### Table 1 - Pin Description (continued)

| Ball #                                                                                            | Name                                                                                                                                                                                                              | I/O | Description                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B8<br>C6<br>H9<br>J9<br>K6<br>M1                                                                  | V <sub>CORE0</sub><br>V <sub>CORE1</sub><br>V <sub>CORE2</sub><br>V <sub>CORE3</sub><br>V <sub>CORE4</sub><br>V <sub>CORE5</sub>                                                                                  |     | <b>Positive Supply Voltage.</b> +1.8V <sub>DC</sub> nominal.<br>These pins should not be connected together on the board. Please refer<br>to ZLAN-327 for recommendations |

| A2<br>A4<br>A6<br>A9<br>A11<br>C3<br>C10<br>D1<br>D12<br>E2<br>E3<br>E10<br>G9<br>J1<br>J12<br>L1 | $\begin{array}{c} V_{DD0} \\ V_{DD1} \\ V_{DD2} \\ V_{DD3} \\ V_{DD4} \\ V_{DD5} \\ V_{DD6} \\ V_{DD7} \\ V_{DD8} \\ V_{DD9} \\ V_{DD10} \\ V_{DD11} \\ V_{DD12} \\ V_{DD13} \\ V_{DD14} \\ V_{DD15} \end{array}$ |     | Positive Supply Voltage. +3.3V <sub>DC</sub> nominal.<br>These pins should not be connected together on the board. Please refer<br>to ZLAN-327 for recommendations        |

| Table 1 - Pin I | Description | (continued) |

|-----------------|-------------|-------------|

|-----------------|-------------|-------------|

| Ball #               | Name            | I/O | Description      |

|----------------------|-----------------|-----|------------------|

| B2                   | V <sub>SS</sub> |     | Ground. 0 Volts. |

| B4                   | 66              |     |                  |

| B6                   |                 |     |                  |

| B9                   |                 |     |                  |

| B11                  |                 |     |                  |

| C4                   |                 |     |                  |

| C5                   |                 |     |                  |

| C7                   |                 |     |                  |

| C7<br>C8<br>C9<br>D2 |                 |     |                  |

| C9                   |                 |     |                  |

| D2                   |                 |     |                  |

| D11                  |                 |     |                  |

| E4                   |                 |     |                  |

| E9                   |                 |     |                  |

| G4                   |                 |     |                  |

| H4                   |                 |     |                  |

| H5<br>H6             |                 |     |                  |

| H7                   |                 |     |                  |

| H8                   |                 |     |                  |

| J2                   |                 |     |                  |

| J4                   |                 |     |                  |

| J5                   |                 |     |                  |

| J6                   |                 |     |                  |

| J7                   |                 |     |                  |

| J8                   |                 |     |                  |

| J11                  |                 |     |                  |

| K5                   |                 |     |                  |

| L2                   |                 |     |                  |

| M2                   |                 |     |                  |

| D5                   |                 |     |                  |

| D6                   |                 |     |                  |

| D7                   |                 |     |                  |

| D8                   |                 |     |                  |

| E5                   |                 |     |                  |

| E6<br>E7             |                 |     |                  |

|                      |                 |     |                  |

| E0<br>E5             |                 |     |                  |

| E8<br>F5<br>F6<br>F7 |                 |     |                  |

| F7                   |                 |     |                  |

| F8                   |                 |     |                  |

| F8<br>G5             |                 |     |                  |

| G6                   |                 |     |                  |

| G7                   |                 |     |                  |

| G8                   |                 |     |                  |

| Table 1 - Pin Description | (continued) |

|---------------------------|-------------|

|---------------------------|-------------|

| Ball #                                           | Name | I/O | Description                                 |

|--------------------------------------------------|------|-----|---------------------------------------------|

| A3<br>A10<br>B3<br>B10<br>E1<br>E12<br>F1<br>F12 | NC   |     | No Connect. These pins should be left open. |

| Table 1 - Pin | Description | (continued) |

|---------------|-------------|-------------|

|---------------|-------------|-------------|

ZL30163

### 3.0 Mechanical Drawing