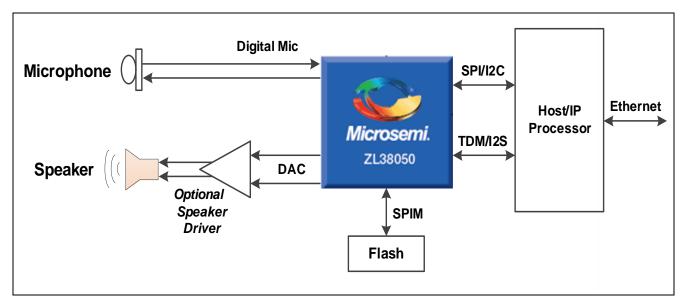

Timberwolf Digital Signal Processor family, powered by *AcuEdge*<sup>™</sup> Technology

Designed for IP and Security Cameras

ZL38050

**Preliminary Data Sheet**

#### Description

The ZL38050 is part of Microsemi's new Timberwolf audio processor family of products that feature the company's innovative *AcuEdge* acoustic technology, which is a set of highly-complex and integrated algorithms. These algorithms are incorporated into a powerful DSP platform that allow the user to extract intelligible information from the audio environment.

The Microsemi *AcuEdge* Technology ZL38050 device is ideal for IP and security camera applications. Its license-free, royalty-free intelligent audio Firmware (ZLS38050) provides Acoustic Echo Cancellation (AEC), Noise Reduction (NR) and a variety of other voice enhancements to improve both the intelligibility and subjective quality of voice in harsh acoustic environments.

Microsemi offers additional tools to speed up the product development cycle. The *MiTuner™* ZLS38508 or ZLS38508LITE GUI software packages allow a user to interactively configure the ZL38050 device. The optional *MiTuner* ZLE38470BADA Automatic Tuning Kit provides automatic tuning and easy control for manual fine tuning adjustments.

### Applications

- IP Cameras

- Security Cameras

| Document ID# 149142                                                                                                                      | Version 6                                                       | October 2015                       |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------|

| C                                                                                                                                        | <b>Drdering Information</b>                                     |                                    |

| Device OPN                                                                                                                               | Package                                                         | Packing                            |

| ZL38050LDF1<br>ZL38050LDG1<br>ZL38050UGB2                                                                                                | 64-pin QFN (9x9)<br>64-pin QFN (9x9)<br>56-ball WLCSP (3.1x3.1) | Tape & Reel<br>Tray<br>Tape & Reel |

| These packages meet RoHS 2 Directive 2011/65/EU of the European Council<br>to minimize the environmental impact of electrical equipment. |                                                                 |                                    |

# Microsemi *AcuEdge* Technology ZLS38050 Firmware

- Wideband and Narrowband Acoustic Echo Cancellation

- Full or Half duplex operation

- Supports long tail AEC (up to 256 ms) in both Narrowband and Wideband operation

- Howling detection/cancellation

- · Prevents oscillation in AEC audio path

- Non-linear echo cancellation provides higher tolerance for speaker distortions

- Advanced NR reduces background noise from the near-end speech signal using Psychoacoustic techniques

- Provisions for stereo audio mixing and stereo music record and playback (sample rate of 48 kHz) with 8 kHz or 16 kHz voice processing

- Multi-tone generation

- Various encoding/decoding options:

- 16-bit 2's complement (linear)

- G.711 A/μ law

- G.722

- Send and receive path equalizers

- 16-band for Narrowband mode

- 22-band for Wideband mode

- Comfort noise generation

- 48 kHz bypass mode

- Configurable Cross Point Switch

#### Tools

- ZLK38000 Evaluation Kit

- MiTuner<sup>™</sup> ZLS38508 and ZLS38508LITE GUI

- MiTuner<sup>™</sup> ZLE38470BADA Automatic Tuning Kit

### Timberwolf Digital Signal Processor family, powered by *AcuEdge*<sup>™</sup> Technology

Designed for IP and Security Cameras ZL38050 Preliminary Data Sheet

#### **ZL38050 Hardware Features**

- DSP with Voice Hardware Accelerators

- Dual  $\Delta\Sigma$  16-bit digital-to-analog converters (DAC)

- Sampling up to 48 kHz and internal output drivers

- Headphone amps capable of 4 single-ended or 2 differential outputs

- 32 mW output drive power into 16 ohms

- Impulse pop/click protection

- A single Digital Microphone input supporting up to 2 Microphones

- TDM port shared between PCM and Inter-IC Sound (I<sup>2</sup>S)

- Performs sample rate conversions

- SPI or I<sup>2</sup>C Slave port for host processor interface

- General purpose UART port for debug

- Master SPI port for serial Flash interface

- Boots from SPI or Flash

- Can run unattended (controllerless), selfbooting into a configured operational state

- Flash firmware can be updated from SPI Slave

- Crystal-less operation (with a valid TDM clock)

- 14 General Purpose Input/Output (GPIO) pins

- 2 low power modes controlled by reset

- Available in miniature Wafer Level Chip Scale

Package

#### Performance

- AEC Tail Length: 256 ms

- AEC sampling rate: 8 and 16 kHz

- Single-Talk Weighted Terminal Coupling Loss (TCLw): > 60 dB

- Double-Talk TCLw: > 40 dB

- Double-Talk Attenuation: < 3 dB</li>

- Noise reduction up to 30 dB

## The *MiTuner*<sup>™</sup> Automatic Tuning Kit and ZLS38508 MiTuner GUI

Microsemi's Automatic Tuning Kit option includes:

- Audio Interface Box hardware

- Microphone and Speaker

- ZLS38508 MiTuner GUI software

- Allows tuning of Microsemi's AcuEdge

Technology Audio Processor

The ZLS38508 software features:

- Auto Tuning and Subjective Tuning support

- Allows tuning of key parameters of the system design

- Provides visual representations of the audio paths with drop-down menus to program parameters, allowing:

- Control of the audio routing configuration

- Programming of key building blocks in the transmit (Tx) and receive (Rx) audio paths

- · Setting analog and digital gains

- Configuration parameters allow users to "fine tune" the overall performance

## **Table of Contents**

| 1.0 ZL38050 Device Overview          |    |

|--------------------------------------|----|

| 2.0 Audio Interfaces                 | 10 |

| 2.1 Digital Microphone Interface     | 10 |

| 2.1.1 Digital Microphone Connections | 10 |

| 2.1.2 Analog Microphone Use.         | 11 |

| 2.2 DAC Output                       | 12 |

| 2.2.1 DAC Bias Circuit               | 12 |

| 2.2.2 Output Driver Configurations   | 13 |

| 3.0 Digital Interfaces               |    |

| 3.1 TDM Interface                    |    |

| 3.1.1 I2S Mode                       | 15 |

| 3.1.2 PCM Mode                       |    |

| 3.1.3 GCI Mode                       |    |

| 3.2 Cross Point Switch               |    |

| 3.3 Host Bus Interface               |    |

| 3.3.1 SPI Slave                      |    |

| 3.3.2 I2C Slave                      |    |

| 3.3.3 UART                           |    |

| 3.3.4 Host Interrupt Pin             |    |

| 3.4 Master SPI.                      |    |

| 3.4.1 Flash Interface                |    |

| 3.4.1.1 Flash Selection              |    |

| 3.5 GPIO                             |    |

| 4.0 Reset                            |    |

| 5.0 Power Supply                     |    |

| 5.1 Power Supply Sequencing/Power up |    |

| 5.1.1 Power Supply Considerations    |    |

| 5.1.1.1 External +1.2 V Power        |    |

| 5.1.1.2 Internal +1.2 V Power.       |    |

| 5.1.1.3 Ultra-Low Power Mode         |    |

| 6.0 Device Booting                   |    |

| 6.1 Boot Loader                      |    |

| 6.2 Bootstrap Modes                  |    |

| 6.3 Loadable Device Code             |    |

| 6.3.1 Boot Speed                     |    |

| 6.4 Bootup Procedure                 |    |

| 7.0 Device Pinouts                   |    |

| 7.1 64-Pin QFN                       |    |

| 7.2 56-Ball WLCSP                    |    |

|                                      |    |

| 8.0 Pin Descriptions.                |    |

| 9.0 Electrical Characteristics       |    |

| 9.1 Absolute Maximum Ratings.        |    |

| 9.2 Thermal Resistance.              |    |

| 9.3 Operating Ranges                 |    |

| 9.4 Device Operating Modes           |    |

| 9.4.1 Normal                         |    |

| 9.4.2 Low-Power                      |    |

| 9.4.3 Sleep                          |    |

| 9.4.4 Reset                          |    |

| 9.4.5 Ultra-Low Power.               |    |

| 9.4.6 Current Consumption            | 44 |

## **Table of Contents**

| 9.5 DC Specifications                                    | 45 |

|----------------------------------------------------------|----|

| 9.6 AC Specifications                                    | 45 |

| 9.6.1 Microphone Interface                               | 45 |

| 9.6.2 DAC                                                | 46 |

| 9.7 External Clock Requirements                          | 48 |

| 9.7.1 Crystal Application                                |    |

| 9.7.2 Clock Oscillator Application.                      |    |

| 9.7.3 PCLK (Crystal-less) Application                    |    |

| 9.7.4 AC Specifications - External Clocking Requirements |    |

| 10.0 Timing Characteristics                              | 50 |

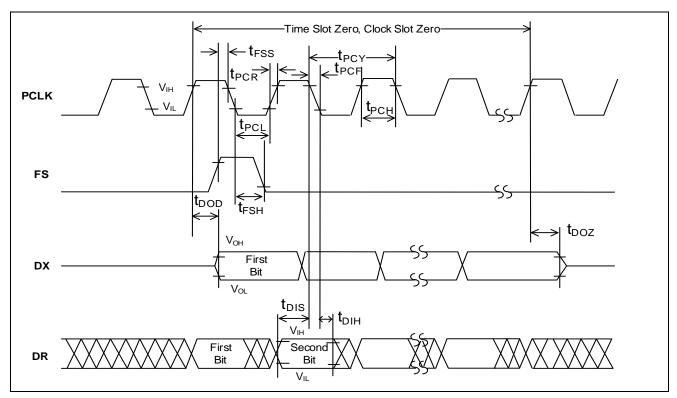

| 10.1 TDM Interface Timing Parameters                     | 51 |

| 10.1.1 GCI and PCM Timing Parameters                     | 51 |

| 10.1.2 I2S Timing Parameters                             | 54 |

| 10.1.2.1 I2S Slave                                       | 54 |

| 10.1.2.2 I2S Master                                      | 55 |

| 10.2 Host Bus Interface Timing Parameters                | 56 |

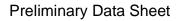

| 10.2.1 SPI Slave Port Timing Parameters                  | 56 |

| 10.2.2 I2C Slave Interface Timing Parameters             |    |

| 10.3 UART Timing Parameters                              | 58 |

| 10.4 Master SPI Timing Parameters                        | 59 |

| 11.0 AEC Tuning                                          | 60 |

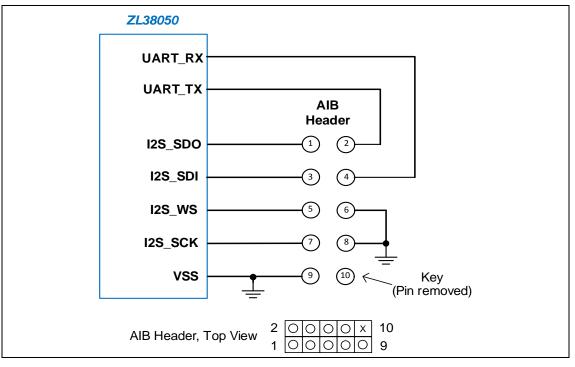

| 12.0 Package Outline Drawings                            |    |

| 13.0 Revision History                                    |    |

|                                                          |    |

## List of Figures

| Figure 1 - IP Camera HD Voice 2-way Audio Application                        |      |

|------------------------------------------------------------------------------|------|

| Figure 2 - ZL38050 Audio Processor for IP Cameras                            |      |

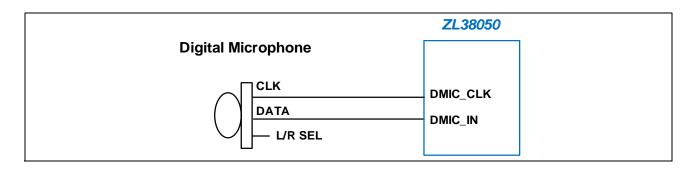

| Figure 3 - Single Mono Digital Microphone Interface                          | . 10 |

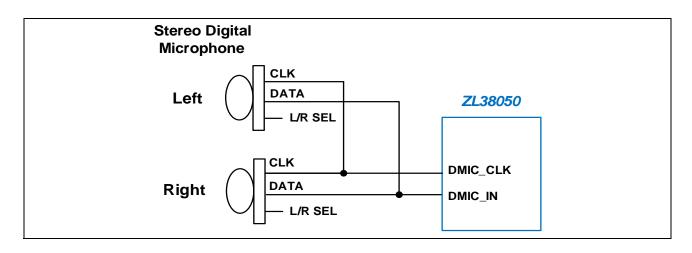

| Figure 4 - Dual Microphone or Stereo Digital Microphone Interface            | . 11 |

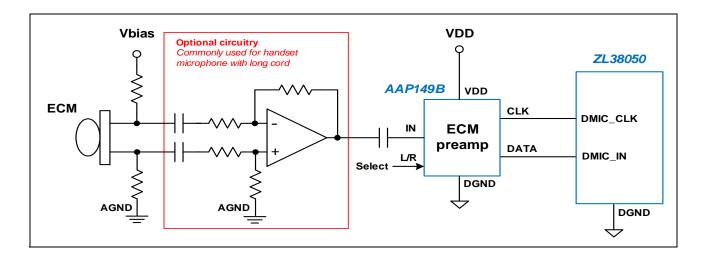

| Figure 5 - ECM Circuit                                                       | . 11 |

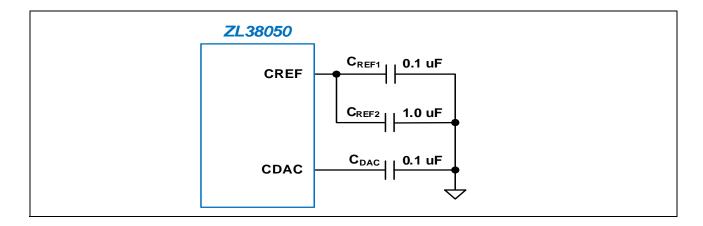

| Figure 6 - ZL38050 Bias Circuit                                              | . 12 |

| Figure 7 - Audio Output Configurations                                       | . 13 |

| Figure 8 - I2S Mode                                                          | . 15 |

| Figure 9 - Left Justified Mode.                                              | . 16 |

| Figure 10 - Dual Codec Configuration                                         |      |

| Figure 11 - TDM - PCM Slave Functional Timing Diagram (8-bit, xeDX = 0)      |      |

| Figure 12 - TDM - PCM Slave Functional Timing Diagram (8-bit, xeDX = 1).     |      |

| Figure 13 - TDM - PCM Master Functional Timing Diagram (8-bit, xeDX = 0).    |      |

| Figure 14 - TDM - PCM Master Functional Timing Diagram (8-bit, xeDX = 1).    |      |

| Figure 15 - TDM - GCI Slave Functional Timing Diagram                        |      |

| Figure 16 - TDM - GCI Master Functional Timing Diagram                       |      |

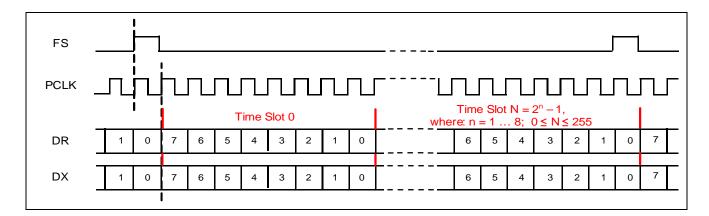

| Figure 17 - SPI Slave Byte Framing Mode - Write                              |      |

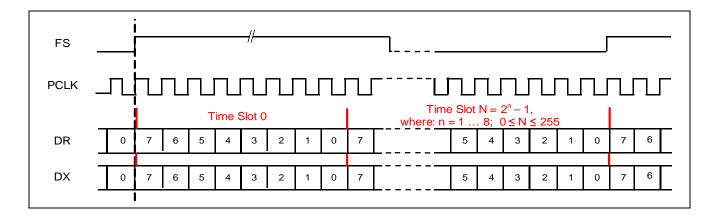

| Figure 18 - SPI Slave Byte Framing Mode - Read.                              |      |

|                                                                              |      |

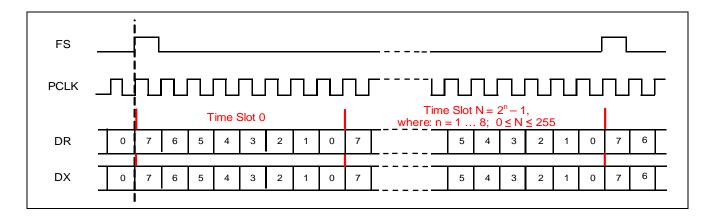

| Figure 19 - SPI Slave Word Framing Mode - Write, Multiple Data Words         |      |

| Figure 20 - SPI Slave Word Framing Mode - Read, Multiple Data Words          |      |

| Figure 21 - SPI Slave Command Framing Mode - Write                           |      |

| Figure 22 - SPI Slave Command Framing Mode - Read                            |      |

| Figure 23 - Flash Interface Circuit                                          |      |

| Figure 24 - External +1.2 V Power Supply Configuration                       | . 29 |

| Figure 25 - Internal +1.2 V Power Supply Configuration                       |      |

| Figure 26 - Ultra-Low Power Operation Circuit                                |      |

| Figure 27 - ZL38050 64-Pin QFN - Top View                                    | . 34 |

| Figure 28 - ZL38050 56-Ball WLCSP - Top View                                 | . 35 |

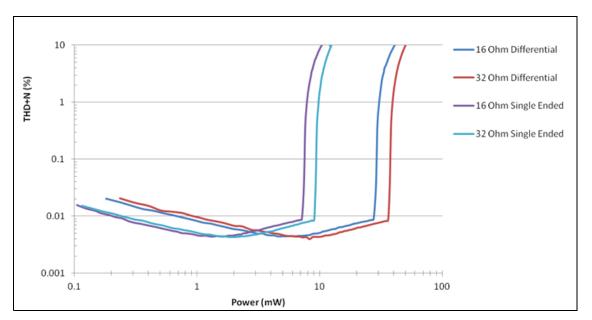

| Figure 29 - THD+N Ratio versus Output Power - Driving Low Impedance          | . 47 |

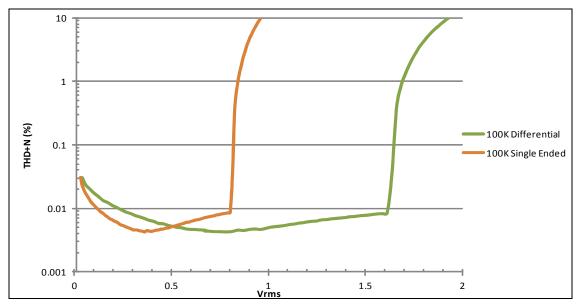

| Figure 30 - THD+N Ratio versus VRMS - Driving High Impedance                 | . 47 |

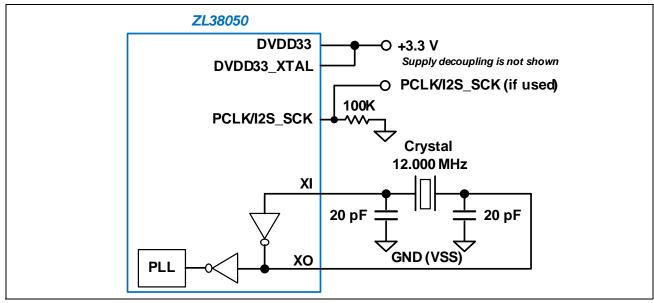

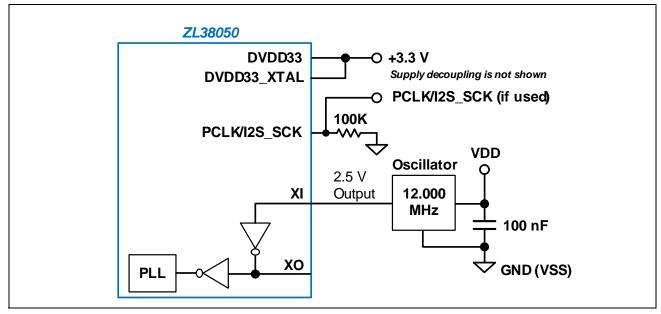

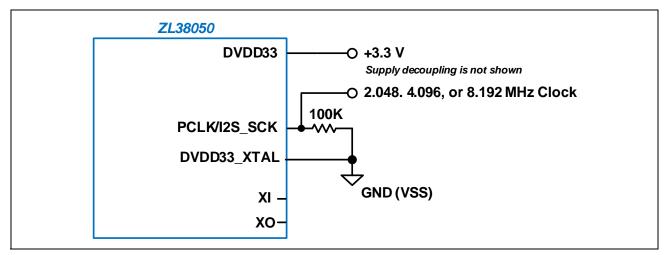

| Figure 31 - Crystal Application Circuit                                      | . 48 |

| Figure 32 - Clock Oscillator Application Circuit                             | . 49 |

| Figure 33 - Crystal-less Application Circuit                                 | . 49 |

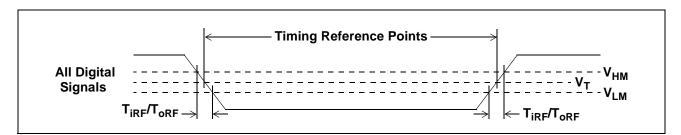

| Figure 34 - Timing Parameter Measurement Digital Voltage Levels              |      |

| Figure 35 - GCI Timing, 8-bit                                                |      |

| Figure 36 - PCM Timing, 8-bit with xeDX = 0 (Transmit on Negative PCLK Edge) |      |

| Figure 37 - PCM Timing, 8-bit with xeDX = 1 (Transmit on Positive PCLK Edge) |      |

| Figure 38 - Slave I2S Timing                                                 |      |

| Figure 39 - Master I2S Timing                                                |      |

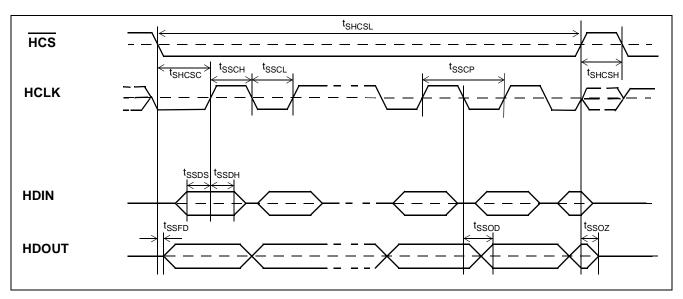

| Figure 40 - SPI Slave Timing                                                 |      |

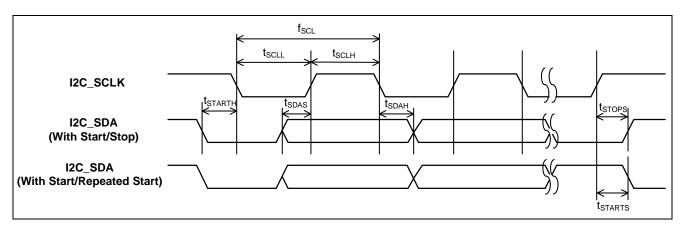

| Figure 41 - I2C Timing Parameter Definitions                                 |      |

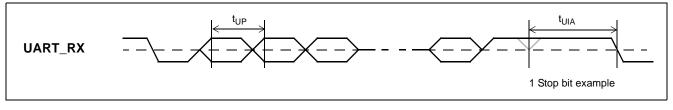

| Figure 42 - UART_RX Timing                                                   |      |

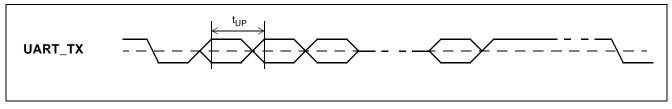

| Figure 43 - UART_TX Timing                                                   |      |

|                                                                              |      |

| Figure 44 - Master SPI Timing                                                |      |

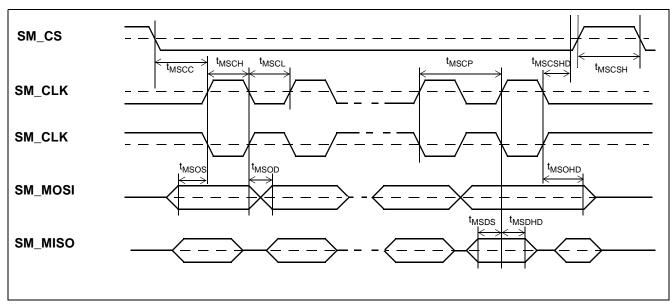

| Figure 45 - AIB System Board Connection                                      |      |

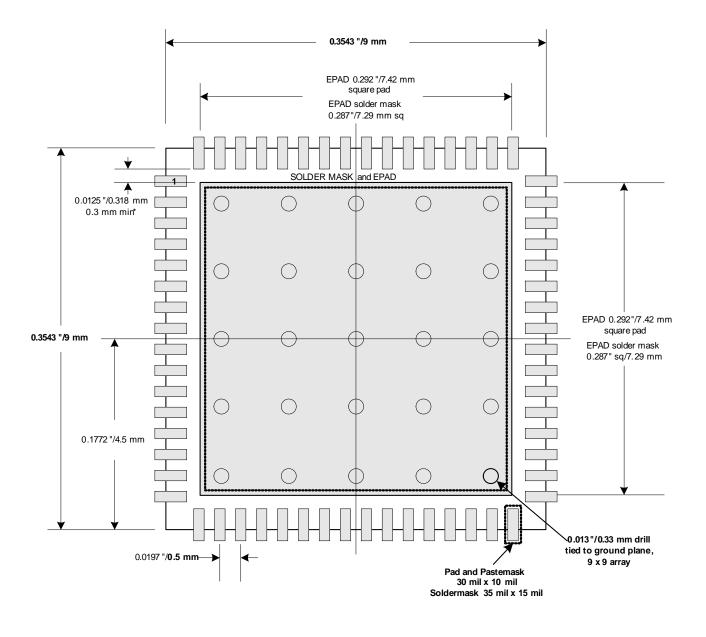

| Figure 46 - 64-Pin QFN                                                       |      |

| Figure 47 - Recommended 64-Pin QFN Land Pattern - Top View                   |      |

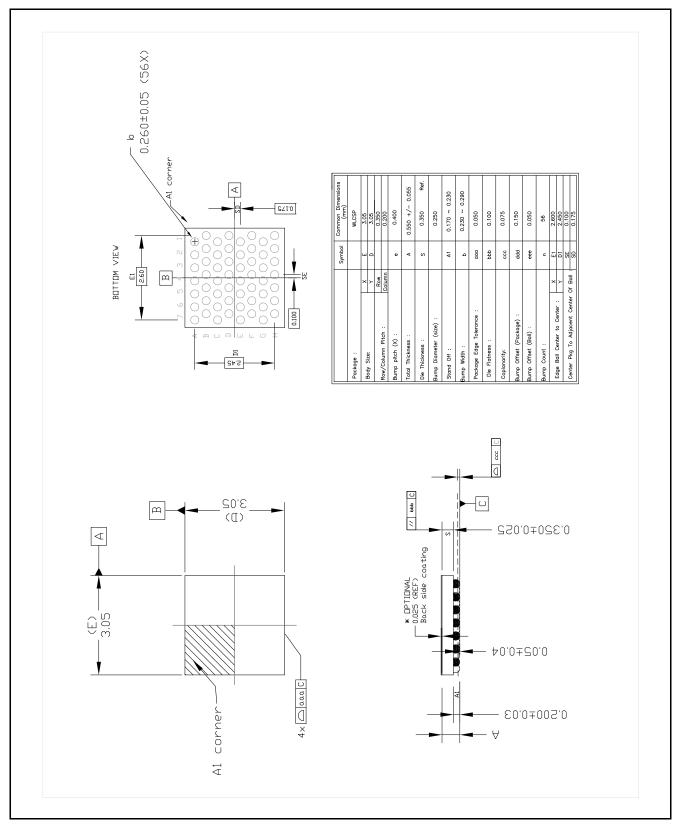

| Figure 48 - 56-Ball WLCSP                                                    | . 63 |

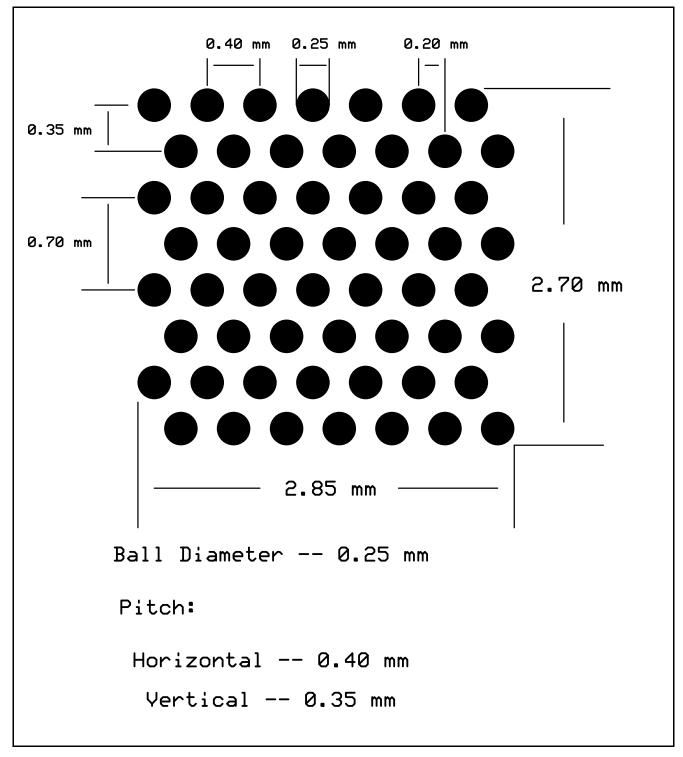

| Figure 49 - 56-Ball WLCSP Staggered Balls Expanded Bottom View | Figure 49 · | 56-Ball WLCSP Staggered Balls | Expanded Bottom | View |  | 64 |

|----------------------------------------------------------------|-------------|-------------------------------|-----------------|------|--|----|

|----------------------------------------------------------------|-------------|-------------------------------|-----------------|------|--|----|

## List of Tables

| 14 |

|----|

| 20 |

| 25 |

| 26 |

| 30 |

| 32 |

| 36 |

| 36 |

| 36 |

| 37 |

| 38 |

| 39 |

| 39 |

| 40 |

| 40 |

| 41 |

| 41 |

| 65 |

|    |

#### 1.0 ZL38050 Device Overview

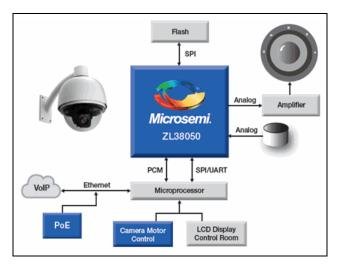

The Microsemi ZL38050 Audio Processor powered by ZLS38050 AcuEdge™ Technology Firmware is ideal for providing high definition audio to IP cameras. A typical IP Camera application is presented in Figure 1.

Figure 1 - IP Camera HD Voice 2-way Audio Application

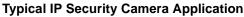

The main functional blocks of the ZL38050 device are shown in Figure 2, a description of each block follows.

Figure 2 - ZL38050 Audio Processor for IP Cameras

The ZL38050 provides the following peripheral audio ports:

- A digital microphone interface allowing input from 1 or 2 digital microphones

- 2 independent headphone drivers

- Dual 16-bit digital-to-analog converters (DACs)

- 16 ohms single-ended or differential drive capability

- 32 mW output drive power into 16 ohms

The ZL38050 provides the following peripheral digital ports:

- SPI The device provides two Serial Peripheral Interface (SPI) ports

- The SPI Slave port is recommended as the main communication port with a host processor. The port provides the fastest means to Host Boot and configure the device's firmware and configuration record\*.

- The Master SPI port is used to Auto Boot and load the device's firmware and configuration record from external Flash memory

- I<sup>2</sup>C The device provides one Inter-Integrated Circuit (I<sup>2</sup>C) port. (pins are shared with the SPI Slave port)

- The I<sup>2</sup>C port can be used as the main communication port with a host processor, and can be used to Host Boot and configure the device's firmware and configuration record

- TDM The device provides a Time-Division Multiplexing (TDM) bus

- The port can be configured for Inter-IC Sound (I<sup>2</sup>S) or Pulse-Code Modulation (PCM) operation

- PCM operation supports PCM and GCI timing, I<sup>2</sup>S operation supports I<sup>2</sup>S and left justified timing

- The port can be a clock master or a slave

- The port supports up to four bi-directional streams when configured in PCM mode or two bi-directional streams when configured for I<sup>2</sup>S mode at data rates from 128 kb/s to 8 Mb/s

- Sample rate conversions are automatically done when the TDM port data is sent/received at different rates than is processed internally

- UART The device provides one Universal Asynchronous Receiver/Transmitter (UART) port

- The UART port can be used as a debug tool and is used for tuning purposes

- GPIO The device provides 14 General Purpose Input/Output (GPIO) ports

- GPIO ports can be used for interrupt and event reporting, fixed function control, bootstrap options, as well as being used for general purpose I/O for communication and controlling external devices

\* Note: The configuration record is a set of register values that are customizable by the application developer to configure and tune the ZL38050 for a particular design. Refer to the Microsemi AcuEdge<sup>™</sup> Technology ZLS38050 Firmware Manual for firmware and configuration record information.

#### 2.0 Audio Interfaces

#### 2.1 Digital Microphone Interface

The ZL38050 can support one or two digital microphones using the DMIC\_CLK and DMIC\_IN interface pins.

The ZL38050 digital microphone clock output (DMIC\_CLK) is either 1.024 MHz or 3.072 MHz depending on the selected TDM sample rate. Selecting an 8 kHz or 16 kHz TDM sample rate corresponds to a 1.024 MHz digital microphone clock and selecting a 48 kHz sample rate corresponds to a 3.072 MHz digital microphone clock. Microphone data is decimated and filtered to operate at the 16 kHz sampling rate of the Audio Processing block. When there is no TDM bus to set the sample rate, the ZL38050 will operate from the crystal and will pass digital audio from the microphones operating at a 48 kHz sampling rate.

Of the two microphone audio paths, only one may be routed to the voice processing algorithms at a time. The other may be routed to the TDM bus for use by the host or an external Codec. Alternatively the host processor could switch different microphones to the voice processing inputs. AEC is performed only on the microphone selected to go to the ZL38050 voice processing section.

Electret condenser microphones can be used with the digital microphone interface by using a Digital Electret Microphone Pre-Amplifier device as shown in <u>Figure 5</u>. External Codecs can also be used to connect to analog microphones. The external Codecs would interface to the ZL38050 via the TDM buses.

#### 2.1.1 Digital Microphone Connections

The digital microphone interface uses 2 pins (DMIC\_CLK and DMIC\_IN) to interface with digital microphones.

A stereo digital microphone, or two separate mono digital microphones, send two microphone channels on one pin by sending the data for one channel on the rising edge and one channel on the falling edge. The selection as to which clock edge is used to clock in the microphone data (rising/falling) is done via the Microphone Enable Configuration register (host writable over the HBI) or in the configuration record (loaded from Flash).

Mono and stereo digital microphone interfaces are presented in Figure 3 and Figure 4.

Figure 3 - Single Mono Digital Microphone Interface

#### Figure 4 - Dual Microphone or Stereo Digital Microphone Interface

#### 2.1.2 Analog Microphone Use

To use analog electret condenser microphones (ECM) with the digital microphone interface, a Digital Electret Microphone Pre-Amplifier device is required. <u>Figure 5</u> illustrates an analog microphone connection.

The analog microphone is wired to an optional differential amplifier which amplifies and converts the microphone signal to single-ended. The microphone signals are then further amplified and digitized through the Digital Electret Microphone Pre-Amplifiers and applied to the ZL38050 digital microphone input. A Microsemi AAP149B ECM Pre-Amplifier is shown.

The ZL38050 provides the clock to activate the Digital Electret Microphone Pre-Amplifier.

#### Figure 5 - ECM Circuit

When using an analog microphone, operation in Low-Power mode is not recommended. For more information, see <u>9.4, "Device Operating Modes" on page 43</u>.

#### 2.2 DAC Output

The ZL38050 has two 16-bit fully differential delta-sigma digital-to-analog converters. The two output DACs independently drive an analog output subsystem. Each subsystem is able to drive two output pins, representing four independent single-ended headphone outputs that can be driven by two independent data streams. The pins can be independently configured. Four analog gains on each headphone output are provided and can be set to: 1x, 0.5x, 0.333x, or 0.25x.

Note: Only the positive DAC outputs are available with the 56-ball WLCSP package. The 56-ball WLCSP package provides two independent single-ended headphone outputs that can be driven by two independent data streams.

The headphone amplifiers are self-protecting so that a direct short from the output to ground or a direct short across the terminals does not damage the device.

The ZL38050 provides audible pop suppression which reduces pop noise in the headphone earpiece when the device is powered on/off or when the device channel configurations are changed. This is especially important when driving a headphone single-ended through an external capacitor (see <u>2.2.2</u>, <u>"Output Driver Configurations"</u>, configuration C).

The DACs and headphone amplifiers can be powered down if they are not required for a given application. To fully power down the DACs, disable both the positive and negative outputs.

#### 2.2.1 DAC Bias Circuit

The common mode bias voltage output signal (CREF) for the DAC output buffers must be decoupled through a 0.1  $\mu$ F (C<sub>REF1</sub>) and a 1.0  $\mu$ F (C<sub>REF2</sub>) ceramic capacitor to VSS. The positive DAC reference voltage output (CDAC) must be decoupled through a 0.1  $\mu$ F (C<sub>DAC</sub>) ceramic capacitor to VSS as shown in <u>Figure 6</u>.

All capacitors can have a 20% tolerance and should have a minimum voltage rating of 6.3 V.

Figure 6 - ZL38050 Bias Circuit

#### 2.2.2 Output Driver Configurations

Microsemi

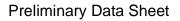

Figure 7 shows the different possible output driver configurations for the 64-pin QFN package. When using the 56-ball WLCSP package, only the positive outputs DAC1\_P and DAC2\_P are provided.

The two output DACs independently drive positive and negative headphone driver amplifiers. The output pins can be independently configured in the following ways:

- A. 64-pin QFN Direct differential drive of a speaker as low as 32 ohms. For this configuration an analog gain of 1x is commonly used. (Differentially driving a 16 ohm speaker is possible, but only with the same amount of power as in the single-ended case. The signal level must be reduced to not exceed ½ scale in this case.)

- B. 64-pin QFN Direct differential drive of a high impedance power amplifier. A Class D amplifier is recommended for this speaker driver. Use an ON Semiconductor<sup>®</sup> NCP2820 or equivalent. A 1 μF coupling capacitor is generally used with the Class D amplifier. The analog gain setting depends on the gain of the Class D amplifier, analog gain settings of 0.25x or 0.5x are commonly used.

- C. Both packages Driving either a high impedance or a capacitively coupled speaker as low as 16 ohms single-ended. For this configuration an analog gain of 1x is commonly used. The coupling capacitor value can vary from 10 µf to 100 µf depending on the type of earpiece used and the frequency response desired.

Figure 7 - Audio Output Configurations

#### 3.0 Digital Interfaces

#### 3.1 TDM Interface

The ZL38050 device has one generic TDM interface. This port can be used for  $I^2S$  or PCM transmissions. The interface consists of four signals:

- Data clock (PCLK/I2S\_SCK)

- Data rate sync (FS/I2S\_WS)

- Serial data input (DR/I2S\_SDI)

- Serial data output (DX/I2S\_SDO)

The TDM port can be configured for Inter-IC Sound (I<sup>2</sup>S) or Pulse-Code Modulation (PCM) operation.

The TDM block is capable of being a master or a slave.

Operation of the TDM interface is subject to the following limitations.

Table 1 - Allowable TDM Configurations

| TDM Mode           | Supported<br>Sample Rates<br>(kHz) |

|--------------------|------------------------------------|

| Master             | 8, 16, 48 <sup>1</sup>             |

| Slave <sup>1</sup> | 0, 10, 10                          |

Note 1: The device can be run without a crystal when the TDM is a slave. However, this mode requires that the PCLK and FS signals are always present and PCLK must be an integer multiple of 2.048 MHz. For crystal-less operation at power-on, PCLK will be auto-detected with only 8 kHz and 16 kHz frame syncs being allowed.

While a TDM bus configuration may carry many encoded audio streams, the ZL38050 device can only address a maximum of 4 bi-directional audio streams. These four audio streams are referred to as channels #1 through #4, and each of these channels can be independently configured to decode any of the TDM bus's audio streams.

Once the TDM bus is configured for a data sample rate and encoding, all data rates and encoding on the bus will be the same. Linear data will be sent on consecutive timeslots (e.g., if timeslot N is programmed in the timeslot registers, the consecutive timeslot is N+1).

The TDM interface supports bit reversal (LSB first <- -> MSB first) and loopbacks within the TDM interface and from one interface to another (see <u>"Cross Point Switch" on page 19</u>).

The generic TDM interface supports the following mode and timing options.

#### 3.1.1 I<sup>2</sup>S Mode

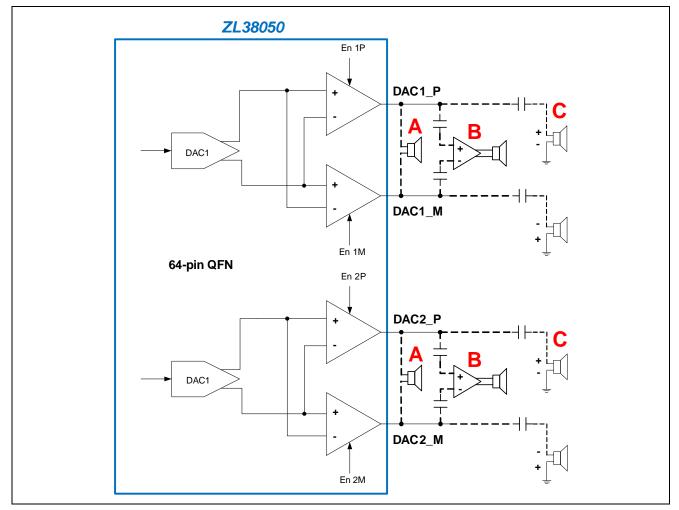

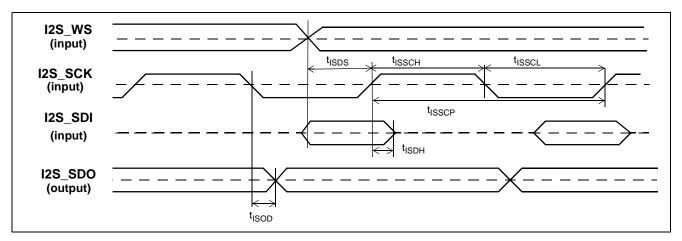

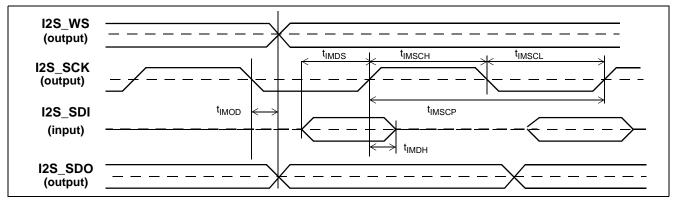

In I<sup>2</sup>S mode, the 4-wire TDM port conforms to the I<sup>2</sup>S protocol and the port pins become I2S\_SCK, I2S\_WS, I2S\_SDI, and I2S\_SDO (refer to <u>Table 10</u> for pin definitions). Both TDM buses have I<sup>2</sup>S capability.

An I<sup>2</sup>S bus supports two bi-directional data streams, left and right channel, by using the send and receive data pins utilizing the common clock and word signals. The send data is transmitted on the I2S\_SDO line and the receive data is received on the I2S\_SDI line.

The I<sup>2</sup>S port can be used to connect external analog-to-digital converters or Codecs. The port can operate in master mode where the ZL38050 is the source of the port clocks, or slave mode where the word select and serial clocks are inputs to the ZL38050.

The word select (I2S\_WS) defines the  $I^2S$  data rate and sets the frame period when data is transmitted for the left and right channels. A frame consists of one left and one right audio channel. The  $I^2S$  ports operate at 8, 16, and 48 kHz data rates as a slave or master (as specified in <u>Table 1</u>). Per the  $I^2S$  standard, the word select is output using a 50% duty cycle.

The serial clock (I2S\_SCK) rate sets the number of bits per word select frame period and defines the frequency of I2S\_CLK. I<sup>2</sup>S data is input and output at the serial clock rate. Input data bits are received on I2S\_SDI and output data bits are transmitted on I2S\_SDO. Data bits are always MSB first. The number of clock and data bits per frame can be programmed as 8, 16, 32, 64, 96, 128, 192, 256, 384, 512, or 1024. Any input data bits that are received after the LSB are ignored.

The I<sup>2</sup>S port operates in two frame alignment modes (I<sup>2</sup>S and Left justified) which determine the data start in relation to the word select.

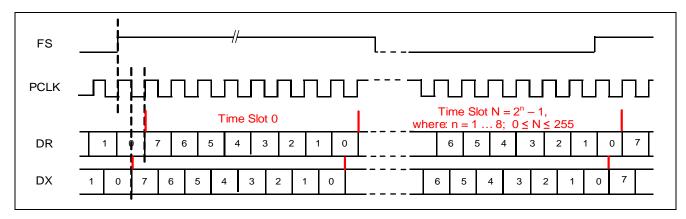

Figure 8 illustrates the I<sup>2</sup>S mode, which is left channel first with I2S\_WS (Left/Right Clock signal) low, followed by the right channel with I2S\_WS high. The MSB of the data is clocked out starting on the second falling edge of I2S\_SCK following the I2S\_WS transition and clocked in starting on the second rising edge of I2S\_SCK following the I2S\_WS transition. Figure 8 shows I<sup>2</sup>S operation with 32 bits per frame.

Figure 8 - I<sup>2</sup>S Mode

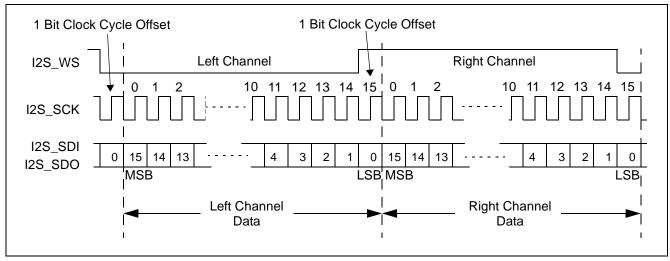

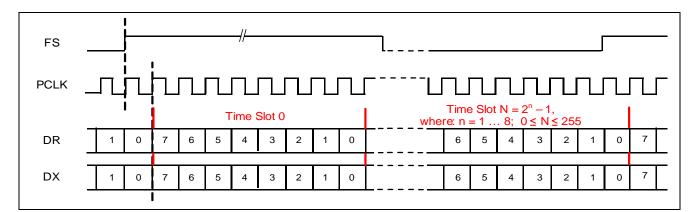

<u>Figure 9</u> illustrates the left justified mode, which is left channel first associated with I2S\_WS (Left/Right Clock signal) high, followed by the right channel associated with I2S\_WS low. The MSB of the data is clocked out starting on the falling edge of I2S\_SCK associated with the I2S\_WS transition, and clocked in starting on the first rising edge of I2S\_SCK following the I2S\_WS transition.

Figure 9 - Left Justified Mode

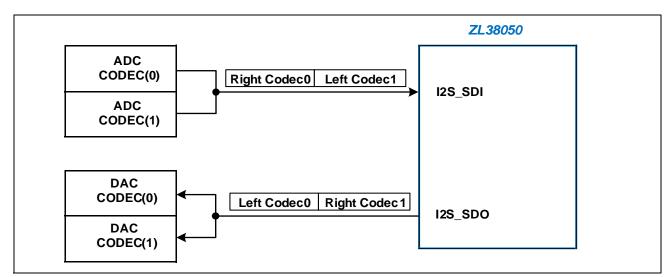

Each  $I^2S$  interface can support one dual channel Codec (Figure 10) through the Codec's  $I^2S$  interface. The four 16bit channel processing capacity of the DSP is spread across the two input channels from the ADCs of Codec(0) and Codec(1), and the two output channels to the DACs of Codec(0) and Codec(1).

Figure 10 - Dual Codec Configuration

Both I<sup>2</sup>S bus modes can support full bi-directional stereo communication.

The device supports  $I^2S$  loopback.

See the Microsemi AcuEdge™ Technology ZLS38050 Firmware Manual for I<sup>2</sup>S port registers.

#### 3.1.2 PCM Mode

Each of the PCM channels can be assigned an independent timeslot. The timeslots can be any 8-bit timeslot up to the maximum supported by the PCLK being used. The PCM port can be configured for Narrowband G.711 A-law/ $\mu$ -Law or Linear PCM or Wideband G.722 encoding. When the TDM bus is configured for a data sample rate and encoding, all data rates and encoding will be the same. 16-bit linear PCM will be sent on consecutive 8-bit timeslots (e.g., if timeslot N is programmed in the timeslot registers, the consecutive timeslot is N+1). The PCM interface can transmit/receive 8-bit compressed or 16-bit linear data with 8 kHz sampling (narrowband), or 16-bit linear data with 16 kHz sampling (wideband).

Wideband audio usually means the TDM bus is operating at a 16 kHz FS, but there are two other operating modes that support wideband audio using an 8 kHz FS:

- G.722 supports wideband audio with an 8 kHz FS. This uses a single 8-bit timeslot on the TDM bus.

- "Half-FS Mode" supports wideband audio with an 8 kHz FS signal. In this mode, 16-bit linear audio is received on two timeslot pairs; the first at the specified timeslot (N, N+1) and the second a half-frame later. In total, four 8-bit timeslots are used per frame, timeslots (N, N+1) and ((N + ((bits\_per\_frame)/16))), (N + 1 + ((bits\_per\_frame)/16))). The user programs the first timeslot and the second grouping is generated automatically 125/2 µs from the first timeslot.

The PCM voice/data bytes can occupy any of the available timeslots, except for PCM clock rates that have extra clocks in the last timeslot. If there is more than one extra clock in the last timeslot, the timeslot data will be corrupted, do not use the last timeslot for these clock frequencies (e.g., 3.088 MHz etc.).

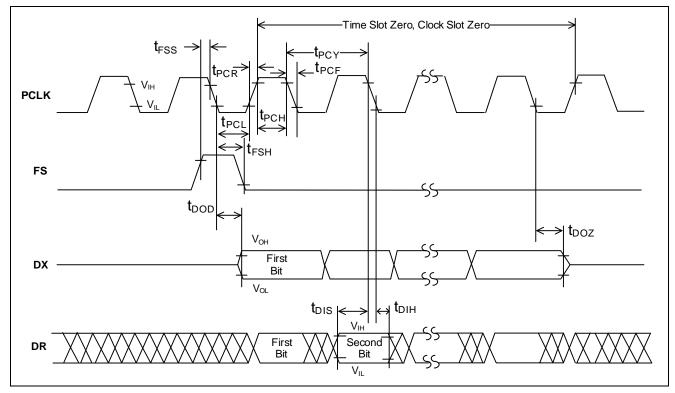

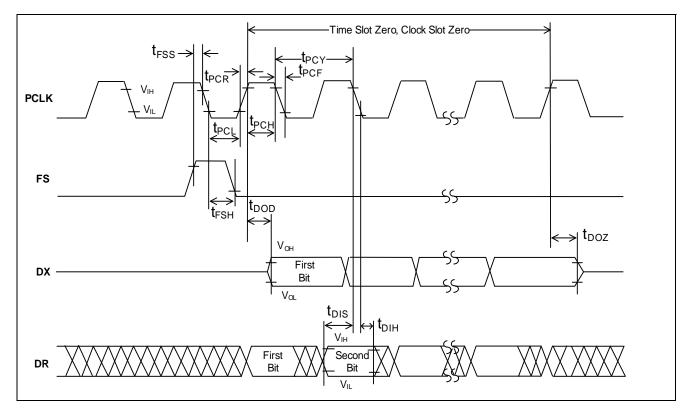

The PCM block can be configured as a master or a slave and is compatible with the Texas Instruments Inc. McBSP mode timing format.

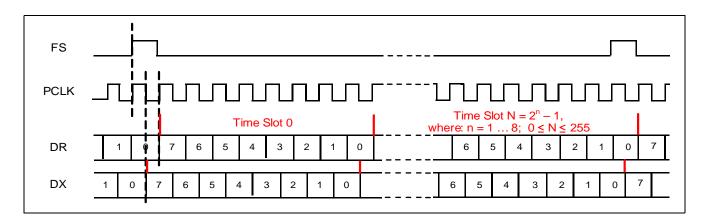

Figure 11 and Figure 12 illustrate the PCM format with slave timing, FS and PCLK are provided by the host. Slave mode accommodates frame sync pulses with various widths (see <u>"GCI and PCM Timing Parameters" on page 51</u>).

Figure 13 and Figure 14 illustrate the PCM format with master timing, FS and PCLK are provided by the ZL38050. Master mode outputs a frame sync pulse equal to one PCLK cycle.

Diagrams for PCM transmit on negative edge (xeDX = 0) and PCM transmit on positive edge (xeDX = 1) are shown for both slave and master timing.

Figure 11 - TDM – PCM Slave Functional Timing Diagram (8-bit, xeDX = 0)

Figure 12 - TDM – PCM Slave Functional Timing Diagram (8-bit, xeDX = 1)

Figure 13 - TDM – PCM Master Functional Timing Diagram (8-bit, xeDX = 0)

Figure 14 - TDM – PCM Master Functional Timing Diagram (8-bit, xeDX = 1)

#### 3.1.3 GCI Mode

The GCI voice/data bytes can occupy any of the available timeslots. The GCI block can be configured as a master or a slave and supports a clock that has the same frequency as the data rate.

Note: Traditional GCI Monitor, Signalling, and Control channel bytes and double data rate are not supported.

<u>Figure 15</u> illustrates the GCI format with slave timing, FS and PCLK are provided by the host. Slave mode accommodates frame sync pulses with various widths (see <u>"GCI and PCM Timing Parameters" on page 51</u>).

Figure 16 illustrates the GCI format with master timing, FS and PCLK are provided by the ZL38050. Master mode outputs a frame sync pulse equal to one PCLK cycle.

For both, first data bits are aligned with the rising edge of the frame sync pulse.

Figure 15 - TDM – GCI Slave Functional Timing Diagram

#### Figure 16 - TDM – GCI Master Functional Timing Diagram

#### 3.2 Cross Point Switch

The ZL38050 contains a Cross Point Switch that allows any input port to be routed to any output port as well as routing the input/outputs to/from the audio processor functions. Refer to the *Microsemi AcuEdge*<sup>TM</sup> *Technology ZLS38050 Firmware Manual* for Cross Point Switch operation and control.

#### 3.3 Host Bus Interface

The host bus interface (HBI) is the main communication port from a host processor to the ZL38050. It can be configured to be either a SPI Slave or an  $I^2C$  Slave port, either of which can be used to program or query the device.

The ZL38050 allows for automatic configuration between SPI and I<sup>2</sup>C operation. For the HBI port, if the HCLK toggles for two cycles, the HBI will default to the SPI Slave, otherwise it will remain configured as I<sup>2</sup>C (see <u>Table 2</u>). The HBI comes up listening in both SPI and I<sup>2</sup>C modes, but with I<sup>2</sup>C inputs selected. If HCLK is present, it switches the data selection before the first byte is complete so that no bits are lost. Once the port is determined to be SPI, a hardware reset is needed to change back to I<sup>2</sup>C.

This port can read and write all of the memory and registers on the ZL38050. The port can also be used to boot the device, refer to <u>"Device Booting" on page 32</u>.

Table 2 - HBI Slave Interface Selection

| Description                    | Condition           | Operating Mode                                        | Notes |

|--------------------------------|---------------------|-------------------------------------------------------|-------|

| HBI Slave interface selection. | HCLK toggling       | Host SPI bus                                          |       |

|                                | HDIN tied to VSS    | Host I <sup>2</sup> C bus. Slave address 45h (7-bit). |       |

|                                | HDIN tied to DVDD33 | Host I <sup>2</sup> C bus. Slave address 52h (7-bit). | 1     |

Note 1: By default, the HBI comes up as an I<sup>2</sup>C interface. Toggling the HCLK pin will cause the host interface to switch to a SPI interface. If an I<sup>2</sup>C interface is desired, HCLK needs to be tied to ground.

#### 3.3.1 SPI Slave

The physical layer is a 4-wire SPI interface. Chip select and clock are both inputs.

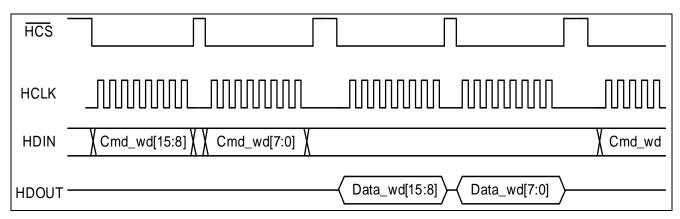

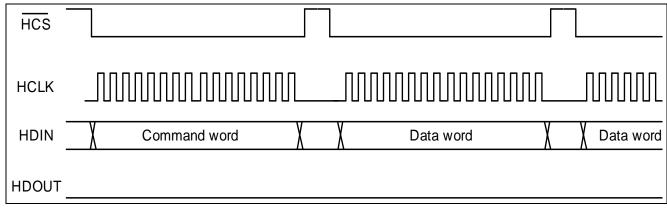

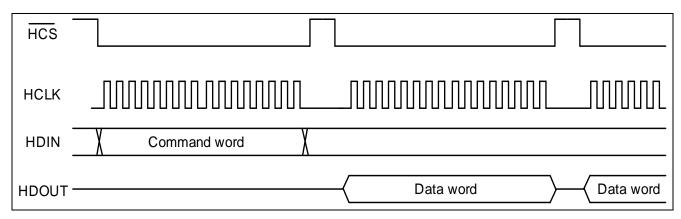

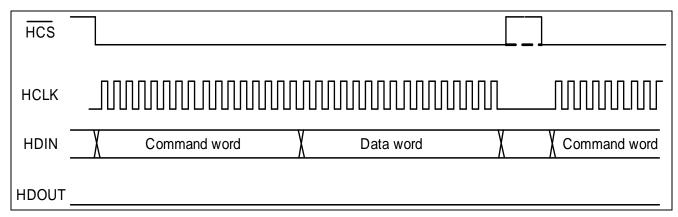

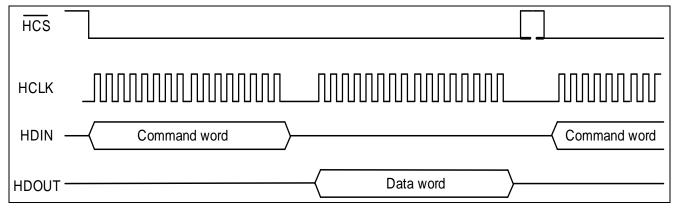

The SPI Slave port can support byte, word, or command framing. Write and read diagrams for these framing modes are shown in Figure 17 – Figure 22. The SPI Slave chip select polarity, clock polarity, and sampling phase are fixed.

The ZL38050 command protocol is half duplex, allowing the serial in and serial out to be shorted together for a 3wire connection. The chip select is active low. The data is output on the falling edge of the clock and sampled on the rising edge of the clock.

The SPI Slave supports access rates up to 25 MHz.

The outbound interrupt is always active low.

| HCS   |                                |                                    | 1      |

|-------|--------------------------------|------------------------------------|--------|

| HCLK  |                                |                                    |        |

| HDIN  | Cmd_wd[15:8] X X Cmd_wd[7:0] X | X Data_wd[15:8] X X Data_wd[7:0] X | Cmd_wd |

| HDOUT |                                |                                    |        |

Figure 18 - SPI Slave Byte Framing Mode – Read

Figure 19 - SPI Slave Word Framing Mode – Write, Multiple Data Words

Figure 20 - SPI Slave Word Framing Mode – Read, Multiple Data Words

Figure 21 - SPI Slave Command Framing Mode – Write

Figure 22 - SPI Slave Command Framing Mode – Read

#### 3.3.2 I<sup>2</sup>C Slave

The I<sup>2</sup>C bus is similar to the Philips Semiconductor (NXP) 1998 Version 2.0, I<sup>2</sup>C standard. The ZL38050 I<sup>2</sup>C bus supports 7-bit addressing and transfer rates up to 400 kHz. External pull-up resistors are required on the I<sup>2</sup>C serial clock input (HCS) and the I<sup>2</sup>C serial data input/output (HDOUT) when operating in this mode (note, the I<sup>2</sup>C slave pins are 3.3 V pins and are not 5 V tolerant).

The selection of the  $I^2C$  slave address is performed at bootup by the strapping of the HDIN and HCLK pins, see <u>Table 2</u>.

#### 3.3.3 UART

The ZL38050 device incorporates a two-wire UART (Universal Asynchronous Receiver Transmitter) interface with a fixed 115.2K baud transfer rate, 8 data bits, 1 stop and no parity. TX and RX pins allow bi-directional communication with a host. The UART pins must be made accessible on the PCB for debug and tuning purposes.

The UART port can be used as a debug tool and is used for tuning purposes.

#### 3.3.4 Host Interrupt Pin

An internal host interrupt controller controls the active low interrupt pin which is part of the host bus interface. Associated with the interrupt controller is an event queue which reports status information about which event caused the interrupts.

Upon sensing the interrupt, the host can read the event queue to determine which event caused the interrupt. Specific events are enabled by the host processor, and are typically not used with a standalone (controllerless) design.

Refer to Events in the *Microsemi AcuEdge™ Technology ZLS38050 Firmware Manual* for Event ID Enumerations.

#### 3.4 Master SPI

Like the HBI SPI Slave, the physical layer of the Master SPI is a 4-wire SPI interface supporting half duplex communication. It supports only one chip select which is multiplexed with GPIO\_9.

The Master SPI is only accessible through boot ROM commands and is only used as the boot loading mechanism for the external Flash. The ZL38050 can automatically read the Flash data (program code and configuration record) through this interface upon the release of reset (Auto Boot), depending on the value of the bootstrap options.

Note: An alternative to Auto Boot is to perform a Host Boot through the HBI port. Refer to 6.0, "Device Booting" on page 32.

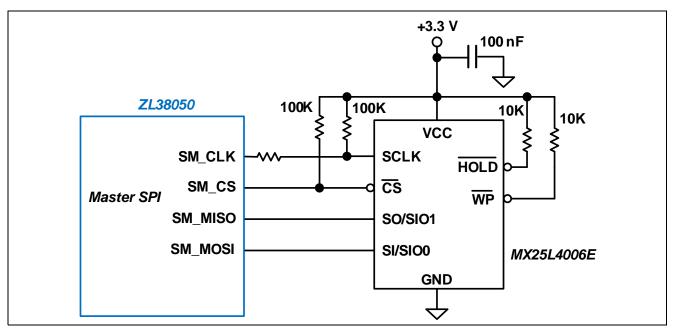

#### 3.4.1 Flash Interface

After power-up the ZL38050 will run its resident boot code, which establishes the initial setup of the Master SPI port and then downloads the firmware from external Flash memory. This Flash firmware establishes the resident application and sets the modes of all the ZL38050 ports.

<u>Figure 23</u> illustrates the connection of Flash memory to the ZL38050 Master SPI port. A 2 Mbit Flash size is all that is required to store the program code and the configuration record of the ZL38050 device. <u>Figure 23</u> and the ZLE38050 demonstration hardware uses the Macronix<sup>™</sup> MX25L4006E 4 Mbit CMOS Serial Flash device.

Figure 23 - Flash Interface Circuit

#### 3.4.1.1 Flash Selection

The ZL38050 Boot ROM is designed to work with a wide variety of Flash devices. There are numerous Flash devices that the ZL38050 Boot ROM can recognize and program without host intervention other than a command to initialize the Flash. Other unrecognized devices may be utilized if they conform to certain characteristics of known devices and the host informs the ZL38050 Boot ROM of their type and size.

The ZL38050 identifies Flash devices (with a single binary image) with the ZL38050 boot ROM auto sensing the Flash type. The ZL38050 complies with JEDEC *Manufacturer and Device ID Read Methodology for SPI Compatible Serial Interface Memory Devices.* The ZL38050 is compatible with the Serial Flash Discoverable Parameters JEDEC standard JESD216B and the Common Flash Interface JESD68.01 JEDEC standard. The ZL38050 can identify devices by their JEDEC standard JEP106-K Standard Manufacturer's Identification Code.

A list of Flash devices that are identifiable by the ZL38050 Boot ROM are shown in <u>Table 3</u>. The size of these devices are all 2 Mbit or 4 Mbit, the Boot ROM will also recognize the size of 8 Mbit parts that are Type 1 or Type 2 devices (as defined in <u>Table 4</u>).

#### Table 3 - Flash Devices Tested with the ZL38050

| Manufacturer       | Part Number              | Description                                                                                                                                                          |

|--------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Macronix™          | MX25V4006EM1I-13G        | 4 Mbit Flash.                                                                                                                                                        |

| Winbond™           | W25X40CLSNIG-ND          | 4 Mbit Flash.                                                                                                                                                        |

|                    | W25X20CLSNIG-ND          | 2 Mbit Flash.                                                                                                                                                        |

| Micron®            | M25P20-VMN6PB            | 2 Mbit Flash. Large 512 Kbit sectors limit the usefulness of this device. Holds only 1 application image.                                                            |

|                    | M25P40-VMN6PB            | 4 Mbit Flash. Large 512 Kbit sectors limit the usefulness of this device. Holds only 2 or 3 application images.                                                      |

| Microchip™         | SST25VF020B-80-4I        | 2 Mbit Flash.                                                                                                                                                        |

| Atmel®             | AT25DF041A<br>AT45DB041D | 4 Mbit Flash. Must be used in its 256 byte page variant.<br>The default configuration is a 264 byte page. It can be<br>ordered or programmed to use a 256 byte page. |

| Spansion™          | S25FL204K0TMF1010        | 4 Mbit Flash.                                                                                                                                                        |

| AMIC<br>Technology | A25L020O-F               | 2 Mbit Flash.                                                                                                                                                        |

Flash devices whose JEDEC ID or size (usually a size of 16 Mbit or larger) that are not recognized by the ZL38050 Boot ROM can be made to work if they fit the characteristics of one of the 4 Flash types listed in <u>Table 4</u>. By writing the type (1, 2, 3, or 4) to ZL38050 address 0x118 and the number of sectors to ZL38050 address 0x116 prior to initializing the Flash device, the Boot ROM will treat it as a known device of known size even though the manufacturer ID or size field are not recognized.

#### Table 4 - Supported Flash Types

| Characteristic        | Type 1                                    | Type 2                                                                                                                                                                      | Туре 3                                                                                            | Туре 4                                    |

|-----------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------|

| Sector Size           | 512 Kbit (64 KB)                          | 32 Kbit (4 KB)                                                                                                                                                              | 32 Kbit (4 KB)                                                                                    | 16 Kbit (2 KB)                            |

| Read Status Reg Cmd   | 0x05                                      | 0x05                                                                                                                                                                        | 0x05                                                                                              | 0xD7                                      |

| Status Reg            | Busy bit = 0x01                           | Busy bit = 0x01                                                                                                                                                             | Busy bit = 0x01                                                                                   | Done bit = 0x80                           |

| Data Read Cmd         | 0x03                                      | 0x03                                                                                                                                                                        | 0x03                                                                                              | 0x03                                      |

| Write Enable Cmd      | 0x06                                      | 0x06                                                                                                                                                                        | 0x06                                                                                              | N/A                                       |

| Page Write Cmd        | 0x02                                      | 0x02                                                                                                                                                                        | N/A<br>Uses AAI to program<br>word or byte. Uses<br>Write Disable<br>command to<br>terminate AAI. | N/A<br>Uses write from<br>buffer command. |

| 4-Byte Bulk Erase Cmd | N/A                                       | N/A                                                                                                                                                                         | N/A                                                                                               | 0xC794809A                                |

| Examples              | Micron®<br>M25P20-VMN6PB<br>M25P40-VMN6PB | Winbond™<br>W25X40CLSNIG-ND<br>W25X20CLSNIG-ND<br>Macronix™<br>MX25V4006EM1I-13G<br>AMIC Technology<br>A25L020O-F<br>Spansion™<br>S25FL204K0TMF1010<br>Atmel®<br>AT25DF041A | Microchip™<br>SST25VF020B-80-4I                                                                   | Atmel®<br>AT45DB021D<br>AT45DB041D        |

#### 3.5 GPIO

The ZL38050 64-pin QFN package has 14 GPIO (General Purpose Input/Output) pins; the ZL38050 56-ball WLCSP package has 11 GPIO pins.

The GPIO can be individually configured as either inputs or outputs, and have associated maskable interrupts reported to the host processor through the interrupt controller and event queue. The GPIO pins are intended for low frequency signalling.

When a GPIO pin is defined as an input, the state of that pin is sampled and latched into the GPIO Read Register. A transition on a GPIO input can cause an interrupt and event to be passed to the host processor.

Certain GPIO pins have special predefined functions, such as volume up/down, associated with that pin. Individual GPIO pins may also be defined as status outputs with associated enable/disable control. See Fixed Function I/O in the *Microsemi AcuEdge™ Technology ZLS38050 Firmware Manual*.

Immediately after any power-on or hardware reset the GPIO pins are defined as inputs and their state is captured in the GPIO Configuration Register. The state of this register is used to determine which options are selected for the device. The GPIO pin status is then redefined as specified in the configuration record upon a load from the Flash or host.

In addition to the predefined fixed functions and the general functionality of the GPIO pins, the GPIO pins also support the bootstrap functions listed in <u>Table 6</u>.

#### 4.0 Reset

The device has a hardware reset pin (RESET) that places the entire device into a known low power state. The device will perform either a digital or an analog reset depending on the duration of the reset pulse.

- Digital reset When the reset pin is brought low for a duration of between 100 ns and 1 μs, a digital reset occurs and all device states and registers are reset by this pin.

- Analog reset –When the reset pin is brought low for a duration greater than 10 μs, both a digital and an analog reset will occur. The analog reset will deactivate the internally generated +1.2 V by shutting off the external FET and the internal PLL. Raising the reset pin high will immediately turn back on these supplies (requiring a corresponding PLL startup time, ~3 ms).

For both digital and analog reset cases when reset is released, the device will go though its boot process and the firmware will be reloaded. If the reset had been an analog reset, then the boot process will take longer waiting for the system clocks to power back on.

GPIO sensing will occur with either type of reset.

A 10 K $\Omega$  pull-up resistor is required on the RESET pin to DVDD33 if this pin is not continuously driven.

#### 5.0 Power Supply

#### 5.1 Power Supply Sequencing/Power up

No special power supply sequencing is required. The +3.3 V or +1.2 V power rails can be applied in either order.

Upon power-up, the ZL38050 begins to boot and senses the external resistors on the GPIO to determine the bootstrap settings. After 3 ms, the boot process begins and the ZL38050 takes less than 1 second to become fully operational (for Auto Boot from Flash, including the time it takes to load the firmware).

In order to properly boot, the clocks to the device must be stable. This requires either the 12.000 MHz crystal or oscillator to be active, or PCLK and frame sync be present and stable before the ZL38050's reset is released.

#### 5.1.1 Power Supply Considerations

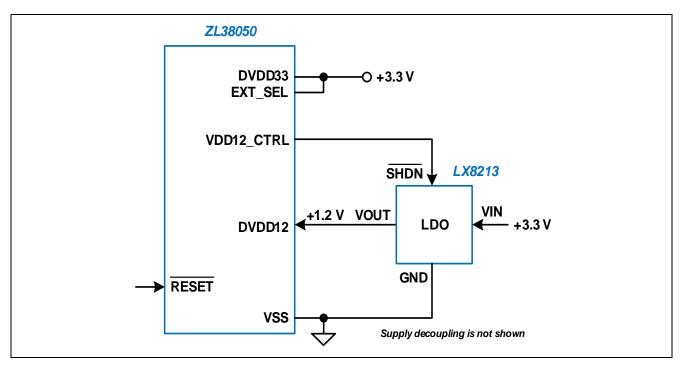

The ZL38050 requires +1.2 V to power its core DSP power supply (DVDD12). To achieve optimum noise and power performance, supply DVDD12 from an external source. Use an LDO regulator like the Microsemi LX8213 to achieve low noise and low overall power consumption. The ZL38050 is designed to minimize power in its active states when DVDD12 is supplied externally.

To further reduce power when using a crystal or clock oscillator, the internal PLL can be shut-down as described in <u>5.1.1.3, "Ultra-Low Power Mode"</u>.

#### 5.1.1.1 External +1.2 V Power

Figure 24 shows DVDD12 powered from an external supply. A Microsemi LX8213 300 mA Low Noise CMOS LDO Regulator is shown.

External supply use is selected when the EXT\_SEL pin is tied to +3.3 V. The EXT\_SEL pin can be pulled high or simply hard-wired to DVDD33.

VDD12\_CTRL is a CMOS output which can be used to control the shutdown of the external supply. VDD12\_CTRL will provide a steady +3.3 V output (with up to 4 mA of source current) for the external supply to be enabled and 0 V for the supply to be disabled.

For power savings when the ZL38050 does not need to be operational, the external voltage regulator can be turned off by pulling the RESET pin low for longer than  $10 \,\mu$ S (Reset mode). This action will force the VDD12\_CTRL pin low, shutting off the external LDO and allowing the +1.2 V supply to collapse to 0 V.

If shutdown of the external +1.2 V supply is not desired, simply leave the VDD12\_CTRL output pin floating.

Figure 24 - External +1.2 V Power Supply Configuration

#### 5.1.1.2 Internal +1.2 V Power

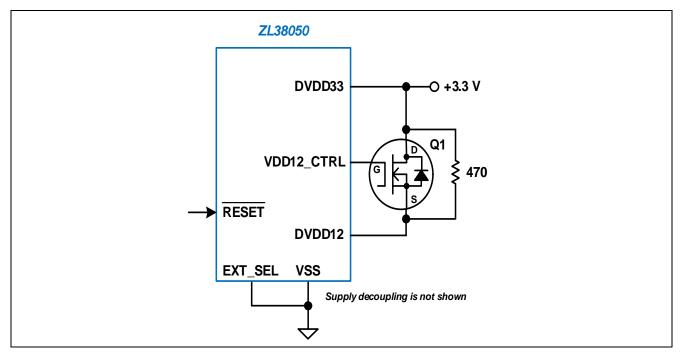

Note: The internal +1.2 V power option is only available with the 64-pin QFN package. The VDD12\_CTRL pin is not available on the 56-ball WLCSP package.

Alternatively, the ZL38050 has a built-in voltage regulator that can be used as the DVDD12 source. The internal voltage regulator requires an external N-channel FET device and a parallel 470 ohm resistor. Figure 25 shows DVDD12 powered from the internal supply. Power dissipation is higher with internal regulator use due to the internal control circuitry and functional blocks being active.

Internal supply use is selected when the EXT\_SEL pin is tied to VSS. With the built-in voltage regulator enabled, VDD12\_CTRL will drive Q1 and generate +1.2 V at DVDD12. The parallel 470 ohm resistor is required to ensure supply start-up. Q1 can be any of the high power FETs shown in <u>Table 5</u>, or an equivalent.

For power savings when the ZL38050 does not need to be operational, the internal voltage regulator can be turned off by pulling the RESET pin low for longer than  $10 \,\mu$ S (Reset mode). This action will force the VDD12\_CTRL pin low, shutting off the FET and allowing the +1.2 V supply to collapse to 0 V.

Figure 25 - Internal +1.2 V Power Supply Configuration

#### Table 5 - Q1 Component Options

| Manufacturer             | Part Number |

|--------------------------|-------------|

| Vishay <sup>®</sup>      | Si1422DH    |

| International Rectifier  | IRLMS2002   |

| Diodes Inc. <sup>®</sup> | ZXMN2B03E6  |

#### 5.1.1.3 Ultra-Low Power Mode

Note: Ultra-low power mode is only available with the 64-pin QFN package. The DVDD33\_XTAL pin is not available on the 56-ball WLCSP package.

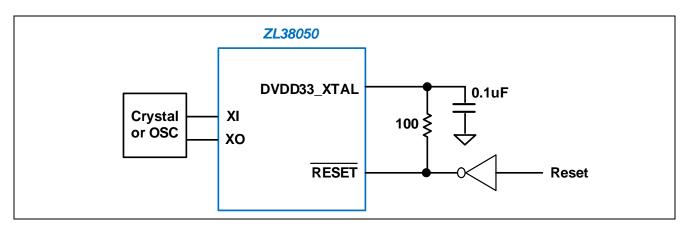

When using a crystal or clock oscillator, the ZL38050 can be placed into an Ultra-low power state by turning off the crystal oscillator's internal voltage regulator. The circuit required to perform this is shown in Figure 26.

The external circuit that drives the ZL38050 RESET pin can also be used to power the DVDD33\_XTAL pin. The reset drive circuit (gate) needs to provide at least 10 mA of source current when reset is high. The series 100 ohm resistor provides a time delay to keep crystal power from reacting to short reset pulses. When the reset line goes low for longer than 10  $\mu$ S, the crystal oscillator's internal regulator will turn off and the ZL38050 will draw Ultra-low power as specified in <u>"Device Operating Modes" on page 43</u>.

Figure 26 - Ultra-Low Power Operation Circuit

#### 6.0 Device Booting

#### 6.1 Boot Loader

The ZL38050 device contains a built-in boot-loader that gets executed after a hardware reset or when power is initially applied to the part. The Boot loader performs the following actions:

- · Reads the GPIO bootstrap information and stores it in the Boot Sense registers

- Determinant on the bootstrap setting, loads external serial Flash device contents (firmware and configuration record) into Program RAM (Auto Boot), or waits for the host to load Program RAM (Host Boot)

- Auto Boot then programs the ZL38050 configuration registers to their proper default values, and

- Auto Boot jumps to Program RAM to execute the firmware

#### 6.2 Bootstrap Modes

<u>Table 6</u> lists the different boot options that can be selected by using external resistors. These GPIOs have internal pull-down resistors, thereby defaulting to a 0 setting. A resistor to DVDD33 is required to select a 1 option. The external pull-up resistors must have a value of  $3.3 \text{ K}\Omega$ . A GPIO with a bootstrap pull-up can be used for other functionality following the power-up boot sense process.

| GPIO_2 | GPIO_1 | GPIO_0 | Operating Mode                            | Description            | Notes |

|--------|--------|--------|-------------------------------------------|------------------------|-------|

| х      | 0      | 0      | Crystal source 12 MHz (default)           | Clock source selection |       |

| Х      | 0      | 1      | TDM FS source is 8 kHz                    |                        | 1     |

| Х      | 1      | 0      | TDM FS source is 16 kHz                   |                        | 2     |

| х      | 1      | 1      | Reserved                                  |                        |       |

| 0      | Х      | Х      | Host Boot (default) Boot source selection |                        |       |

| 1      | Х      | Х      | Auto Boot from external Flash             |                        | 3     |

#### Table 6 - Bootstrap Modes

X = Don't care.

Note 1: Apply a 3.3 K  $\Omega$  resistor from GPIO\_0 to DVDD33.

Note 2: Apply a 3.3  $K\Omega$  resistor from GPIO\_1 to DVDD33.

Note 3: Apply a 3.3 K $\Omega$  resistor from GPIO\_2 to DVDD33. Note, when external Flash is selected, GPIO\_9 = SM\_CS.

#### 6.3 Loadable Device Code

In order for the ZL38050 to operate, it must be loaded with code that resides externally. This code can either be Auto Booted from an external Flash memory through the Master SPI, or can be loaded into the ZL38050 by the host processor through the HBI port. An external resistor pull-up or an internal resistor pull-down determines which boot mode will be used (see <u>Table 6</u>).

The external code consists of two logical segments, the firmware code itself and the configuration record. The firmware is a binary image which contains all of the executable code allowing the ZL38050 to perform voice processing and establishes the user command set. The configuration record contains settings for all of the user registers and defines the power-up operation of the device.

For an application that has no host and no way of externally programming the ZL38050, the configuration record is setup so that the registers are set to their desired values for normal operation.

A GUI development tool (*MiTuner*<sup>TM</sup> ZLS38508) is provided to create and modify a configuration record and create a bootable Flash image which can then be duplicated for production of the end product. This tool requires access to the UART and to the I<sup>2</sup>S port for tuning (refer to <u>11.0</u>, "AEC Tuning" on page 60).

#### 6.3.1 Boot Speed

When performing an Auto Boot from a Flash device the boot sequence lasts <1 second.

When performing a Host Boot through the HBI SPI/I<sup>2</sup>C Slave port, the boot time will vary depending on the host's communications speed. SPI can run up to a speed of 25 MHz and has less overhead, allowing it to perform a boot download ~<300 ms; I<sup>2</sup>C is limited to a speed of 400 kHz, making a boot download last ~>5 seconds. If boot speed is important, use the HBI SPI Slave port for booting rather than the I<sup>2</sup>C Slave port.

#### 6.4 Bootup Procedure

Valid clocks (PCLK/FS or a crystal or oscillator) must be present before the ZL38050 device can exit its reset state. After the reset line is released, the ZL38050's internal voltage regulator will be enabled (if the EXT\_SEL pin is strapped low). Once the +1.2 V supply is established, the PLL will be also be enabled. Based on the GPIO bootstrap options, the ZL38050 will select the appropriate PLL source and system parameters and the <u>PLL</u> will lock to the desired operating frequency. An event will be placed in the event-queue and the interrupt pin (HINT) will be pulled low to signal the host when it's OK to load boot code.

Next, if the GPIO strapping pins indicate that the ZL38050 will Auto Boot, it will begin reading data from the external Flash. Refer to the *Microsemi AcuEdge™ Technology ZLS38050 Firmware Manual* for a listing of the complete Boot Sequence.

If the GPIO strapping pins indicate that the ZL38050 will Host Boot, the SPI or  $I^2C$  port that initiates the loading process becomes the boot master. The ZL38050 allows for automatic configuration between SPI and  $I^2C$  operation. For the HBI port, if the HCLK toggles for two cycles, the HBI will default to the SPI Slave, otherwise it will remain configured as  $I^2C$ .

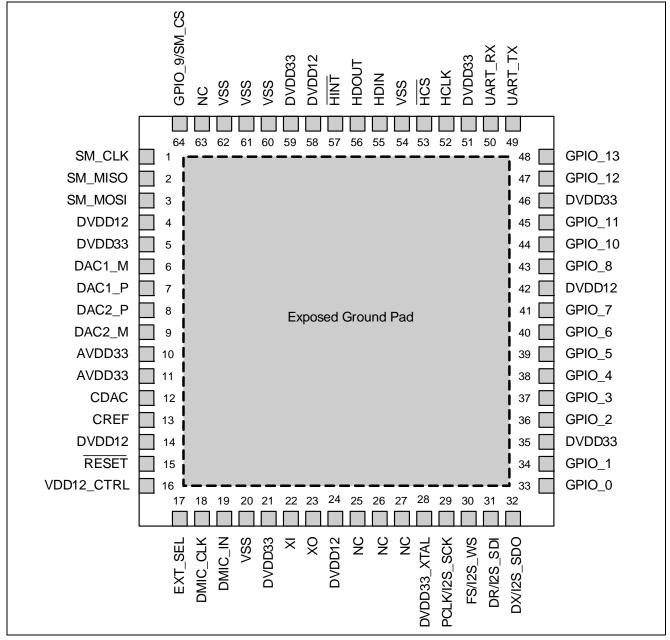

#### 7.0 Device Pinouts

#### 7.1 64-Pin QFN

Figure 27 - ZL38050 64-Pin QFN - Top View

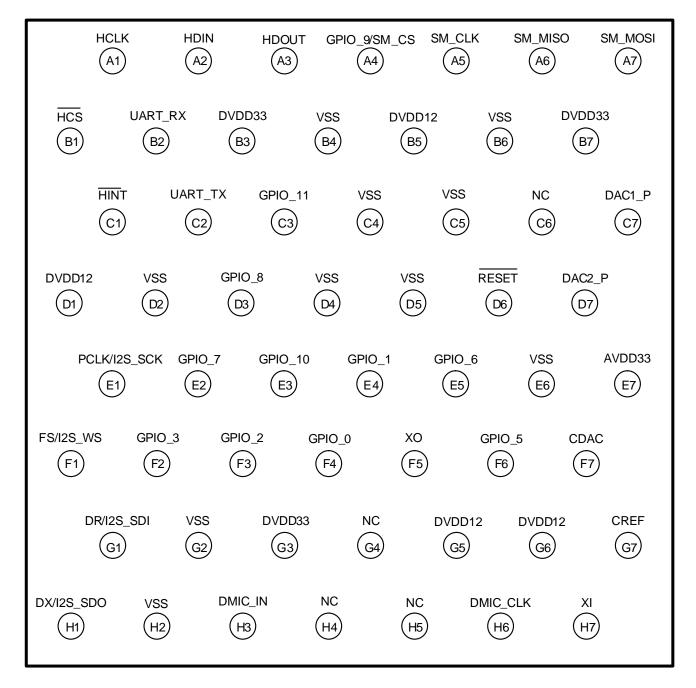

#### 7.2 56-Ball WLCSP

Figure 28 - ZL38050 56-Ball WLCSP - Top View

#### 8.0 Pin Descriptions

Table 7 - Reset Pin Description

| QFN<br>Pin # | WLCSP<br>Ball | Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|---------------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15           | D6            | RESET |      | <b>Reset.</b> When low the device is in its reset state and all tristate outputs will be in a high impedance state. This input must be high for normal device operation. A 10 K $\Omega$ pull-up resistor is required on this node to DVDD33 if this pin is not continuously driven.<br>Refer to <u>"Reset" on page 27</u> for an explanation of the various reset states and their timing. |

#### Table 8 - DAC Pin Descriptions

| QFN<br>Pin # | WLCSP<br>Ball | Name   | Туре   | Description                                                                                                                                          |

|--------------|---------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6            | _             | DAC1_M | Output | <b>DAC 1 Minus Output.</b> This is the negative output signal of the differential amplifier of the DAC 1. <i>Not available on the WLCSP package.</i> |

| 7            | C7            | DAC1_P | Output | <b>DAC 1 Plus Output.</b> This is the positive output signal of the differential amplifier of the DAC 1.                                             |

| 9            | _             | DAC2_M | Output | <b>DAC 2 Minus Output.</b> This is the negative output signal of the differential amplifier of the DAC 2. <i>Not available on the WLCSP package.</i> |

| 8            | D7            | DAC2_P | Output | <b>DAC 2 Plus Output.</b> This is the positive output signal of the differential amplifier of the DAC 2.                                             |

| 12           | F7            | CDAC   | Output | <b>DAC Reference.</b> This pin requires capacitive decoupling. Refer to <u>"DAC Bias Circuit" on page 12</u> .                                       |

| 13           | G7            | CREF   | Output | <b>Common Mode Reference.</b> This pin requires capacitive decoupling.<br>Refer to <u>"DAC Bias Circuit" on page 12</u> .                            |

#### Table 9 - Microphone Pin Descriptions

| QFN<br>Pin # | WLCSP<br>Ball | Name     | Туре   | Description                                                                                                                         |

|--------------|---------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| 18           | H6            | DMIC_CLK | Output | <b>Digital Microphone Clock Output.</b> Clock output for digital microphones and digital electret microphone pre-amplifier devices. |

| 19           | H3            | DMIC_IN  | Input  | <b>Digital Microphone Input.</b> Stereo or mono digital microphone input. <i>Tie to VSS if unused.</i>                              |

# Table 10 - TDM and I<sup>2</sup>S Port Pin Descriptions

The ZL38050 device has one TDM interface. The TDM block is capable of being a master or a slave. The port can be configured for Pulse-Code Modulation (PCM) or Inter-IC Sound ( $I^2S$ ) operation. The port conforms to PCM, GCI, and  $I^2S$  timing protocols.

| QFN<br>Pin # | WLCSP<br>Ball | Name             | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|---------------|------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29           | E1            | PCLK/<br>I2S_SCK | Input/<br>Output | <ul> <li>PCM Port Clock (Input/Tristate Output). PCLK is equal to the bit rate of signals DR/DX. In TDM master mode this clock is an output and in TDM slave mode this clock is an input.</li> <li>I<sup>2</sup>S Port Serial Clock (Input/Tristate Output). This is the I<sup>2</sup>S port bit clock. In I<sup>2</sup>S master mode this clock is an output and drives the bit clock input of the external slave device's peripheral converters. In I<sup>2</sup>S slave mode this clock is an input and is driven from a converter operating in master mode.</li> <li>After power-up, this signal defaults to be an input in I<sup>2</sup>S slave mode.</li> <li>A 100 KΩ pull-down resistor is required on this pin to VSS. If this pin is unused, tie the pin to VSS.</li> <li>When driving PCLK/I2S_SCK from a host, one of the following conditions must be satisfied:</li> <li>Host drives PCLK low during reset (the 100 KΩ resistor will keep PCLK low), or</li> <li>Host drives PCLK at its normal frequency</li> </ul> |

| 30           | F1            | FS/<br>I2S_WS    | Input/<br>Output | <ul> <li>PCM Port Frame Pulse (Input/Tristate Output). This is the TDM frame alignment reference. This signal is an input for applications where the PCM bus is frame aligned to an external frame signal (slave mode). In master mode this signal is a frame pulse output.</li> <li>I<sup>2</sup>S Port Word Select (Left/Right) (Input/Tristate Output). This is the I<sup>2</sup>S port left or right word select. In I<sup>2</sup>S master mode word select is an output which drives the left/right input of the external slave device's peripheral converters. In I<sup>2</sup>S slave mode this pin is an input which is driven from a converter operating in master mode.</li> <li>After power-up, this signal defaults to be an input in I<sup>2</sup>S slave mode. <i>Tie this pin to VSS if unused</i>.</li> </ul>                                                                                                                                                                                                      |

| 31           | G1            | DR/<br>I2S_SDI   | Input            | <ul> <li>PCM Port Serial Data Stream Input. This serial data stream operates at PCLK data rates.</li> <li>I<sup>2</sup>S Port Serial Data Input. This is the I<sup>2</sup>S port serial data input Tie this pin to VSS if unused.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| QFN<br>Pin # | WLCSP<br>Ball | Name           | Туре | Description                                                                                     |

|--------------|---------------|----------------|------|-------------------------------------------------------------------------------------------------|

| 32           | H1            | DX/<br>I2S_SDO | •    | <b>PCM Port Serial Data Stream Output.</b> This serial data stream operates at PCLK data rates. |

|              |               |                |      | I <sup>2</sup> S Port Serial Data Output. This is the I <sup>2</sup> S port serial data output. |

# Table 11 - HBI – SPI Slave Port Pin Descriptions

This port functions as a peripheral interface for an external controller, and supports access to the internal registers and memory of the device.

| QFN<br>Pin # | WLCSP<br>Ball | Name  | Туре             | Description                                                                                                                                                                                       |  |

|--------------|---------------|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 52           | A1            | HCLK  | Input            | HBI SPI Slave Port Clock Input.<br>Clock input for the SPI Slave port. Maximum frequency = 25 MHz.                                                                                                |  |

|              |               |       |                  | This input should be tied to VSS in $I^2C$ mode, refer to <u>Table 2</u> . <i>Tie this pin to VSS if unused.</i>                                                                                  |  |

| 53           | B1            | HCS   | Input            | HBI SPI Slave Chip Select Input. This active low chip select signal activates the SPI Slave port.                                                                                                 |  |

|              |               |       |                  | <b>HBI I<sup>2</sup>C Serial Clock Input.</b> This pin functions as the I2C_SCLK input in $I^2C$ mode. A pull-up resistor is required on this node for $I^2C$ operation.                          |  |

|              |               |       |                  | Tie this pin to VSS if unused.                                                                                                                                                                    |  |

| 55           | A2            | HDIN  | Input            | HBI SPI Slave Port Data Input. Data input signal for the SPI Slave port.                                                                                                                          |  |

|              |               |       |                  | This input selects the slave address in I <sup>2</sup> C mode, refer to <u>Table 2</u> . <i>Tie this pin to VSS if unused.</i>                                                                    |  |

| 56           | A3            | HDOUT | Input/<br>Output | HBI SPI Slave Port Data Output (Tristate Output). Data output signal for the SPI Slave port.                                                                                                      |  |

|              |               |       |                  | <b>HBI I<sup>2</sup>C Serial Data (Input/Output).</b> This pin functions as the I2C_SDA I/O in I <sup>2</sup> C mode. A pull-up resistor is required on this node for I <sup>2</sup> C operation. |  |

| 57           | C1            | HINT  | Output           | <b>HBI Interrupt Output.</b> This output can be configured as either CMOS or open drain by the host.                                                                                              |  |

.

#### Table 12 - Master SPI Port Pin Descriptions

This port functions as the interface to an external Flash device used to optionally Auto Boot and load the device's firmware and configuration record from external Flash memory.

| QFN<br>Pin # | WLCSP<br>Ball | Name             | Туре             | Description                                                                                                       |

|--------------|---------------|------------------|------------------|-------------------------------------------------------------------------------------------------------------------|

| 1            | A5            | SM_CLK           | Output           | Master SPI Port Clock (Tristate Output). Clock output for the Master SPI port. Maximum frequency = 8 MHz.         |

| 2            | A6            | SM_MISO          | Input            | Master SPI Port Data Input. Data input signal for the Master SPI port.                                            |

| 3            | A7            | SM_MOSI          | Output           | Master SPI Port Data Output (Tristate Output). Data output signal for the Master SPI port.                        |

| 64           | A4            | GPIO_9/<br>SM_CS | Input/<br>Output | Master SPI Port Chip Select (Input Internal Pull-Up/Tristate Output). Chip select output for the Master SPI port. |

|              |               |                  |                  | Shared with GPIO_9, see <u>Table 14</u> .                                                                         |

#### Table 13 UART Pin Descriptions