# Microsemi.

## Timberwolf Digital Signal Processor family, powered by *AcuEdge*<sup>™</sup> Technology

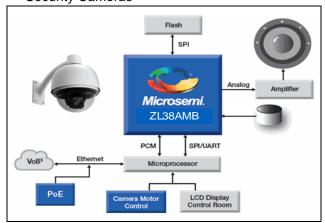

Designed for IP Cameras with advanced security features

ZL38AMB Product Brief

#### **Description**

The ZL38AMB is part of Microsemi's new Timberwolf audio processor family of products that feature the company's innovative *AcuEdge* acoustic technology, which is a set of highly-complex and integrated algorithms. These algorithms are incorporated into a powerful DSP platform that allow the user to extract intelligible information from the audio environment.

The Microsemi AcuEdge Technology ZL38AMB is designed to provide leading edge far field microphone processing with advanced features targeted for IP and security cameras with high definition (HD) 2-way hands-free voice.

The Microsemi AcuEdge Technology license-free, royalty-free intelligent audio Firmware provides Beamforming, Sound Location Estimation, Acoustic Echo Cancellation (AEC), Noise Reduction and a variety of other voice enhancements to improve both the intelligibility and subjective quality of voice in harsh environments.

Microsemi offers additional tools to speed up the product development cycle. The *MiTuner*<sup>TM</sup> ZLS38508 or ZLS38508LITE GUI software packages allow a user to interactively configure the ZL38AMB device. The optional *MiTuner* ZLE38470BADA Automatic Tuning Kit provides automatic tuning and easy control for manual fine tuning adjustments.

## **Applications**

- IP Cameras

- Security Cameras

**Typical IP Security Camera Application**

Document ID# 152263

Version 2

December 2015

#### **Ordering Information**

| Device OPN  | Package                              | Packing     |

|-------------|--------------------------------------|-------------|

| ZL38AMBLDF1 | 64-pin QFN (9x9)                     | Tape & Reel |

| ZL38AMBLDG1 | 64-pin QFN (9x9)<br>64-pin QFN (9x9) | Tray        |

| ZL38AMBUGB2 | 56-ball WLCSP (3.1x3.1)              | Tape & Reel |

|             |                                      |             |

These packages meet RoHS 2 Directive 2011/65/EU of the European Council to minimize the environmental impact of electrical equipment.

## Microsemi *AcuEdge* Technology Firmware

- Far Field Microphone Processing

- · Microphone Beamforming

- Sound Location Estimation

- Audio Compressor/Limiter/Expander

- Wideband Acoustic Echo Cancellation (for up to 3 microphones)

- Full or Half duplex operation

- Supports long tail AEC (up to 256 ms)

- · Howling detection/cancellation

- Prevents oscillation in AEC audio path

- Non-linear echo cancellation provides higher tolerance for speaker distortions

- Advanced noise reduction reduces background noise from the near-end speech signal using Psychoacoustic techniques

- Provisions for stereo audio mixing and stereo music record and playback (sample rates of 48 kHz) with 16 kHz voice processing

- Various encoding/decoding options:

- 16-bit 2's complement (linear)

- G.711 A/μ law

- G.722

- Send and receive path 8-band parametric equalizers

- · Comfort noise generation

- 48 kHz bypass mode

- Configurable Cross Point Switch

#### **Tools**

- ZLK38000 Evaluation Kit

- MiTuner™ ZLS38508 and ZLS38508LITE GUI

- MiTuner™ ZLE38470BADA Automatic Tuning Kit

# Timberwolf Digital Signal Processor family, powered by *AcuEdge*<sup>™</sup> Technology

Designed for IP Cameras with advanced security features

ZL38AMB

**Product Brief**

#### **ZL38AMB Hardware Features**

- DSP with Voice Hardware Accelerators

- Dual ΔΣ 16-bit digital-to-analog converters (DAC)

- Sampling up to 48 kHz and internal output drivers

- Headphone amps capable of 4 single-ended or 2 differential outputs

- 32 mW output drive power into 16 ohms

- · Impulse pop/click protection

- 2 Digital Microphone inputs supporting up to 4 Microphones

- 2 TDM ports shared between PCM and Inter-IC Sound (I<sup>2</sup>S)

- Each port can be a clock master or a slave

- Each port supports delayed and non-delayed (GCI) timing and I<sup>2</sup>S normal and left justified modes

- Each port provides sample rate conversion and synchronous TDM bus operation

- SPI or I<sup>2</sup>C Slave port for host processor interface

- · General purpose UART port for debug

- · Master SPI port for serial Flash interface

- · Boots from SPI or Flash

- Can run unattended (controllerless), selfbooting into a configured operational state

- · Flash firmware can be updated from SPI Slave

- Crystal-less operation (with a valid TDM clock)

- 14 General Purpose Input/Output (GPIO) pins

- · 2 low power modes controlled by reset

- Available in miniature Wafer Level Chip Scale Package

#### **Performance**

AEC Tail Length: 256 ms

AEC sampling rate: 16 kHz

Single-Talk Weighted Terminal Coupling Loss

(TCLw): > 60 dB

Double-Talk TCLw: > 40 dB

Double-Talk Attenuation: > 3 dB

Noise reduction up to 30 dB

## The *MiTuner*<sup>™</sup> Automatic Tuning Kit and ZLS38508 MiTuner GUI

Microsemi's Automatic Tuning Kit option includes:

- Audio Interface Box hardware

- Microphone and Speaker

- ZLS38508 MiTuner GUI software

- Allows tuning of Microsemi's AcuEdge Technology Audio Processor

The ZLS38508 software features:

- Auto Tuning and Subjective Tuning support

- Allows tuning of key parameters of the system design

- Provides visual representations of the audio paths with drop-down menus to program parameters, allowing:

- Control of the audio routing configuration

- Programming of key building blocks in the transmit (Tx) and receive (Rx) audio paths

- · Setting analog and digital gains

- Configuration parameters allow users to "fine tune" the overall performance

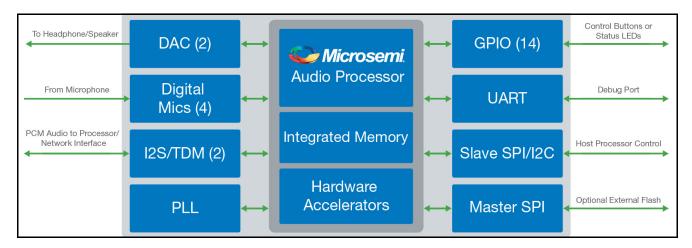

#### **Device Block Diagram**

The Microsemi AcuEdge™ Technology Firmware offers a sophisticated audio compressor/limiter/expander (CLE) with adjustable attack and decay time. This feature along with Beamforming and advanced Noise Reduction allows for Far Field Microphone pick-up.

Beamforming can be performed with 2 or 3 microphones. The Beamformer uses the signals from multiple microphones to determine the direction of arrival of various sound sources. The beamformer accepts those sources that it determines are in the direction of interest and attenuates those that are deemed to be coming from other directions. By attenuating anything extraneous outside of the beam, the distance of microphone pick-up improves and interfering sounds are reduced. The Beamformer's beam width, steering angle, and out-of-beam attenuation are programmable.

The Microsemi *AcuEdge* Technology Firmware Sound Location feature reports the angle at which a sound arrives at the microphones. The Sound Locator can track an audio source with a +/-10 degree accuracy.

The majority of the signal processing (AEC, Equalization, Noise Reduction, Beamforming, CLE, etc.) runs in the Audio Processor Block at 16 kHz. Each of the audio inputs (Digital Mics, I<sup>2</sup>S/TDM) and outputs (DACs, I<sup>2</sup>S/TDM) can be routed amongst themselves or to the Audio Processor via a highly configurable Cross Point Switch.

**ZL38AMB IP Camera Audio Processor**

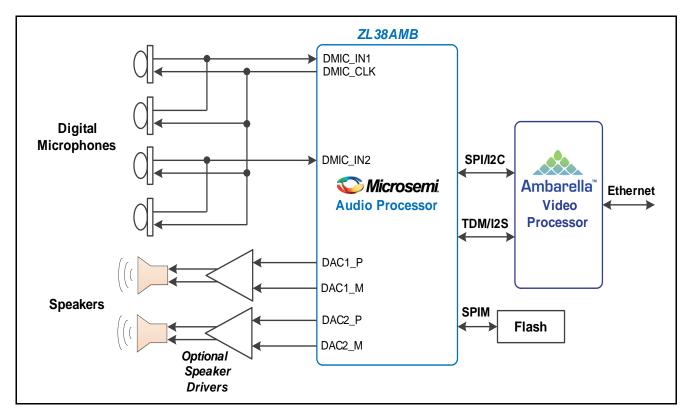

## **Typical Application Block Diagram**

The Microsemi *AcuEdge™* Technology ZL38AMB is a hardware platform designed to support advanced features such as far field microphone, sound locator, beamforming, acoustic echo canceller and noise reduction with the Firmware pack for IP camera applications.

IP Camera HD Voice 2-way Audio Application

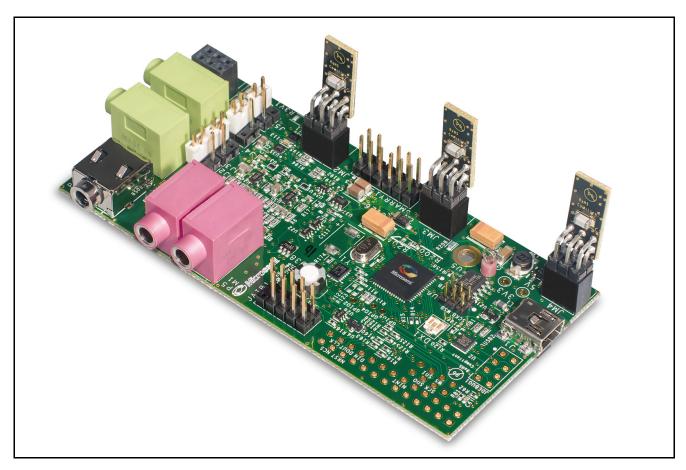

#### **Evaluation Kit**

The Evaluation Board is designed to aid and speed up the evaluation of the Microsemi  $AcuEdge^{TM}$  Technology ZL38AMB IP Camera Audio Processor with the Microsemi AcuEdge Technology Firmware. It provides a simple analog interface that can be connected to microphones and speakers in a plastic enclosure to allow for subjective testing of the Acoustic Echo Canceller. The miniature size allows for easy mounting in an existing plastic enclosure. Easy access to all analog and digital interfaces is provided.

**Evaluation Board**

The Evaluation Kit is a fully contained design consisting of the Evaluation Board with USB cable, headset with extension cable, and a speaker.

The Evaluation Board is controlled using the Microsemi  $MiTuner^{TM}$  GUI Software (ZLS38508). The MiTuner GUI Software can also be used with the optional Microsemi Audio Interface Box (AIB) Evaluation Kit (OPN ZLE38470BADA) to auto tune the Evaluation Board.

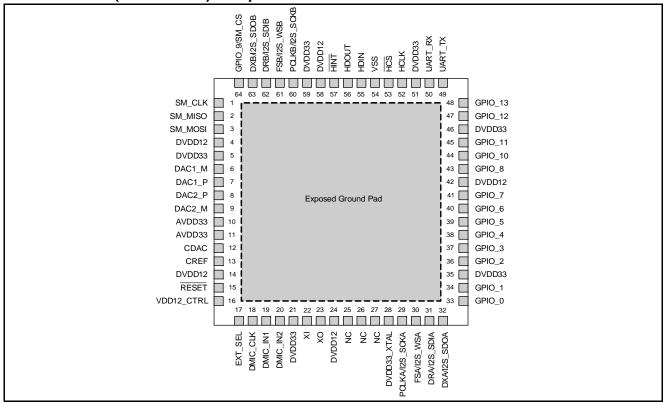

#### Device Pinout (64-Pin QFN) - Top View

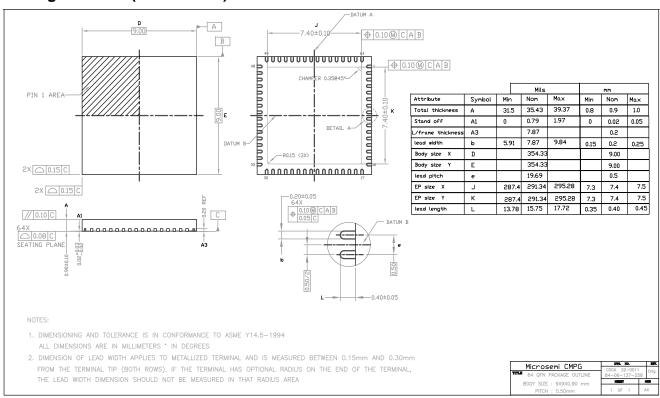

## Package Outline (64-Pin QFN)

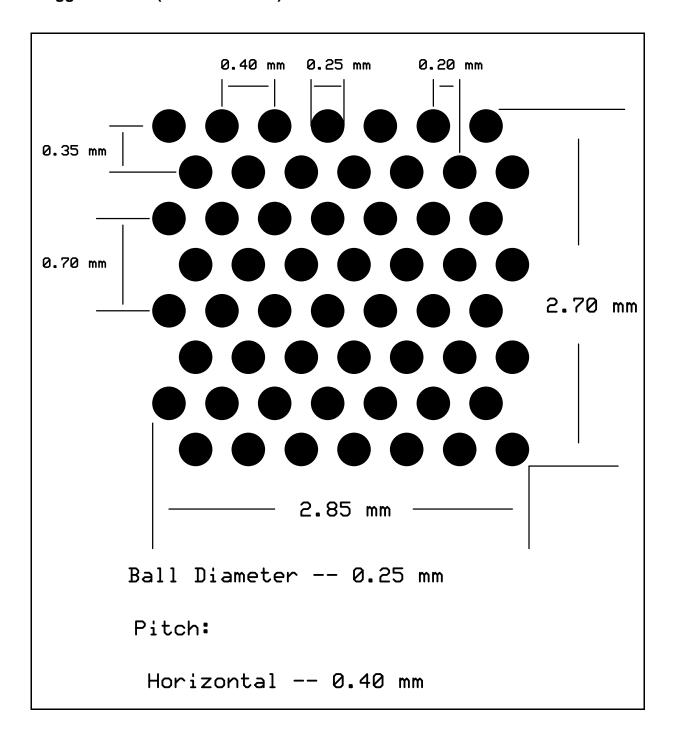

## Device Pinout (56-Ball WLCSP) - Top View

|           | HCLK<br>(A1)   |           | HDIN<br>(A2) | H       | HDOUT  | GPI       | D_9/SM <sub>.</sub> | _CS         | SM_CLF         | < 5       | SM_MISO        | O 8      | SM_MOSI  A7 |

|-----------|----------------|-----------|--------------|---------|--------|-----------|---------------------|-------------|----------------|-----------|----------------|----------|-------------|

| HCS<br>B1 |                | UART_R    | X I          | DVDD33  |        | VSS<br>B4 | [                   | DVDD1<br>B5 | 2              | VSS<br>B6 | I              | DVDD33   | 3           |

|           | HINT<br>C1     | L         | C2           | X G     | PIO_11 | PCLKE     | 3/I2S_S<br>C4       | CKB [       | ORB/I2S_<br>C5 | _SDIB I   | OXB/I2S_<br>C6 | _SDOB    | DAC1_P      |

| DVDD12    | 2              | VSS<br>D2 |              | GPIO_8  |        | VSS<br>D4 | FSE                 | 3/I2S_V     | VSB            | RESET D6  |                | DAC2_F   | •           |

| PCL       | KA/I2S_<br>E1) | SCKA      | GPIO_7       | G       | PIO_10 | (         | GPIO_1              |             | GPIO_6         | 6         | VSS<br>E6      | ,        | AVDD33      |

| FSA/I2S_V | WSA            | GPIO_3    | 3            | GPIO_2  | (      | GPIO_0    |                     | XO<br>F5    |                | GPIO_5    | 5              | CDAC     |             |

| DR        | A/I2S_         | SDIA      | VSS<br>G2    | С       | G3     |           | NC<br>G4            |             | DVDD1          | 2         | DVDD12         | 2        | CREF<br>G7  |

| DXA/I2S_S | SDOA           | DMIC_II   | N2 [         | DMIC_IN | 1      | NC<br>H4  |                     | NC<br>H5    | Г              | OMIC_C    | LK             | XI<br>H7 |             |

## Staggered Balls (56-Ball WLCSP) - Bottom View

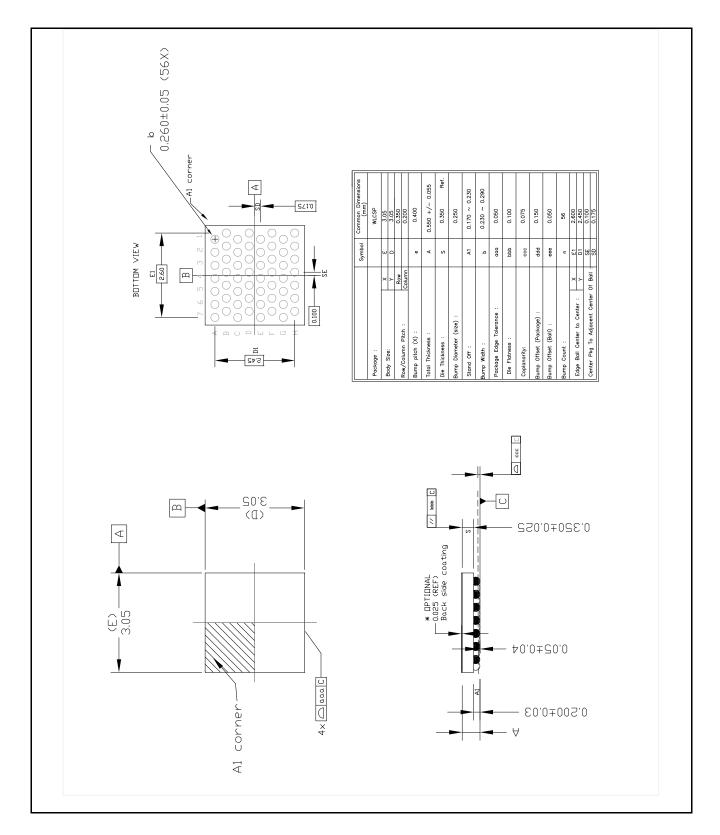

## Package Outline (56-Ball WLCSP)

## **Pin Descriptions**

### **Table 1 - Reset Pin Description**

| QFN<br>Pin# | WLCSP<br>Ball | Name  | Туре | Description                                                                                                                                                                                                                                                                          |

|-------------|---------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15          | D6            | RESET |      | <b>Reset.</b> When low the device is in its reset state and all tristate outputs will be in a high impedance state. This input must be high for normal device operation. A 10 K $\Omega$ pull-up resistor is required on this node to DVDD33 if this pin is not continuously driven. |

### **Table 2 - DAC Pin Descriptions**

| QFN<br>Pin # | WLCSP<br>Ball | Name   | Туре   | Description                                                                                               |

|--------------|---------------|--------|--------|-----------------------------------------------------------------------------------------------------------|

| 6            | _             | DAC1_M | Output | DAC 1 Minus Output. This is the negative output signal of the differential amplifier of the DAC 1.        |

|              |               |        |        | Not available on the WLCSP package.                                                                       |

| 7            | C7            | DAC1_P | Output | DAC 1 Plus Output. This is the positive output signal of the differential amplifier of the DAC 1.         |

| 9            | -             | DAC2_M | Output | <b>DAC 2 Minus Output.</b> This is the negative output signal of the differential amplifier of the DAC 2. |

|              |               |        |        | Not available on the WLCSP package.                                                                       |

| 8            | D7            | DAC2_P | Output | DAC 2 Plus Output. This is the positive output signal of the differential amplifier of the DAC 2.         |

| 12           | F7            | CDAC   | Output | DAC Reference. This pin requires capacitive decoupling.                                                   |

| 13           | G7            | CREF   | Output | Common Mode Reference. This pin requires capacitive decoupling.                                           |

## **Table 3 - Microphone Pin Descriptions**

| QFN<br>Pin # | WLCSP<br>Ball | Name     | Туре   | Description                                                                                                                         |

|--------------|---------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| 18           | H6            | DMIC_CLK | Output | <b>Digital Microphone Clock Output.</b> Clock output for digital microphones and digital electret microphone pre-amplifier devices. |

| 19           | НЗ            | DMIC_IN1 | Input  | Digital Microphone Input 1. Stereo or mono digital microphone input. Tie to VSS if unused.                                          |

| 20           | H2            | DMIC_IN2 | Input  | <b>Digital Microphone Input 2.</b> Stereo or mono digital microphone input. <i>Tie to VSS if unused.</i>                            |

## Table 4 - TDM and I<sup>2</sup>S Ports Pin Descriptions

The ZL38AMB device has two TDM interfaces, TDM-A and TDM-B. Each TDM block is capable of being a master or a slave. The ports can be configured for Pulse-Code Modulation (PCM) or Inter-IC Sound ( $I^2S$ ) operation. The ports conform to PCM, GCI, and  $I^2S$  timing protocols.

| QFN<br>Pin # | WLCSP<br>Ball | Name               | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|---------------|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29           | E1            | PCLKA/<br>I2S_SCKA | Input/<br>Output | PCM Port A Clock (Input/Tristate Output). PCLKA is equal to the bit rate of signals DRA/DXA. In TDM master mode this clock is an output and in TDM slave mode this clock is an input.                                                                                                                                                                                                                    |

|              |               |                    |                  | I <sup>2</sup> S Port A Serial Clock (Input/Tristate Output). This is the I <sup>2</sup> S port A bit clock. In I <sup>2</sup> S master mode this clock is an output and drives the bit clock input of the external slave device's peripheral converters. In I <sup>2</sup> S slave mode this clock is an input and is driven from a converter operating in master mode.                                 |

|              |               |                    |                  | After power-up, this signal defaults to be an input in I <sup>2</sup> S slave mode.                                                                                                                                                                                                                                                                                                                      |

|              |               |                    |                  | A 100 KΩ pull-down resistor is required on this pin to VSS. If this pin is unused, tie the pin to VSS.  When driving PCLKA/I2S_SCKA from a host, one of the following conditions must be satisfied:  1. Host drives PCLKA low during reset, or                                                                                                                                                           |

|              |               |                    |                  | 2. Host tri-states PCLKA during reset (the 100 K $\Omega$ resistor will keep PCLKA low), or                                                                                                                                                                                                                                                                                                              |

|              |               |                    |                  | 3. Host drives PCLKA at its normal frequency                                                                                                                                                                                                                                                                                                                                                             |

| 30           | F1            | FSA/<br>I2S_WSA    | Input/<br>Output | CM Port A Frame Sync (Input/Tristate Output). This is the TDM frame alignment reference. This signal is an input for applications where the PCM bus is frame aligned to an external frame signal (slave mode). In master mode this signal is a frame pulse output.                                                                                                                                       |

|              |               |                    |                  | I <sup>2</sup> S Port A Word Select (Left/Right) (Input/Tristate Output). This is the I <sup>2</sup> S port A left or right word select. In I <sup>2</sup> S master mode word select is an output which drives the left/right input of the external slave device's peripheral converters. In I <sup>2</sup> S slave mode this pin is an input which is driven from a converter operating in master mode. |

|              |               |                    |                  | After power-up, this signal defaults to be an input in I <sup>2</sup> S slave mode.<br>Tie this pin to VSS if unused.                                                                                                                                                                                                                                                                                    |

| 31           | G1            | DRA/<br>I2S_SDIA   | Input            | PCM Port A Serial Data Stream Input. This serial data stream operates at PCLK data rates.                                                                                                                                                                                                                                                                                                                |

|              |               |                    |                  | I <sup>2</sup> S Port A Serial Data Input. This is the I <sup>2</sup> S port serial data input.                                                                                                                                                                                                                                                                                                          |

|              |               |                    |                  | Tie this pin to VSS if unused.                                                                                                                                                                                                                                                                                                                                                                           |

| 32           | H1            | DXA/<br>I2S_SDOA   | Output           | PCM Port A Serial Data Stream Output. This serial data stream operates at PCLK data rates.                                                                                                                                                                                                                                                                                                               |

|              |               |                    |                  | I <sup>2</sup> S Port A Serial Data Output. This is the I <sup>2</sup> S port serial data output.                                                                                                                                                                                                                                                                                                        |

| QFN<br>Pin # | WLCSP<br>Ball | Name               | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|---------------|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60           | C4            | PCLKB/<br>I2S_SCKB | Input/<br>Output | PCM Port B Clock (Input/Tristate Output). PCLKB is equal to the bit rate of signals DRB/DXB. In TDM master mode this clock is an output and in TDM slave mode this clock is an input.                                                                                                                                                                                                                    |

|              |               |                    |                  | <b>I<sup>2</sup>S Port B Serial Clock (Input/Tristate Output).</b> This is the I <sup>2</sup> S port B bit clock. In I <sup>2</sup> S master mode this clock is an output and drives the bit clock input of the external slave device's peripheral converters. In I <sup>2</sup> S slave mode this clock is an input and is driven from a converter operating in master mode.                            |

|              |               |                    |                  | After power-up, this signal is an input in I <sup>2</sup> S slave mode. <i>Tie this pin to VSS if unused.</i>                                                                                                                                                                                                                                                                                            |

| 61           | D5            | FSB/<br>I2S_WSB    | Input/<br>Output | PCM Port B Frame Sync (Input/Tristate Output). This is the TDM frame alignment reference. This signal is an input for applications where the PCM bus is frame aligned to an external frame signal (slave mode). In master mode this signal is a frame pulse output.                                                                                                                                      |

|              |               |                    |                  | I <sup>2</sup> S Port B Word Select (Left/Right) (Input/Tristate Output). This is the I <sup>2</sup> S port B left or right word select. In I <sup>2</sup> S master mode word select is an output which drives the left/right input of the external slave device's peripheral converters. In I <sup>2</sup> S slave mode this pin is an input which is driven from a converter operating in master mode. |

|              |               |                    |                  | After power-up, this signal defaults to be an input in I <sup>2</sup> S slave mode.<br>Tie this pin to VSS if unused.                                                                                                                                                                                                                                                                                    |

| 62           | C5            | DRB/<br>I2S_SDIB   | Input            | PCM Port B Serial Data Stream Input. This serial data stream operates at PCLK data rates.                                                                                                                                                                                                                                                                                                                |

|              |               |                    |                  | I <sup>2</sup> S Port B Serial Data Input. This is the I <sup>2</sup> S port serial data input.                                                                                                                                                                                                                                                                                                          |

|              |               |                    |                  | Tie this pin to VSS if unused.                                                                                                                                                                                                                                                                                                                                                                           |

| 63           | C6            | DXB/<br>I2S_SDOB   | Output           | PCM Port B Serial Data Stream Output. This serial data stream operates at PCLK data rates.                                                                                                                                                                                                                                                                                                               |

|              |               |                    |                  | I <sup>2</sup> S Port B Serial Data Output. This is the I <sup>2</sup> S port serial data output.                                                                                                                                                                                                                                                                                                        |

#### Table 5 - HBI - SPI Slave Port Pin Descriptions

This port functions as a peripheral interface for an external controller, and supports access to the internal registers and memory of the device.

| QFN<br>Pin # | WLCSP<br>Ball | Name  | Туре             | Description                                                                                                                                                                                                                                                                                                                |

|--------------|---------------|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52           | A1            | HCLK  | Input            | HBI SPI Slave Port Clock Input. Clock input for the SPI Slave port. Maximum frequency = 25 MHz. This input should be tied to VSS in I <sup>2</sup> C mode.  Tie this pin to VSS if unused.                                                                                                                                 |

| 53           | B1            | HCS   | Input            | HBI SPI Slave Chip Select Input. This active low chip select signal activates the SPI Slave port.  HBI I <sup>2</sup> C Serial Clock Input. This pin functions as the I2C_SCLK input in I <sup>2</sup> C mode. A pull-up resistor is required on this node for I <sup>2</sup> C operation.  Tie this pin to VSS if unused. |

| 55           | A2            | HDIN  | Input            | HBI SPI Slave Port Data Input. Data input signal for the SPI Slave port.  This input selects the slave address in I <sup>2</sup> C mode.  Tie this pin to VSS if unused.                                                                                                                                                   |

| 56           | А3            | HDOUT | Input/<br>Output | HBI SPI Slave Port Data Output (Tristate Output). Data output signal for the SPI Slave port.  HBI I <sup>2</sup> C Serial Data (Input/Output). This pin functions as the I2C_SDA I/O in I <sup>2</sup> C mode. A pull-up resistor is required on this node for I <sup>2</sup> C operation.                                 |

| 57           | C1            | HINT  | Output           | <b>HBI Interrupt Output.</b> This output can be configured as either CMOS or open drain by the host.                                                                                                                                                                                                                       |

#### **Table 6 - Master SPI Port Pin Descriptions**

This port functions as the interface to an external Flash device used to optionally Auto Boot and load the device's firmware and configuration record from external Flash memory.

| QFN<br>Pin # | WLCSP<br>Ball | Name             | Туре             | Description                                                                                                                            |

|--------------|---------------|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1            | A5            | SM_CLK           | Output           | Master SPI Port Clock (Tristate Output). Clock output for the Master SPI port. Maximum frequency = 8 MHz.                              |

| 2            | A6            | SM_MISO          | Input            | Master SPI Port Data Input. Data input signal for the Master SPI port.                                                                 |

| 3            | A7            | SM_MOSI          | Output           | Master SPI Port Data Output (Tristate Output). Data output signal for the Master SPI port.                                             |

| 64           | A4            | GPIO_9/<br>SM_CS | Input/<br>Output | Master SPI Port Chip Select (Input Internal Pull-Up/Tristate Output). Chip select output for the Master SPI port.  Shared with GPIO_9. |

#### Table 7 - UART Pin Descriptions

The ZL38AMB device incorporates a two-wire UART (Universal Asynchronous Receiver Transmitter) interface with a fixed 115.2K baud transfer rate, 8 data bits, 1 stop and no parity. The UART port can be used as a debug tool and is used for tuning purposes.

| QFN<br>Pin # | WLCSP<br>Ball | Name    | Туре   | Description                                                                                                                                                                                               |

|--------------|---------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50           | B2            | UART_RX | Input  | <b>UART (Input).</b> Receive serial data in. This port functions as a peripheral interface for an external controller and supports access to the internal registers and memory of the device.             |

| 49           | C2            | UART_TX | Output | <b>UART (Tristate Output).</b> Transmit serial data out. This port functions as a peripheral interface for an external controller and supports access to the internal registers and memory of the device. |

**Table 8 - GPIO Pin Descriptions**

GPIO ports can be used for interrupt and event reporting, fixed function control, bootstrap options, as well as being used for general purpose I/O for communication and controlling external devices.

| QFN<br>Pin #                 | WLCSP<br>Ball               | Name             | Туре             | Description                                                                                                                                                       |

|------------------------------|-----------------------------|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33, 34,<br>36                | F4, E4,<br>F3               | GPIO_[0:2]       | Input/<br>Output | General Purpose I/O (Input Internal Pull-Down/Tristate Output). These pins can be configured as an input or output and are intended for low-frequency signalling. |

| 37, 38,<br>39, 40,<br>41, 43 | F2, -,<br>F6, E5,<br>E2, D3 | GPIO_[3:8]       | Input/<br>Output | General Purpose I/O (Input Internal Pull-Down/Tristate Output). These pins can be configured as an input or output and are intended for low-frequency signalling. |

|                              |                             |                  |                  | GPIO_4 is not available on the WLCSP package.                                                                                                                     |

| 64                           | A4                          | GPIO_9/<br>SM_CS | Input/<br>Output | General Purpose I/O (Input Internal Pull-Down/Tristate Output). This pin can be configured as an input or output and is intended for low-frequency signalling.    |

|                              |                             |                  |                  | Alternate functionality with SM_CS.                                                                                                                               |

| 44, 45,<br>47, 48            | E3, C3,<br>-, -             | GPIO_<br>[10:13] | Input/<br>Output | General Purpose I/O (Input Internal Pull-Down/Tristate Output). These pins can be configured as an input or output and are intended for low-frequency signalling. |

|                              |                             |                  |                  | GPIO_12 and GPIO_13 are not available on the WLCSP package.                                                                                                       |

#### **Table 9 - Oscillator Pin Descriptions**

These pins are connected to a 12.000 MHz crystal or clock oscillator which drives the device's internal PLL. Alternatively, PCLKA can be used as the internal clock source.

| QFN<br>Pin # | WLCSP<br>Ball | Name | Туре   | Description                |

|--------------|---------------|------|--------|----------------------------|

| 22           | H7            | ΧI   | Input  | Crystal Oscillator Input.  |

| 23           | F5            | XO   | Output | Crystal Oscillator Output. |

## **Table 10 - Supply and Ground Pin Descriptions**

| QFN<br>Pin#                 | WLCSP<br>Ball                | Name                  | Туре   | Description                                                                                                                                                                                                                                                                     |

|-----------------------------|------------------------------|-----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                          | -                            | EXT_SEL               | Input  | VDD +1.2 V Select. Select external +1.2 V supply. Tie to DVDD33 if the +1.2 V supply is to be provided externally. Tie to VSS (0 V) if the +1.2 V supply is to be generated internally.                                                                                         |

|                             |                              |                       |        | Not available on the WLCSP package.                                                                                                                                                                                                                                             |

| 16                          | _                            | VDD12_CTRL            | Output | VDD +1.2 V Control. Analog control line for the voltage regulator external FET when EXT_SEL is tied to VSS. When EXT_SEL is tied to DVDD33, the VDD12_CTRL pin becomes a CMOS output which can drive the shutdown input of an external LDO.                                     |

|                             |                              |                       |        | Not available on the WLCSP package.                                                                                                                                                                                                                                             |

| 4, 14,<br>24, 42,<br>58     | B5, D1,<br>G5, G6            | DVDD12                | Power  | Core Supply. Connect to a +1.2 V ±5% supply.  Place a 100 nF, 20%, 10 V, ceramic capacitor on each pin decoupled to the VSS plane.                                                                                                                                              |

| 5, 21,<br>35, 46,<br>51, 59 | B3, B7,<br>G3                | DVDD33                | Power  | <b>Digital Supply.</b> Connect to a +3.3 V ±5% supply. Place a 100 nF, 20%, 10 V, ceramic capacitor on each pin decoupled to the VSS plane.                                                                                                                                     |

| 28                          | -                            | DVDD33_<br>XTAL       | Power  | Crystal Digital Supply. For designs using a crystal or external oscillator, this pin must be connected to a +3.3 V supply source capable of delivering 10 mA.  For designs that do not use a crystal or external oscillator this pin can be tied to VSS in order to save power. |

|                             |                              |                       |        | Not available on the WLCSP package.                                                                                                                                                                                                                                             |

| 10, 11                      | E7                           | AVDD33                | Power  | <b>Analog Supply.</b> Connect to a +3.3 V ±5% supply. Place a 100 nF, 20%, 10 V, ceramic capacitor on each pin decoupled to the VSS plane.                                                                                                                                      |

| 54                          | B4, B6,<br>D2, D4,<br>E6, G2 | VSS                   | Ground | Ground. Connect to digital ground plane.                                                                                                                                                                                                                                        |

|                             | _                            | Exposed<br>Ground Pad | Ground | <b>Exposed Pad Substrate Connection.</b> Connect to VSS. This pad is at ground potential and must be soldered to the printed circuit board and connected via multiple vias to a heatsink area on the bottom of the board and to the internal ground plane.                      |

|                             |                              |                       |        | Not available on the WLCSP package.                                                                                                                                                                                                                                             |

## **Table 11 - No Connect Pin Description**

| QFN<br>Pin #  | WLCSP<br>Ball | Name | Туре | Description                                                                             |

|---------------|---------------|------|------|-----------------------------------------------------------------------------------------|

| 25, 26,<br>27 | G4, H4,<br>H5 | NC   |      | <b>No Connection.</b> These pins are to be left unconnected, do not use as a tie point. |