### 60V HIGH ACCURACY BUCK/BOOST/BUCK-BOOST LED DRIVER-CONTROLLER

### **Description**

The ZXLD1371 is an LED driver controller IC for driving external MOSFETs to drive high current LEDs. It is a multitopology controller enabling it to efficiently control the current through series connected LEDs. The multi-topology enables it to operate in buck, boost and buck-boost configurations.

The 60V capability coupled with its multi-topology capability enables it to be used in a wide range of applications and drive in excess of 15 LEDs in series.

The ZXLD1371 is a modified hysteretic controller using a patent pending control scheme providing high output current accuracy in all three modes of operation. High accuracy dimming is achieved through DC control and high frequency PWM control.

The ZXLD1371 uses two pins for fault diagnosis. A flag output highlights a fault, while the multi-level status pin gives further information on the exact fault.

#### **Features**

- 0.5% typical output current accuracy

- 5 to 60V operating voltage range

- LED driver supports Buck, Boost and Buck-boost

- configurations

- Wide dynamic range dimming

- 10:1 DC dimming

- o 1000:1 dimming range at 500Hz

- Up to 1MHz switching

- High temperature control of LED current using T<sub>ADJ</sub>

- Available in Automotive Grade with AEC-Q100 and TS16949 certification

- Available in "Green" Molding Compound (No Br, Sb) with lead Free Finish/ RoHS Compliant (Note 1)

Note 1: EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2). All applicable RoHS exemptions applied.

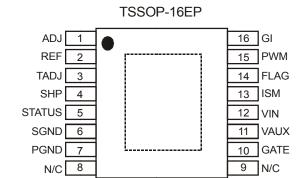

### Pin Assignments

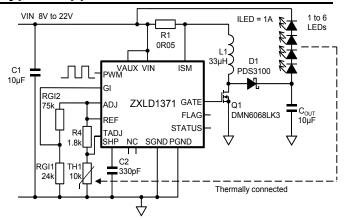

# **Typical Application Circuit**

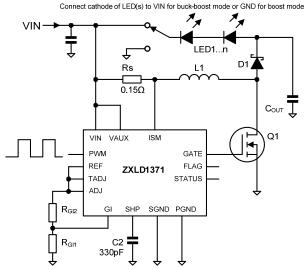

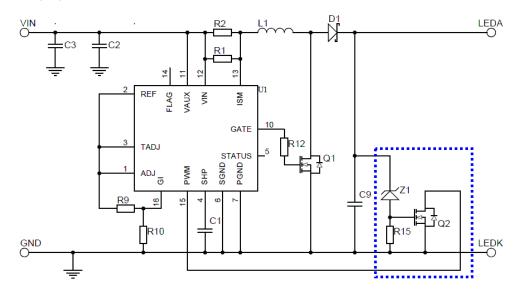

**Buck-Boost Diagram Utilizing Thermistor and TADJ**

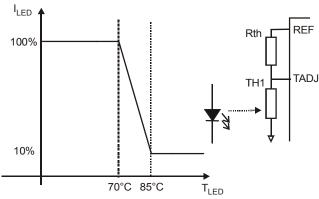

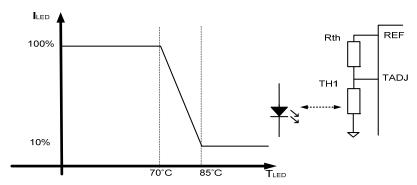

Thermal network response in Buck configuration with: Rth =  $1.8k\Omega$  and TH1 =  $10k\Omega$  (beta = 3900)

Curve Showing LED Current vs. T<sub>LED</sub>

# **Pin Descriptions**

| Pin       | Pin  | Type     | Description                                                                                                                                                         |

|-----------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name      |      | (Note 2) | Adjust input (for dc output current control)                                                                                                                        |

|           |      |          | Connect to REF to set 100% output current.                                                                                                                          |

| ADJ       | 1    | ı        | Drive with dc voltage (125mV <v<sub>ADJ&lt; 1.25V) to adjust output current from 10% to 100%</v<sub>                                                                |

|           |      |          | of set value. The ADJ pin has an internal clamp that limits the internal node to less than                                                                          |

|           |      |          | 3V. This provides some failsafe should they get overdriven                                                                                                          |

| REF       | 2    | 0        | Internal 1.25V reference voltage output                                                                                                                             |

|           |      |          | Temperature Adjust input for LED thermal current control                                                                                                            |

| TADJ      | 3    | ,        | Connect thermistor/resistor network to this pin to reduce output current above a preset temperature threshold.                                                      |

| TADJ      | 3    | '        | Connect to REF to disable thermal compensation function. (See section on thermal                                                                                    |

|           |      |          | control.)                                                                                                                                                           |

| SHP       | 4    | I/O      | Shaping capacitor for feedback control loop                                                                                                                         |

| 0111      |      | 1/0      | Connect 330pF ±20% capacitor from this pin to ground to provide loop compensation                                                                                   |

|           |      |          | Operation status output (analog output) Pin is at 4.5V (nominal) during normal operation.                                                                           |

| STATUS    | 5    | 0        | Pin switches to a lower voltage to indicate specific operation warnings or fault                                                                                    |

| 0171100   | Ŭ    | J        | conditions. (See section on STATUS output.)                                                                                                                         |

|           |      |          | Status pin voltage is low during shutdown mode                                                                                                                      |

| SGND      | 6    | Р        | Signal ground (Connect to 0V)                                                                                                                                       |

| PGND      | 7    | Р        | Power ground - Connect to 0V and pin 8 to maximize copper area                                                                                                      |

| N/C       | 8    | _        | Not Connected internally – recommend connection to pin 7, (PGND), to maximize PCB                                                                                   |

| 14.0      |      |          | copper for thermal dissipation  Not Connected internally – recommend connection pin 10 (GATE) to permit wide copper                                                 |

| N/C       | 9    |          | trace to gate of MOSFET                                                                                                                                             |

| GATE      | 10   | 0        | Gate drive output to external NMOS transistor – connect to pin 9                                                                                                    |

| OATE      | 10   |          | Auxiliary positive supply to internal switch gate driver                                                                                                            |

|           |      |          | At V <sub>IN</sub> < 8V; a bootstrap circuit is recommended to ensure adequate gate drive voltage                                                                   |

|           |      |          | (see Applications section)                                                                                                                                          |

| $V_{AUX}$ | 11   | Р        | At $V_{IN} > 8V$ ; connect to $V_{IN}$                                                                                                                              |

|           |      |          | At V <sub>IN</sub> >24V; to reduce power dissipation, V <sub>AUX</sub> can be connected to an 8V to 15V                                                             |

|           |      |          | auxiliary power supply (see Applications section). Decouple to ground with capacitor                                                                                |

|           |      |          | close to device (see Applications section) Input supply to device 5V to 60V                                                                                         |

| $V_{IN}$  | 12   | Р        | Decouple to ground with capacitor close to device (refer to Applications section)                                                                                   |

|           |      |          | Current monitor input. Connect current sense resistor between this pin and V <sub>IN</sub>                                                                          |

| ISM       | 13   | ı        | The nominal voltage, V <sub>SENSE</sub> , across the resistor is 218mV fixed in Buck mode and                                                                       |

| 10.11     | , 0  | ·        | initially 225mV in Boost and Buck-Boost modes, varying with duty cycle.                                                                                             |

|           |      |          | Flag open drain output                                                                                                                                              |

| FLAG      | 14   | 0        | Pin is high impedance during normal operation                                                                                                                       |

|           |      |          | Pin switches low to indicate a fault, or warning condition                                                                                                          |

|           |      |          | Digital PWM output current control Pin driven either by open Drain or push-pull 3.3V or 5V logic levels.                                                            |

|           |      |          | Drive with frequency higher than 100Hz to gate output 'on' and 'off' during dimming                                                                                 |

| PWM       | 15   | I        | control.                                                                                                                                                            |

|           |      |          | The device enters standby mode when PWM pin is driven with logic low level for more                                                                                 |

|           |      |          | than 15ms nominal (Refer to application section for more details)                                                                                                   |

|           |      |          | Gain setting input Used to set the device in Buck mode or Boost, Buck-boost modes and to control the                                                                |

|           |      |          | sense voltage in Boost and Buck-boost modes                                                                                                                         |

|           | 40   |          | Connect to ADJ pin for Buck mode operation                                                                                                                          |

| GI        | 16   |          | For Boost and Buck-boost modes, connect to resistive divider from ADJ to SGND. The                                                                                  |

|           |      |          | GI divider is required to compensate for duty cycle gating in the internal feedback loop                                                                            |

|           |      |          | (see Application section). The GI pin has an internal clamp that limits the internal node to less than 3V. This provides some failsafe should it become overdriven. |

| EP        | PAD  | Р        | Exposed paddle. Connect to 0V plane for electrical and thermal management                                                                                           |

| L1        | י אט | '        | Expedit paddio. Comment to 64 plane for electrical and thermal management                                                                                           |

Notes: 2. Type refers to whether or not pin is an Input, Output, Input/Output or Power supply pin.

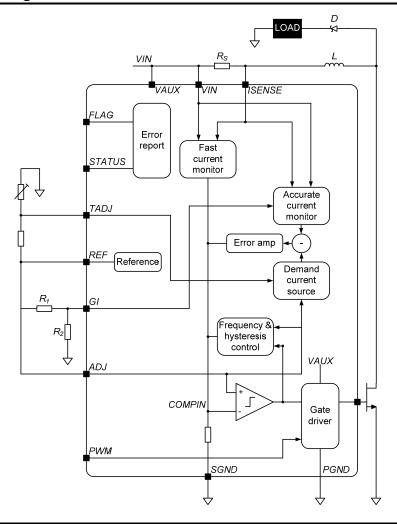

### **Functional Block Diagram**

### Absolute Maximum Ratings (Voltages to GND Unless Otherwise Stated) (Note 3)

| Symbol                                        | Parameter                                                          | Rating      | Unit |

|-----------------------------------------------|--------------------------------------------------------------------|-------------|------|

| V <sub>IN</sub>                               | Input supply voltage                                               | -0.3 to 65  | V    |

| V <sub>AUX</sub>                              | Auxiliary supply voltage                                           | -0.3 to 65  | V    |

| V <sub>ISM</sub>                              | Current monitor input relative to GND                              | -0.3 to 65  | V    |

| V <sub>SENSE</sub>                            | Current monitor sense voltage (V <sub>IN</sub> -V <sub>ISM</sub> ) | -0.3 to 5   | V    |

| V <sub>GATE</sub>                             | Gate driver output voltage                                         | -0.3 to 20  | V    |

| I <sub>GATE</sub>                             | Gate driver continuous output current                              | 18          | mA   |

| $V_{FLAG}$                                    | Flag output voltage                                                | -0.3 to 40  | V    |

| $V_{PWM}, V_{ADJ}, V_{TADJ}, V_{GI}, V_{PWM}$ | Other input pins                                                   | -0.3 to 5.5 | V    |

| TJ                                            | Maximum junction temperature                                       | 150         | °C   |

| T <sub>ST</sub>                               | Storage temperature                                                | -55 to 150  | °C   |

Stresses greater than the 'Absolute Maximum Ratings' specified above, may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions exceeding those indicated in this specification is not implied. Device reliability may be affected by exposure to absolute maximum rating conditions for extended periods of time.

Semiconductor devices are ESD sensitive and may be damaged by exposure to ESD events. Suitable ESD precautions should be taken when handling and transporting these devices.

# **Package Thermal Data**

| Thermal Resistance                            | Package     | Typical | Unit |

|-----------------------------------------------|-------------|---------|------|

| Junction-to-Ambient, θ <sub>JA</sub> (Note 4) | TSSOP-16 EP | 50      | °C/W |

| Junction-to-Case, θ <sub>JC</sub>             | TSSOP-16 EP | 23      | °C/W |

# Recommended Operating Conditions (-40°C ≤ T<sub>J</sub> ≤ 125°C)

| Symbol              | Parameter                                                               | Performance/Comment                                 | Min   | Max       | Unit |

|---------------------|-------------------------------------------------------------------------|-----------------------------------------------------|-------|-----------|------|

|                     |                                                                         | Normal Operation                                    | 8.0   | 60        |      |

| V <sub>IN</sub>     | Input supply voltage range                                              | (Note 5) Reduced performance operation              | 5.0   | 8.0       | V    |

|                     |                                                                         | Normal Operation                                    | 8.0   | 60        |      |

| V <sub>AUX</sub>    | Auxiliary supply voltage range (Note 6)                                 | (Note 5) Reduced performance operation              | 5.0   | 8.0       | V    |

| V <sub>SENSE</sub>  | Differential input voltage                                              | $V_{IN}$ - $V_{ISM}$ , with $0 \le V_{ADJ} \le 2.5$ | 0     | 450       | mV   |

| V <sub>ADJ</sub>    | External dc control voltage applied to ADJ pin to adjust output current | DC brightness control mode from 10% to 100%         | 0.125 | 1.25      | V    |

| I <sub>REF</sub>    | Reference external load current                                         | REF sourcing current                                |       | 1         | mA   |

| f <sub>max</sub>    | Recommended switching frequency range                                   | (Note 7)                                            | 300   | 1000      | kHz  |

| $V_{TADJ}$          | Temperature adjustment (T <sub>ADJ</sub> ) input voltage range          |                                                     | 0     | $V_{REF}$ | V    |

| £                   | Pagammandad DWM dimming fraguancy range                                 | To achieve 1000:1 resolution                        | 100   | 500       | Hz   |

| f <sub>PWM</sub>    | Recommended PWM dimming frequency range                                 | To achieve 500:1 resolution                         | 100   | 1000      | Hz   |

| t <sub>PWMH/L</sub> | PWM pulse width in dimming mode                                         | PWM input high or low                               | 0.002 | 10        | ms   |

| V <sub>PWMH</sub>   | PWM pin high level input voltage                                        |                                                     | 2     | 5.5       | V    |

| V <sub>PWML</sub>   | PWM pin low level input voltage                                         |                                                     | 0     | 0.4       | V    |

| TJ                  | Operating Junction Temperature Range                                    |                                                     | -40   | 125       | °C   |

| GI                  | Gain setting ratio for boost and buck-boost modes                       | Ratio= V <sub>GI</sub> /V <sub>ADJ</sub>            | 0.20  | 0.50      |      |

#### Notes:

- 3. For correct operation SGND and PGND should always be connected together.

- 4. Measured on "High Effective Thermal Conductivity Test Board" according to JESD51.

- 5. Device starts up above 5.4V and as such the minimum applied supply voltage has to be above 5.4V (plus any noise margin). The ZXLD1371 will, however, continue to function when the input voltage is reduced from ≥ 8V down to 5.0V. When operating with input voltages below 8V the output current and device parameters may deviate from their normal values; and is dependent

- on power MOSFET switch, load and ambient temperature conditions. To ensure best operation in Boost and Buck-boost modes with input voltages, V<sub>IN</sub>, between 5.0 and 8V a suitable boot-strap network on V<sub>AUX</sub> pin is recommended.

- Performance in Buck mode will be reduced at input voltages (VIN, VAUX) below 8V. a boot-strap network cannot be implemented in buck mode.

- 6. V<sub>AUX</sub> can be driven from a voltage higher than V<sub>IN</sub> to provide higher efficiency at low V<sub>IN</sub> voltages, but to avoid false operation; a voltage should not be applied to V<sub>AUX</sub> in the absence of a voltage at V<sub>IN</sub>. V<sub>AUX</sub> can also be operated at a lower voltage than V<sub>IN</sub> to increase efficiencies at high V<sub>IN</sub>.

- 7. The device contains circuitry to control the switching frequency to approximately 400kHz. The maximum and minimum operating frequency is not tested in production.

# Electrical Characteristics (Test conditions: $V_{IN} = V_{AUX} = 12V$ , $T_A = 25$ °C, unless otherwise specified.)

| Symbol                 | Parameter                                                                           | Conditions                                           | Min   | Тур   | Max   | Units  |

|------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------|-------|-------|-------|--------|

| Supply and             | reference parameters                                                                |                                                      | •     |       |       |        |

| V <sub>UV-</sub>       | Under-Voltage detection threshold Normal operation to switch disabled               | V <sub>IN</sub> or V <sub>AUX</sub> falling (Note 8) |       | 4.5   |       | V      |

| V <sub>UV+</sub>       | Under-Voltage detection threshold Switch disabled to normal operation               | V <sub>IN</sub> or V <sub>AUX</sub> rising (Note 8)  |       | 4.9   |       | V      |

| I <sub>Q-IN</sub>      | Quiescent current into V <sub>IN</sub>                                              | PWM pin floating.                                    |       | 1.5   | 3     | mA     |

| I <sub>Q-AUX</sub>     | Quiescent current into V <sub>AUX</sub>                                             | Output not switching                                 |       | 150   | 300   | μA     |

| I <sub>SB-IN</sub>     | Standby current into V <sub>IN</sub> .                                              | PWM pin grounded                                     |       | 90    | 150   | μA     |

| I <sub>SB-AUX</sub>    | Standby current into V <sub>AUX</sub> .                                             | for more than 15ms                                   |       | 0.7   | 10    | μA     |

| $V_{REF}$              | Internal reference voltage                                                          | No load                                              | 1.237 | 1.25  | 1.263 | V      |

| ۸۱/                    | Change in reference voltage with output                                             | Sourcing 1mA                                         | -5    |       |       | mV     |

| $\Delta V_{REF}$       | current                                                                             | Sinking 25µA                                         |       |       | 5     | IIIV   |

| $V_{REF\_LINE}$        | Reference voltage line regulation                                                   | $V_{IN} = V_{AUX}, 8.0V < V_{IN} = <60V$             | -60   | -90   |       | dB     |

| V <sub>REF-TC</sub>    | Reference temperature coefficient                                                   |                                                      |       | ±50   |       | ppm/°C |

| DC-DC conv             | verter parameters                                                                   |                                                      |       |       |       |        |

| I <sub>ADJ</sub>       | ADJ input current (Note 9)                                                          | V <sub>ADJ</sub> ≤ 1.25V                             |       |       | 100   | nA     |

|                        |                                                                                     | V <sub>ADJ</sub> = 5.0V                              |       |       | 5     | μA     |

| $V_{GI}$               | GI Voltage threshold for boost and buck-<br>boost modes selection ( <b>Note 9</b> ) | V <sub>ADJ</sub> = 1.25V                             |       |       | 0.8   | V      |

|                        | GI input current (Note 9)                                                           | V <sub>GI</sub> ≤ 1.25V                              |       |       | 100   | nA     |

| I <sub>GI</sub>        |                                                                                     | V <sub>GI</sub> = 5.0V                               |       |       | 5     | μA     |

| I <sub>PWM</sub>       | PWM input current                                                                   | V <sub>PWM</sub> = 5.5V                              |       | 36    | 100   | μA     |

| t <sub>PWMoff</sub>    | PWM pulse width (to enter shutdown state)                                           | PWM input low                                        | 10    | 15    | 25    | ms     |

| T <sub>SDH</sub>       | Thermal shutdown upper threshold (GATE output forced low)                           | Temperature rising.                                  |       | 150   |       | °C     |

| T <sub>SDL</sub>       | Thermal shutdown lower threshold (GATE output re-enabled)                           | Temperature falling.                                 |       | 125   |       | °C     |

| High-Side C            | Current Monitor (Pin ISM)                                                           | •                                                    |       | •     | •     | •      |

| I <sub>ISM</sub>       | Input Current                                                                       | Measured into ISM pin V <sub>ISM</sub> = 12V         |       | 11    | 20    | μA     |

| V <sub>SENSE_acc</sub> | Accuracy of nominal V <sub>SENSE</sub> threshold voltage                            | V <sub>ADJ</sub> = 1.25V                             |       | ±0.25 | ±2    | %      |

| V <sub>SENSE-OC</sub>  | Over-current sense threshold voltage                                                | 7                                                    | 300   | 350   | 375   | mV     |

Notes: 8. UVLO levels are such that all ZXLD1371 will function above 5.4V for rising supply voltages and function down to 5V for falling supply voltages.

The ADJ and GI pins have an internal clamp that limits the internal node to less than 3V. This provides some failsafe should those pins get overdriven.

### Electrical Characteristics (cont.) (Test conditions: V<sub>IN</sub> = V<sub>AUX</sub> = 12V, T<sub>A</sub> = 25°C, unless otherwise specified.)

| Symbol               | Parameter                                                            | Conditions                                                                     | Min | Тур  | Max | Units |

|----------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------|-----|------|-----|-------|

| Output Par           | rameters                                                             |                                                                                |     |      |     |       |

| $V_{FLAGL}$          | FLAG pin low level output voltage                                    | Output sinking 1mA                                                             |     |      | 0.5 | V     |

| I <sub>FLAGOFF</sub> | FLAG pin open-drain leakage current                                  | V <sub>FLAG</sub> = 40V                                                        |     |      | 1   | μΑ    |

|                      |                                                                      | Normal operation                                                               | 4.2 | 4.5  | 4.8 |       |

|                      |                                                                      | Out of regulation (V <sub>SHP</sub> out of range) ( <b>Note 11</b> )           | 3.3 | 3.6  | 3.9 |       |

|                      | STATUS Flag no-load output voltage                                   | V <sub>IN</sub> under-voltage (V <sub>IN</sub> < UVLO)                         | 3.3 | 3.6  | 3.9 | ] ,,  |

| V <sub>STATUS</sub>  | (Note 10)                                                            | Switch stalled (t <sub>ON</sub> or t <sub>OFF</sub> > 100µs)                   | 3.3 | 3.6  | 3.9 | V     |

|                      |                                                                      | Over-temperature (T <sub>J</sub> > 125°C)                                      | 1.5 | 1.8  | 2.1 |       |

|                      |                                                                      | Excess sense resistor current (V <sub>SENSE</sub> > 0.32V)                     | 0.6 | 0.9  | 1.2 |       |

| R <sub>STATUS</sub>  | Output impedance of STATUS output                                    | Normal operation                                                               |     | 10   |     | kΩ    |

| Driver outp          | out (PIN GATE)                                                       |                                                                                |     |      |     |       |

| V <sub>GATEH</sub>   | High level output voltage                                            | No load Sourcing 1mA (Note 12)                                                 | 10  | 11   |     | V     |

| $V_{GATEL}$          | Low level output voltage                                             | Sinking 1mA, (Note 13)                                                         |     |      | 0.5 | V     |

| V <sub>GATECL</sub>  | High level GATE CLAMP voltage                                        | $V_{IN} = V_{AU X} = V_{ISM} = 18V$<br>$I_{GATE} = 1mA$                        |     | 12.8 | 15  | ٧     |

| I <sub>GATE</sub>    | Dynamic peak current available during rise or fall of output voltage | Charging or discharging gate of external switch with $Q_G = 10nC$ and $400kHz$ |     | ±300 |     | mA    |

| t <sub>STALL</sub>   | Time to assert 'STALL' flag and warning on STATUS output (Note 14)   | GATE low or high                                                               |     | 100  | 170 | μs    |

| LED Therr            | mal control circuit (T <sub>ADJ</sub> ) parameters                   |                                                                                |     |      |     |       |

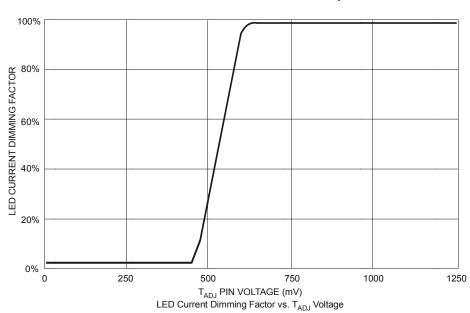

| $V_{TADJH}$          | Upper threshold voltage                                              | Onset of output current reduction (V <sub>TADJ</sub> falling)                  | 560 | 625  | 690 | mV    |

| $V_{TADJL}$          | Lower threshold voltage                                              | Output current reduced to <10% of set value (V <sub>TADJ</sub> falling)        | 380 | 440  | 500 | mV    |

| I <sub>TADJ</sub>    | T <sub>ADJ</sub> pin Input current                                   | V <sub>TADJ</sub> = 1.25V                                                      |     |      | 1   | μA    |

Notes:

<sup>10.</sup> In the event of more than one fault/warning condition occurring, the higher priority condition will take precedence. For example 'Excessive coil current' and 'Out of regulation' occurring together will produce an output of 0.9V on the STATUS pin. These STATUS pin voltages apply for an input voltage to V<sub>IN</sub> of 7.5V < V<sub>IN</sub> < 60V. Below 7.5V the STATUS pin voltage levels reduce and therefore may not report the correct status. For 5.4V < V<sub>IN</sub> < 7.5V the flag pin still reports any error by going low. At low V<sub>IN</sub> in Boost and Buck-boost modes an over-current status may be indicated when operating at high boost ratios – this due to the feedback loop increasing the sense voltage.

For more information see the Application Information section about Flag/Status levels.

<sup>11.</sup> Flag is asserted if V<sub>SHP</sub> < 1.5V or V<sub>SHP</sub> > 2.5V

<sup>12.</sup> GATE is switched to the supply voltage V<sub>AUX</sub> for low values of V<sub>AUX</sub> (5V ≤ V<sub>AUX</sub> ≤ ~12V). For V<sub>AUX</sub> > 12V, GATE is clamped internally to prevent it exceeding 15V.

<sup>13.</sup> GATE is switched to PGND by an NMOS transistor

<sup>14.</sup> If toN exceeds t<sub>STALL</sub>, the device will force GATE low to turn off the external switch and then initiate a restart cycle. During this phase, ADJ is grounded internally and the SHP pin is switched to its nominal operating voltage, before operation is allowed to resume. Restart cycles will be repeated automatically until the operating conditions are such that normal operation can be sustained. If t<sub>OFF</sub> exceeds t<sub>STALL</sub>, the switch will remain off until normal operation is possible.

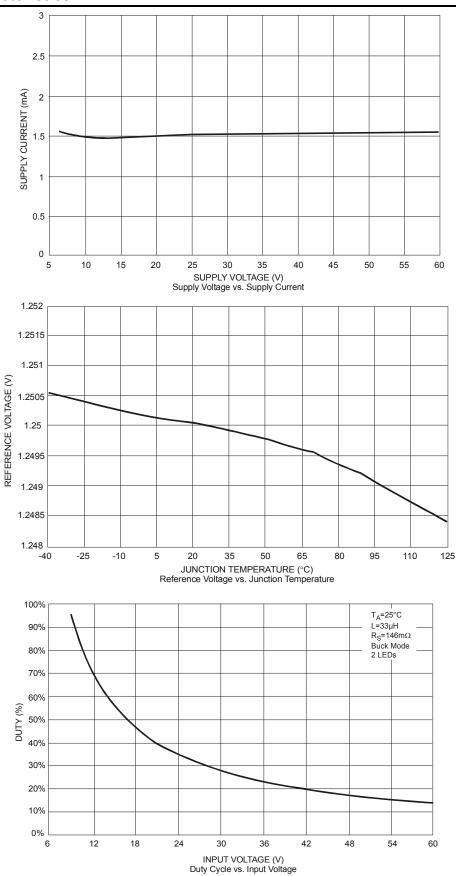

# **Typical Characteristics**

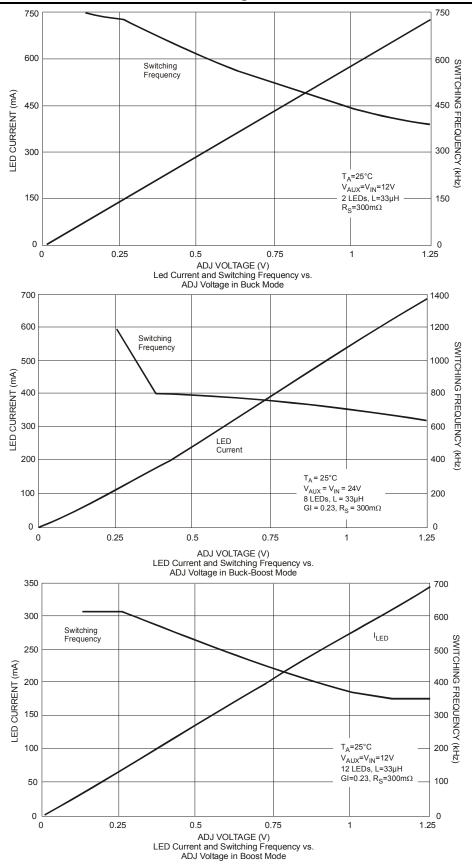

# Typical Characteristics - Linear/DC Dimming

# Typical Characteristics - PWM/Thermal Dimming

I<sub>LED</sub> vs. Time - PWM Pin Transient Response

M 10.0,us

CH4 \ 1.48V

1.00000kHz

CH1 10.0VB<sub>W</sub> CH2 500mA

CH4 1.00V

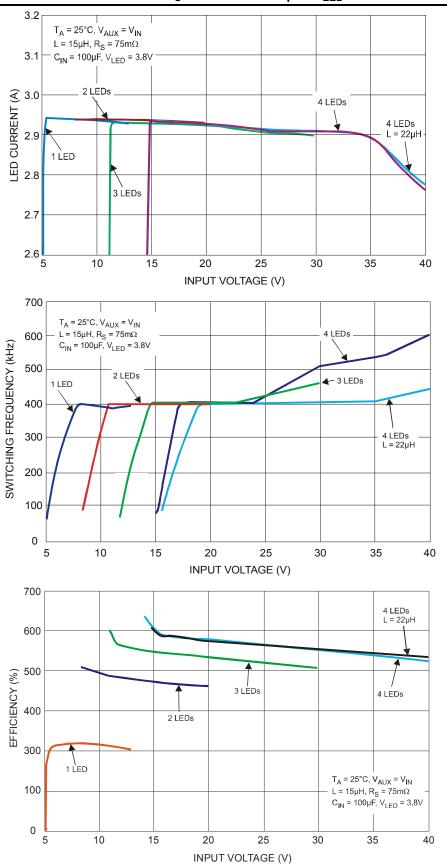

# Typical Characteristics — Buck Mode — $R_S = 75 m\Omega$ — $L = 33 \mu H$ — $I_{LED} = 2.9 A$

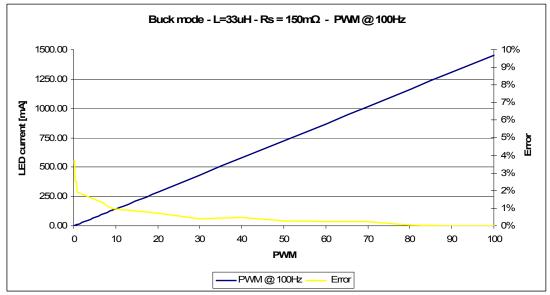

### Typical Characteristics - Buck Mode - $R_S$ =150m $\Omega$ - L = 33 $\mu$ H - $I_{LED}$ = 1.45A

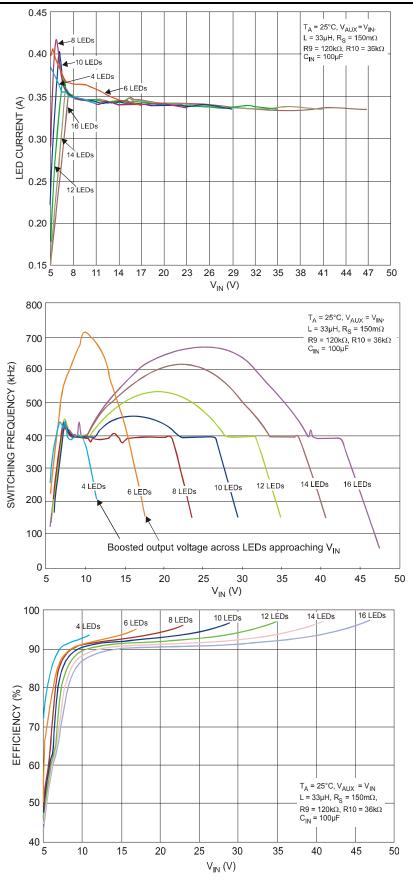

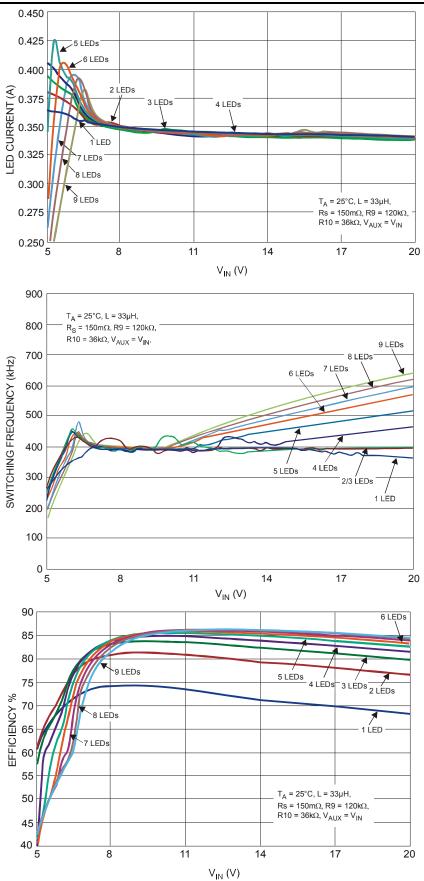

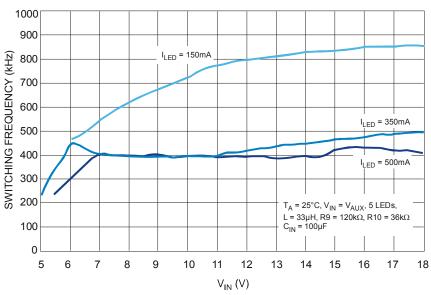

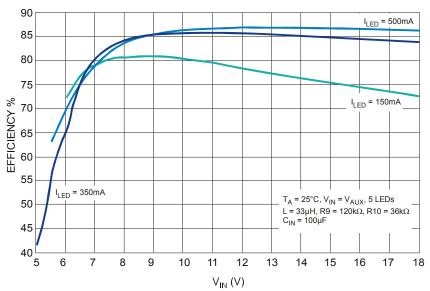

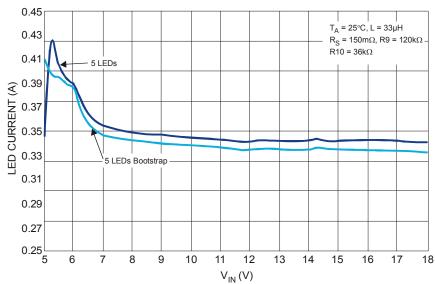

# Typical Characteristics - Boost Mode - $I_{LED}$ = $350mA - R_S$ = $150m\Omega - GI_{RATIO}$ = 0.23

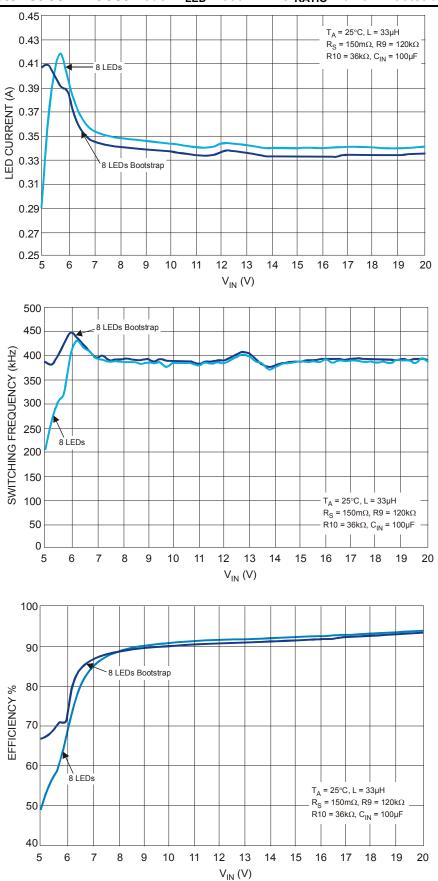

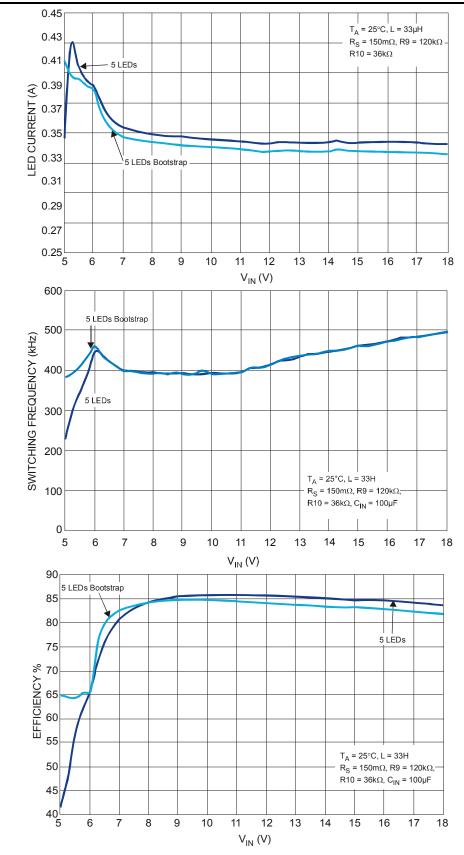

# Typical Characteristics - Boost Mode - I<sub>LED</sub> = 350mA - GI<sub>RATIO</sub> = 0.23 - Bootstrap comparison

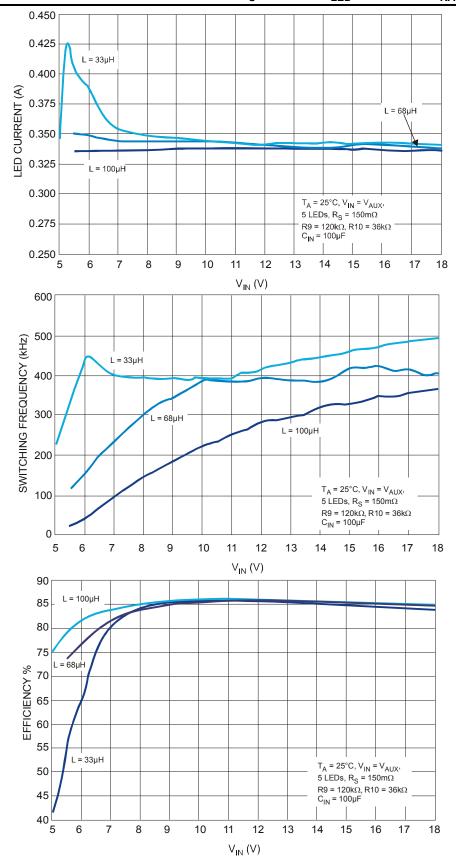

# Typical Characteristics - Boost Mode - $I_{LED}$ = 350mA - $R_S$ = 150m $\Omega$ - $GI_{RATIO}$ = 0.23

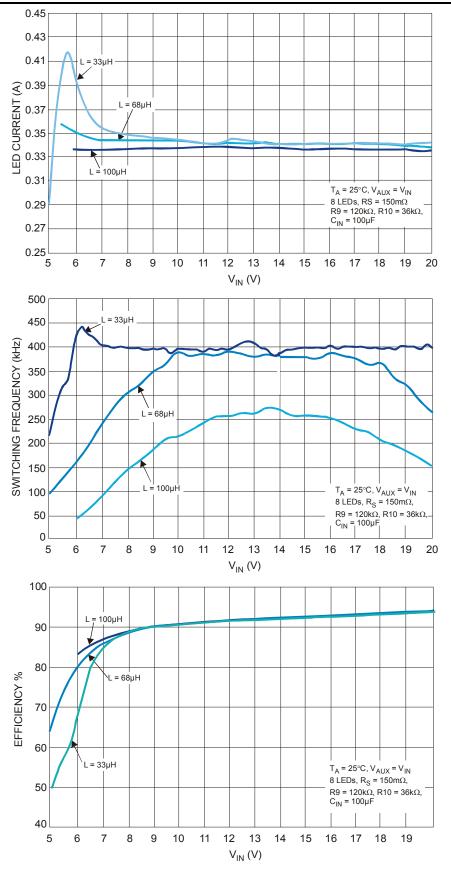

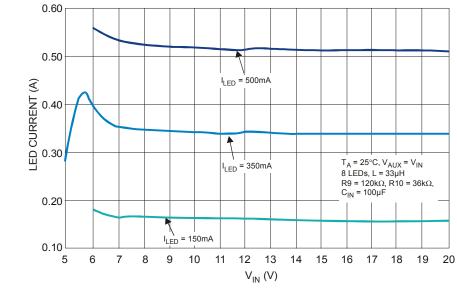

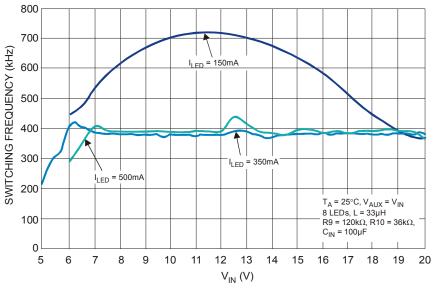

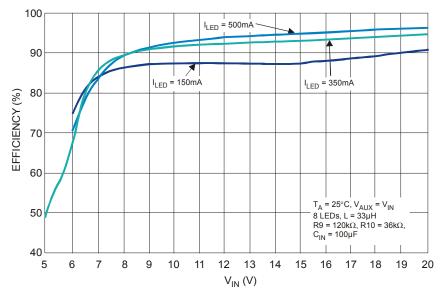

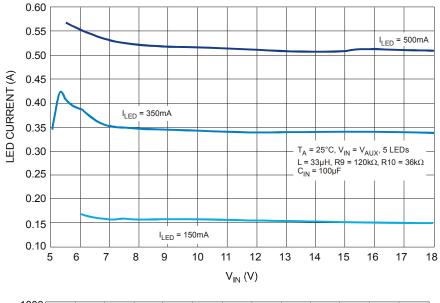

# Typical Characteristics - Boost Mode - 8 LEDs - GIRATIO = 0.23

# Typical Characteristics – Buck-Boost Mode – $R_S$ = 150m $\Omega$ - $I_{LED}$ = 350mA – $GI_{RATIO}$ = 0.23

# Typical Characteristics - Buck-Boost Mode - $R_S$ = 150m $\Omega$ - $I_{LED}$ = 350mA - $GI_{RATIO}$ = 0.23

# Typical Characteristics - Buck-Boost Mode - $R_S$ = 150m $\Omega$ - $I_{LED}$ = 350mA - $GI_{RATIO}$ = 0.23

# Typical Characteristics - Buck-Boost Mode -5 LEDs GI<sub>RATIO</sub> = 0.23

### **Applications Information**

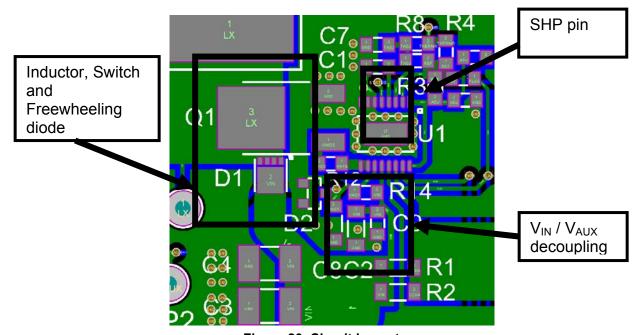

The ZXLD1371 is a high accuracy hysteretic inductive buck/boost/buck-boost controller designed to be used with an external NMOS switch for current-driving single or multiple series-connected LEDs. The device can be configured to operate in buck, boost, or buck-boost modes by suitable configuration of the external components as shown in the schematics shown in the device operation description.

#### **DEVICE DESCRIPTION**

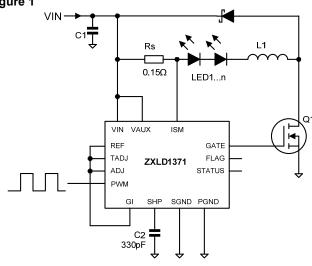

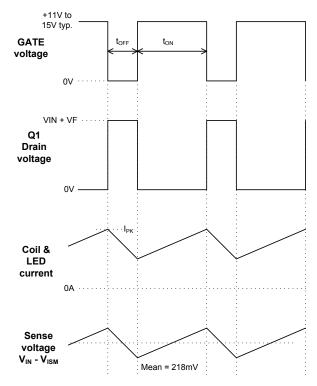

### a) Buck mode - the most simple buck circuit is shown in Figure 1

Control of the LED current buck mode is achieved by sensing the coil current in the sense resistor Rs, connected between the two inputs of a current monitor within the control loop block. An output from the control loop drives the input of a comparator which drives the gate of the external NMOS switch transistor Q1 via the internal Gate Driver. When the switch is on, the drain voltage of Q1 is near zero. Current flows from VIN. via Rs. LED. coil and switch to ground. This current ramps up until an upper threshold value is reached (see Figure 2). At this point GATE goes low, the switch is turned off and the drain voltage increases to VIN plus the forward voltage, V<sub>F</sub>, of the schottky diode D1. Current flows via Rs, LED, coil and D1 back to VIN. When the coil current has ramped down to a lower threshold value, GATE goes high, the switch is turned on again and the cycle of events repeats, resulting in continuous oscillation. The feedback loop adjusts the NMOS switch duty cycle to stabilize the LED current in response to changes in external conditions, including input voltage and load voltage.

The average current in the sense resistor, LED and coil is equal to the average of the maximum and minimum threshold currents. The ripple current (hysteresis) is equal to the difference between the thresholds. The control loop maintains the average LED current at the set level by adjusting the switch duty cycle continuously to force the average sense resistor current to the value demanded by the voltage on the ADJ pin. This minimizes variation in output current with changes in operating conditions.

The control loop also regulates the switching frequency by varying the level of hysteresis. The hysteresis has a defined minimum (typ 5%) and a maximum (typ 30%). The frequency may deviate from nominal in some conditions. This depends upon the desired LED current, the coil inductance and the voltages at the input and the load. Loop compensation is achieved by a single external capacitor C2, connected between SHP and SGND.

The control loop sets the duty cycle so that the sense voltage is

$$V_{SENSE} = 0.218 \left( \frac{V_{ADJ}}{V_{DEE}} \right)$$

Therefore.

$$I_{LED} = \left(\frac{0.218}{R_S}\right) \left(\frac{V_{ADJ}}{V_{REF}}\right)$$

(Buck mode)

#### **Equation 1**

If the ADJ pin is connected to the REF pin, this simplifies to

$$I_{LED} = \left(\frac{0.218}{R_S}\right)$$

(Buck mode).

Figure 1. Buck configuration

Figure 2. Operating waveforms (Buck mode)

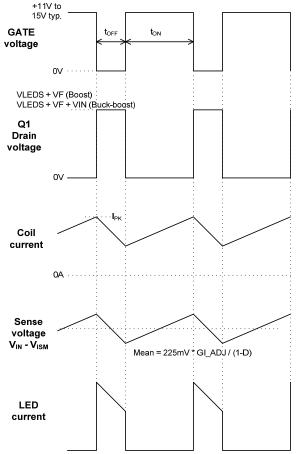

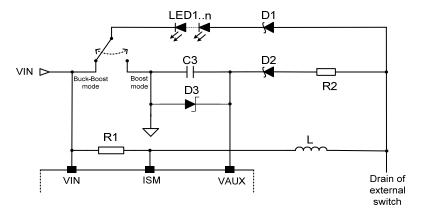

### b) Boost and Buck-Boost modes - the most simple boost/buck-boost circuit is shown in Figure 3

Control in Boost and Buck-boost mode is achieved by sensing the coil current in the series resistor Rs, connected between the two inputs of a current monitor within the control loop block. An output from the control loop drives the input of a comparator which drives the gate of the external NMOS switch transistor Q1 via the internal Gate Driver. When the switch is on, the drain voltage of Q1 is near zero. Current flows from VIN, via Rs, coil and switch to ground. This current ramps up until an upper threshold value is reached (see **Figure 4**). At this point GATE goes low, the switch is turned off and the drain voltage increases to either:

the load voltage VLEDS plus the forward voltage of D1 in Boost configuration,

or

the load voltage VLEDS plus the forward voltage of D1 plus VIN in Buck-boost configuration.

Current flows via Rs, coil, D1 and LED back to VIN (Buckboost mode), or GND (Boost mode). When the coil current has ramped down to a lower threshold value, GATE goes high, the switch is turned on again and the cycle of events repeats, resulting in continuous oscillation.

The feeback loop adjusts the NMOS switch duty cycle to stabilize the LED current in response to changes in external conditions, including input voltage and load voltage. Loop compensation is achieved by a single external capacitor C2, connected between SHP and SGND. Note that in reality, a load capacitor  $C_{\text{OUT}}$  is used, so that the LED current waveform shown is smoothed.

The average current in the sense resistor and coil, I<sub>RS</sub>, is equal to the average of the maximum and minimum threshold currents and the ripple current (hysteresis) is equal to the difference between the thresholds.

The average current in the LED,  $I_{LED}$ , is always less than  $I_{RS}$ . The feedback control loop adjusts the switch duty cycle, D, to achieve a set point at the sense resistor. This controls  $I_{RS}$ . During the interval  $t_{OFF}$ , the coil current flows through D1 and the LED load. During  $t_{ON}$ , the coil current flows through Q1, not the LEDs. Therefore the set point is modified by D using a gating function to control  $I_{LED}$  indirectly. In order to compensate internally for the effect of the gating function, a control factor,  $GI_{ADJ}$  is used.  $GI_{ADJ}$  is set by a pair of external resistors,  $R_{GI1}$  and  $R_{GI2}$ . (Figure 3.) This allows the sense voltage to be adjusted to an optimum level for power efficiency without significant error in the LED controlled current.

$$GI\_ADJ = \left(\frac{RGI1}{RGI1 + RGI2}\right)$$

Equation 2

(Boost and Buck-boost modes)

The control loop sets the duty cycle so that the sense resistor current is

$$I_{RS} = \left(\frac{0.225}{R_S}\right) \left(\frac{GI\_ADJ}{1-D}\right) \left(\frac{V_{ADJ}}{V_{REF}}\right)$$

Equation 3

(Boost and Buck-boost modes)

Figure 3. Boost and Buck-boost configuration

Figure 4. Operating waveforms (Boost and Buck-boost modes)

$I_{RS}$  equals the coil current. The coil is connected only to the switch and the schottky diode. The schottky diode passes the LED current. Therefore the average LED current is the coil current multiplied by the schottky diode duty cycle, 1-D.

### **Applications Information (cont.)**

$$I_{LED} = I_{RS} (1-D) = \left(\frac{0.225}{R_S}\right) GI\_ADJ \left(\frac{V_{ADJ}}{V_{REF}}\right)$$

(Boost and Buck-boost) **Equation 4**

This shows that the LED current depends on the ADJ pin voltage, the reference voltage and 3 resistor values (RS, RGI1 and RGI2). It is independent of the input and output voltages.

If the ADJ pin is connected to the REF pin, this simplifies to

$$I_{LED} = \left(\frac{0.225}{R_S}\right) GI\_ADJ$$

(Boost and Buck-boost)

Now  $I_{\text{LED}}$  is dependent only on the 3 resistor values.

Considering power dissipation and accuracy, it is useful to know how the mean sense voltage varies with input voltage and other parameters.

$$V_{RS} = I_{RS} R_S = 0.225 \left(\frac{GI\_ADJ}{1-D}\right) \left(\frac{V_{ADJ}}{V_{REF}}\right)$$

(Boost and Buck-boost) **Equation 5**

This shows that the sense voltage varies with duty cycle in Boost and Buck-boost configurations.

# **Applications Information (cont.)**

#### **APPLICATION CIRCUIT DESIGN**

External component selection is driven by the characteristics of the load and the input supply, since this will determine the kind of topology being used for the system. Component selection begins with the current setting procedure, the inductor/frequency setting and the MOSFET selection. Finally after selecting the freewheeling diode and the output capacitor (if needed), the application section will cover the PWM dimming and thermal feedback. The full procedure is greatly accelerated by the web **Calculator** spreadsheet, which includes fully automated component selection, and is available on the Diodes web site. However the full calculation is also given here.

Please note the following particular feature of the web Calculator. The GI ratio can be set for Automatic calculation, or it can be fixed at a chosen value. When optimizing a design, it is best first to optimize for the chosen voltage range of most interest, using the Automatic setting. In order to subsequently evaluate performance of the circuit over a wider input voltage range, fix the GI ratio in the Calculator input field, and then set the desired input voltage range.

Some components depend upon the switching frequency and the duty cycle. The switching frequency is regulated by the ZXLD1371 to a large extent, depending upon conditions. This is discussed in a later paragraph dealing with coil selection.

### **Duty Cycle Calculation and Topology Selection**

The duty cycle is a function of the input and output voltages. Approximately, the MOSFET switching duty cycle is

$$D_{BUCK} \approx \frac{V_{OUT}}{V_{IN}}$$

for Buck

$D_{BOOST} \approx \frac{V_{OUT} - V_{IN}}{V_{OUT}}$  for Boost

$D_{BB} \approx \frac{V_{OUT} + V_{IN}}{V_{OUT} + V_{IN}}$  for Buck-Boost

Because D must always be a positive number less than 1, these equations show that

$V_{OUT} < V_{IN}$  for Buck (voltage step-down)  $V_{OUT} > V_{IN}$  for Boost (voltage step-up)  $V_{OUT} > or = or < V_{IN}$  for Buck-boost (voltage step-down or step-up)

This allows us to select the topology for the required voltage range.

More exact equations are used in the web Calculator. These are:

$\begin{array}{lll} D_{BUCK} &= \frac{V_{OUT} + V_F + I_{OUT}(R_S + R_{COIL})}{V_{IN} + V_F - V_{DSON}} & \text{for Buck} \\ \\ D_{BOOST} &= \frac{V_{OUT} - V_{IN} + I_{IN}(R_S + R_{COIL}) + V_F}{V_{OUT} + V_F - V_{DSON}} & \text{for Boost} & \textbf{Equation 7} \\ \\ D_{BB} &= \frac{V_{OUT} + V_F + (I_{IN} + I_{OUT})(R_S + R_{COIL})}{V_{OUT} + V_{IN} + V_F - V_{DSON}} & \text{for Buck-boost} \\ \\ \text{where} & V_F &= \text{schottky diode forward voltage, estimated for the expected coil current, I}_{COIL} \\ \\ V_{DSON} &= \text{MOSFET drain source voltage in the ON condition (dependent on R}_{DSON} \text{ and drain current} = I}_{COIL}) \\ \\ R_{COIL} &= DC \text{ winding resistance of L1} \end{array}$

# **Applications Information (cont.)**

The additional terms are relatively small, so the exact equations will only make a significant difference at lower operating voltages at the input and output, i.e. low input voltage or a small number of LEDs connected in series. The estimates of  $V_F$  and  $V_{DSON}$  depend on the coil current. The mean coil current,  $I_{COIL}$  depends upon the topology and upon the mean terminal currents as follows:

$$I_{CO|L} = I_{LED}$$

for Buck

$I_{CO|L} = I_{IN}$  for Boost Equation 8

$I_{CO|L} = I_{IN} + I_{LED}$  for Buck-boost

$I_{LED}$  is the target LED current and is already known.  $I_{IN}$  will be calculated with some accuracy later, but can be estimated now from the electrical power efficiency. If the expected efficiency is roughly 90%, the output power  $P_{OUT}$  is 90% of the input power,  $P_{IN}$ , and the coil current is estimated as follows.

$$\begin{array}{c} P_{OUT} & \approx 0.9 \; P_{IN} \\ \\ \text{or} \\ \\ I_{LED} \; N \; V_{LED} \; \approx 0.9 \; I_{IN} \; V_{IN} \\ \end{array}$$

where N is the number of LEDs connected in series, and V<sub>LED</sub> is the forward voltage drop of a single LED at I<sub>LED</sub>.

So

$$I_{IN} \approx \frac{I_{LED} N V_{LED}}{0.9 V_{IN}}$$

Equation 9

**Equation 9** can now be used to find I<sub>COIL</sub> in **Equation 8**, which can then be used to estimate the small terms in **Equation 7**. This completes the calculation of Duty Cycle and the selection of Buck, Boost or Buck-boost topology.

An initial estimate of duty cycle is required before we can choose a coil. In **Equation** 7, the following approximations are recommended:

$$\begin{array}{lll} V_F & = 0.5V \\ I_{IN} \times (R_S + R_{COIL}) & = 0.5V \\ I_{OUT} \times (R_S + R_{COIL}) & = 0.5V \\ V_{DSON} & = 0.1V \\ (I_{IN} + I_{OUT})(R_S + R_{COIL}) & = 1.1V \\ \end{array}$$

#### Then Equation 7 becomes

$$\begin{array}{ll} D_{\text{BUCK}} & \approx \frac{V_{\text{OUT}} + 1}{V_{\text{IN}} + 0.4} & \text{for Buck} \\ \\ D_{\text{BOOST}} & \approx \frac{V_{\text{OUT}} - V_{\text{IN}} + 1}{V_{\text{OUT}} + 0.4} & \text{for Boost} & \text{Equation 7a} \\ \\ D_{\text{BB}} & \approx \frac{V_{\text{OUT}} + 1.6}{V_{\text{OUT}} + V_{\text{IN}} + 0.4} & \text{for Buck-boost} \end{array}$$

### **Setting the LED Current**

The LED current requirement determines the choice of the sense resistor Rs. This also depends on the voltage on the ADJ pin and the voltage on the GI pin, according to the topology required.

The ADJ pin may be connected directly to the internal 1.25V reference ( $V_{REF}$ ) to define the nominal 100% LED current. The ADJ pin can also be driven with an external dc voltage between 125mV and 1.25V to adjust the LED current proportionally between 10% and 100% of the nominal value.

For a divider ratio GI\_ADJ greater than 0.65V, the ZXLD1371 operates in Buck mode when  $V_{ADJ}$  = 1.25V. If GI\_ADJ is less than 0.65V (typical), the device operates in Boost or buck-Boost mode, according to the load connection. This 0.65V threshold varies in proportion to  $V_{ADJ}$ , i.e., the Buck mode threshold voltage is 0.65  $V_{ADJ}$ /1.25 V.

ADJ and GI are high impedance inputs within their normal operating voltage ranges. An internal 1.3V clamp protects the device against excessive input voltage and limits the maximum output current to approximately 4% above the maximum current set by V<sub>REF</sub> if the maximum input voltage is exceeded.

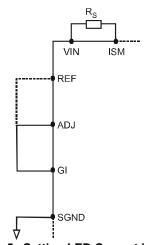

#### **Buck topology**

In Buck mode, GI is connected to ADJ as in **Figure 5**. The LED current depends only upon  $R_S$ ,  $V_{ADJ}$  and  $V_{REF}$ . From **Equation 1** above.

$$R_{SBUCK} = \left(\frac{0.218}{I_{LED}}\right) \left(\frac{V_{ADJ}}{V_{REF}}\right)$$

Equation 10

If ADJ is directly connected to VREF, this becomes:

$$R_{SBUCK} = \left(\frac{0.218}{I_{LED}}\right)$$

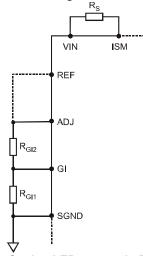

#### Boost and Buck-boost topology

For Boost and Buck-boost topologies, the LED current depends upon the resistors,  $R_S$ ,  $R_{GI1}$ , and  $R_{GI2}$  as in **Equations 4** and **2** above. There is more than one degree of freedom. That is to say, there is not a unique solution. From **Equation 4**,

$$R_{SBoostBB} = \left(\frac{0.225}{I_{LED}}\right) GI\_ADJ \left(\frac{V_{ADJ}}{V_{REF}}\right)$$

Equation 11

If ADJ is connected to REF, this becomes

$$R_{SBoostBB} = \left(\frac{0.225}{I_{LED}}\right) GI\_ADJ$$

GI\_ADJ is given by **Equation 2**, repeated here for convenience:

$$GI\_ADJ = \left(\frac{RGI1}{RGI1 + RGI2}\right)$$

Figure 5. Setting LED Current in Buck Configuration

Figure 6. Setting LED current in Boost and Buck-boost configurations

Note that from considerations of ZXLD1371 input bias current, the recommended limits for R<sub>GI1</sub> are:

$$22k\Omega$$

<  $R_{GI1}$  <  $100k\Omega$  Equation 12

The additional degree of freedom allows us to select GI\_ADJ within limits but this may affect overall performance a little. As mentioned above, the working voltage range at the GI pin is restricted. The permitted range of GI\_ADJ in Boost or Buck-boost configuration is

The mean voltage across the sense resistor is

$$V_{RS} = I_{COIL} R_S$$

Equation 14

Note that if  $GI\_ADJ$  is made larger, these equations show that  $R_S$  is increased and  $V_{RS}$  is increased. Therefore, for the same coil current, the dissipation in  $R_S$  is increased. So, in some cases, it is better to minimize  $GI\_ADJ$ . However, consider **Equation 5**. If ADJ is connected to REF, this becomes

$$V_{RS} = 0.225 \left( \frac{GI\_ADJ}{1-D} \right)$$

This shows that  $V_{RS}$  becomes smaller than 225mV if GI\_ADJ < 1 - D. If also D is small,  $V_{RS}$  can become too small. For example if D = 0.2, and GI\_ADJ is the minimum value of 0.2, then  $V_{RS}$  becomes 0.225\* 0.2 / 0.8 = 56.25 mV. This will increase the LED current error due to small offsets in the system, such as mV drop in the copper printed wiring circuit, or offset uncertainty in the ZXLD1371. If now, GI\_ADJ is increased to 0.4 or 0.5,  $V_{RS}$  is increased to a value greater than 100mV.

This will give small enough I<sub>LED</sub> error for most practical purposes. Satisfactory operation will be obtained if  $V_{RS}$  is more than about 80mV. This means GI ADJ should be greater than  $(1-D_{MIN})$  \*  $80/225 = (1-D_{MIN})$  \* 0.355.

There is also a maximum limit on  $V_{RS}$  which gives a maximum limit for GI\_ADJ. If  $V_{RS}$  exceeds approximately 300mV, or 133% of 225mV, the STATUS output may indicate an over-current condition. This will happen for larger  $D_{MAX}$ . Therefore, together with the requirement of **Equation 13**, the recommended range for GI\_ADJ is

$$0.355 (1-D_{MIN}) < GI ADJ < 1.33 (1-D_{MAX})$$

**Equation 15**

An optimum compromise for GI ADJ has been suggested, i.e.

$$GI ADJ_{AUTO} = 1 - D_{MAX}$$

**Equation 16**

This value has been used for the "Automatic" setting of the web Calculator. If 1-D<sub>MAX</sub> is less than 0.2, then GI\_ADJ is set to 0.2. If 1-D<sub>MAX</sub> is greater than 0.5 then GI\_ADJ is set to 0.5.

Once GI\_ADJ has been selected, a value of RGI1 can be selected from **Equation 12**. Then RGI2 is calculated as follows, rearranging **Equation 2**:

$$R_{GI2} = R_{GI1} \left( \frac{1 - GI\_ADJ}{GI\_ADJ} \right)$$

**Equation 17**

For example to drive 12 LEDS at a current of 350mA from a 12V supply requires Boost configuration. Each LED has a forward voltage of 3.2V at 350mA, so Vout = 3.2\*12 = 38.4V. From **Equation 6**, the duty cycle is approximately

$$\frac{(V_{OUT}-V_{IN})}{V_{OUT}} = \frac{(38.4-12)}{38.4} = 0.6875$$

From **Equation 16**, we set GI ADJ to 1 - D = 0.3125.

IF  $R_{GI1}$  = 33k $\Omega$ , then from **Equation 17**,  $R_{GI2}$  = 33000 \* (1 -0.3125) / 0.3125 = 72.6k $\Omega$ . Let us choose the preferred value  $R_{GI2}$  = 75k $\Omega$ . Now GI\_ADJ is adjusted to the new value, using **Equation 2**.

$$GI\_ADJ = \left(\frac{RGI1}{RGI1 + RGI2}\right) = \frac{33k}{33k + 75k} = 0.305$$

Now we calculate Rs from Equation 11. Assume ADJ is connected to REF.

$$R_{SBoostBB} = \left(\frac{0.225}{I_{LED}}\right) GI\_ADJ\left(\frac{V_{ADJ}}{V_{REF}}\right) = \frac{0.225}{0.35} * 0.305 = 0.196 \Omega$$

A preferred value of  $R_{SBoostBB}$  = 0.2 $\Omega$  will give the desired LED current with an error of 2% due to the preferred value selection.

Table 1 shows typical resistor values used to determine the GI\_ADJ ratio with E24 series resistors.

Table 1

| GI ratio | RGI1  | RG2             |

|----------|-------|-----------------|

| 0.2      | 30kΩ  | 120kΩ           |

| 0.25     | 33kΩ  | 100kΩ           |

| 0.3      | 39kΩ  | 91kΩ            |

| 0.35     | 30kΩ  | 56k $Ω$         |

| 0.4      | 100kΩ | 150kΩ           |

| 0.45     | 51kΩ  | 62kΩ            |

| 0.5      | 30kΩ  | $30$ k $\Omega$ |

This completes the LED current setting.

# **Applications Information (cont.)**

#### **Inductor Selection and frequency Control**

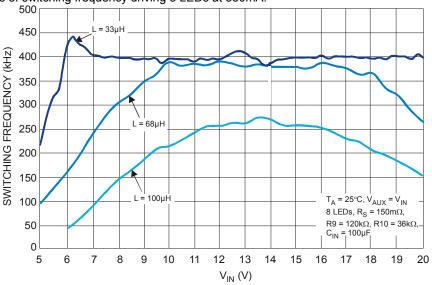

The selection of the inductor coil, L1, requires knowledge of the switching frequency and current ripple, and also depends on the duty cycle to some extent. In the hysteretic converter, the frequency depends upon the input and output voltages and the switching thresholds of the current monitor. The peak-to-peak coil current is adjusted by the ZXLD1371 to control the frequency to a fixed value. This is done by controlling the switching thresholds within particular limits. This effectively much reduces the overall frequency range for a given input voltage range. Where the input voltage range is not excessive, the frequency is regulated to approximately 390kHz. This is helpful in terms of EMC and other system requirements. **Figure 7** shows practical results of switching frequency driving 8 LEDs at 350mA.

Figure 7. Frequency vs. V<sub>IN</sub> for Boost LED Driver with 350mA LED Current and Various Inductor Values

For larger input voltage variation, or when the choice of coil inductance is not optimum, the switching frequency may depart from the regulated value, but the regulation of LED current remains successful. If desired, the frequency can to some extent be increased by using a smaller inductor, or decreased using a larger inductor. The web Calculator will evaluate the frequency across the input voltage range and the effect of this upon power efficiency and junction temperatures.

Determination of the input voltage range for which the frequency is regulated may be required. This calculation is very involved, and is not given here. However the performance in this respect can be evaluated within the web Calculator for the chosen inductance.

The inductance is given as follows in terms of peak-to-peak ripple current in the coil, ∆I<sub>L</sub> and the MOSFET on time, t<sub>ON</sub>.

$$\begin{aligned} & \text{L1} = \{\, V_{\text{IN}} - \text{N} \, V_{\text{LED}} - \, I_{\text{OUT}} \, (R_{\text{DSON}} \, + R_{\text{COIL}} + \, R_{\text{S}}) \,\} \, \, \frac{t_{\text{ON}}}{\Delta I_{\text{L}}} & \text{for Buck} \\ & \text{L1} = \{\, V_{\text{IN}} - \, \, I_{\text{IN}} (R_{\text{DSON}} \, + R_{\text{COIL}} + \, R_{\text{S}}) \,\} \, \, \frac{t_{\text{ON}}}{\Delta I_{\text{L}}} & \text{for Boost} \\ & \text{L1} = \left\{\, V_{\text{IN}} - \, \, \left( I_{\text{IN}} + I_{\text{OUT}} \, \right) \, (R_{\text{DSON}} \, + R_{\text{COIL}} + \, R_{\text{S}}) \,\right\} \, \, \frac{t_{\text{ON}}}{\Delta I_{\text{L}}} & \text{for Buck-boost} \end{aligned}$$

Therefore In order to calculate L1, we need to find  $I_{IN}$ ,  $t_{ON}$ , and  $\Delta I_{L}$ . The effects of the resistances are small and will be estimated.

I<sub>IN</sub> is estimated from **Equation 9**.

t<sub>ON</sub> is related to switching frequency, f, and duty cycle, D, as follows:

$$t_{ON} = \frac{D}{f}$$

Equation 19

As the regulated frequency is known, and we have already found D from **Equation 7** or the approximation **Equation 7b**, this allows calculation of  $t_{ON}$ .

The ZXLD1371 sets the ripple current,  $\Delta I_L$ , to between nominally 10% and 30% of the mean coil current,  $I_{COIL}$ , which is found from **Equation 8**. The device adjusts the ripple current within this range in order to regulate the switching frequency. We therefore need to use a  $\Delta I_L$  value of 20% of  $I_{COIL}$  to find an inductance which is optimized for the input voltage range. The range of ripple current control is also modulated by other circuit parameters as follows.

Targe of hippie current control is also modulated

$$\Delta I_{LMAX} = \left\{ 0.06 + 0.24 \begin{pmatrix} V_{ADJ} \\ V_{REF} \end{pmatrix} \right\} \frac{1-D}{GI\_ADJ} I_{COIL}$$

$$\Delta I_{LMIN} = \left\{ 0.02 + 0.08 \begin{pmatrix} V_{ADJ} \\ V_{REF} \end{pmatrix} \right\} \frac{1-D}{GI\_ADJ} I_{COIL}$$

$$\Delta I_{LMID} = \left\{ 0.04 + 0.16 \begin{pmatrix} V_{ADJ} \\ V_{REF} \end{pmatrix} \right\} \frac{1-D}{GI\_ADJ} I_{COIL}$$

**Equation 20**

If ADJ is connected to REF, this simplifies to

$$\Delta I_{LMAX} = 0.3 \frac{1-D}{GI\_ADJ} I_{COIL}$$

$$\Delta I_{LMIN} = 0.1 \frac{1-D}{GI\_ADJ} I_{COIL}$$

$$\Delta I_{LMID} = 0.2 \frac{1-D}{GI\_ADJ} I_{COIL}$$

**Equation 20a**

where  $\Delta I_{LMID}$  is the value we must use in **Equation 18**. We have now established the inductance value.

The chosen coil should saturate at a current greater than the peak sensed current. This saturation current is the DC current for which the inductance has decreased by 10% compared to the low current value.

Assuming ±10% ripple current, we can find this peak current from **Equation 8**, adjusted for ripple current:

$\begin{array}{lll} I_{COILPEAK} = 1.1 \ I_{LED} & \text{for Buck} \\ I_{COILPEAK} = 1.1 \ I_{INMAX} & \text{for Boost} \\ I_{COILPEAK} = 1.1 \ I_{INMAX} + I_{LED} & \text{for Buck-boost} \end{array}$

**Equation 21**

where  $I_{INMAX}$  is the value of  $I_{IN}$  at minimum  $V_{IN}$ .

The mean current rating is also a factor, but normally the saturation current is the limiting factor.

The following websites may be useful in finding suitable components

www.coilcraft.com www.niccomp.com www.wuerth-elektronik.de

#### **MOSFET Selection**

The ZXLD1371 requires an external NMOS FET as the main power switch with a voltage rating at least 15% higher than the maximum circuit voltage to ensure safe operation during the overshoot and ringing of the switch node. The current rating is recommended to be at least 10% higher than the average transistor current. The power rating is then verified by calculating the resistive and switching power losses.

$$P = P_{resistive} + P_{switching}$$

#### Resistive power losses

The resistive power losses are calculated using the RMS transistor current and the MOSFET on-resistance. Calculate the current for the different topologies as follows:

#### **Buck mode**

#### **Boost / Buck-boost mode**

$$I_{MOSFETMAX} = \frac{I_{LED}}{1 - D_{MAX}}$$

During the on-time, the MOSFET switch current is equal to the coil current. The rms MOSFET current is  $I_{COIL}$   $\sqrt{D}$  where  $I_{COIL}$  is the mean coil current. Therefore the approximate RMS current in the MOSFET during  $t_{ON}$  is: **Buck mode**

$$I_{MOSFETRMS} = I_{LED} \sqrt{D}$$

#### **Boost / Buck-boost mode**

$$I_{MOSFETRMS} = \frac{\sqrt{D}}{1 - D} x I_{LED}$$

The resistive power dissipation of the MOSFET is:

### **Switching power losses**

Calculating the switching MOSFET's switching loss depends on many factors that influence both turn-on and turn-off. Using a first order rough approximation, the switching power dissipation of the MOSFET is:

$$P_{switching} = \frac{C_{RSS} \times V^2_{IN} \times f_{sw} \times I_{LOAD}}{I_{GATE}}$$

where

C<sub>RSS</sub> is the MOSFET's reverse-transfer capacitance (a data sheet parameter),

f<sub>SW</sub> is the switching frequency,

$I_{\mathsf{GATE}}$  is the MOSFET gate-driver's sink/source current at the MOSFET's turn-on threshold.

Matching the MOSFET with the controller is primarily based on the rise and fall time of the gate voltage. The best rise/fall time in the application is based on many requirements, such as EMI (conducted and radiated), switching losses, lead/circuit inductance, switching frequency, etc. How fast a MOSFET can be turned on and off is related to how fast the gate capacitance of the MOSFET can be charged and discharged. The relationship between C (and the relative total gate charge Qg), turn-on/turn-off time and the MOSFET driver current rating can be written as:

$$dt = \frac{dV \cdot C}{I} = \frac{Qg}{I}$$

where

dt = turn-on/turn-off time

dV = gate voltage

C = gate capacitance = Qg/V

I = drive current – constant current source (for the given voltage value)

Here the constant current source" I " usually is approximated with the peak drive current at a given driver input voltage. Example 1)

Using the DMN6068 MOSFET ( $V_{DS(MAX)} = 60V$ ,  $I_{D(MAX)} = 8.5A$ ):

$$\rightarrow$$

Q<sub>G</sub> = 10.3nC at V<sub>GS</sub> = 10V

ZXLD1371 I<sub>PEAK</sub> = I<sub>GATE</sub> = 300mA

$$dt = \frac{Q_g}{I_{PEAK}} = \frac{10.3nC}{300mA} = 35ns$$

Assuming that cumulatively the rise time and fall time can account for a maximum of 10% of the period, the maximum frequency allowed in this condition is:

$$t_{PERIOD} = 20*dt \rightarrow f = 1/t_{PERIOD} = 1.43MHz$$

This frequency is well above the max frequency the device can handle, therefore the DNM6068 can be used with the ZXLD1371 in the whole spectrum of frequencies recommended for the device (from 300kHz to 1MHz).

Example 2)

Using the ZXMN6A09K ( $V_{DS(MAX)} = 60V$ ,  $I_{D(MAX)} = 12.2A$ ):

$$\rightarrow$$

Q<sub>G</sub> = 29nC at V<sub>GS</sub> = 10V

ZXLD1371 I<sub>PEAK</sub> = 300mA

$$dt = \frac{Q_g}{I_{PEAK}} = \frac{29nC}{300mA} = 97ns$$

Assuming that cumulatively the rise time and fall time can account for a maximum of 10% of the period, the maximum frequency allowed in this condition is:

$$t_{PERIOD} = 20*dt$$

$\rightarrow$   $f = 1/t_{PERIOD} = 515kHz$

This frequency is within the recommended frequency range the device can handle, therefore the ZXMN6A09K is recommended to be used with the ZXLD1371 for frequencies from 300kHz to 500kHz).

The recommended total gate charge for the MOSFET used in conjunction with the ZXLD1371 is less than 30nC.

#### **Junction Temperature Estimation**

Finally, the ZXLD1371 junction temperature can be estimated using the following equations:

Total supply current of ZXLD1371:

$$I_{OTOT} \approx I_{O} + f \cdot Q_{G}$$

Where  $I_Q$  = total quiescent current  $I_{Q-IN} + I_{Q-AUX}$

Power consumed by ZXLD1371

$$P_{IC} = V_{IN} \cdot (I_O + f \cdot Qg)$$

Or in case of separate voltage supply, with V<sub>AUX</sub> < 15V

$$P_{IC} = V_{IN} \cdot I_{Q-IN} + V_{aux} \cdot (I_{Q-AUX} + f \cdot Qg)$$

$$T_{J} = T_{A} + P_{IC} \cdot \theta_{JA} = T_{A} + P_{IC} \cdot (\theta_{JC} + \theta_{CA})$$

Where the total quiescent current  $I_{QTOT}$  consists of the static supply current ( $I_Q$ ) and the current required to charge and discharge the gate of the power MOSFET. Moreover the part of thermal resistance between case and ambient depends on the PCB characteristics.

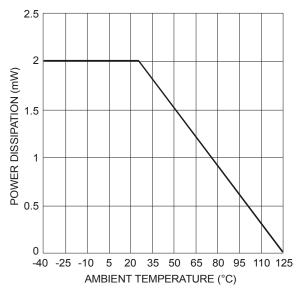

Figure 8. Power derating curve for ZXLD1370 mounted on test board according to JESD51

### **Applications Information (cont.)**

#### **Diodes Selection**

For maximum efficiency and performance, the rectifier (D1) should be a fast low capacitance Schottky diode\* with low reverse leakage at the maximum operating voltage and temperature. The Schottky diode also provides better efficiency than silicon PN diodes, due to a combination of lower forward voltage and reduced recovery time.

It is important to select parts with a peak current rating above the peak coil current and a continuous current rating higher than the maximum output load current. In particular, it is recommended to have a voltage rating at least 15% higher than the maximum transistor voltage to ensure safe operation during the ringing of the switch node and a current rating at least 10% higher than the average diode current. The power rating is verified by calculating the power loss through the diode.

The higher forward voltage and overshoot due to reverse recovery time in silicon diodes will increase the peak voltage on the Drain of the external MOSFET. If a silicon diode is used, care should be taken to ensure that the total voltage appearing on the Drain of the external MOSFET, including supply ripple, does not exceed the specified maximum value.

\*A suitable Schottky diode for a switching current of up to about 1.5A would be PDS3100 (Diodes Inc).

#### **Output Capacitor**

An output capacitor may be required to limit interference or for specific EMC purposes. For boost and buck-boost regulators, the output capacitor provides energy to the load when the freewheeling diode is reverse biased during the first switching subinterval. An output capacitor in a buck topology will simply reduce the LED current ripple below the inductor current ripple. In other words, this capacitor changes the current waveform through the LED(s) from a triangular ramp to a more sinusoidal version without altering the mean current value.

In all cases, the output capacitor is chosen to provide a desired current ripple of the LED current (usually recommended to be less than 40% of the average LED current).

#### **Buck:**

$$C_{OUTPUT} = \frac{\Delta I_{L-PP}}{8x f_{SW} x r_{LED} x \Delta I_{LED-PP}}$$

#### **Boost and Buck-boost**

$$C_{\text{OUTPUT}} = \frac{D x \Delta I_{\text{L-PP}}}{f_{\text{SW}} x r_{\text{LED}} x \Delta I_{\text{LED-PP}}}$$

where:

- ΔI<sub>1-PP</sub> is the ripple of the inductor current, usually ± 20% of the average sensed current

- Δl<sub>LED-PP</sub> is the ripple of the LED current, it should be <40% of the LEDs average current

- f<sub>sw</sub> is the switching frequency (From graphs and calculator)

- r<sub>LED</sub> is the dynamic resistance of the LEDs string (n times the dynamic resistance of the single LED from the datasheet of the LED manufacturer).

The output capacitor should be chosen to account for derating due to temperature and operating voltage. It must also have the necessary RMS current rating. The minimum RMS current for the output capacitor is calculated as follows:

#### **Buck**

$$I_{\text{COUTPUTRMS}} = \frac{I_{\text{LED-PP}}}{\sqrt{12}}$$

#### **Boost and Buck-boost**

$$I_{\text{COUTPUTRMS}} = I_{\text{LED}} \sqrt{\frac{D_{\text{MAX}}}{1 - D_{\text{MAX}}}}$$

Ceramic capacitors with X7R dielectric are the best choice due to their high ripple current rating, long lifetime, and performance over the voltage and temperature ranges.

### **Applications Information (cont.)**

### **Input Capacitor**

The input capacitor can be calculated knowing the input voltage ripple  $\Delta V_{\text{IN-PP}}$  as follows:

#### **Buck**

$$C_{IN} = \frac{D x (1-D) x I_{LED}}{f_{SW} x \Delta V_{IN-PP}}$$

Use D = 0.5 as worst case

#### **Boost**

$$C_{IN} = \frac{\Delta I_{L-PP}}{8x f_{SW} x \Delta V_{IN-PP}}$$

#### **Buck-boost**

$$C_{IN} = \frac{D \times I_{LED}}{f_{SW} \times \Delta V_{IN-PP}}$$

Use D = D<sub>MAX</sub> as worst case

The minimum RMS current for the output capacitor is calculated as follows:

#### Buck

$$I_{CIN-RMS} = I_{LED} x \sqrt{Dx(1-D)}$$

use D=0.5 as worst case

#### **Boost**

$$I_{CIN-RMS} = \frac{I_{L-PP}}{\sqrt{12}}$$

#### **Buck-boost**

$$I_{CIN-RMS} = I_{LED} x \sqrt{\frac{D}{(1-D)}}$$

Use D=D<sub>MAX</sub> as worst case

### **LED Current Dimming**

The ZXLD1371 has 3 dimming methods for reducing the average LED current

- 1. DC dimming using the ADJ pin

- 2. PWM dimming using the PWM pin

- 3. DC dimming for thermal protection using the TADJ pin.

#### **DC Dimming**

The ZXLD1371 has a clamp on the ADJ pin to prevent over-driving of the LED current which results in the maximum voltage being applied to internal circuitry is the reference voltage. This provides a 10:1 dynamic range of dc LED current adjustment.

The equation for DC dimming of the LED current is approximately:

$$\begin{split} I_{LED\_DIM} = & I_{LED\_NOM} \left( \frac{V_{ADJ}}{V_{REF}} \right) \\ & \text{Where} \\ & I_{LED\_DIM} \quad \text{is the dimmed LED current} \\ & I_{LED\ NOM} \text{ is the LED current with } V_{ADJ} = 1.25V \end{split}$$

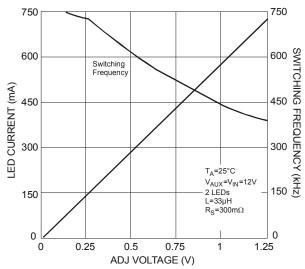

One consequence of DC dimming is that as the ADJ pin voltage is reduced the sense voltage will also be reduced which has an impact on accuracy and switching frequency especially at lower ADJ pin voltages.

Figure 9. LED Current and switching frequency vs. ADJ Voltage

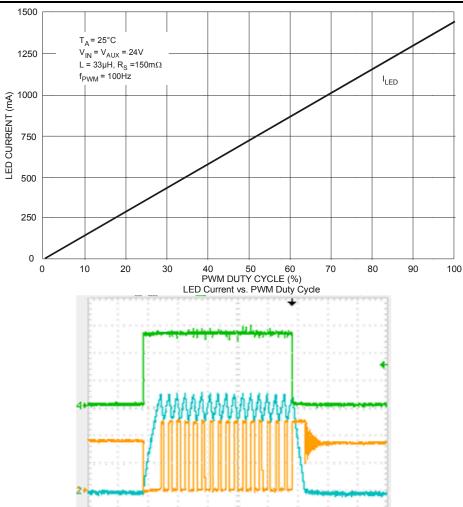

### **PWM Output Current Control & Dimming**

The ZXLD1371 has a dedicated PWM dimming input that allows a wide dimming frequency range from 100Hz to 1kHz with up to 1000:1 resolution; however higher dimming frequencies can be used – at the expense of dimming dynamic range and accuracy.

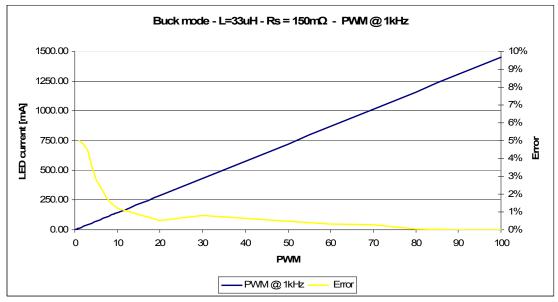

Typically, for a PWM frequency of 1kHz, the error on the current linearity is lower than 5%; in particular the accuracy is better than 1% for PWM from 5% to 100%. This is shown in the graph below:

Figure 10. LED Current Linearity and Accuracy with PWM Dimming at 1kHz

For a PWM frequency of 100Hz, the error on the current linearity is lower than 2.5%; it becomes negligible for PWM greater than 5%. This is shown in the graph below:

Figure 11. LED Current Linearity and Accuracy with PWM Dimming at 100Hz

The PWM pin is designed to be driven by both 3.3V and 5V logic levels and as such doesn't require open collector/drain drive. It can also be driven by an open drain/collector transistor. In this case the designer can either use the internal pull-up network or an external pull-up network in order to speed-up PWM transitions, as shown in the Boost/ Buck-Boost section.

### **Applications Information (cont.)**

LED current can be adjusted digitally, by applying a low frequency PWM logic signal to the PWM pin to turn the controller on and off. This will produce an average output current proportional to the duty cycle of the control signal. During PWM operation, the device remains powered up and only the output switch is gated by the control signal.

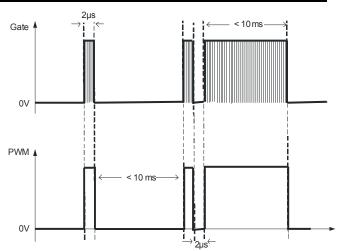

The PWM signal can achieve very high LED current resolution. In fact, dimming down from 100% to 0, a minimum pulse width of 2µs can be achieved resulting in very high accuracy. While the maximum recommended pulse is for the PWM signal is10ms.

Figure 12. PWM Dimming Minimum and Maximum Pulse

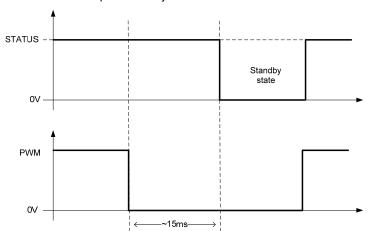

The device can be put in standby by taking the PWM pin to ground, or pulling it to a voltage below 0.4V with a suitable open collector NPN or open drain NMOS transistor, for a time exceeding 15ms (nominal). In the shutdown state, most of the circuitry inside the device is switched off and residual quiescent current will be typically 90µA. In particular, the Status pin will go down to GND while the FLAG and REF pins will stay at their nominal values.

Figure 13. Stand-by State From PWM Signal

#### Thermal Control of LED Current

For thermal control of the LEDs, the ZXLD1371 monitors the voltage on the TADJ pin and reduces output current if the voltage on this pin falls below 625mV. An external NTC thermistor and resistor can therefore be connected as shown below to set the voltage on the TADJ pin to 625mV at the required temperature threshold. This will give 100% LED current below the threshold temperature and a falling current above it as shown in the graph. The temperature threshold can be altered by adjusting the value of Rth and/or the thermistor to suit the requirements of the chosen LED.

The Thermal Control feature can be disabled by connecting TADJ directly to REF.

Here is a simple procedure to design the thermal feedback circuit:

- 1) Select the temperature threshold T<sub>threshold</sub> at which the current must start to decrease

- 2) Select the Thermistor TH1 (both resistive value at 25°C and beta)

- 3) Select the value of the resistor  $R_{th}$  as  $R_{th}$  = TH at  $T_{threshold}$

# **Applications Information (cont.)**

Thermal network response in Buck configuration with: Rth =  $1.8k\Omega$  and TH1= $10k\Omega$  (beta =3900)

Figure 14. Thermal Feedback Network

The thermistor resistance, R<sub>T</sub>, at a temperature of T degrees Kelvin is given by

$$R_T = R_R e^{B\left(\frac{1}{T} - \frac{1}{T_R}\right)}$$

Where

$R_{\text{R}}$  is the thermistor resistance at the reference temperature,  $T_{\text{R}}$

$T_R$  is the reference temperature, in Kelvin, normally 273 + 25 = 298K (25°C)

B is the "beta" value of the thermistor.

For example,

- 1) Temperature threshold  $T_{threshold} = 273 + 70 = 343K$  (70°C)

- 2) TH1 =  $10k\Omega$  at  $25^{\circ}$ C and B =  $3900 \rightarrow R_T = 1.8k\Omega$  @  $70^{\circ}$ C

- 3)  $R_{th} = R_T$  at  $T_{threshold} = 1.8k\Omega$

#### **Over-Temperature Shutdown**

The ZXLD1371 incorporates an over-temperature shutdown circuit to protect against damage caused by excessive die temperature. A warning signal is generated on the STATUS output when die temperature exceeds 125°C nominal and the output is disabled when die temperature exceeds 150°C nominal. Normal operation resumes when the device cools back down to 125°C.

### **Applications Information (cont.)**

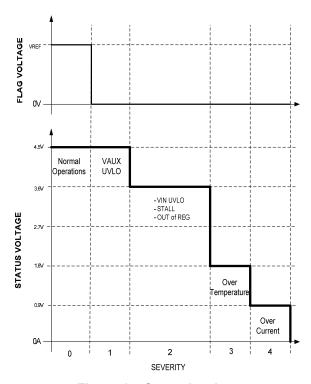

### **FLAG/STATUS Outputs**

The FLAG/STATUS outputs provide a warning of extreme operating or fault conditions. FLAG is an open-drain logic output, which is normally off, but switches low to indicate that a warning, or fault condition exists. STATUS is a DAC output, which is normally high (4.5V), but switches to a lower voltage to indicate the nature of the warning/fault.

Conditions monitored, the method of detection and the nominal STATUS output voltage are given in the following table (Note 15):

Table 2

| Warning/Fault condition                                        | Severity<br>(Note 16) | Monitored parameters                          | FLAG | Nominal STATUS voltage |

|----------------------------------------------------------------|-----------------------|-----------------------------------------------|------|------------------------|

| Normal operation                                               |                       |                                               | Н    | 4.5V                   |

| Supply under voltage                                           | 1                     | V <sub>AUX</sub> < 5.0V                       | L    | 4.5V                   |

| Supply under-voltage                                           | 2                     | V <sub>IN</sub> < 5.6V                        | L    | < 3.6V                 |

| Output current out of regulation (Note 17)                     | 2                     | V <sub>SHP</sub> outside normal voltage range | L    | 3.6V                   |

| Driver stalled with switch 'on', or 'off' (Note 18)            | 2                     | t <sub>ON</sub> , or t <sub>OFF</sub> > 100μs | L    | 3.6V                   |

| Device temperature above maximum recommended operating value   | 3                     | T <sub>J</sub> > 125°C                        | L    | 1.8V                   |

| Sense resistor current I <sub>RS</sub> above specified maximum | 4                     | V <sub>SENSE</sub> > 0.3V                     | L    | 0.9V                   |

Notes:

- 15. These STATUS pin voltages apply for an input voltage, V<sub>IN</sub>, of 7.5V < V<sub>IN</sub> < 60V. Below 7.5V the STATUS pin voltage levels reduce and therefore may not report the correct status. For 5.4V < V<sub>IN</sub> < 7.5V the flag pin still reports an error by going low. At low V<sub>IN</sub> in Boost and Buck-boost modes an over-current status may be indicated when operating at high boost ratios this due to the feedback loop increasing the sense voltage.

- 16. Severity 1 denotes lowest severity.

- 17. This warning will be indicated if the output power demand is higher than the available input power; the loop may not be able to maintain regulation.

- 18. This warning will be indicated if the gate pin stays at the same level for greater than 100µs (e.g. the output transistor cannot pass enough current to reach the upper switching threshold).

Figure 15. Status levels

February 2012

© Diodes Incorporated

### **Applications Information (cont.)**

In the event of more than one fault/warning condition occurring, the higher severity condition will take precedence. E.g. 'Excessive coil current' and 'Out of regulation' occurring together will produce an output of 0.9V on the STATUS pin.

If  $V_{ADJ}$ >1.7V,  $V_{SENSE}$  may be greater than the excess coil current threshold in normal operation and an error will be reported. Hence, STATUS and FLAG are only guaranteed for  $V_{ADJ}$ <= $V_{REF}$ .

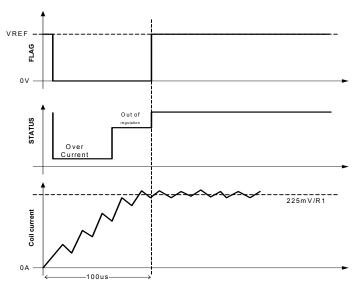

Diagnostic signals should be ignored during the device start – up for  $100\mu s$ . The device start up sequence will be initiated both during the first power on of the device or after the PWM signal is kept low for more than 15ms, initiating the standby state of the device.

In particular, during the first 100µs the diagnostic is signaling an over-current then an out-of-regulation status. These two events are due to the charging of the inductor and are not true fault conditions.

Figure 16. Diagnostic during Start-up

#### **Reduced Input Voltage Operation**