# iW-RainboW-G27D i.MX8 QuadMax/QuadPlus Qseven Development Platform Hardware User Guide

#### **Document Revision History**

| Document Number                                             |  | iW-PREJD-UM-01-R2.0-REL1.0-Hardware-i.MX8-DevKit |

|-------------------------------------------------------------|--|--------------------------------------------------|

| Revision Date                                               |  | Description                                      |

| 0.1 24 <sup>th</sup> Feb 2021 Draft version Release Version |  | Draft version Release Version                    |

PROPRIETARY NOTICE: This document contains proprietary material for the sole use of the intended recipient(s). Do not read this document if you are not the intended recipient. Any review, use, distribution or disclosure by others is strictly prohibited. If you are not the intended recipient (or authorized to receive for the recipient), you are hereby notified that any disclosure, copying distribution or use of any of the information contained within this document is STRICTLY PROHIBITED. Thank you. "iWave Systems Tech. Pvt. Ltd."

#### Disclaimer

iWave Systems reserves the right to change details in this publication including but not limited to any Product specification without notice.

No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by iWave Systems, its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

CPU and other major components used in this product may have several silicon errata associated with it. Under no circumstances, iWave Systems shall be liable for the silicon errata and associated issues.

#### **Trademarks**

All registered trademarks, product names mentioned in this publication are the property of their respective owners and used for identification purposes only.

#### Certification

iWave Systems Technologies Pvt. Ltd. is an ISO 9001:2015 Certified Company.

#### Warranty & RMA

Warranty support for Hardware: 1 Year from iWave or iWave's EMS partner.

For warranty terms, go through the below web link,

http://www.iwavesystems.com/support/warranty.html

For Return Merchandise Authorization (RMA), go through the below web link,

http://www.iwavesystems.com/support/rma.html

#### **Technical Support**

iWave Systems technical support team is committed to provide the best possible support for our customers so that our Hardware and Software can be easily migrated and used.

For assistance, contact our Technical Support team at,

Email : support.ip@iwavesystems.com

Website : <u>www.iwavesystems.com</u>

Address : iWave Systems Technologies Pvt. Ltd.

# 7/B, 29<sup>th</sup> Main, BTM Layout 2<sup>nd</sup> Stage,

Bengaluru, Karnataka,

India - 560076

## **Table of Contents**

| 1. II | NTRODUCTION                                           | 8  |

|-------|-------------------------------------------------------|----|

| 1.1   | Purpose                                               | 8  |

| 1.2   | Overview                                              | 8  |

| 1.3   | LIST OF ACRONYMS                                      | 8  |

| 1.4   | TERMINOLOGY DESCRIPTION                               | 10 |

| 1.5   | References                                            | 10 |

| 2. A  | ARCHITECTURE AND DESIGN                               | 11 |

| 2.1   | I.MX8 QM/QP QSEVEN DEVELOPMENT PLATFORM BLOCK DIAGRAM | 11 |

| 2.2   | I.MX8 QM/QP QSEVEN DEVELOPMENT PLATFORM FEATURES      | 12 |

| 2.3   | Qseven MXM Connector                                  | 14 |

| 2     | 2.3.1 Qseven PCB Edge Connector Pin Assignment        | 15 |

| 2.4   | Serial Interface Features                             | 34 |

| 2     | 2.4.1 Debug UART Interface                            | 34 |

| 2     | 2.4.2 Data UART Interface                             | 35 |

| 2.5   | HIGH SPEED INTERFACE FEATURES                         | 36 |

| 2     | 2.5.1 PCIe Interface                                  | 36 |

| 2     | 2.5.2 SATA Interface                                  | 42 |

| 2     | 2.5.3 USB3.0 Host Interface                           | 44 |

| 2.6   | COMMUNICATION INTERFACE FEATURES                      | 45 |

| 2     | 2.6.1 Gigabit Ethernet Interface                      | 45 |

| 2     | 2.6.2 USB2.0 Host Interface                           | 45 |

| 2     | 2.6.3 USB2.0 OTG Interface                            | 46 |

| 2     | 2.6.4 SDIO Interface                                  | 48 |

| 2     | 2.6.5 CAN Interface                                   | 49 |

| 2.7   | Audio/Video Features                                  | 51 |

| 2     | 2.7.1 HDMI Interface                                  | 51 |

| 2     | 2.7.2 I2S Audio Interface                             | 52 |

| 2     | 2.7.3 7" LCD with Capacitive Touch                    | 53 |

| 2     | 2.7.4 LVDS Port with Resistive Touch                  | 55 |

| 2.8   | Additional Features                                   | 57 |

| 2     | 2.8.1 SPI Flash                                       | 57 |

| 2     | 2.8.2 RTC Coin Cell Holder                            | 57 |

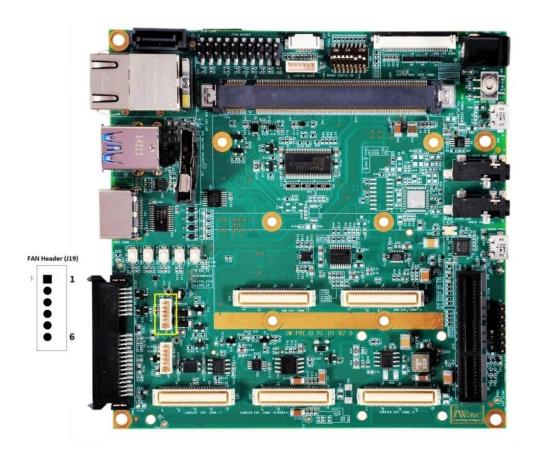

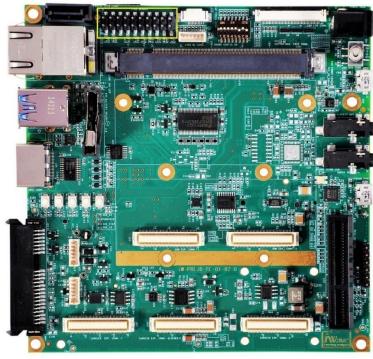

| 2     | 2.8.3 Fan Header                                      | 58 |

| 2     | 2.8.4 JTAG Header (Optional)                          | 59 |

| 2.9   | On Board Switches                                     | 60 |

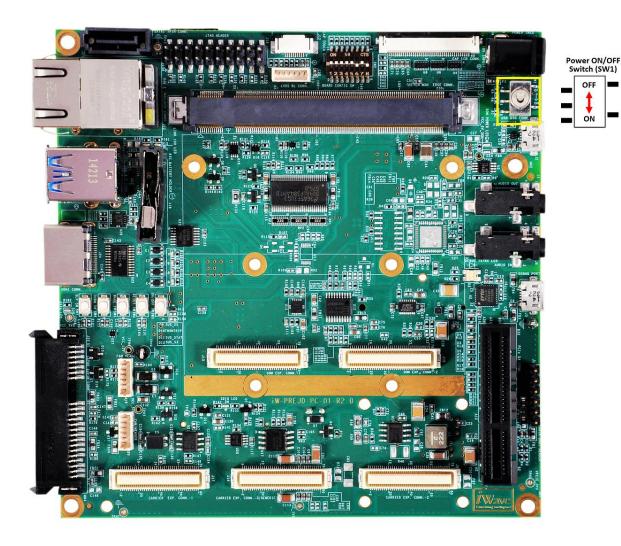

| 2     | 2.9.1 Power ON/OFF Switch                             | 60 |

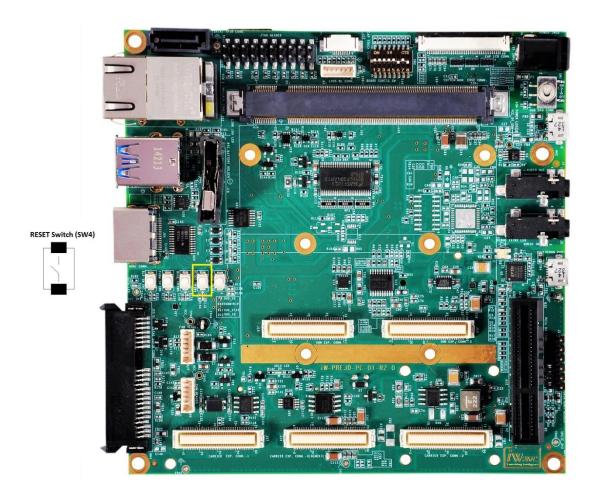

| 2     | 2.9.2 Reset Switch                                    | 61 |

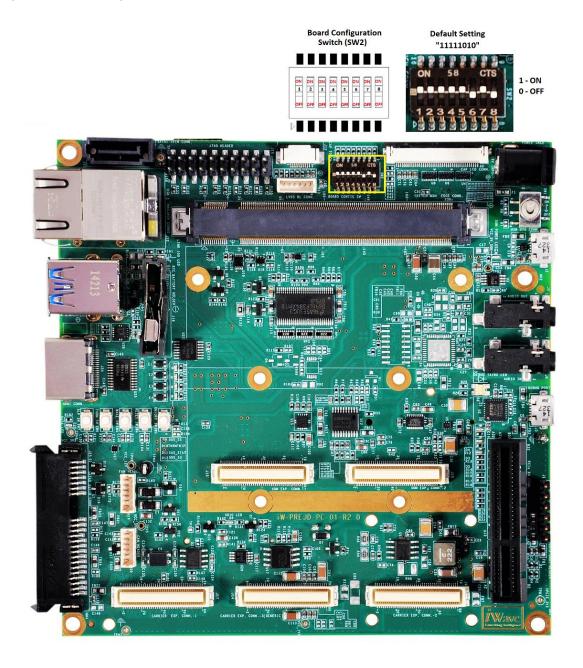

| 2     | 2.9.3 Board Configuration Switch                      | 62 |

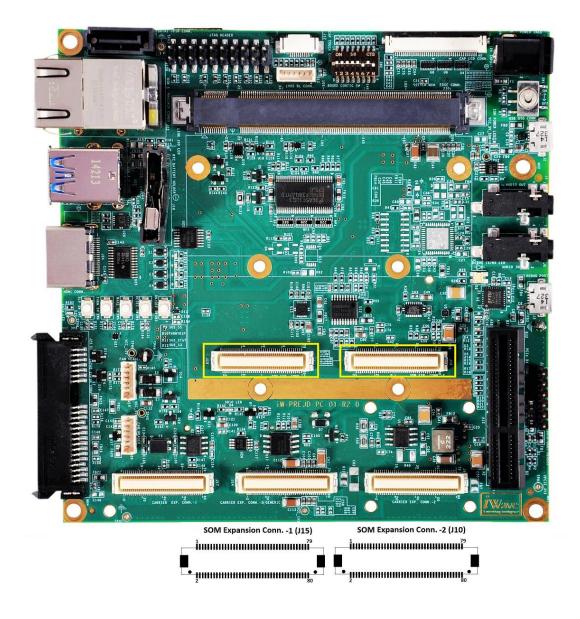

| 2.1   | SOM Expansion Connectors                              | 64 |

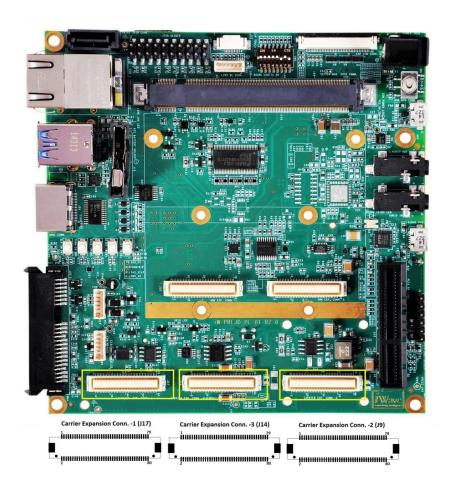

| 2.2   | CARRIER BOARD EXPANSION CONNECTORS                    | 65 |

|       |                                                       |    |

| 3. TEC | CHNICAL SPECIFICATION                                      | 72 |

|--------|------------------------------------------------------------|----|

| 2.4    | Device Iver Brown Brown                                    | 70 |

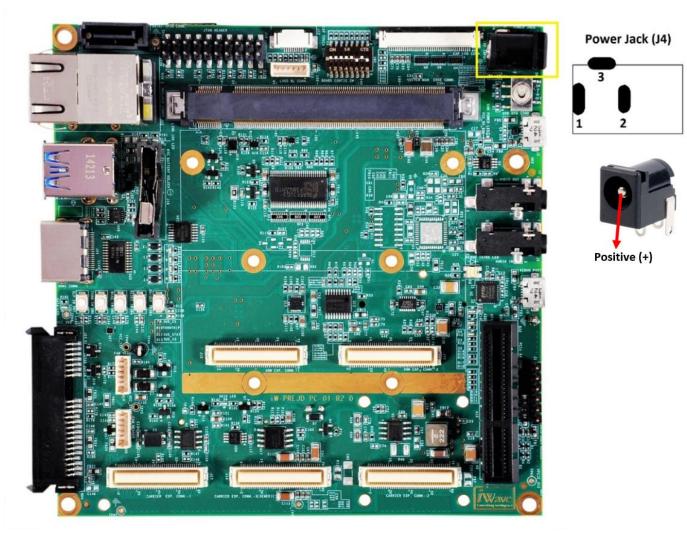

| 3.1    | Power Input Requirement                                    |    |

| 3.2    | POWER OUTPUT SPECIFICATION                                 | 73 |

| 3.3    | ENVIRONMENTAL CHARACTERISTICS                              | 74 |

| 3.3.   | .1 Environmental Specification                             | 74 |

| 3.3.   | .2 RoHS Compliance                                         | 74 |

| 3.3.   | .3 Electrostatic Discharge                                 | 74 |

| 3.4    | MECHANICAL CHARACTERISTICS                                 | 75 |

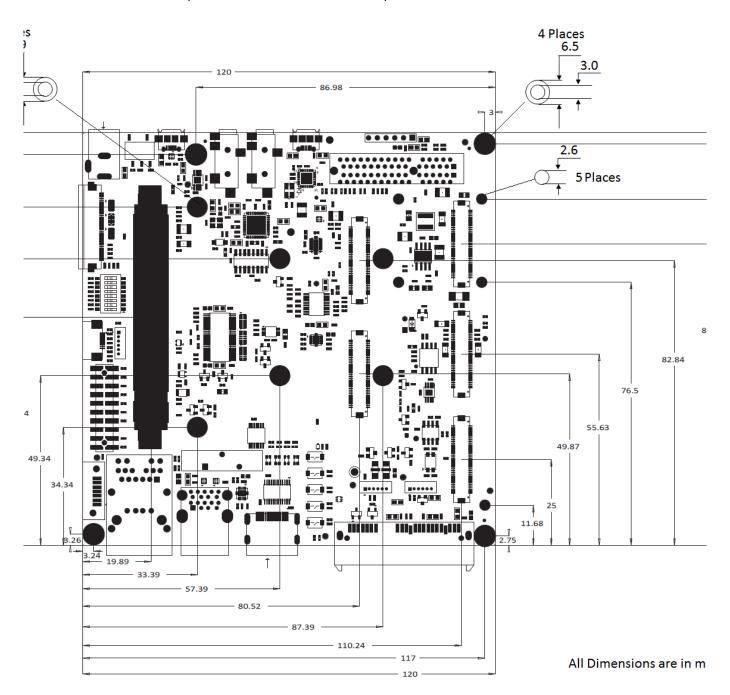

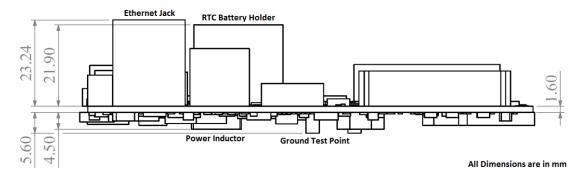

| 3.4.   | .1 i.MX 8 QM/QP Qseven Carrier Board Mechanical Dimensions | 75 |

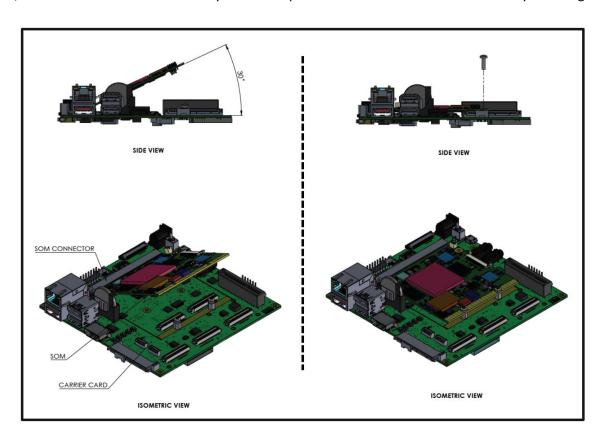

| 3.4.   | .2 Guidelines to insert the Qseven SOM into Carrier Board  | 76 |

| 4. ORI | DERING INFORMATION                                         | 77 |

## **List of Figures**

| FIGURE 1: I.MX8 QM/QP QSEVEN DEVELOPMENT PLATFORM BLOCK DIAGRAM                   | 11 |

|-----------------------------------------------------------------------------------|----|

| FIGURE 2: QSEVEN MXM CONNECTOR                                                    | 14 |

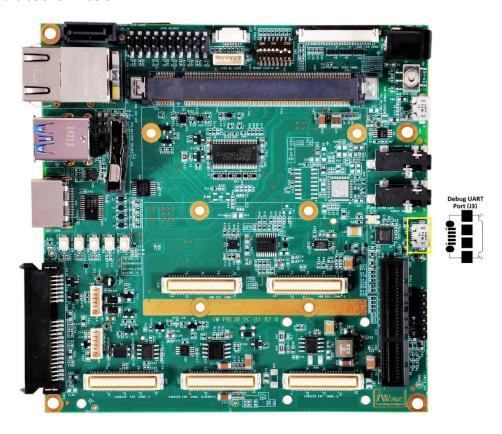

| FIGURE 3: DEBUG UART PORT                                                         | 34 |

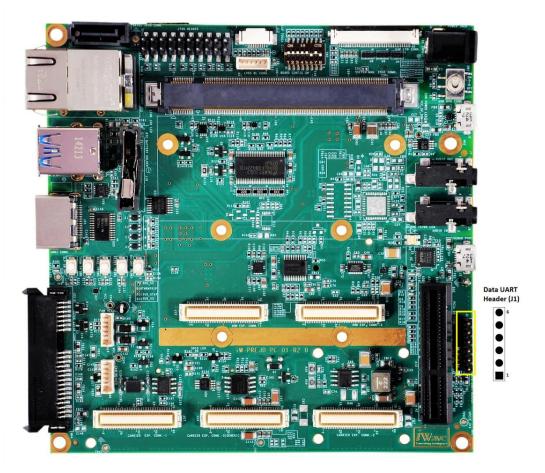

| FIGURE 4: DATA UART HEADER                                                        | 35 |

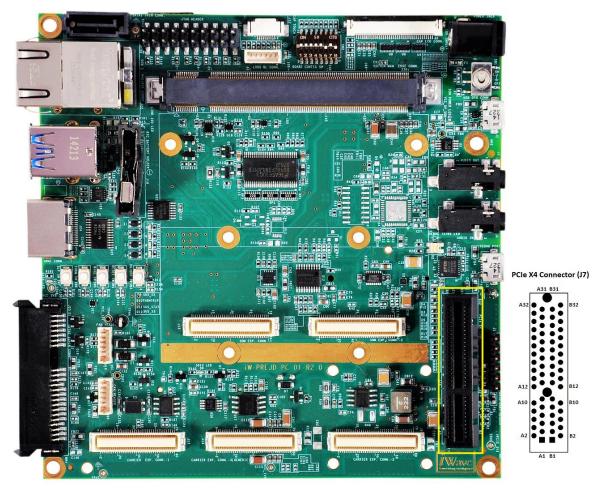

| FIGURE 5: PCIEX4 CONNECTOR                                                        | 36 |

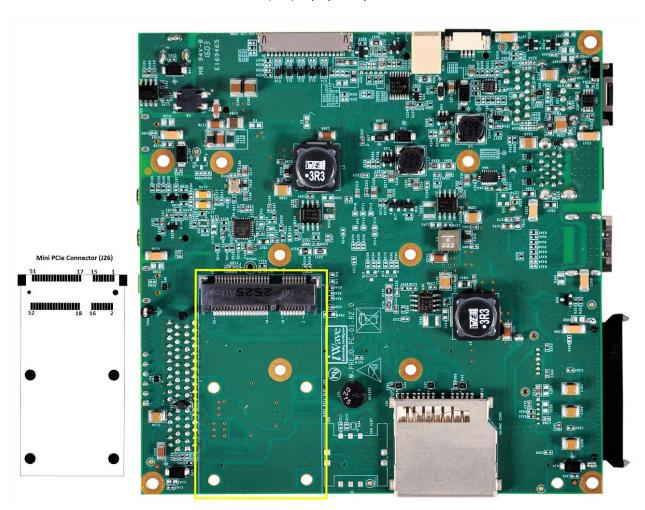

| FIGURE 6: MINI PCIE CONNECTOR                                                     | 39 |

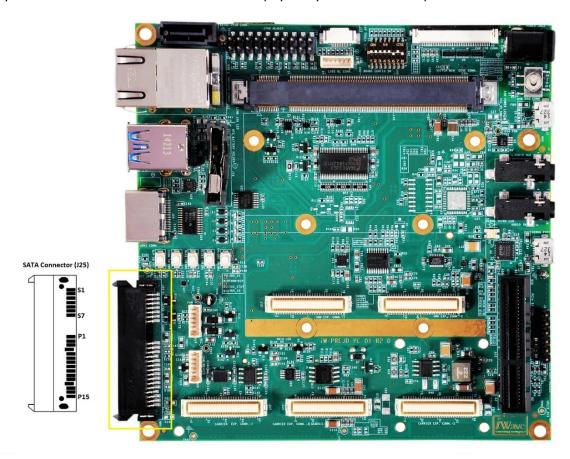

| FIGURE 7: SATA CONNECTOR                                                          | 42 |

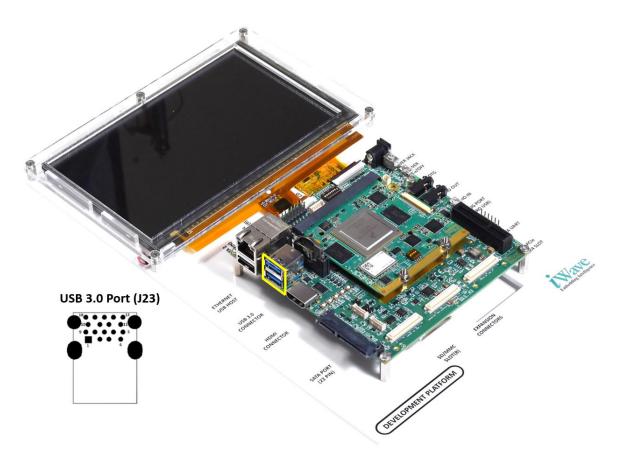

| FIGURE 8: USB3.0 HOST                                                             | 44 |

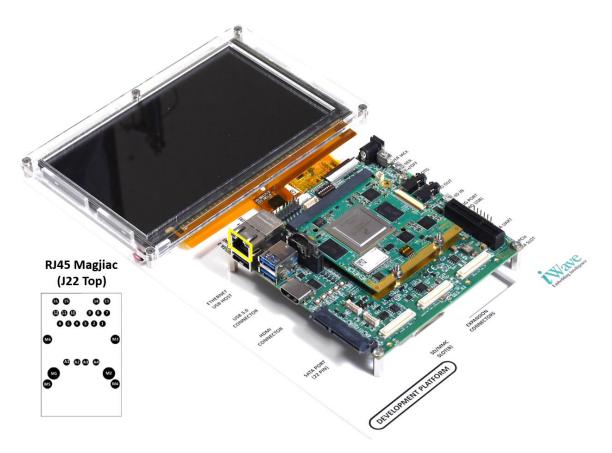

| FIGURE 9: RJ45 MAGJACK                                                            | 45 |

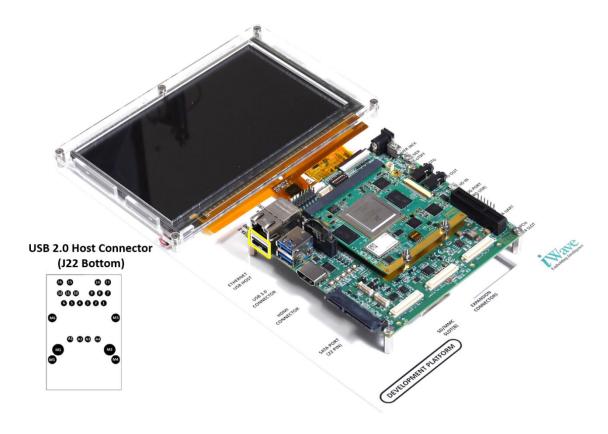

| FIGURE 10: USB2.0 HOST                                                            | 46 |

| FIGURE 11: USB2.0 OTG                                                             | 47 |

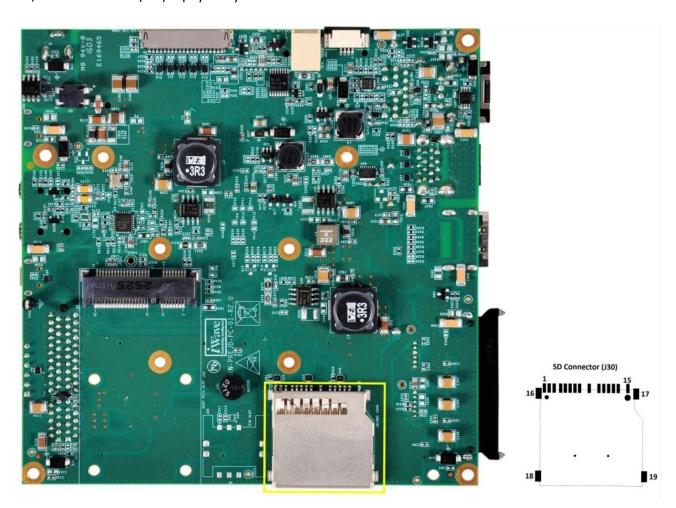

| FIGURE 12:STANDARD SD CONNECTOR                                                   | 48 |

| FIGURE 13: CAN HEADER                                                             | 49 |

| FIGURE 14: HDMI OUTPUT                                                            | 51 |

| FIGURE 15: AUDIO JACK                                                             | 52 |

| FIGURE 16: RGB LCD CONNECTOR                                                      | 53 |

| FIGURE 17: LVDS DISPLAY CONNECTOR                                                 | 55 |

| FIGURE 18: RTC BATTERY HOLDER                                                     | 57 |

| FIGURE 19: FAN HEADER                                                             | 58 |

| FIGURE 20: JTAG HEADER                                                            | 59 |

| FIGURE 21: POWER ON/OFF SWITCH                                                    | 60 |

| FIGURE 22: RESET SWITCH                                                           | 61 |

| FIGURE 23: BOARD CONFIGURATION SWITCH                                             | 62 |

| FIGURE 24: SOM EXPANSION CONNECTORS                                               | 64 |

| FIGURE 25: CARRIER BOARD EXPANSION CONNECTORS                                     | 65 |

| FIGURE 27: POWER JACK                                                             | 72 |

| FIGURE 28: MECHANICAL DIMENSIONS OF I.MX 8 QM/QP QSEVEN CARRIER BOARD- TOP VIEW   | 75 |

| FIGURE 29: MECHANICAL DIMENSIONS OF I.MX 8 QM/QP QSEVEN CARRIER BOARD - SIDE VIEW | 76 |

| FIGURE 30: SOM INSERTION GUIDELINE                                                | 76 |

## **List of Tables**

| Table 1: Acronyms & Abbreviations                 |    |

|---------------------------------------------------|----|

| TABLE 2: TERMINOLOGY                              | 10 |

| TABLE 3: QSEVEN PCB EDGE CONNECTOR PIN ASSIGNMENT | 15 |

| TABLE 4: DATA UART HEADER PINOUT                  | 35 |

| TABLE 5: PCIEX4 CONNECTOR PINOUT                  | 37 |

| TABLE 6: MINI-PCIE CONNECTOR PINOUT               | 39 |

| TABLE 7: 22 PINS SATA CONNECTOR PINOUT            | 42 |

| TABLE 8: CAN HEADER PINOUT                        | 49 |

| TABLE 9: 7" RGB LCD CONNECTOR PIN OUT             | 54 |

| TABLE 10: LVDS CONNECTOR PINOUT                   | 55 |

| Table 11: Fan Header Pin Out                      | 58 |

| TABLE 12: BOARD CONFIGURATION SWITCH              | 63 |

| TABLE 13: EXPANSION CONNECTOR3 PIN OUT            | 66 |

| TABLE 14: POWER INPUT REQUIREMENT                 | 73 |

| TABLE 15: POWER OUTPUT SPECIFICATION              | 73 |

| TABLE 16: ENVIRONMENTAL SPECIFICATION             | 74 |

| TARLE 17: OPDERARIE PRODUCT PART NUMBERS          | 77 |

#### 1. INTRODUCTION

#### 1.1 Purpose

This document is the Hardware User Guide for the i.MX8 QM/QP Qseven V2.1 Development platform "iW-RainboW-G27D" based on the NXP's i.MX8 Application processor. This board is fully supported by iWave Systems Technologies Pvt. Ltd. This Guide provides detailed information on the overall design and usage of the i.MX8 QM/QP based Qseven development platform from a Hardware Systems perspective. Complete information about the i.MX8 QM/QP Qseven SOM is explained in another document "iW-RainboW-G27M\_i.MX8QM\_QP\_Qseven\_SOM-HardwareUserGuide".

#### 1.2 Overview

The Qseven V2.1 concept is an off-the-shelf, multi-vendor, Computer-On-Module that integrates all the core components of a common PC and is mounted onto an application specific carrier board.

iW-RainboW-G27D Development Platform comes with Qseven V2.1 Generic Carrier, i.MX8 QM/QP based Qseven V2.1 SOM along with 7-inch Capacitive Touch Display. The development board can be used for quick prototyping of various applications targeted by the i.MX8 processor. With the 120mmx120mm Nano ITX size, Qseven carrier board is highly packed with all the necessary on-board connectors to validate the Qseven features of i.MX8 QM/QP Qseven SOM.

#### 1.3 List of Acronyms

The following acronyms will be used throughout this document.

Table 1: Acronyms & Abbreviations

| Acronyms | Abbreviations                           |  |  |  |

|----------|-----------------------------------------|--|--|--|

| CAN      | Controller Area Network                 |  |  |  |

| CMOS     | Complementary Metal-Oxide Semiconductor |  |  |  |

| CPU      | Central Processing Unit                 |  |  |  |

| CSI      | Camera Serial Interface                 |  |  |  |

| DP       | Display Port                            |  |  |  |

| DSI      | Display Serial Interface                |  |  |  |

| еММС     | Enhanced Multi Media Card               |  |  |  |

| GB       | Giga Byte                               |  |  |  |

| Gbps     | Gigabits per sec                        |  |  |  |

| GPIO     | General Purpose Input Output            |  |  |  |

| HDMI     | High-Definition Multimedia Interface    |  |  |  |

| Hz       | Hertz                                   |  |  |  |

| I2C      | Inter-Integrated Circuit                |  |  |  |

| I2S      | Inter-IC Sound                          |  |  |  |

| IC       | Integrated Circuit                      |  |  |  |

| LVDS     | Low Voltage Differential Signalling     |  |  |  |

| Acronyms | Abbreviations                               |  |  |  |

|----------|---------------------------------------------|--|--|--|

| MIPI     | Mobile Industry Processor Interface         |  |  |  |

| MLB      | Media Local Bus                             |  |  |  |

| MXM      | Mobile PCI Express Module                   |  |  |  |

| PCB      | Printed Circuit Board                       |  |  |  |

| PCle     | Peripheral Component Interconnect Express   |  |  |  |

| RoHS     | Restriction of Hazardous Substances         |  |  |  |

| RTC      | Real Time Clock                             |  |  |  |

| SATA     | Serial Advanced Technology Attachment       |  |  |  |

| SD       | Secure Digital                              |  |  |  |

| SOM      | System On Module                            |  |  |  |

| TBD      | To Be Defined                               |  |  |  |

| UART     | Universal Asynchronous Receiver/Transmitter |  |  |  |

| USB      | Universal Serial Bus                        |  |  |  |

| USB OTG  | USB On The Go                               |  |  |  |

| V        | Voltage                                     |  |  |  |

#### 1.4 Terminology Description

In this document, wherever Signal Type is mentioned, below terminology is used.

**Table 2: Terminology**

| Terminology | Description                                                          |  |  |  |

|-------------|----------------------------------------------------------------------|--|--|--|

| 1           | Input Signal                                                         |  |  |  |

| 0           | Output Signal                                                        |  |  |  |

| 10          | Bidirectional Input/output Signal                                    |  |  |  |

| CMOS        | Complementary Metal Oxide Semiconductor Signal                       |  |  |  |

| DIFF        | Differential Signal                                                  |  |  |  |

| LVDS        | Low Voltage Differential Signal                                      |  |  |  |

| GBE         | Gigabit Ethernet Media Dependent Interface differential pair signals |  |  |  |

| USB HS      | Universal Serial Bus High Speed differential pair signals            |  |  |  |

| USB SS      | Universal Serial Bus Super Speed differential pair signals           |  |  |  |

| MIPI        | Mobile Industry Processor Interface signals                          |  |  |  |

| HDMI        | High-Definition Multimedia Interface Differential Signal             |  |  |  |

| DP          | Display Port Differential Signal                                     |  |  |  |

| OD          | Open Drain Signal                                                    |  |  |  |

| OC          | Open Collector Signal                                                |  |  |  |

| Power       | Power Pin                                                            |  |  |  |

| PU          | Pull Up                                                              |  |  |  |

| PD          | Pull Down                                                            |  |  |  |

| NA          | Not Applicable                                                       |  |  |  |

| NC          | Not Connected                                                        |  |  |  |

Note: Signal Type does not include internal pull-ups or pull-downs implemented by the chip vendors and only includes the pull-ups or pull-downs implemented On- Qseven SOM.

#### 1.5 References

- IMX8QMAEC\_Revx.pdf

- iMX8QM\_RM\_Rev\_x.pdf

- Qseven® Specification Version 2.1

- Qseven® Design Guide 2.0

#### 2. ARCHITECTURE AND DESIGN

This section provides detailed information about the i.MX8 QM/QP Qseven SOM features and Hardware architecture with high level block diagram.

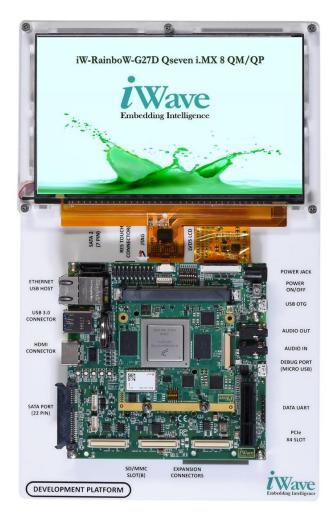

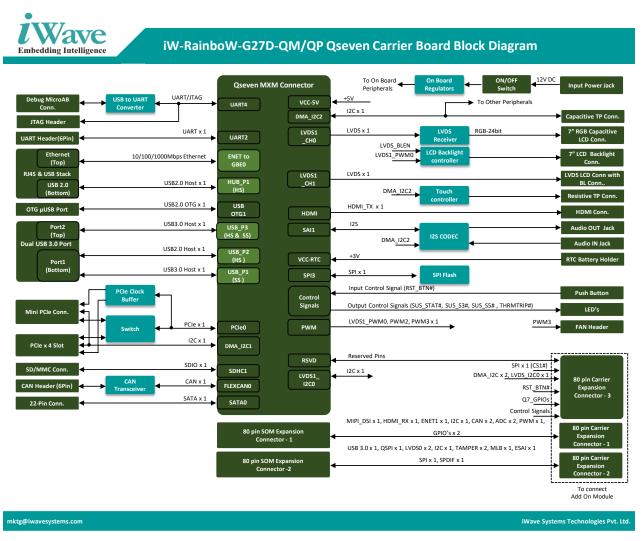

#### 2.1 i.MX8 QM/QP Qseven Development Platform Block Diagram

Figure 1: i.MX8 QM/QP Qseven Development Platform Block Diagram

#### 2.2 i.MX8 QM/QP Qseven Development Platform Features

The NXP's i.MX8 QM/QP Qseven carrier board supports the following features to validate the NXP's i.MX8 QM/QP Qseven SOM Edge connector interface.

#### **Serial Interface Features**

- Debug UART through USB Micro AB Connector

- Data UART x 1 Port through Header

#### **High Speed Interface Features**

- PCle x 1 Port through x4 connector or Mini-PCle connector<sup>1</sup>

- SATA x 1 Port through 22pin SATA Connector

- USB 3.0 Host x 2 Port through USB 3.0 Type A Connector<sup>2</sup>

#### **Communication Features**

- 10/100/1000Mbps Ethernet through RJ45MagJack

- USB 2.0 Host x 1 Port through Type A Connector (Dual stack USB 3.0 Top)

- USB 2.0 Host x 1 Port through Type A Connector

- USB 2.0 OTG x 1 Port through Micro AB Connector

- SDHC/SDIO (4bit) x 1 Port through Standard SD Connector

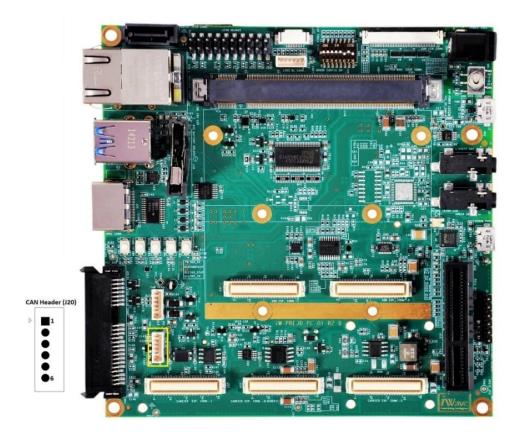

- CAN x 1 Port Through Header

#### **Audio/Video Features**

- I2S Audio Codec with 3.5mm Audio IN and OUT jack

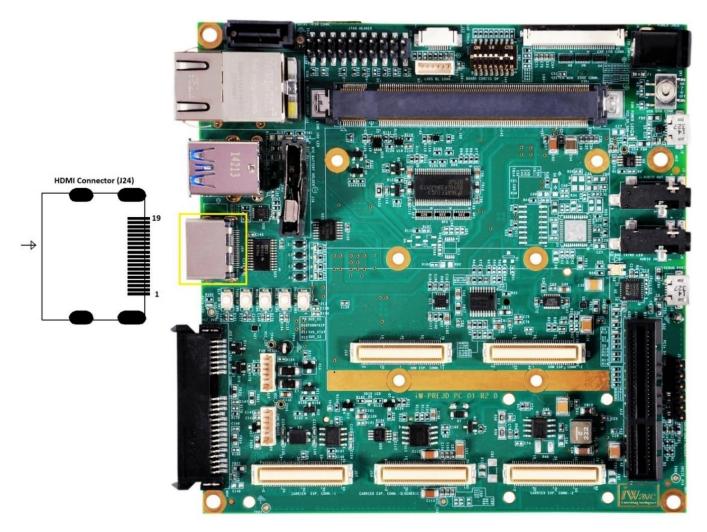

- HDMI X 1 Port through Type A Connector

- 7" RGB Display Connector through LVDS to RGB Transmitter with Capacitive Touch

- 2<sup>nd</sup> LVDS Port display Connector

#### **Additional Features**

- SPI Flash

- RTC Coin Cell holder

- Buzzer

- Fan Header

- 20 Pin JTAG Header

#### **On Board Switches**

- Power ON/OFF Switch

- Board Configuration Switch

- Reset Switch

#### **Carrier board Expansion Connectors**

- SPI x 2 Port (1 is Optional Shared with SPI Flash)

- QSPI/SPI x 1 Port

- HDMI Receiver x 1Port

- LVDS x 2 Channel

- MIPI DSI x 2 Channel

- ENET1 x 1

- CAN x 2 Port

- ADC x 2

- USB3.0 Host x 1 Ports (through On-SOM USB Hub)

- ESAI x 1 Port

- SPDIF x 1 Port

- MLB x 1 Port

- I2C x 3 Port

- TAMPER In & Out

- GPIOs & Power

#### **General Specification**

Power Supply : 12V, 2A Power Input Jack

Temperature Supported : 0°C to +60°C

• Form Factor : 120mm X 120mm Nano ITX

<sup>&</sup>lt;sup>1.</sup>PCIe Channel 0 can be connected to either Mini PCIe or PETp0 of PCIe X4 connector by using on Board Switches, whereas PCIe Channel 1 is directly connected to PETp1 of PCIe X4 connector.

<sup>&</sup>lt;sup>2</sup> Either USB 2.0 in Mini PCIe connector or USB 3.0 Type A TOP connector can be supported at a time. Anyone can be selected using on Board Switches.

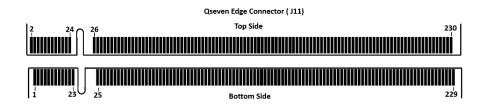

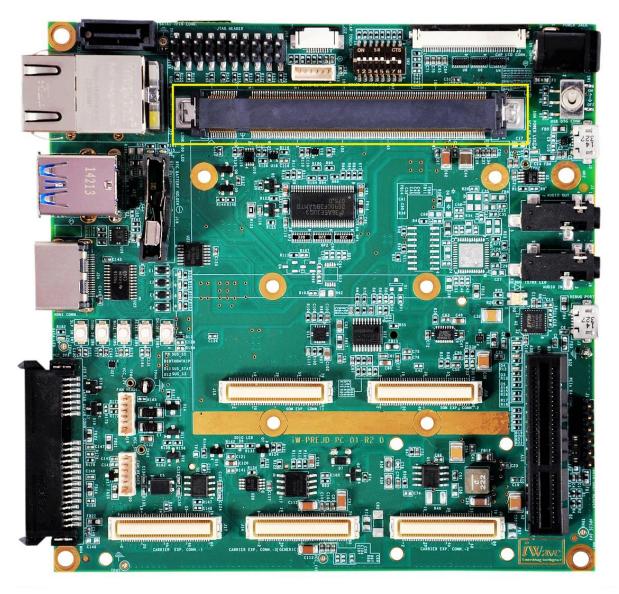

#### 2.3 Qseven MXM Connector

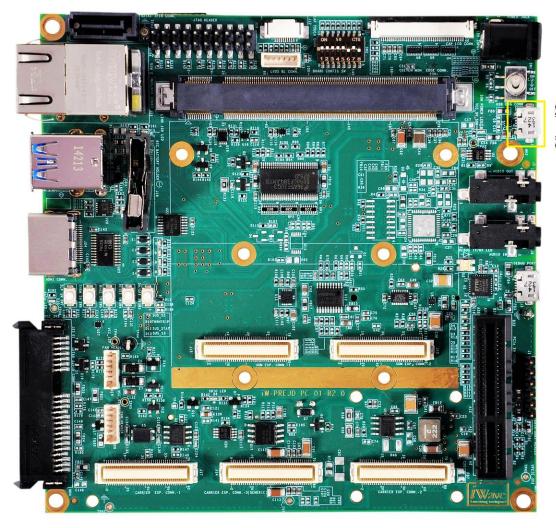

The i.MX8 QM/QP Qseven carrier board supports 230Pin Qseven MXM Edge mating connector for Qseven SOM attachment. This standard 230-pin robust connector is capable of handling high-speed serialized signals and can be used for size constrained embedded applications. This Qseven MXM connector (J11) is physically located at the top of the board as shown below.

Figure 2: Qseven MXM Connector

## 2.3.1 Qseven PCB Edge Connector Pin Assignment

Table 3: Qseven PCB Edge Connector Pin Assignment

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name         | CPU Ball Name/<br>Pin Number | Signal Type/<br>Termination | Description                                                                                                                                     |

|------------|-------------------------------------|---------------------|------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | GND                                 | GND                 | NA                           | Power                       | Ground.                                                                                                                                         |

| 2          | GND                                 | GND                 | NA                           | Power                       | Ground.                                                                                                                                         |

| 3          | GBE_MDI3-                           | GBE0_MDI3-          | NA                           | IO, DIFF                    | Gigabit Ethernet MDI differential pair 3 negative.                                                                                              |

| 4          | GBE_MDI2-                           | GBE0_MDI2-          | NA                           | IO, DIFF                    | Gigabit Ethernet MDI differential pair 2 negative.                                                                                              |

| 5          | GBE_MDI3+                           | GBE0_MDI3+          | NA                           | IO, DIFF                    | Gigabit Ethernet MDI differential pair 3 positive.                                                                                              |

| 6          | GBE_MDI2+                           | GBE0_MDI2+          | NA                           | IO, DIFF                    | Gigabit Ethernet MDI differential pair 2 positive.                                                                                              |

| 7          | GBE_LINK100#                        | GBE0_LINK100#       | NA                           | I, 3.3V CMOS                | 100Mbps Ethernet link status LED.  Note: This pin is connected to D15  Green LED.                                                               |

| 8          | GBE_LINK1000#                       | GBE0_LINK1000<br>#  | NA                           | I, 3.3V CMOS                | Gigabit Ethernet link status LED.  Note: This pin is connected to D16  Green LED.                                                               |

| 9          | GBE_MDI1-                           | GBE0_MDI1-          | NA                           | IO, DIFF                    | Gigabit Ethernet MDI differential pair 1 negative.                                                                                              |

| 10         | GBE_MDI0-                           | GBE0_MDI0-          | NA                           | IO, DIFF                    | Gigabit Ethernet MDI differential pair 0 negative.                                                                                              |

| 11         | GBE_MDI1+                           | GBE0_MDI1+          | NA                           | IO, DIFF                    | Gigabit Ethernet MDI differential pair 1 positive.                                                                                              |

| 12         | GBE_MDI0+                           | GBE0_MDI0+          | NA                           | IO, DIFF                    | Gigabit Ethernet MDI differential pair 0 positive.                                                                                              |

| 13         | GBE_LINK#                           | GPHY_LINK_LED       | NA                           | I, 3.3V CMOS                | Gigabit Ethernet link status LED.                                                                                                               |

| 14         | GBE_ACT#                            | GBEO_LINK_ACT<br>#  | NA                           | I, 3.3V CMOS                | Gigabit Ethernet Activity status LED.                                                                                                           |

| 15         | GBE_CTREF                           | VPHY0_DVDDL         | NA                           | Power                       | Power for the Centre Tap of Mack Jack connector                                                                                                 |

| 16         | SUS_S5#                             | SUS_S5_Q7           | NA                           | I, 3.3V CMOS                | S5 State. This pin is connected to indication LED D9. Note: This pin is optionally connected to Expansion Connector3 (J14) 8 <sup>th</sup> Pin. |

| 17         | WAKE#                               | WAKE#(GPIO3_<br>04) | SPIO_SDI/<br>BA5             | O, 3.3V CMOS                | This pin is connected to Push button (SW5) in carrier board.                                                                                    |

|            | Qseven MXM            |                           |                              |                             |                                                                                                                                                                                                  |

|------------|-----------------------|---------------------------|------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No. | Connector Pin<br>Name | Signal Name               | CPU Ball Name/<br>Pin Number | Signal Type/<br>Termination | Description                                                                                                                                                                                      |

|            |                       |                           |                              |                             | Note: This pin is optionally connected to Expansion Connector3 (J14) 16 <sup>th</sup> Pin.                                                                                                       |

| 18         | SUS_S3#               | SUS_S3_Q7                 | NA                           | I, 3.3V CMOS                | S3 state. This pin is connected to indication LED D12. Note: This pin is optionally connected to Expansion Connector3 (J14) 7 <sup>th</sup> Pin.                                                 |

| 19         | SUS_STAT#             | SUS_STAT_Q7(G<br>PIO2_05) | ESAI1_FST/<br>BF12           | I, 3.3V CMOS                | Suspend Status. This pin is connected to indication LED D10. Note: This pin is optionally connected to Expansion Connector3 (J14) 10 <sup>th</sup> Pin.                                          |

| 20         | PWRBTN#               | PWRBTN#                   | ON_OFF_BUTTO<br>N/<br>BE47   | O, 3.3V CMOS                | Power Button output. This pin is connected to Push button (SW3) in the carrier board used for SOM On/Off control. Note: This pin is optionally connected to Expansion Connector3 (J14) 24th Pin. |

| 21         | SLP_BTN#              | GPII_1(GPIO0_0<br>4)      | LSIO.GPIOO.IOO<br>4/<br>AT48 | O, 3.3V CMOS                | This pin is connected to Push button (SW7) in carrier board.  Note: This pin is optionally connected to Expansion Connector3 (J14) 22nd Pin.                                                     |

| 22         | LID_BTN#              | GPII_0(GPIO3_0<br>3)      | SPIO_SDO/<br>AY6             | I, 3.3V CMOS                | This pin is connected from 8bit DIP switch (SW2) 3 <sup>rd</sup> position in carrier board.  Note: This pin is optionally connected to Expansion Connector3 (J14) 28th Pin.                      |

| 23         | GND                   | GND                       | NA                           | Power                       | Ground.                                                                                                                                                                                          |

| 24         | GND                   | GND                       | NA                           | Power                       | Ground.                                                                                                                                                                                          |

|            |                       |                           | Key                          |                             |                                                                                                                                                                                                  |

| 25         | GND                   | GND                       | NA                           | Power                       | Ground.                                                                                                                                                                                          |

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name                  | CPU Ball Name/<br>Pin Number | Signal Type/<br>Termination | Description                                                                                                                                                                                                |

|------------|-------------------------------------|------------------------------|------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26         | PWGIN                               | PWGIN                        | NA                           | O, 5V CMOS/<br>10K PU       | Power Good Output.                                                                                                                                                                                         |

| 27         | BATLOW#                             | GPII_2(GPIO0_0<br>5)         | LSIO.GPIO0.IO0<br>5/ AP46    | I, 3.3V CMOS                | This pin is connected from 8bit DIP switch (SW2) 2 <sup>nd</sup> position in carrier board.  Note: This pin is optionally connected to Expansion Connector3 (J14) 30th Pin.                                |

| 28         | RSTBTN#                             | RSTBN                        | NA                           | O, 3.3V CMOS                | Active low Reset button Output. This pin is connected to Push button SW4 in carrier board for reset generation. Note: This pin is optionally connected to Expansion Connector3 (J14) 12 <sup>th</sup> Pin. |

| 29         | SATAO_TX+                           | PCIE_SATAO_TX<br>O_P         | PCIE_SATA0_<br>TX0_P/ B16    | I, SATA                     | This pin is connected to 22pin SATA Connector (J25) for SATA Channel0 Transmit differential pair positive.                                                                                                 |

| 30         | SATA1_TX+                           | NC                           | NA                           | NA                          | NC in i.MX8 Qseven SOM.  This pin connected to 7pin SATA  Connector (J21) in carrier board.                                                                                                                |

| 31         | SATAO_TX-                           | PCIE_SATAO_TX<br>O_N         | PCIE_SATA0_<br>TX0_N/ C17    | I, SATA                     | This pin connected to 22pin SATA Connector (J25) for SATA Channel0 Transmit differential pair negative.                                                                                                    |

| 32         | SATA1_TX-                           | NC                           | NA                           | NA                          | NC in i.MX8 Qseven SOM.  This pin connected to 7pin SATA  Connector (J21) in carrier board.                                                                                                                |

| 33         | SATA_ACT#                           | GPIO_SATA_AC<br>T#(GPIO1_18) | MIPI_DSI0_<br>GPIO0_00/BD30  | I, 3.3V CMOS                | This pin connected from 22pin SATA<br>Connector (J25) for SATA Channel0<br>command Activity line.                                                                                                          |

| 34         | GND                                 | GND                          | NA                           | Power                       | Ground.                                                                                                                                                                                                    |

| 35         | SATAO_RX+                           | PCIE_SATAO_RX<br>O_P         | PCIE_SATAO_<br>RXO_P/ A19    | I, SATA                     | This pin connected to 22pin SATA Connector (J25) for SATA Channel0 Receive differential pair positive.                                                                                                     |

| 36         | SATA1_RX+                           | NC                           | NA                           | -                           | NC in i.MX8 Qseven SOM.  This pin connected to 7pin SATA  Connector (J21) in carrier board.                                                                                                                |

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name                        | CPU Ball Name/<br>Pin Number | Signal Type/<br>Termination | Description                                                                                                                                                                                        |

|------------|-------------------------------------|------------------------------------|------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37         | SATAO_RX-                           | PCIE_SATAO_RX<br>O_N               | PCIE_SATAO_<br>RXO_N/ B20    | I, SATA                     | NC in i.MX8 Qseven SOM.  This pin connected to 22pin SATA Connector (J25) for SATA Channel0 Receive differential pair negative.                                                                    |

| 38         | SATA1_RX-                           | NC                                 | NA                           | NA                          | NC in i.MX8 Qseven SOM.  This pin connected to 7pin SATA  Connector (J21) in carrier board.                                                                                                        |

| 39         | GND                                 | GND                                |                              | Power                       | Ground.                                                                                                                                                                                            |

| 40         | GND                                 | GND                                |                              | Power                       | Ground.                                                                                                                                                                                            |

| 41         | BIOS_DISABLE#/<br>BOOT_ALT#         | NC                                 | NA                           | NA                          | NC in i.MX8 Qseven SOM. This pin is connected from 8bit DIP switch (SW2) 1 <sup>st</sup> position in carrier board. Note: This pin is optionally connected to Expansion Connector3 (J14) 32nd Pin. |

| 42         | SDIO_CLK#                           | uSDHC1_CLK                         | USDHC1_CLK<br>/J39           | I, 3.3V CMOS                | uSDHC1 Clock. This pin is connected to SD/MMC connector (J30).                                                                                                                                     |

| 43         | SDIO_CD#                            | GPIO_SDC1_CD(<br>GPIO1_23)         | MIPI_DSI1_GPI<br>O0_01/BK24  | O, 3.3V CMOS                | uSDHC1 Card Detect. This pin is connected from SD/MMC connector (J30).                                                                                                                             |

| 44         | SDIO_LED                            | GPIO_SD1_LED(<br>GPIO3_06)         | SPIO_CS1/<br>BA3             | I, 3.3V CMOS                | SDIO LED. This pin is connected to D8 Green LED.                                                                                                                                                   |

| 45         | SDIO_CMD                            | uSDHC1_CMD                         | USDHC1_CMD<br>/G41           | IO,3.3VCMOS                 | uSDHC1 command. This pin is connected to SD/MMC connector (J30).                                                                                                                                   |

| 46         | SDIO_WP                             | GPIO_SDC1_WP<br>(GPIO1_22)         | MIPI_DSI1_GPI<br>O0_00/BM24  | O, 3.3V CMOS                | uSDHC1 Write Protect. This pin is connected to SD/MMC connector (J30).                                                                                                                             |

| 47         | SDIO_PWR#                           | GPIO_SDC1_PW<br>R_EN(GPIO1_19<br>) | MIPI_DSIO_GPI<br>O0_01/BD28  | I, 3.3V CMOS/<br>10K PD     | SD/MMC Interface Power Enable. This pin is used control the power input to the SD/MMC connector.                                                                                                   |

| 48         | SDIO_DAT1                           | uSDHC1_DATA1                       | USDHC1_DATA1<br>/F38         | IO, 3.3V CMOS               | uSDHC1 Data1. This pin is connected to SD/MMC connector (J30).                                                                                                                                     |

| 49         | SDIO_DAT0                           | uSDHC1_DATA0                       | USDHC1_DATA0<br>/E37         | IO, 3.3V CMOS               | uSDHC1 Data0.                                                                                                                                                                                      |

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name              | CPU Ball Name/<br>Pin Number | Signal Type/<br>Termination | Description                                                                                                                                        |

|------------|-------------------------------------|--------------------------|------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                     |                          |                              |                             | This pin is connected to SD/MMC connector (J30).                                                                                                   |

| 50         | SDIO_DAT3                           | uSDHC1_DATA3             | USDHC1_DATA3<br>/F40         | IO, 3.3V CMOS               | uSDHC1 Data3. This pin is connected to SD/MMC connector (J30).                                                                                     |

| 51         | SDIO_DAT2                           | uSDHC1_DATA2             | USDHC1_DATA2<br>/E39         | IO, 3.3V CMOS               | uSDHC1 Data2. This pin is connected to SD/MMC connector (J30).                                                                                     |

| 52         | SDIO_DAT5                           | NC                       | NA                           | NA                          | NC in i.MX8 Qseven SOM.  This pin is connected to SD/MMC connector (J30) in carrier board.                                                         |

| 53         | SDIO_DAT4                           | NC                       | NA                           | NA                          | NC in i.MX8 Qseven SOM.  This pin is connected to SD/MMC connector (J30) in carrier board.                                                         |

| 54         | SDIO_DAT7                           | NC                       | NA                           | NA                          | NC in i.MX8 Qseven SOM.  This pin is connected to SD/MMC connector (J30) in carrier board.                                                         |

| 55         | SDIO_DAT6                           | NC                       | NA                           | NA                          | NC in i.MX8 Qseven SOM.  This pin is connected to SD/MMC connector (J30) in carrier board.                                                         |

| 56         | USB_DRIVE_VB                        | USB_OTG1_PW              | USB_SS3_TC0/                 | I, 3.3V CMOS                | USB OTG Power enable.                                                                                                                              |

|            | US                                  | R(GPIO4_03)              | J9                           |                             |                                                                                                                                                    |

| 57         | GND                                 | GND                      | NA                           | Power                       | Ground.                                                                                                                                            |

| 58         | GND                                 | GND                      | NA                           | Power                       | Ground.                                                                                                                                            |

| 59         | HDA_SYNC/<br>I2S_WS                 | SAI1_TXFS                | SAI1_TXFS/<br>AV2            | I, 3.3V CMOS                | SSI Audio transmit frame synchronization. This pin is connected to I2S audio codec.                                                                |

| 60         | SMB_CLK/<br>GP1_I2C_CLK             | DMA_I2C1_SCL             | DMA.I2C1.SCL/<br>AY52        | I, 3.3V OD                  | I2CO clock. This pin is connected to PCIe Clock buffer, PCIex4 connector, Mini PCIe connector and Expansion Connector3 (J14) 77 <sup>th</sup> Pin. |

| 61         | HDA_RST#/<br>I2S_RST#               | GPIO_RESET(GPI<br>O1_05) | LVDS0_GPIO01/<br>BD40        | I, 3.3V CMOS/<br>10K PU     | Audio Codec Reset. This pin is connected to Capacitive Touch Connector for touch reset & Expansion connector3 (J14) 42 <sup>nd</sup> Pin.          |

| 62         | SMB_DAT/<br>GP1_I2C_DAT             | DMA_I2C1_SDA             | DMA.I2C1.SDA/<br>AV52        | IO, 3.3V OD                 | I2C0 Data. This pin is connected to PCIe Clock buffer, PCIex4 connector, Mini PCIe                                                                 |

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name                        | CPU Ball Name/<br>Pin Number | Signal Type/<br>Termination | Description                                                                                                                                                       |

|------------|-------------------------------------|------------------------------------|------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                     |                                    |                              |                             | connector and Expansion<br>Connector3 (J14) 79 <sup>th</sup> Pin.                                                                                                 |

| 63         | HDA_BCLK/<br>I2S_CLK                | SAI1_TXC                           | SAI1_TXC /<br>AU5            | O, 3.3V CMOS                | SSI Audio transmit clock. This pin is connected from I2S audio codec.                                                                                             |

| 64         | SMB_ALERT#                          | SMBUS_ALERT(<br>GPIO1_15)          | LVDS1_I2C1_SD<br>A/BN35      | O, 3.3V CMOS                | NC in i.MX8 Qseven SOM.  This pin is connected to Expansion connector3 (J14) 11 <sup>th</sup> Pin in carrier board.                                               |

| 65         | HDA_SDI/<br>I2S_SDI                 | SAI1_RXD                           | SAI1_RXD/<br>AV4             | O, 3.3V CMOS                | SSI Audio Transmit Data. This pin is connected from I2S audio codec.                                                                                              |

| 66         | GP0_I2C_CLK                         | DMA_I2C2_SCL                       | DMA.I2C2.SCL<br>/BA53        | I, 3.3V OD                  | I2C2 clock. This pin is connected to I2S Audio Codec, Capacitive touch connector, Resistive touch connector, and Expansion Connector3 (J14) 78 <sup>th</sup> Pin. |

| 67         | HDA_SDO/<br>I2S_SDO                 | SAI1_TXD                           | SAI1_TXD /<br>AU1            | I, 3.3V CMOS                | SSI Audio Receive Data. This pin is connected to I2S audio codec.                                                                                                 |

| 68         | GP0_I2C_DAT                         | DMA_I2C2_SDA                       | DMA.I2C2.SDA /<br>AY50       | IO, 3.3V OD                 | I2C2 Data. This pin is connected to I2S Audio Codec, Capacitive touch connector, Resistive touch connector, and Expansion Connector3 (J14) 80 <sup>th</sup> Pin.  |

| 69         | THRM#                               | THRM#                              | NA                           | I, 3.3V CMOS                | This pin is connected from Push button (SW6) in carrier board.  Note: This pin is optionally connected to Expansion Connector3  (J14) 20 <sup>th</sup> Pin.       |

| 70         | WDTRIG#                             | Q7_WDTRIG_B                        | NA                           | I, 3.3V CMOS                | This pin is connected to Expansion connector3 (J14) 17 <sup>th</sup> Pin in carrier board.                                                                        |

| 71         | THRMTRIP#                           | GPIO_THRMTRI<br>P_Q7(GPIO3_05<br>) | SPIO_CSO /BC1                | O, 3.3V CMOS                | Thermal trip. This pin is connected to indication LED D11 and Expansion connector3 (J14) 53 <sup>rd</sup> Pin.                                                    |

| Pin<br>No. | Qseven MXM<br>Connector Pin | Signal Name       | CPU Ball Name/<br>Pin Number | Signal Type/ Termination | Description                                                                                                                                     |

|------------|-----------------------------|-------------------|------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 72         | Name<br>WDOUT               | Q7_WDOG_B         | NA                           | O, 3.3V CMOS             | This pin is connected to Expansion                                                                                                              |

|            |                             |                   |                              | ,                        | connector3 (J14) 15 <sup>th</sup> Pin in carrier board.                                                                                         |

| 73         | GND                         | GND               | NA                           | Power                    | Ground.                                                                                                                                         |

| 74         | GND                         | GND               | NA                           | Power                    | Ground.                                                                                                                                         |

| 75         | USB_P7-/<br>USB_SSTX0-      | USB3_HUB1_TX<br>M | NA                           | I, USB SS                | USB3.0 Host Port0 Transmit Differential pair negative. This pin is connected to Dual stack USB3.0 TypeA connector (J23) bottom port.            |

| 76         | USB_P6-/<br>USB_SSRXO-      | USB3_HUB1_RX<br>M | NA                           | O, USB SS                | USB3.0 Host Port0 Receive Differential pair negative. This pin is connected to Dual stack USB3.0 TypeA connector (J23) bottom port.             |

| 77         | USB_P7+/<br>USB_SSTX0+      | USB3_HUB1_TX<br>P | NA                           | I, USB SS                | USB3.0 Host Port0 Transmit Differential pair positive. This pin is connected to Dual stack USB3.0 TypeA connector (J23) bottom port.            |

| 78         | USB_P6+/<br>USB_SSRX0+      | USB3_HUB1_RX<br>P | NA                           | O, USB SS                | USB3.0 Host Port0 Receive Differential pair positive. This pin is connected to Dual stack USB3.0 TypeA connector (J23) bottom port.             |

| 79         | USB_6_7_OC#                 | NC                | NA                           | NA                       | NC in i.MX8 Qseven SOM.  Over current sense signal for USB3.0 Host Port0.  This pin is connected from USB3.0 Host Port0 Over current indicator. |

| 80         | USB_4_5_OC#                 | NC                | NA                           | NA                       | NC in i.MX8 Qseven SOM. This pin is connected to USB3.0 Host Port1 Over current indicator in carrier board.                                     |

| 81         | USB_P5-/<br>USB_SSTX1-      | USB3_HUB3_TX<br>M | NA                           | I, USB SS                | This pin is connected to Dual stack USB3.0 TypeA connector (J23) top port in carrier board.                                                     |

| 82         | USB_P4-/<br>USB_SSRX1-      | USB3_HUB3_RX<br>M | NA                           | O, USB SS                | This pin is connected to Dual stack USB3.0 TypeA connector (J23) top port in carrier board.                                                     |

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name                              | CPU Ball Name/<br>Pin Number | Signal Type/<br>Termination | Description                                                                                                                                                                    |

|------------|-------------------------------------|------------------------------------------|------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 83         | USB_P5+/<br>USB_SSTX1+              | USB3_HUB3_TX<br>P                        | NA                           | I, USB SS                   | NC in I.MX8 Qseven SOM. This pin is connected to Dual stack USB3.0 TypeA connector (J23) top port in carrier board.                                                            |

| 84         | USB_P4+/<br>USB_SSRX1+              | USB3_HUB3_RX<br>P                        | NA                           | O, USB SS                   | NC in I.MX8 Qseven SOM. This pin is connected to Dual stack USB3.0 TypeA connector (J23) top port in carrier board.                                                            |

| 85         | USB_2_3_OC#                         | USB_HUB3_OC/<br>USB_HUB2_OC              | NA                           | O, 3.3V CMOS                | Over current sense signal for USB Host Port2 and Port3. This pin is connected from USB Host Port2 Over current indicator.                                                      |

| 86         | USB_0_1_OC#                         | USB_UB1_OC/U<br>SB_OTG1_OC(G<br>PIO0_03) | NA                           | O, 3.3V CMOS/<br>10K PU     | Over current sense signal for USB Host Port0 and OTG Port1. This pin is connected from Host Port0 and USB OTG Port1 Over current indicator.                                    |

| 87         | USB_P3-                             | USB_HUB3OUT_<br>DM                       | NA                           | IO, DIFF                    | USB 2.0 Host Port3 Data negative. This pin is connected to Dual stack USB3.0 TypeA connector (J23) top port in carrier board (from the USB HUB output port2 of the I.MX8 SOM). |

| 88         | USB_P2-                             | USB_HUB2OUT_<br>DM                       | NA                           | IO, DIFF                    | USB 2.0 Host Port2 Data negative. This pin is connected to Dual stack USB3.0 TypeA connector (J23) bottom port.                                                                |

| 89         | USB_P3+                             | USB_HUB3OUT_<br>DP                       | NA                           | IO, DIFF                    | USB 2.0 Host Port3 Data positive. This pin is connected to Dual stack USB3.0 TypeA connector (J23) top port in carrier board (from the USB HUB output port2 of the I.MX8 SOM). |

| 90         | USB_P2+                             | USB_HUB2OUT_<br>DP                       | NA                           | IO, DIFF                    | USB 2.0 Host Port2 Data positive. This pin is connected to Dual stack USB3.0 TypeA connector (J23) bottom port.                                                                |

| 91         | USB_VBUS                            | VBUS_OTG1                                | USB_OTG1_VBU<br>S/ A39       | O, 5V Power                 | Reference voltage to USB controller.                                                                                                                                           |

| 92         | USB_ID                              | USB_ID                                   | USB_OTG1_ID/<br>A37          | O, 3.3V CMOS                | USB OTG ID.                                                                                                                                                                    |

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name         | CPU Ball Name/<br>Pin Number | Signal Type/<br>Termination | Description                                                                                                                                  |

|------------|-------------------------------------|---------------------|------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                     |                     |                              |                             | This pin is connected from Micro USB OTG connector (J2).                                                                                     |

| 93         | USB_P1-                             | USB_OTG1_DM         | USB_OTG1_DM<br>/<br>C39      | IO, DIFF                    | USB 2.0 OTG Port1 Data negative. This pin is connected to Micro USB OTG connector (J2).                                                      |

| 94         | USB_PO-                             | USB_HUB1OUT_<br>DM  | NA                           | IO, DIFF                    | USB 2.0 Host Port0 Data negative. This pin is connected to USB TypeA combo connector (J22) (from the USB HUB output port1 of the I.MX8 SOM). |

| 95         | USB_P1+                             | USB_OTG1_DP         | USB_OTG1_DP /<br>B40         | IO, DIFF                    | USB 2.0 OTG Port1 Data positive. This pin is connected to Micro USB OTG connector (J2).                                                      |

| 96         | USB_P0+                             | USB_HUB1OUT_<br>DP  | NA                           | IO, DIFF                    | USB 2.0 Host Port0 Data positive. This pin is connected to USB TypeA combo connector (J22) (from the USB HUB output port1 of the I.MX8 SOM). |

| 97         | GND                                 | GND                 | NA                           | Power                       | Ground.                                                                                                                                      |

| 98         | GND                                 | GND                 | NA                           | Power                       | Ground.                                                                                                                                      |

| 99         | eDP0_TX0+/<br>LVDS_A0+              | LVDS1_CH0_TX0<br>_P | LVDS1_CH0_TX0<br>_P/<br>BN37 | LVDS, DIFF                  | LVDS primary channel differential pair0 positive.  This pin is connected to LVDS Receiver.                                                   |

| 100        | eDP1_TX0+/<br>LVDS_B0+              | LVDS1_CH1_TX0<br>_P | LVDS1_CH1_TX0<br>_P/<br>BN33 | LVDS, DIFF                  | LVDS secondary channel differential pair0 positive. This pin is connected to secondary LVDS connector (J27) in carrier board.                |

| 101        | eDP0_TX0-/<br>LVDS_A0-              | LVDS1_CH0_TX0<br>_N | LVDS1_CH0_TX0<br>_N/<br>BL37 | LVDS, DIFF                  | LVDS primary channel differential pair0 negative. This pin is connected to LVDS Receiver.                                                    |

| 102        | eDP1_TX0-/<br>LVDS_B0-              | LVDS1_CH1_TX0<br>_N | LVDS1_CH1_TX0<br>_N/<br>BL33 | LVDS, DIFF                  | LVDS secondary channel differential pair0 negative. This pin is connected to secondary LVDS connector (J27) in carrier board.                |

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name               | CPU Ball Name/<br>Pin Number | Signal Type/<br>Termination | Description                                                                                                                   |

|------------|-------------------------------------|---------------------------|------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 103        | eDP0_TX1+/<br>LVDS_A1+              | LVDS1_CH0_TX1<br>_P       | LVDS1_CH0_TX1<br>_P/<br>BM38 | LVDS, DIFF                  | LVDS primary channel differential pair1 positive. This pin is connected to LVDS Receiver.                                     |

| 104        | eDP1_TX1+/<br>LVDS_B1+              | LVDS1_CH1_TX1<br>_P       | LVDS1_CH1_TX1<br>_P/<br>BM32 | LVDS, DIFF                  | LVDS secondary channel differential pair1 positive. This pin is connected to secondary LVDS connector (J27) in carrier board. |

| 105        | eDP0_TX1-/<br>LVDS_A1-              | LVDS1_CH0_TX1<br>_N       | LVDS1_CH0_TX1<br>_N/<br>BK38 | LVDS, DIFF                  | LVDS primary channel differential pair1 negative. This pin is connected to LVDS Receiver.                                     |

| 106        | eDP1_TX1-/<br>LVDS_B1-              | LVDS1_CH1_TX1<br>_N       | LVDS1_CH1_TX1<br>_N/<br>BK32 | LVDS, DIFF                  | LVDS secondary channel differential pair1 negative. This pin is connected to secondary LVDS connector (J27) in carrier board. |

| 107        | eDP0_TX2+/<br>LVDS_A2+              | LVDS1_CH0_TX2<br>_P       | LVDS1_CH0_TX2<br>_P/<br>BN39 | LVDS, DIFF                  | LVDS primary channel differential pair2 positive. This pin is connected to LVDS Receiver.                                     |

| 108        | eDP1_TX2+/<br>LVDS_B2+              | LVDS1_CH1_TX2<br>_P       | LVDS1_CH1_TX2<br>_P/<br>BN31 | LVDS, DIFF                  | LVDS secondary channel differential pair2 positive. This pin is connected to secondary LVDS connector (J27) in carrier board. |

| 109        | eDP0_TX2-/<br>LVDS_A2-              | LVDS1_CH0_TX2<br>_N       | LVDS1_CH0_TX2<br>_N/<br>BL39 | LVDS, DIFF                  | LVDS primary channel differential pair2 negative. This pin is connected to LVDS Receiver.                                     |

| 110        | eDP1_TX2-/<br>LVDS_B2-              | LVDS1_CH1_TX2<br>_N       | LVDS1_CH1_TX2<br>_N/<br>BL31 | LVDS, DIFF                  | LVDS secondary channel differential pair2 negative. This pin is connected to secondary LVDS connector (J27) in carrier board. |

| 111        | LVDS_PPEN                           | LCD1_VDD_EN(<br>GPIO1_14) | LVDS1_I2C1_SC<br>L/<br>BD32  | I, 3.3V CMOS/<br>10K PU     | LCD Panel Power Enable.                                                                                                       |

| 112        | LVDS_BLEN                           | LCD1_EN(GPIO1<br>_09)     | LVDS0_I2C1_SD<br>A/          | I, 3.3V CMOS/<br>10K PU     | LCD Panel Backlight Enable Control.                                                                                           |

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name         | CPU Ball Name/<br>Pin Number         | Signal Type/<br>Termination | Description                                                                                                                   |

|------------|-------------------------------------|---------------------|--------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 113        | eDPO_TX3+/<br>LVDS_A3+              | LVDS1_CH0_TX3<br>_P | BE35<br>LVDS1_CH0_TX3<br>_P/<br>BM40 | LVDS, DIFF                  | LVDS primary channel differential pair3 positive. This pin is connected to LVDS Receiver.                                     |

| 114        | eDP1_TX3+/<br>LVDS_B3+              | LVDS1_CH1_TX3<br>_P | LVDS1_CH1_TX3<br>_P/<br>BM30         | LVDS, DIFF                  | LVDS secondary channel differential pair3 positive. This pin is connected to secondary LVDS connector (J27) in carrier board. |

| 115        | eDP0_TX3-/<br>LVDS_A3-              | LVDS1_CH0_TX3<br>_N | LVDS1_CH0_TX3<br>_N/<br>BK40         | LVDS, DIFF                  | LVDS primary channel differential pair3 negative. This pin is connected to LVDS Receiver.                                     |

| 116        | eDP1_TX3-/<br>LVDS_B3-              | LVDS1_CH1_TX3<br>_N | LVDS1_CH1_TX3<br>_N/<br>BK30         | LVDS, DIFF                  | LVDS secondary channel differential pair3 negative. This pin is connected to secondary LVDS connector (J27) in carrier board. |

| 117        | GND                                 | GND                 | NA                                   | Power                       | Ground.                                                                                                                       |

| 118        | GND                                 | GND                 | NA                                   | Power                       | Ground.                                                                                                                       |

| 119        | eDP0_AUX+/<br>LVDS_A_CLK+           | LVDS1_CH0_CLK<br>_P | LVDS1_CH0_CLK<br>_P/<br>BM36         | LVDS, DIFF                  | LVDS primary channel differential Clock positive. This pin is connected to LVDS Receiver.                                     |

| 120        | eDP1_AUX+/<br>LVDS_B_CLK+           | LVDS1_CH1_CLK<br>_P | LVDS1_CH1_CLK<br>_P/<br>BM34         | LVDS, DIFF                  | LVDS secondary channel differential Clock positive. This pin is connected to secondary LVDS connector in carrier board.       |

| 121        | eDP0_AUX-/<br>LVDS_A_CLK-           | LVDS1_CH0_CLK<br>_N | LVDS1_CH0_CLK<br>_N/<br>BK36         | LVDS, DIFF                  | LVDS primary channel differential Clock negative. This pin is connected to LVDS Receiver.                                     |

| 122        | eDP1_AUX-/<br>LVDS_B_CLK-           | LVDS1_CH1_CLK<br>_N | LVDS1_CH1_CLK<br>_N/<br>BK34         | LVDS, DIFF                  | LVDS secondary channel differential Clock negative. This pin is connected to secondary LVDS connector (J27) in carrier board. |

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name                            | CPU Ball Name/<br>Pin Number | Signal Type/<br>Termination | Description                                                                                                                  |

|------------|-------------------------------------|----------------------------------------|------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 123        | LVDS_BLT_CTRL<br>/GP_PWM_OUT<br>0   | LCD1_BL_PWM(<br>GPIO1_10) <sup>1</sup> | LVDS1_GPIO00/<br>BD34        | I, 3.3V CMOS/<br>10K PU     | RGB & LVDS LCD Panel Backlight Control.                                                                                      |

| 124        | GP_1-Wire_Bus                       | HDMI_TX0_CEC                           | HDMI_TX0_CEC<br>/<br>BJ1     | O, 3.3V CMOS                | This pin is connected to HDMI connector (J24) in carrier board.                                                              |

| 125        | GP2_I2C_DAT/L<br>VDS_DID_DAT        | LVDS1_I2C0_SD<br>A                     | LVDS1_I2C0_SD<br>A/E33       | IO, 3.3V OD/                | I2C3 Data. This pin is directly connected to Expansion Connector3 (J14) 35 <sup>th</sup> Pin in carrier board.               |

| 126        | eDP0_HPD#<br>/LVDS_BLC_DAT          | NC                                     | NA                           | NA                          | NC in i.MX8 Qseven SOM.  This pin is directly connected to Expansion Connector3 (J14) 19 <sup>th</sup> Pin in carrier board. |

| 127        | GP2_I2C_CLK<br>/LVDS_DID_CLK        | LVDS1_I2C0_SC<br>L                     | LVDS1_I2C0_SC<br>L/BL35      | I, 3.3V OD                  | I2C3 Clock. This pin is directly connected to Expansion Connector3 (J14) 37 <sup>th</sup> Pin in carrier board.              |

| 128        | eDP1_HPD#<br>/LVDS_BLC_CLK          | NC                                     | NA                           | NA                          | NC in i.MX8 Qseven SOM.  This pin is directly connected to Expansion Connector3 (J14) 21 <sup>st</sup> Pin in carrier board. |

| 129        | CANO_TX                             | FLEXCANO_TX                            | FLEXCANO_TX/H<br>6           | I, 3.3V CMOS                | Transmit input for CAN0 bus.  This pin is connected to CAN0  Transceiver.                                                    |

| 130        | CANO_RX                             | FLEXCANO_RX                            | FLEXCANO_RX/C<br>5           | O, 3.3V CMOS                | Receive output for CAN0 bus.  This pin is connected from CAN0  Transceiver.                                                  |

| 131        | DP_LANE3+/<br>TMDS_CLK+             | HDMI_TXO_CLK<br>_P/EDP3_P              | HDMI_TX0_CLK<br>_EDP3_P/BL3  | I, HDMI or EDP              | HDMI differential data lane clock positive. This pin is connected to HDMI connector (J24) in carrier board.                  |

| 132        | RSVD                                | USB3_HUB2_TX<br>M                      | NA                           | I, USB SS                   | Note: This pin is directly connected to Expansion Connector3 (J14) 23 <sup>rd</sup> Pin in carrier board.                    |

| 133        | DP_LANE3-/<br>TMDS_CLK-             | HDMI_TX0_CLK<br>_N/EDP3_N              | HDMI_TX0_CLK<br>_EDP3_N/BK2  | I, HDMI or EDP              | HDMI differential data clock negative. This pin is connected to HDMI connector (J24) in carrier board.                       |

| 134        | RSVD                                | USB3_HUB2_TX<br>P                      | NA                           | I, USB SS                   | Note: This pin is directly connected to Expansion Connector3 (J14) 25 <sup>th</sup> Pin in carrier board.                    |

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name                 | CPU Ball Name/<br>Pin Number      | Signal Type/<br>Termination | Description                                                                                                                       |

|------------|-------------------------------------|-----------------------------|-----------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 135        | GND                                 | GND                         | NA                                | Power                       | Ground.                                                                                                                           |

| 136        | GND                                 | GND                         | NA                                | Power                       | Ground.                                                                                                                           |

| 137        | DP_LANE1+/<br>TMDS_LANE1+           | HDMI_TX0_DAT<br>A1_P/EDP1_P | HDMI_TX0_DAT<br>A1_EDP1_P<br>/BL7 | I, HDMI or EDP              | HDMI differential data lane 1 positive. This pin is connected to HDMI connector (J24) in carrier board.                           |

| 138        | DP_AUX+                             | EDP_AUX_P                   | HDMI_TX0_AUX<br>_P /<br>BH2       | I, EDP                      | Note: This pin is directly connected to Expansion Connector3 (J14) 52 <sup>nd</sup> Pin in carrier board.                         |

| 139        | DP_LANE1-/<br>TMDS_LANE1-           | HDMI_TX0_DAT<br>A1_N/EDP1_N | HDMI_TX0_DAT<br>A1_EDP1_N<br>/BM6 | I, HDMI or EDP              | HDMI differential data lane 1 negative. This pin is connected to HDMI connector (J24) in carrier board.                           |

| 140        | DP_AUX-                             | EDP_AUX_N                   | HDMI_TX0_AUX<br>_N /<br>BG3       | I, EDP                      | Note: This pin is directly connected to Expansion Connector3 (J14) 54 <sup>th</sup> Pin in carrier board.                         |

| 141        | GND                                 | GND                         | NA                                | Power                       | Ground.                                                                                                                           |

| 142        | GND                                 | GND                         | NA                                | Power                       | Ground.                                                                                                                           |

| 143        | DP_LANE2+/<br>TMDS_LANE0+           | HDMI_TX0_DAT<br>A0_P/EDP2_P | HDMI_TX0_DAT<br>A0_EDP2_P<br>/BL5 | I, HDMI or EDP              | NC in I.MX8 Qseven SOM.  HDMI differential data lane 0 positive.  This pin is connected to HDMI connector (J24) in carrier board. |

| 144        | RSVD                                | USB3_HUB2_RX<br>M           | NA                                | O, USB SS                   | Note: This pin is directly connected to Expansion Connector3 (J14) 29 <sup>th</sup> Pin in carrier board.                         |

| 145        | DP_LANE2-/<br>TMDS_LANE0-           | HDMI_TX0_DAT<br>A0_N/EDP2_N | HDMI_TX0_DAT<br>A0_EDP2_N<br>/BM4 | I, HDMI or EDP              | NC in I.MX8 Qseven SOM.  HDMI differential data lane 0 negative.  This pin is connected to HDMI connector (J24) in carrier board. |

| 146        | RSVD                                | USB3_HUB2_RX<br>P           | NA                                | O, USB SS                   | Note: This pin is directly connected to Expansion Connector3 (J14) 31 <sup>st</sup> Pin in carrier board.                         |

| 147        | GND                                 | GND                         | NA                                | Power                       | Ground.                                                                                                                           |

| 148        | GND                                 | GND                         | NA                                | Power                       | Ground.                                                                                                                           |

| 149        | DP_LANE0+/<br>TMDS_LANE2+           | HDMI_TX0_DAT<br>A2_P/EDP0_P | HDMI_TX0_DAT<br>A2_EDP0_P<br>/BL9 | I, HDMI or EDP              | HDMI differential data lane 2 positive. This pin is connected to HDMI connector (J24) in carrier board.                           |

| 150        | HDMI_CTRL_DA<br>T                   | HDMI_TX0_CTR<br>L_DAT       | HDMI_TX0_DDC<br>_SDA/             | IO, 3.3V CMOS               | HDMI I2C Data.                                                                                                                    |

| Pin<br>No. | Qseven MXM<br>Connector Pin<br>Name | Signal Name                             | CPU Ball Name/<br>Pin Number      | Signal Type/<br>Termination | Description                                                                                                                        |

|------------|-------------------------------------|-----------------------------------------|-----------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|            |                                     |                                         | BN5                               |                             | This pin is connected to HDMI connector (J24) in carrier board.                                                                    |

| 151        | DP_LANEO-/<br>TMDS_LANE2-           | HDMI_TX0_DAT<br>A2_N/EDP0_N             | HDMI_TX0_DAT<br>A2_EDP0_N<br>/BM8 | I, HDMI or EDP              | HDMI differential data lane 2 negative. This pin is connected to HDMI connector (J24) in carrier board.                            |

| 152        | HDMI_CTRL_CL<br>K                   | HDMI_TX0_CTR<br>L_CLK                   | HDMI_TX0_DDC<br>_SCL/<br>BG1      | I, 3.3V CMOS                | HDMI I2C Clock.  This pin is connected to HDMI connector (J24) in carrier board.                                                   |

| 153        | DP_HDMI_HPD#                        | HDMI_TX_HPD                             | HDMI_TX0_HPD<br>/<br>BH8          | O, 3.3V CMOS                | HDMI hot plug detect. This pin is connected to HDMI connector (J24) in carrier board.                                              |

| 154        | RSVD                                | NC                                      | NA                                | NA                          | NC in i.MX8 Qseven SOM.  Note: This pin is directly connected to Expansion Connector3 (J14) 39 <sup>th</sup> Pin in carrier board. |

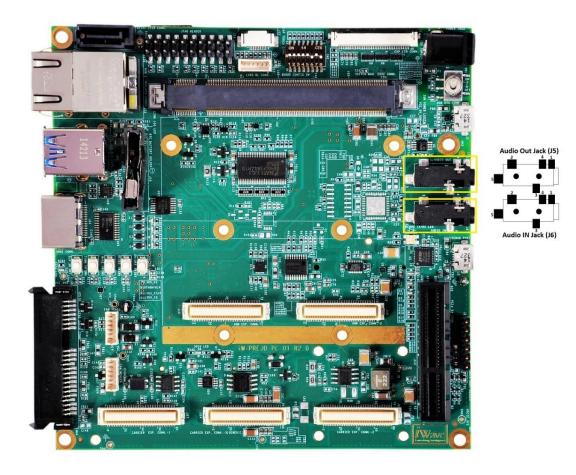

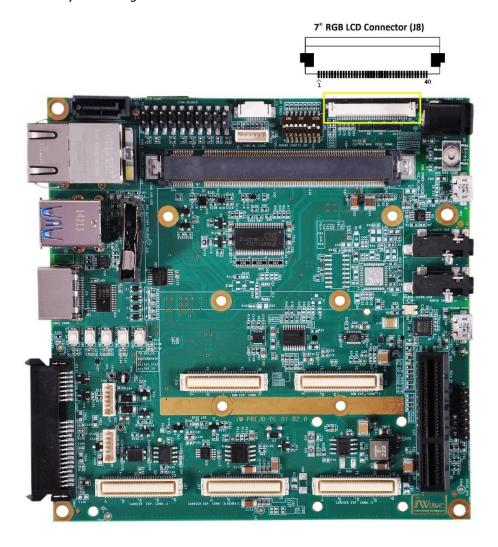

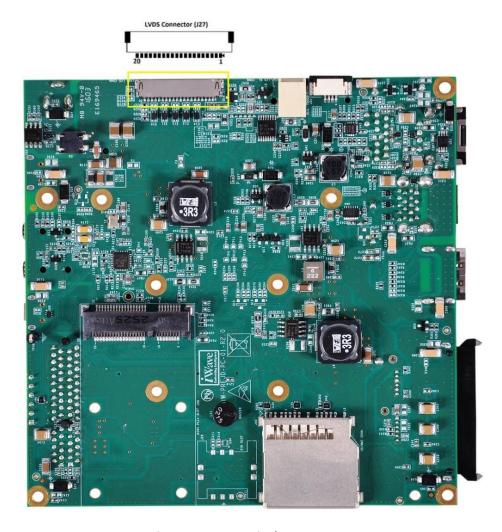

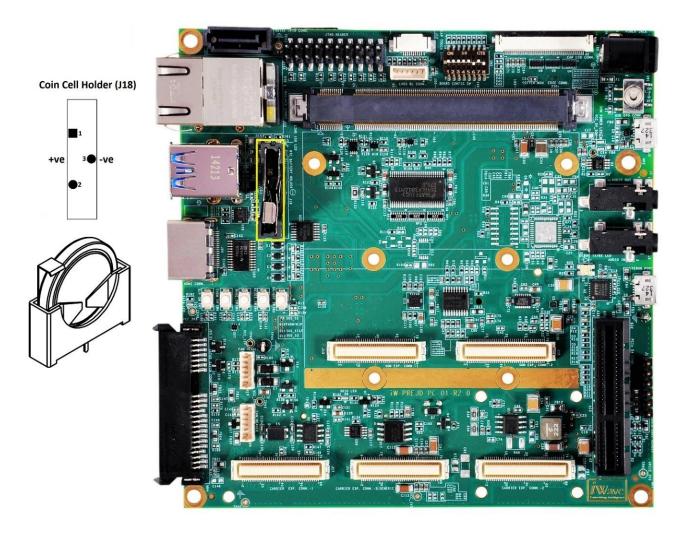

| 155        | PCIE_CLK_REF+                       | PCIE_A_REFCLK<br>_P                     | NA                                | I, PCIe                     | PCIe differential reference clock positive. This pin is connected to PCIe clock buffer.                                            |