## nRF21540

## **Objective Product Specification**

v0.5.2

## Key features

#### Key features:

- Supports *Bluetooth*<sup>®</sup> Low Energy, 802.15.4, and proprietary applications

- Max output power 22 dBm

- Adjustable output power to ±1 dB from 5 to 21 dBm

- User programmable modes for TX gain

- Support for two antenna interfaces

- Receive gain +13 dB

- Single-ended 50 Ω matched input and output

- 115 mA @ +20 dBm output power

- 42 mA @ +10 dBm output power

- Control interface via IO, SPI, or a combination of both

- Supply voltage 1.7 to 3.6 V, suitable for 1.8+/-5% systems

- Operating temperature -40°C to 105°C

- Package variant QFN16 4 x 4 mm

#### Applications:

- Smart Home applications

- Industrial and factory automation

- Asset tracking

- Advanced CE remote controls

- Sports and Fitness

- Toys

- Medical

- Beacons

## Contents

|    | Key features                                                                                                                                                                                                                       | ii                                                                                                                     |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 1  | Revision history                                                                                                                                                                                                                   | 5                                                                                                                      |

| 2  | Product overview                                                                                                                                                                                                                   | 6                                                                                                                      |

| 3  | About this document.         3.1 Document status .         3.2 Peripheral chapters .         3.3 Register tables .         3.3.1 Fields and values .         3.3.2 Permissions .         3.4 Registers .         3.4.1 DUMMY .     | . 7<br>. 7<br>. 7<br>. 8                                                                                               |

| 4  | Block diagram                                                                                                                                                                                                                      | 10                                                                                                                     |

| 5  | Device control.         5.1 Operational states .         5.2 State transition timing .         5.3 TX power control .         5.4 UICR program usage .                                                                             | 12<br>13                                                                                                               |

| 6  | SPI interface                                                                                                                                                                                                                      | 15                                                                                                                     |

| 7  | Flectrical specification.         7.1 Electrical specification.         7.1.1 Current consumption.         7.1.2 RX.         7.1.3 TX.         7.1.4 SPI timing specification.                                                     | 17<br>17<br>17<br>17<br>17<br>18                                                                                       |

| 8  | Register interface.         8.1 Registers         8.1.1 CONFREG0         8.1.2 CONFREG1         8.1.3 CONFREG2         8.1.4 CONFREG3         8.1.5 PARTNUMBER         8.1.6 HW_REVISION         8.1.7 HW_ID0         8.1.8 HW_ID1 | <ol> <li>19</li> <li>19</li> <li>19</li> <li>20</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> <li>21</li> </ol> |

| 9  | Hardware and layout                                                                                                                                                                                                                | <b>22</b>                                                                                                              |

| 10 | 9.2 Reference circuitry                                                                                                                                                                                                            | 23<br>24                                                                                                               |

| 11 | Absolute maximum ratings. | 25 |

|----|---------------------------|----|

| 12 | Legal notices.            | 26 |

# 1 Revision history

| Date     | Version | Description   |

|----------|---------|---------------|

| Dec 2019 | 0.5.2   | First release |

# 2 Product overview

nRF21540 is an RF front-end module suitable for Bluetooth Low Energy and IEEE 802.15.4 range extension.

Features include a configurable gain Power amplifier (PA) in the transmit path (TX) and Low noise amplifier (LNA) in the receive path (RX). Single-ended operation on both TRX and ANT1/2 ports is supported and requires only three external components (for single antenna operation) for the RF path.

The device is controlled through a set of input pins and/or through the SPI interface, by writing to internal control registers. The two antenna ports enable applications using antenna diversity and can be selected using pin ANT\_SEL.

The device features highly configurable gain in Transmit state, enabling the application to implement adaptive gain control algorithms.

# **3** About this document

This document is organized into chapters that are based on the modules and peripherals available in the IC.

### 3.1 Document status

The document status reflects the level of maturity of the document.

| Document name                         | Description                                                                                                                                                                                                                                                              |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective Product Specification (OPS) | Applies to document versions up to 1.0.<br>This document contains target specifications for<br>product development.                                                                                                                                                      |

| Product Specification (PS)            | Applies to document versions 1.0 and higher.<br>This document contains final product<br>specifications. Nordic Semiconductor ASA reserves<br>the right to make changes at any time without<br>notice in order to improve design and supply the<br>best possible product. |

Table 1: Defined document names

### 3.2 Peripheral chapters

Every peripheral has a unique capitalized name or an abbreviation of its name, e.g. TIMER, used for identification and reference. This name is used in chapter headings and references, and it will appear in the ARM<sup>®</sup> Cortex<sup>®</sup> Microcontroller Software Interface Standard (CMSIS) hardware abstraction layer to identify the peripheral.

The peripheral instance name, which is different from the peripheral name, is constructed using the peripheral name followed by a numbered postfix, starting with 0, for example, TIMERO. A postfix is normally only used if a peripheral can be instantiated more than once. The peripheral instance name is also used in the CMSIS to identify the peripheral instance.

The chapters describing peripherals may include the following information:

- A detailed functional description of the peripheral

- Register configuration for the peripheral

- Electrical specification tables, containing performance data which apply for the operating conditions described in Recommended operating conditions on page 24.

### 3.3 Register tables

Individual registers are described using register tables. These tables are built up of two sections. The first three colored rows describe the position and size of the different fields in the register. The following rows describe the fields in more detail.

### 3.3.1 Fields and values

The **Id** (Field Id) row specifies the bits that belong to the different fields in the register. If a field has enumerated values, then every value will be identified with a unique value id in the Value Id column.

A blank space means that the field is reserved and read as undefined, and it also must be written as 0 to secure forward compatibility. If a register is divided into more than one field, a unique field name is specified for each field in the **Field** column. The **Value Id** may be omitted in the single-bit bit fields when values can be substituted with a Boolean type enumerator range, e.g. true/false, disable(d)/enable(d), on/ off, and so on.

Values are usually provided as decimal or hexadecimal. Hexadecimal values have a  $0 \times$  prefix, decimal values have no prefix.

The Value column can be populated in the following ways:

- Individual enumerated values, for example 1, 3, 9.

- Range of values, e.g. [0..4], indicating all values from and including 0 and 4.

- Implicit values. If no values are indicated in the **Value** column, all bit combinations are supported, or alternatively the field's translation and limitations are described in the text instead.

If two or more fields are closely related, the **Value Id**, **Value**, and **Description** may be omitted for all but the first field. Subsequent fields will indicate inheritance with '..'.

A feature marked **Deprecated** should not be used for new designs.

#### 3.3.2 Permissions

Different fields in a register might have different access permissions enforced by hardware.

The access permission for each register field is documented in the Access column in the following ways:

| Access | Description     | Hardware behavior                                                                                                      |

|--------|-----------------|------------------------------------------------------------------------------------------------------------------------|

| RO     | Read-only       | Field can only be read. A write will be ignored.                                                                       |

| WO     | Write-only      | Field can only be written. A read will return an undefined value.                                                      |

| RW     | Read-write      | Field can be read and written multiple times.                                                                          |

| W1     | Write-once      | Field can only be written once per reset. Any subsequent write will be ignored. A read will return an undefined value. |

| RW1    | Read-write-once | Field can be read multiple times, but only written once per reset. Any subsequent write will be ignored.               |

Table 2: Register field permission schemes

## 3.4 Registers

| Register | Offset                                      | Description                |

|----------|---------------------------------------------|----------------------------|

| DUMMY    | UMMY 0x514 Example of a register controllin |                            |

|          |                                             | Table 3: Register overview |

#### 3.4.1 DUMMY

Address offset: 0x514

Example of a register controlling a dummy feature

| Bit number       |              | 31 30 29 28 27 26 25 2 | 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4   | 3210       |

|------------------|--------------|------------------------|------------------------------------------------------------|------------|

| ID               |              | DDD                    | D C C C B                                                  | A A        |

| Reset 0x00050002 |              | 0 0 0 0 0 0 0          | 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0                    | 0010       |

| ID Acce Field    |              |                        |                                                            |            |

| A RW FIELD_A     |              |                        | Example of a read-write field with several enumerated      |            |

|                  |              |                        | values                                                     |            |

|                  | Disabled     | 0                      | The example feature is disabled                            |            |

|                  | NormalMode   | 1                      | The example feature is enabled in normal mode              |            |

|                  | ExtendedMode | 2                      | The example feature is enabled along with extra            |            |

|                  |              |                        | functionality                                              |            |

| B RW FIELD_B     |              |                        | Example of a deprecated read-write field                   | Deprecated |

|                  | Disabled     | 0                      | The override feature is disabled                           |            |

|                  | Enabled      | 1                      | The override feature is enabled                            |            |

| C RW FIELD_C     |              |                        | Example of a read-write field with a valid range of values |            |

|                  | ValidRange   | [27]                   | Example of allowed values for this field                   |            |

| D RW FIELD_D     |              |                        | Example of a read-write field with no restriction on the   |            |

| values           |              | values                 |                                                            |            |

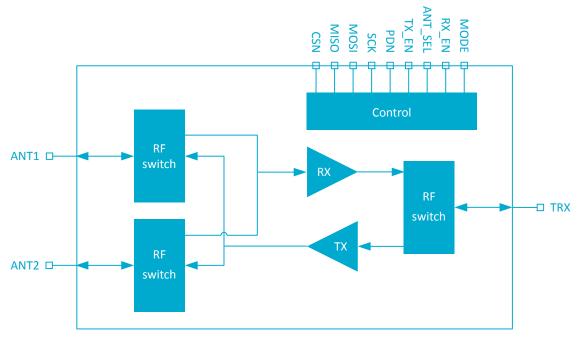

## 4 Block diagram

The block diagram illustrates the overall system.

Figure 1: nRF21540 Block diagram

# 5 Device control

### 5.1 Operational states

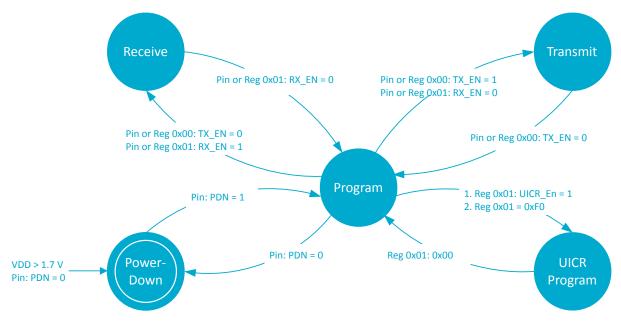

This section describes how nRF21540 can be set to different operational states.

When PDN is set to 0, the device is in Power-down state. When PDN is set to 1, the device is in the Program state. It can be set to any other state (Receive, Transmit, and UICR Program) using pin control or the SPI interface.

State transitions are controlled by pins PDN, RX\_EN, and TX\_EN or bit fields in SPI registers 0x00 and 0x01. For example, if RX\_EN is set to 1 in Program state, the device will enter the Receive state. Similarly, if TX\_EN is set to 1 in Program state, the device will enter the Transmit state. If RX\_EN is set to 0 during the Receive state, and TX\_EN is set to 1 at the same write cycle, then the state changes first to the Program state and then to the Transmit state. If both RX\_EN and TX\_EN are set to 1 when the device is in the Program state, the device will stay in the Program state (i.e. the operational state does not change). State transitions are shown in the following figure. For details regarding timings required when switching between operating states, see <u>State transition timing</u> on page 12.

When the device is in the Receive state, the receive path is active and the transmit path is disabled. When the device is in the Transmit state, the transmit path is enabled and the receive path is disabled.

When the device is in the Receive state, CSN needs to be driven low when either pin RX\_EN or an SPI command is used for control, as shown in Figure 4: Control pin controls state change on page 13.

#### Figure 2: State diagram

The device features a configurable TX output power. See TX power control on page 13 for details.

UICR (user information configuration register) Program state programs default settings for TX power control to UICR EFUSE (one time programmable memory). UICR Program state is accessed from Program state by writing specific values to register 0x01. Registers 0x02 and 0x03 are where bit programming definition and triggering of UICR EFUSE programming can take place. See UICR program usage on page 14 for more details about UICR programming.

The SPI register interface is described in detail in SPI interface on page 15.

| State        | Symbol | Description                                                                                                              |

|--------------|--------|--------------------------------------------------------------------------------------------------------------------------|

| Power-down   | PD     | The device is in Power-down state.                                                                                       |

| Program      | PG     | The device can be configured and set to other states.                                                                    |

| UICR program | UICR   | User defined initialization values for POUTA_SEL,<br>POUTA_UICR, POUTB_SEL, and POUTB_UICR can be<br>configured to UICR. |

| Receive      | RX     | The RX path is enabled.                                                                                                  |

| Transmit     | ТХ     | The TX path is enabled.                                                                                                  |

Table 4: Operating states description

ANT\_SEL selects which of the two antenna interfaces is used during RX or TX. Antenna interface control is specified in Table 5: Antenna switch control with ANT\_SEL in different states on page 12.

| State ANT_SEL I     |   | Description                                |  |  |

|---------------------|---|--------------------------------------------|--|--|

| Power-down          | х | Antenna switches disabled (i.e. isolating) |  |  |

| Program X Antenna s |   | Antenna switches disabled (i.e. isolating) |  |  |

| UICR program        | х | Antenna switches disabled (i.e. isolating) |  |  |

| Dessive             | 0 | ANT1 enabled, ANT2 disabled                |  |  |

| Receive             | 1 | ANT1 disabled, ANT2 enabled                |  |  |

| Transmit            | 0 | ANT1 enabled, ANT2 disabled                |  |  |

| Iransiiit           | 1 | ANT1 disabled, ANT2 enabled                |  |  |

Table 5: Antenna switch control with ANT\_SEL in different states

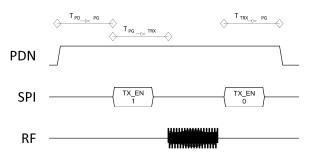

### 5.2 State transition timing

The following equation is used to define TPG $\rightarrow$ TRX when a slower SPI is used. Here it is assumed that there is a half SCK cycle gap between CSN and the first rising edge of SCK and the last falling edge of SCK and CSN.

Note: GPIO control is faster than SPI control.

$$T_{PG \to TRX} = \left(12.5 + 16.5 \cdot \left(\frac{1}{F_{SCK} \text{ [MHz]}} - \frac{1}{8}\right)\right) \mu \text{s}$$

| Figure 3: Defining | TPG to | TRX with | slower SPI |

|--------------------|--------|----------|------------|

|--------------------|--------|----------|------------|

Settling time requirements when switching between operational states are defined in Table 6: Settling times on page 13. An 8 MHz SCK clock must be used with SPI to obtain the timing given in the following table.

| Symbol                  | Parameter                                        | Note                                                  | Max. | Unit |

|-------------------------|--------------------------------------------------|-------------------------------------------------------|------|------|

| $T_{PD \rightarrow PG}$ | Settling time from state PD to PG                | Triggered by PDN                                      | 17.5 | μs   |

| T <sub>PG→TRX</sub>     | Settling time from state PG to TX or RX          | Triggered by RX_EN, TX_EN, or SPI register write      | 12.5 | μs   |

| T <sub>TRX→PG</sub>     | Power-off time when changing from RX or TX to PG | Triggered by RX_EN, TX_EN, or SPI<br>Reg<br>0x0 write | 5    | μs   |

| $T_{PG \rightarrow PD}$ | Settling time from state PG to PD                | Triggered by PDN                                      | 10   | μs   |

#### Table 6: Settling times

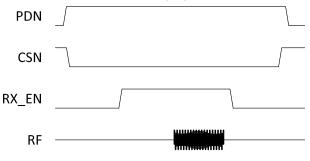

When the device is in the Receive state, CSN pin needs to be driven low. An example of RX timing using an RX\_EN pin-based configuration is shown in the following figure.

Figure 4: Control pin controls state change

The following figure shows the Transmit state configured using SPI.

### 5.3 TX power control

The output power for the Transmit state can be configured using either pin control or the SPI interface.

To configure the output power through pins, the MODE pin or register 0x00 can be used to set TX power control to one of two preset values. Preset values are used to update the TX\_Gain value when the MODE pin control changes in the Program state. Preset values can be set in UICR and selected. Table 7: TX power control on page 14 presents the TX\_Gain initialization functionality.

The SPI interface can also be used to control the output power. Before entering the Transmit state, TX Gain is configured by writing the gain value over SPI to register 0x00 TX\_Gain field. SPI write will always overwrite the initialization value. The Gain word can be set in the same write cycle when TX is enabled in the Program state.

Note: Gain should not be changed while the device is in the Transmit state.

If TX\_Gain is modified through SPI, and TX is not enabled (i.e. Reg 0x00: TX\_EN = 0), toggling the MODE bit in Reg 0x00 will change register TX\_Gain field content to preset values. If SPI write sets TX\_Gain at the same time TX\_EN is set to 1, and the MODE bit in Reg 0x0 is not toggled at the same write, it does not matter if MODE has been toggled before. The SPI written value for TX\_Gain will be used in the Transmit state. If SPI write sets the MODE bit to toggle at the same time TX\_EN is set to 1, the preset TX\_Gain value will be used in the Transmit state.

The following table shows TX power control with MODE control and corresponding preset values of TX\_Gain in program state.

| MODE | POUTA_SEL | POUTB_SEL | TX_Gain    | Description                        |

|------|-----------|-----------|------------|------------------------------------|

| 0    | 0         | x         | POUTA_PROD | Chip production default value used |

| 1    | x         | 0         | POUTB_PROD | Chip production default value used |

| 0    | 1         | X         | POUTA_UICR | End-user default value used        |

| 1    | X         | 1         | POUTB_UICR | End-user default value used        |

Table 7: TX power control

### 5.4 UICR program usage

The UICR program state enables the automated programming sequence for UICR EFUSE cell.

The automated programming sequence can be utilized in the following manner:

**1.** Apply VDD supply voltage using the specifications set in the following table.

| Parameter       | Min.   | Max.   |

|-----------------|--------|--------|

| V <sub>DD</sub> | 3.45 V | 3.60 V |

| T <sub>OP</sub> | 0°C    | 85°C   |

#### Table 8: EFUSE programming conditions

- Set device to UICR Program state by sequentially writing 0x04 (UICR\_EN = 1) and 0xF0 to register CONFREG1.

- 3. Write desired configuration values to register 0x03 for POUT\_B\_Sel and POUTB\_UICR.

- **4.** Write desired configuration values for POUTA\_Sel and POUTA\_UICR to register 0x02. Write a 1 to WR\_UICR in register 0x02.

- 5. Wait for at least 0.5 ms to guarantee successful programming.

- **6.** Reset the circuit by setting PDN to 0 and then back to 1.

The programmed values are now set for register 0x02 and 0x03. The device can be set to UICR mode for reading registers 0x02 and 0x03 to verify programmed values.

# 6 SPI interface

SPI registers are one byte long. The data transitions for slave in and out (MOSI and MISO) happen on the falling edge of the serial clock (SCK).

Input data is sampled on the rising edge of SCK, starting with the first rising edge. Therefore, it is required that the first bit is stable on the first rising clock edge of SCK. Common definitions for SPI bus are CPOL = 0 and CPHA = 0. The serial data frame is 16 bits long and consists of three parts in transmission order: command (Cmd), address, and data. All fields are sent on MOSI line MSB first. In the event of a write operation, a command is 2 bits long, an address is 6 bits long, followed by 8 bits of data. CSN is active low and it is assumed that it is set to 0 at least half a SCK cycle before the first rising edge of SCK, and then again to logical 1 earliest after half a cycle of 16th SCK falling edge.

The following commands are used:

- READ, b10 This command allows reading of registers. The register address to read from is sent after the command. The read data will be clocked out to the MISO line during the data part of the SPI frame.

- WRITE, b11 This command allows writing to registers. The last 8 bits sent on the MOSI line will be written to a register pointed with 6-bit address field. The write command has writeback property. When a register is accessed by the write command to update its value, the previous register value will be written to MISO line in serial format MSB first.

SPI timing specification presents the required timings between CSN signal and SCK edge.

Figure 6: SPI write configuration example on page 15 shows a configuration example for SPI when writing to register 0x00. Command b11 is written to the command field. The first bit on the MOSI line shall be set to its value (in this case to 1) before the first rising edge of SCK occurs, since Cmd is read on the rising edge of the first and second SCK cycle. SCK rising edges 3 to 8 are used to read the address field and 9 to 16 read the data field. Register 0x00 writeback data is written on the MISO line starting on the falling edge of cycle 8 so that cycle 9 to 16 rising edges can be used to read in MISO data on the Master side. Guaranteed settling time for the first read bit before the cycle 9 falling edge can be found in SPI timing specification.

Functionality of the read operation is similar to writeback, meaning that read data is written to the MISO line starting on the cycle 8 falling edge when the read command is given in the Cmd field.

An overview of register address space and accessibility of registers in different operation states is found in SPI timing.

The detailed register map is given in the Register interface on page 19.

| SCK  |   | 2 3 4 5 6   |                     |                              |  |

|------|---|-------------|---------------------|------------------------------|--|

| CSN  |   |             |                     |                              |  |

| MOSI |   | Cmd:<br>b11 | Address:<br>b000000 | Data:<br>b00100110           |  |

| MISO | 0 |             |                     | Writeback data:<br>b00100100 |  |

Figure 6: SPI write configuration example

| Register address | Function                                              | Accessible via SPI |  |  |  |

|------------------|-------------------------------------------------------|--------------------|--|--|--|

| 0x00             | TX state control and TX gain control in Program state | PG, RX, TX, UICR   |  |  |  |

| 0x01             | RX state control and RX gain control in Program state | PG, RX, TX, UICR   |  |  |  |

| 0x02, 0x03       | UICR programming interface registers                  | UICR               |  |  |  |

| 0x14, 0x15[7:4]  | Part number, hardware revision                        | PG                 |  |  |  |

| 0x16, 0x17       | Hardware ID                                           | PG                 |  |  |  |

Table 9: Register overview and accessibility in different operation states

## 7 Electrical specification

The device is calibrated at  $25^{\circ}$ C to VDD = 3.0 V.

Unless otherwise stated, the following conditions apply:

- VDD = 3.0 V

- Z<sub>L</sub> = 50 Ω

- P<sub>IN\_TRX</sub> = 0 dBm

## 7.1 Electrical specification

### 7.1.1 Current consumption

| Symbol                | Description              | Min. | Тур. | Max. | Units |

|-----------------------|--------------------------|------|------|------|-------|

| I <sub>PD</sub>       | State: PD                |      | 30   |      | nA    |

| I <sub>PG</sub>       | State: PG                |      | 0.7  |      | mA    |

| I <sub>RX</sub>       | State: RX                |      | 4.1  |      | mA    |

| I <sub>TX_10dBm</sub> | State: TX                |      | 42   |      | mA    |

|                       | P <sub>OUT</sub> = 10dBm |      |      |      |       |

| I <sub>TX_20dBm</sub> | State: TX                |      | 115  |      | mA    |

|                       | P <sub>OUT</sub> = 20dBm |      |      |      |       |

### 7.1.2 RX

| Symbol                | Description                                                     | Min.  | Тур.  | Max.  | Units |

|-----------------------|-----------------------------------------------------------------|-------|-------|-------|-------|

| f                     | Operating frequency range                                       | 2360  |       | 2500  | MHz   |

| G <sub>RX</sub>       | Gain                                                            |       | 13    |       | dB    |

| NF <sub>RX</sub>      | Noise figure                                                    |       | 2.5   |       | dB    |

| P <sub>1dB</sub>      | Input 1 dB compression point (single tone CW)                   | -18.0 | -13.5 |       | dBm   |

| IMD3-50dBm            | Two tone IMD at -50dBm                                          |       | -109  |       | dBm   |

|                       | Two tone CW, f0: 2440 MHz, f1: +/- 3 MHz, f2: +/- 6 MHz         |       |       |       |       |

| IMD3-30dBm            | Two tone IMD at -30dBm                                          |       | -75   |       | dBm   |

|                       | Two tone CW, f0: 2440 MHz, f1: +/- 3 MHz, f2: +/- 6 MHz         |       |       |       |       |

| H2 <sub>RX</sub>      | Harmonic 2nd (CW, -10 dBm)                                      |       | -20   |       | dBm   |

| H3 <sub>RX</sub>      | Harmonic 3rd (CW, -10 dBm)                                      |       | -17   |       | dBm   |

| S <sub>11_ANTdB</sub> | ANT port input reflection (over input frequency, 50 $\Omega$ )  |       | -10.0 | -8.4  | dB    |

| S <sub>22_TRXdB</sub> | TRX port output reflection (over input frequency, 50 $\Omega$ ) |       | -12.0 | -10.6 | dB    |

| A <sub>RX_2GHz</sub>  | Out-of-band gain (at 2 GHz)                                     |       | 5.0   | 6.0   | dB    |

| A <sub>RX_3GHz</sub>  | Out-of-band gain (at 3 GHz)                                     |       | 5.0   | 6.0   | dB    |

| P <sub>MAX,RX</sub>   | Maximum output power (at TRX, $P_{IN} = 0 \text{ dBm}$ )        |       | 2.5   | 5.0   | dBm   |

#### 7.1.3 TX

| Symbol | Description           | Min. | Тур. | Max. | Units |

|--------|-----------------------|------|------|------|-------|

| f      | Input frequency range | 2360 |      | 2500 | MHz   |

| Cumhal                | Description                                                 |      | <b>T</b> |      | 11    |

|-----------------------|-------------------------------------------------------------|------|----------|------|-------|

| Symbol                | Description                                                 | Min. | Тур.     | Max. | Units |

| P <sub>SAT</sub>      | Saturated output power; GFSK/OQPSK modulation               |      | 21.5     |      | dBm   |

| G <sub>TX</sub>       | Gain (P <sub>OUT</sub> <p<sub>P1dB)</p<sub>                 |      | 20       |      | dB    |

| P <sub>P1dB</sub>     | Output power in 1dB compression; GFSK/OQPSK modulation      |      | 21       |      | dBm   |

| AM/AM                 | Compression - positive                                      |      | 6        |      | dB    |

| AM/AM                 | Compression - negative                                      |      | 0        |      | dB    |

| T <sub>carrier</sub>  | Carrier switching time                                      |      |          | 1    | μs    |

|                       | P <sub>OUT</sub> from -30 dBm to +20 dBm                    |      |          |      |       |

| P <sub>SPUR2MHz</sub> | In-band spurious emissions 2 MHz (GFSK/OQPSK)               |      |          | -26  | dBm   |

| P <sub>SPUR3MHz</sub> | In-band spurious emissions 3 MHz (GFSK/OQPSK)               |      |          | -36  | dBm   |

| H2, H3                | Harmonic, 2nd, 3rd; RBW = 1.0 MHz                           |      |          | -42  | dBm   |

| H4, H5                | Harmonic, 4th, 5th; RBW = 1.0 MHz                           |      |          | -36  | dBm   |

| S <sub>11_TRXdB</sub> | Input reflection at TRX pin (over input frequency range, 50 |      | -10      | -7   | dB    |

|                       | Ω)                                                          |      |          |      |       |

| VSWR <sub>STB</sub>   | Unconditionally stable                                      |      |          |      |       |

| VSWR <sub>RGN</sub>   | No permanent damage (load 10:1, all phase angles)           |      |          |      | -     |

|                       |                                                             |      |          |      |       |

### 7.1.4 SPI timing specification

| Symbol                 | Description                                                | Min. | Тур. | Max. | Units |

|------------------------|------------------------------------------------------------|------|------|------|-------|

| т <sub>sck</sub>       | SCK clock period (50% duty cycle)                          | 125  |      |      | ns    |

| T <sub>CSN-SCK1</sub>  | CSN lead time                                              | 62.5 |      |      | ns    |

|                        | Time from CSN set to 0 to first rising edge at SCK         |      |      |      |       |

| T <sub>SCK16-CSN</sub> | CSN trail time                                             | 62.5 |      |      | ns    |

|                        | Time from 16th falling edge at SCK to CSN set to 1         |      |      |      |       |

| T <sub>CSN</sub>       | CSN idle time                                              | 125  |      |      | ns    |

|                        | Time required between consecutive transmissions            |      |      |      |       |

| T <sub>S_MISO</sub>    | MISO settling time                                         | 30   |      |      | ns    |

|                        | Guaranteed settling margin for MISO before 9th rising edge |      |      |      |       |

|                        | at SCK                                                     |      |      |      |       |

# 8 Register interface

### 8.1 Registers

| Base address | Peripheral | Instance   | Description              | Configuration |  |  |  |  |

|--------------|------------|------------|--------------------------|---------------|--|--|--|--|

| 0x0000000    | REGIF      | REGIF      | Register interface       |               |  |  |  |  |

|              |            |            | Table 10: Instar         | nces          |  |  |  |  |

| Register     | Offset     | Descriptio | on                       |               |  |  |  |  |

| CONFREG0     | 0x0        | Configura  | tion register 0          |               |  |  |  |  |

| CONFREG1     | 0x1        | Configura  | Configuration register 1 |               |  |  |  |  |

| CONFREG2     | 0x2        | Configura  | tion register 2          |               |  |  |  |  |

| CONFREG3     | 0x3        | Configura  | tion register 3          |               |  |  |  |  |

| PARTNUMBER   | 0x14       |            |                          |               |  |  |  |  |

| HW_REVISION  | 0x15       |            |                          |               |  |  |  |  |

| HW_ID0       | 0x16       |            |                          |               |  |  |  |  |

| HW_ID1       | 0x17       |            |                          |               |  |  |  |  |

Table 11: Register overview

### 8.1.1 CONFREGO

Address offset: 0x0

Configuration register 0

| Dit r | number     |         |   | 7 6                                       | : c | Λ | о · | 2 1 | 0 |

|-------|------------|---------|---|-------------------------------------------|-----|---|-----|-----|---|

| ыст   | lumber     |         |   |                                           |     |   |     |     |   |

| ID    |            |         |   | C                                         | C C | С | C ( | СВ  | A |

| Res   | et 0x00    |         |   | 0 0                                       | 0 0 | 0 | 0 ( | 0 0 | 0 |

| ID    |            |         |   |                                           |     |   |     |     |   |

| А     | RW TX_EN   |         |   | TX enable                                 |     |   |     |     |   |

|       |            | Disable | 0 | TX mode disabled                          |     |   |     |     |   |

|       |            | Enable  | 1 | TX mode enabled                           |     |   |     |     |   |

| В     | RW MODE    |         |   | Select preset value of TX output power.   |     |   |     |     |   |

|       |            | 0       | 0 | TX_Gain = POUTA                           |     |   |     |     |   |

|       |            | 1       | 1 | TX_Gain = POUTB                           |     |   |     |     |   |

| С     | RW TX_GAIN |         |   | TX gain control (0: minimum, 31: maximum) |     |   |     |     |   |

Initialized with value from POUTA or POUTB. See CONFREG2 and CONFREG3.

#### 8.1.2 CONFREG1

Address offset: 0x1

Configuration register 1

| Bit n | umber      |         |    |                                         | 7    | 6 | 5 | 4 | 3 | 2 | 1 ( |

|-------|------------|---------|----|-----------------------------------------|------|---|---|---|---|---|-----|

| ID    |            |         |    |                                         | E    | E | E | Ε |   | С | ,   |

| Rese  | et 0x00    |         |    |                                         | 0    | 0 | 0 | 0 | 0 | 0 | 0 ( |

|       |            |         |    |                                         |      |   |   |   |   |   |     |

| А     | RW RX_EN   |         |    | RX enable                               |      |   |   |   |   |   |     |

|       |            | Disable | 0  | RX mode disabled                        |      |   |   |   |   |   |     |

|       |            | Enable  | 1  | RX mode enabled                         |      |   |   |   |   |   |     |

| С     | RW UICR_EN |         |    | UICR program mode enable                |      |   |   |   |   |   |     |

|       |            | Disable | 0  |                                         |      |   |   |   |   |   |     |

|       |            | Enable  | 1  |                                         |      |   |   |   |   |   |     |

| E     | RW KEY     |         |    | UICR program mode enter/leave key       |      |   |   |   |   |   |     |

|       |            | Enter   | 15 | Set to 0xF when enabling UICR program r | node |   |   |   |   |   |     |

|       |            | Leave   | 0  | Set to 0x0 when leaving UICR program m  | ode  |   |   |   |   |   |     |

### 8.1.3 CONFREG2

Address offset: 0x2

Configuration register 2

| Bit r | number        |   |   |                                                              | 7     | 6    | 5 | 43  | 2 | 1 | 0 |

|-------|---------------|---|---|--------------------------------------------------------------|-------|------|---|-----|---|---|---|

| ID    |               |   |   |                                                              | D     |      | B | Α Α | A | А | A |

| Rese  | et 0x00       |   |   |                                                              | 0     | 0    | 0 | 0 0 | 0 | 0 | 0 |

| ID    |               |   |   |                                                              |       |      |   |     |   |   |   |

| А     | RW POUTA_UICR |   |   | User defined initialization value for POUTA (0: minimum - PA |       |      |   |     |   |   |   |

|       |               |   |   | disabled, 31: maximum)                                       |       |      |   |     |   |   |   |

| В     | RW POUTA_SEL  |   |   |                                                              |       |      |   |     |   |   |   |

|       |               | 0 | 0 | TX_Gain initialized with POUTA_PROD (20 dBm                  | +/- ( | 0.25 | 5 |     |   |   |   |

|       |               |   |   | dBm)                                                         |       |      |   |     |   |   |   |

|       |               | 1 | 1 | TX_Gain initialized with POUTA_UICR                          |       |      |   |     |   |   |   |

| D     | RW WR_UICR    |   |   | Write UICR memory                                            |       |      |   |     |   |   |   |

|       |               | 0 | 0 | EFUSE idle                                                   |       |      |   |     |   |   |   |

|       |               | 1 | 1 | EFUSE write                                                  |       |      |   |     |   |   |   |

|       |               |   |   |                                                              |       |      |   |     |   |   |   |

#### 8.1.4 CONFREG3

Address offset: 0x3

Configuration register 3

| Bit nu | mber          |   |   |                                                   | 7     | 6    | 5   | 4  | 3 | 2 1 | 0 |

|--------|---------------|---|---|---------------------------------------------------|-------|------|-----|----|---|-----|---|

| ID     |               |   |   |                                                   |       |      | В   | A  | A | A A | A |

| Reset  | 0x00          |   |   |                                                   | 0     | 0    | 0   | 0  | 0 | 0   | 0 |

| ID     |               |   |   |                                                   |       |      |     |    |   |     |   |

| Α      | RW POUTB_UICR |   |   | User defined initialization value for POUTB (0: r | niniı | nur  | n - | PA |   |     |   |

|        |               |   |   | disabled, 31: maximum)                            |       |      |     |    |   |     |   |

| В      | RW POUTB_SEL  |   |   |                                                   |       |      |     |    |   |     |   |

|        |               | 0 | 0 | TX_Gain initialized with POUTB_PROD (10 dBm       | +/-   | 1.00 | D   |    |   |     |   |

|        |               |   |   | dBm)                                              |       |      |     |    |   |     |   |

|        |               | 1 | 1 | TX_Gain initialized with POUTB_UICR               |       |      |     |    |   |     |   |

### 8.1.5 PARTNUMBER

Address offset: 0x14

| А     | RW PARTNUMBER |  | Part identification number |                 |

|-------|---------------|--|----------------------------|-----------------|

| ID    |               |  |                            |                 |

| Rese  | et 0x0C       |  |                            | 0 0 0 0 1 1 0 0 |

| ID    |               |  |                            | ААААААА         |

| Bit n | umber         |  |                            | 7 6 5 4 3 2 1 0 |

### 8.1.6 HW\_REVISION

Address offset: 0x15

| Bit n | umber          |  |                  | 7 ( | 5 5 | 4   | 3 | 2 2 | 1 0 |

|-------|----------------|--|------------------|-----|-----|-----|---|-----|-----|

| ID    |                |  |                  | ΒĒ  | 3 E | B   |   |     |     |

| Rese  | t 0x10         |  |                  | 0 ( | ) ( | ) 1 | 0 | 0 0 | 0 0 |

| ID    |                |  |                  |     |     |     |   |     |     |

| в     | RW HW_REVISION |  | HW revision code |     |     |     |   |     |     |

### 8.1.7 HW\_ID0

Address offset: 0x16

| Bit n | umber     |  |             | 7 6 5 4 3 2 1 0 |

|-------|-----------|--|-------------|-----------------|

| ID    |           |  |             | ААААААА         |

| Rese  | t 0x01    |  |             | 0 0 0 0 0 0 1   |

| ID    |           |  |             |                 |

| A     | RW HW_ID0 |  | Hardware ID |                 |

### 8.1.8 HW\_ID1

Address offset: 0x17

| Bit n | umber     |  |             | 7 6 5 4 3 2 1 0 |

|-------|-----------|--|-------------|-----------------|

| ID    |           |  |             | A A A A A A A A |

| Rese  | et 0x85   |  |             | 1 0 0 0 0 1 0 1 |

| ID    |           |  |             |                 |

| A     | RW HW_ID1 |  | Hardware ID |                 |

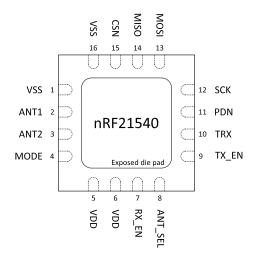

### 9.1 Pin assignments

The pin assignment figure and tables describe the pinouts for the device. There are also recommendations for how the GPIO pins should be configured, in addition to any usage restrictions.

| Pin    | Pin name | Туре        | Description                                     |

|--------|----------|-------------|-------------------------------------------------|

| number |          |             |                                                 |

| 1      | VSS      | Power       | Ground                                          |

| 2      | ANT1     | RF I/O      | First antenna interface                         |

| 3      | ANT2     | RF I/O      | Second antenna interface                        |

| 4      | MODE     | Digital IN  | TX power mode control                           |

| 5      | VDD      | Power       | Supply voltage                                  |

| 6      | VDD      | Power       | Supply voltage                                  |

| 7      | RX_EN    | Digital IN  | RX mode enable                                  |

| 8      | ANT_SEL  | Digital IN  | Antenna select                                  |

| 9      | TX_EN    | Digital IN  | TX mode enable                                  |

| 10     | TRX      | RF IO       | Transceiver interface                           |

| 11     | PDN      | Digital IN  | Power-down, active low                          |

| 12     | SCK      | Digital IN  | SPI clock                                       |

|        |          |             | Connect to VSS if SPI interface is not used     |

| 13     | MOSI     | Digital IN  | SPI data in                                     |

|        |          |             | Connect to VSS if SPI interface is not used     |

| 14     | MISO     | Digital OUT | SPI data out                                    |

|        |          |             | Leave unconnected if SPI interfaces is not used |

| 15     | CSN      | Digital IN  | SPI chip select, active low                     |

|        |          |             | Connect to VDD if SPI interface is not used     |

| 16     | VSS      | Power       | Ground                                          |

| DAP    | VSS      | Power       | Ground                                          |

Table 12: Pin assignments

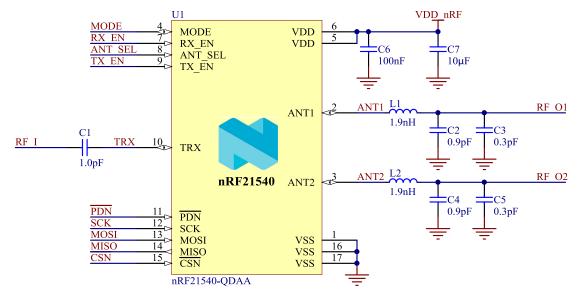

### 9.2 Reference circuitry

The reference circuitry schematic shows the application schematic.

Figure 8: Reference circuitry schematic

The following table lists the recommended and tested component types and values.

| Designator | Value Alt. 1  | Value Alt. 2 | Description                                    | Footprint |

|------------|---------------|--------------|------------------------------------------------|-----------|

| C1         | 1.0 pF        |              | Capacitor, NP0, ±5%                            | 0201      |

| C2, C4     | 1.2 pF        | 0.9 pF       | Capacitor, NP0, ±5%                            | 0201      |

| C3, C5     | N.C.          | 0.3 pF       | Capacitor, NP0, ±5%                            | 0201      |

| C6         | 100 nF        |              | Capacitor, X7S, ±10%                           | 0201      |

| C7         | 10 µF         |              | Capacitor, X7S, ±20%                           | 0603      |

| L1, L2     | 1.9 nH        |              | High frequency chip inductor ±5%               | 0201      |

| U1         | nRF21540-QDAA |              | Radio front-end /range<br>extender for 2.4 GHz | QFN-16    |

Table 13: Bill of material for QFN16

Note: For increased third harmonic suppression, chose value alternative 2 from the table.

# 10 Recommended operating conditions

#### The operating conditions are the physical parameters that the chip can operate within.

| Symbol            | Parameter                   | Notes                                    | Min.             | Nom. | Max.                 | Units |

|-------------------|-----------------------------|------------------------------------------|------------------|------|----------------------|-------|

| VDD               | Main supply voltage/battery | Functional range                         | 1.7              | 3.0  | 3.6                  | V     |

| V <sub>IH</sub>   | Digital input high          | SPI, PDN, ANT_SEL                        | $0.7 V_{VDD}$    |      | V <sub>VDD</sub>     | V     |

| V <sub>IL</sub>   | Digital input low           | SPI, PDN, ANT_SEL                        | V <sub>VSS</sub> |      | 0.3 V <sub>VDD</sub> | V     |

| F <sub>SCK</sub>  | SPI clock frequency         | Exceeding may cause SPI malfunction      |                  |      | 8                    | MHz   |

| C <sub>MISO</sub> | MISO load capacitance       | Exceeding may cause SPI read malfunction |                  |      | 50                   | pF    |

| T <sub>OP</sub>   | Operating temperature range | Board temperature, 1 mm from the package | -40              | +25  | +105                 | °C    |

| ZL                | Load impedance              |                                          |                  | 50   |                      | Ω     |

Table 14: Recommended operating conditions

# 11 Absolute maximum ratings

Maximum ratings are the extreme limits to which the chip can be exposed to for a limited amount of time without permanently damaging it. Exposure to absolute maximum ratings for prolonged periods of time may affect the reliability of the device.

|                              | Note                       | Min. | Max.      | Unit |

|------------------------------|----------------------------|------|-----------|------|

| Supply voltage               |                            |      |           |      |

| VDD                          |                            | 0    | 3.6       | V    |

| VSS                          |                            |      | 0         | V    |

| Digital I/O pin voltage      |                            |      |           |      |

| V <sub>I/O</sub>             | VDD ≤ 3.6 V                | -0.3 | VDD + 0.3 | V    |

| RF I/O pin voltage           |                            |      |           |      |

| V <sub>ANT</sub>             |                            | TBD  | TBD       | V    |

| V <sub>TRX</sub>             |                            | TBD  | TBD       | V    |

| RF I/O pin input power       |                            |      |           |      |

| P <sub>IN_TRX</sub>          | CW, Transmit mode          |      | +5        | dBm  |

| P <sub>IN_ANT</sub>          | CW, Receive/Program mode   |      | +15       | dBm  |

| Environmental                |                            |      |           |      |

| Storage temperature          |                            | -40  | 125       | °C   |

| Reflow soldering temperature | IPC/JEDEC J-STD-020        |      | 260       | °C   |

| MSL                          | Moisture sensitivity level |      |           |      |

| ESD HBM                      | Human Body Model           |      | 2         | kV   |

| ESD CDM                      | Charged Device Model       |      | 1         | kV   |

Table 15: Absolute maximum ratings